Newcastle University

School of Electrical, Electronic and Computer Engineering

# **Interpreted Graph Models**

by Ivan Poliakov PhD Thesis

2011

### Abstract

A model class called an *Interpreted Graph Model (IGM)* is defined. This class includes a large number of graph-based models that are used in asynchronous circuit design and other applications of concurrecy. The defining characteristic of this model class is an underlying static graph-like structure where behavioural semantics are attached using additional entities, such as tokens or node/arc states. The similarities in notation and expressive power allow a number of operations on these formalisms, such as visualisation, interactive simulation, serialisation, schematic entry and model conversion to be generalised.

A software framework called Workcraft was developed to take advantage of these properties of IGMs. Workcraft provides an environment for rapid prototyping of graph-like models and related tools. It provides a large set of standardised functions that considerably facilitate the task of providing tool support for any IGM.

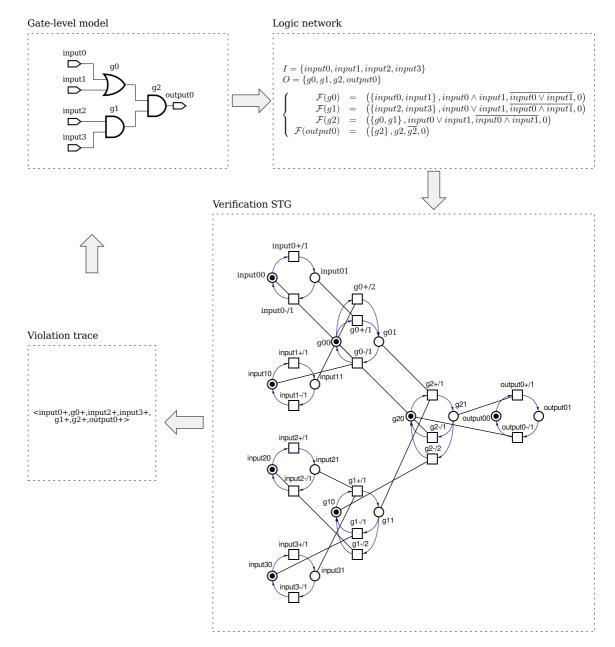

The concept of *Interpreted Graph Models* is the result of research on methods of application of lower level models, such as Petri nets, as a back-end for simulation and verification of higher level models that are more easily manipulated. The goal is to achieve a high degree of automation of this process. In particular, a method for verification of speed-independence of asynchronous circuits is presented. Using this method, the circuit is specified as a gate netlist and its environment is specified as a Signal Transition Graph. The circuit is then automatically translated into a behaviourally equivalent Petri net model. This model is then composed with the specification of the environment. A number of important properties can be established on this compound model, such as the absence of deadlocks and hazards. If a trace is found that violates the required property, it is automatically interpreted in terms of switching of the gates in the original gate-level circuit specification and may be presented visually to the circuit designer.

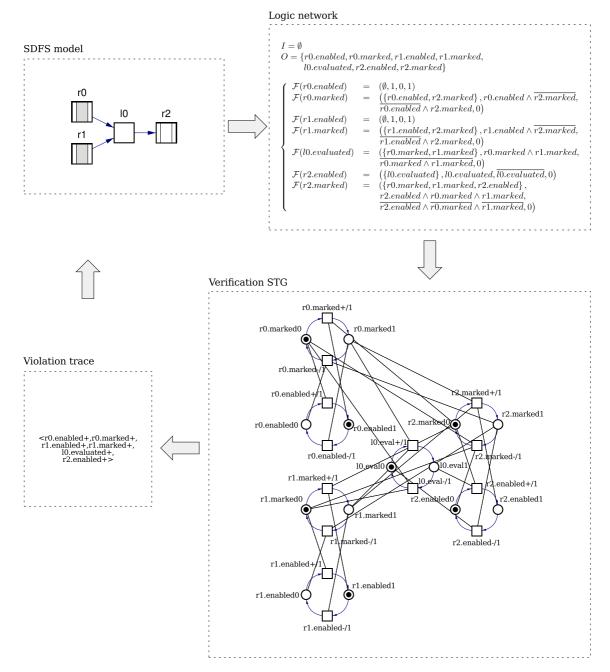

A similar technique is also used for the verification of a model called *Static Data Flow Structure (SDFS)*. This high level model describes the behaviour of an asynchronous data path. SDFS is particularly interesting because it models complex behaviours such as *preemption, early evaluation* and *speculation*. Preemption is a technique which allows to destroy data objects in a computation pipeline if the result of computation is no longer needed, reducing the power consumption. Early evaluation allows a circuit to compute the output using a subset of its inputs and preempting the inputs which are not needed. In speculation, all conflicting branches of computation run concurrently without waiting for the selecting condition; once the selecting condition is computed the unneeded branches are preempted. The automated Petri net based verification technique is especially useful in this case because of the complex nature of these features.

As a result of this work, a number of cases are presented where the concept of IGMs and the Workcraft tool were instrumental. These include the design of two different types of arbiter circuits, the design and debugging of the SDFS model, synthesis of asynchronous circuits from the Conditional Partial Order Graph model and the modification of the workflow of Balsa asynchronous circuit synthesis system.

## Acknowledgements

I am very grateful to my supervisor, Alex Yakovlev, for his invaluable guidance and constant support.

I would like to thank my friends and colleagues for their input, especially Victor Khomenko for the numerous fruitful discussions on the topics of verification, synthesis, and Interpreted Graph Models; Danil Sokolov who formalised the SDFS model and Arseniy Alekseyev who contributed a lot to the development of Workcraft.

I would also like to thank Jordi Cortadella, Oriol Roig and Tomohiro Yoneda for their help setting up the verification tools which made it possible to do the benchmarks for Chapter 4.

And a very special thanks to my family, my father Valery, my mother Natalia and my brother Ilya who were always supporting me, even when the times were dire for themselves; and of course to my wife Katerina, always loving and patient.

This work was supported by the EPSRC grants EP/D053064/1 (SEDATE) and EP/G037809/1 (VERDAD).

# Contents

| Al | bstrac                 | et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            | ii  |

|----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|

| A  | cknow                  | vledgem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ients                                                                      | iii |

| Li | st of l                | knowledgements       iii         at of Figures       x         st of Publications       xv         Introduction       1         1.1       Motivation       4         1.1.1       Automated verification of asynchronous circuits using Petri nets       6         1.1.2       Modelling, simulation and automated verification of the data path of asynchronous circuits       7         1.1.3       Multi-formalism models and interaction between formalisms       9         1.1.4       The tool interoperability problem       10         1.1.5       Interactive graphical environment       12         1.2       Contribution       14         1.3       Organisation of the thesis       15 |                                                                            |     |

| Li | ist of Publications xv |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            | XV  |

| 1  | Intr                   | oductio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n                                                                          | 1   |

|    | 1.1                    | Motiva                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ation                                                                      | 4   |

|    |                        | 1.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Automated verification of asynchronous circuits using Petri nets           | 6   |

|    |                        | 1.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelling, simulation and automated verification of the data path of asyn- |     |

|    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | chronous circuits                                                          | 7   |

|    |                        | 1.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Multi-formalism models and interaction between formalisms                  | 9   |

|    |                        | 1.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The tool interoperability problem                                          | 10  |

|    |                        | 1.1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Interactive graphical environment                                          | 12  |

|    | 1.2                    | Contri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bution                                                                     | 14  |

|    | 1.3                    | Organ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | isation of the thesis                                                      | 15  |

| 2  | Bac                    | kground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | d                                                                          | 18  |

|    | 2.1                    | Async                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hronous circuits                                                           | 18  |

|    |                        | 2.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Delay models                                                               | 19  |

|    |                        | 2.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operation modes                                                            | 19  |

|    |                        | 2.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Classes                                                                    | 20  |

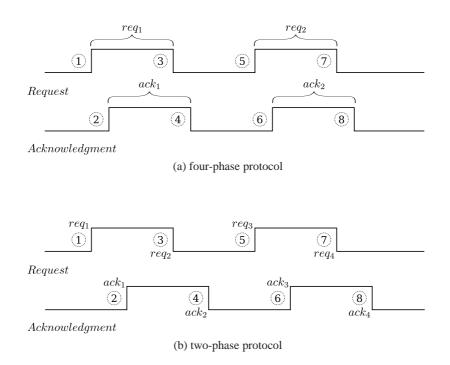

|   |      | 2.1.4   | Handshake protocols                                    | 20 |

|---|------|---------|--------------------------------------------------------|----|

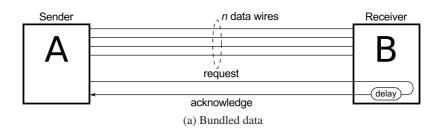

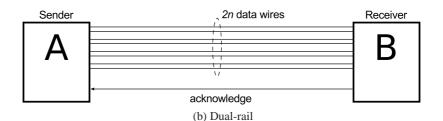

|   |      | 2.1.5   | Data protocols                                         | 21 |

|   | 2.2  | Async   | hronous circuit design paradigms                       | 23 |

|   |      | 2.2.1   | Direct mapping and syntax-driven translation           | 24 |

|   |      | 2.2.2   | Logic synthesis                                        | 26 |

|   |      | 2.2.3   | Mixed approach                                         | 29 |

|   | 2.3  | CAD t   | tools for the design of asynchronous circuits          | 30 |

|   |      | 2.3.1   | Direct mapping/syntax-driven translation tools         | 31 |

|   |      | 2.3.2   | Logic synthesis tools                                  | 33 |

|   |      | 2.3.3   | Analysis and verification tools                        | 36 |

|   |      | 2.3.4   | Modelling tools                                        | 40 |

|   | 2.4  | Conclu  | usions                                                 | 42 |

| _ | _    |         |                                                        |    |

| 3 | Petr | i nets  |                                                        | 43 |

|   | 3.1  | Definit | tions                                                  | 44 |

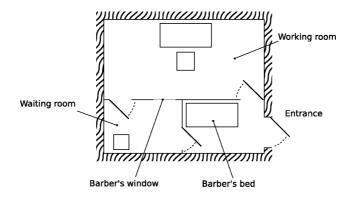

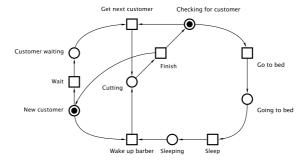

|   |      | 3.1.1   | An example system: the Sleeping Barber's Shop          | 45 |

|   |      | 3.1.2   | Contextual nets                                        | 48 |

|   |      | 3.1.3   | Another example: a traffic network                     | 50 |

|   | 3.2  | Signal  | Transition Graphs                                      | 51 |

|   | 3.3  | Proper  | ties and analysis of Petri nets                        | 52 |

|   | 3.4  | Conclu  | usions                                                 | 53 |

| 4 |      |         |                                                        | 54 |

| 4 |      |         | verification of asynchronous circuits using Petri nets | 54 |

|   | 4.1  |         | erification problem                                    | 56 |

|   | 4.2  | Circuit | ts and Petri nets                                      | 57 |

|   | 4.3  | Constr  | ruction of a circuit Petri net                         | 59 |

|   |      | 4.3.1   | Applying environment interface                         | 59 |

|   |      | 4.3.2   | Read arcs complexity reduction                         | 61 |

|   | 4.4  | Verific | ation                                                  | 62 |

|   |      | 4.4.1   | Detection of potential hazards                         | 62 |

|   |       | 4.4.2    | Detection of interface non-conformance                                | 64  |

|---|-------|----------|-----------------------------------------------------------------------|-----|

|   | 4.5   | A prac   | tical example                                                         | 66  |

|   | 4.6   | Verific  | ation of a counterflow data path controller                           | 70  |

|   | 4.7   | Perform  | nance and comparison statistics                                       | 71  |

|   | 4.8   | Conclu   | isions                                                                | 72  |

| 5 | Mod   | lelling, | simulation and automated verification of the data path of asynchronou | IS  |

|   | circu | uits     |                                                                       | 73  |

|   | 5.1   | The St   | atic Data Flow Structure model                                        | 74  |

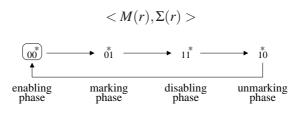

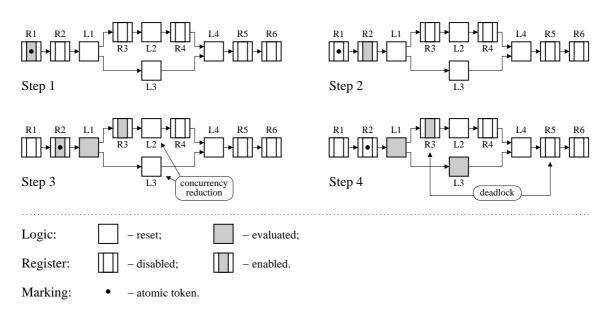

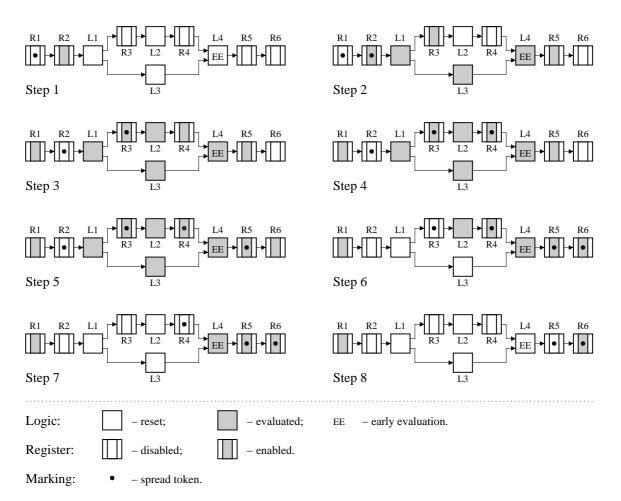

|   | 5.2   | Atomic   | c token semantics                                                     | 76  |

|   | 5.3   | Spread   | token semantics                                                       | 80  |

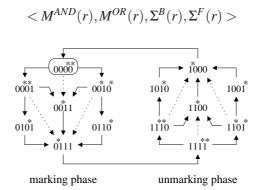

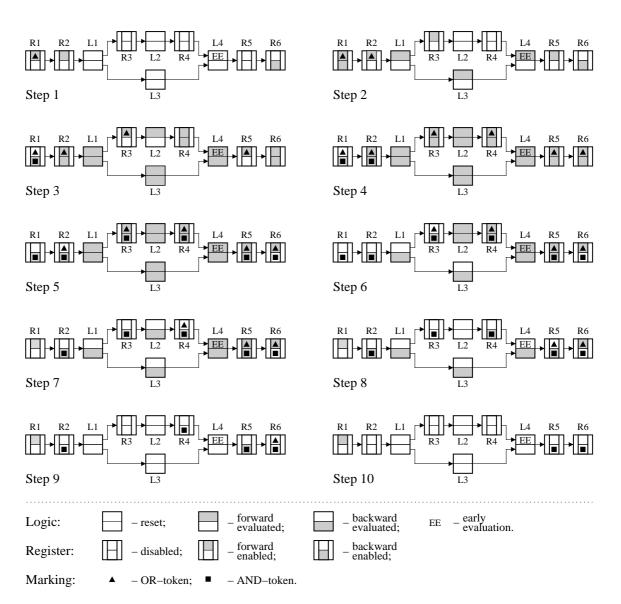

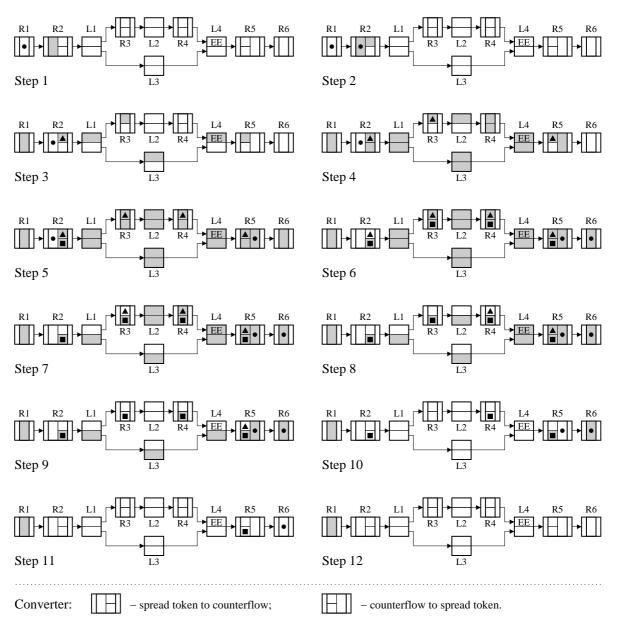

|   | 5.4   | Counte   | erflow semantics                                                      | 84  |

|   | 5.5   | Hybrid   | semantics                                                             | 92  |

|   | 5.6   | Verific  | ation of SDFS models                                                  | 98  |

|   | 5.7   | Compa    | arison of SDFS token game semantics                                   | 102 |

|   | 5.8   | SDFS     | with dynamic elements                                                 | 107 |

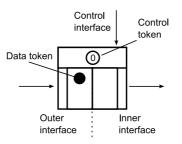

|   |       | 5.8.1    | Dynamic elements                                                      | 108 |

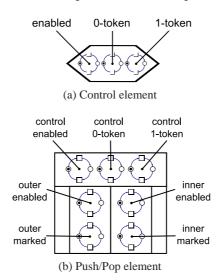

|   |       | 5.8.2    | Control                                                               | 108 |

|   |       | 5.8.3    | Push                                                                  | 109 |

|   |       | 5.8.4    | Pop                                                                   | 110 |

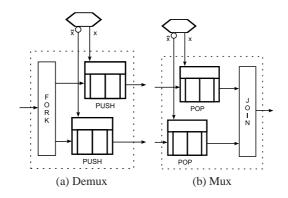

|   |       | 5.8.5    | Mux and Demux                                                         | 110 |

|   |       | 5.8.6    | Mapping of the dynamic SDFS elements into Petri net fragments         | 112 |

|   | 5.9   | Conclu   | isions                                                                | 112 |

| 6 | Inte  | rpreted  | Graph Models                                                          | 114 |

|   | 6.1   | Basic o  | lefinitions                                                           | 116 |

|   | 6.2   | Graphi   | cal representation of Interpreted Graph Models                        | 117 |

|   |       | 6.2.1    | Building a graphical representation of a Petri net                    | 120 |

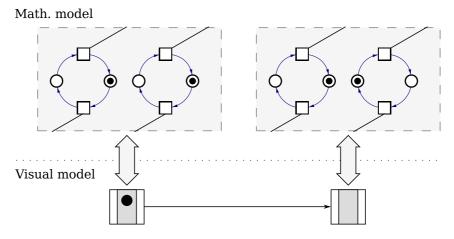

|   |       | 6.2.2    | Using a separate visual model                                         | 121 |

|   |       | 6.2.3    | Using a hierarchical structure                                        | 122 |

|   |     | 6.2.4    | Redefining the display operation                                      | 123 |

|---|-----|----------|-----------------------------------------------------------------------|-----|

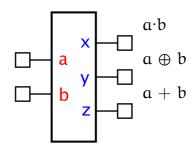

|   | 6.3 | Logic    | networks                                                              | 123 |

|   |     | 6.3.1    | Using logic networks to verify multi-formalism models                 | 126 |

|   | 6.4 | Conclu   | isions                                                                | 126 |

| 7 | Wor | kcraft:  | a framework for Interpreted Graph Models                              | 131 |

|   | 7.1 | Object   | ives                                                                  | 131 |

|   |     | 7.1.1    | Graphical user interface                                              | 132 |

|   |     | 7.1.2    | Tool integration                                                      | 133 |

|   |     | 7.1.3    | Formalism interoperation                                              | 134 |

|   | 7.2 | Compa    | arison with other tools                                               | 135 |

|   | 7.3 | Tool a   | rchitecture                                                           | 136 |

|   |     | 7.3.1    | The framework core                                                    | 137 |

|   |     | 7.3.2    | The plug-in manager                                                   | 138 |

|   |     | 7.3.3    | The graphical user interface                                          | 139 |

|   |     | 7.3.4    | Automated serialisation                                               | 141 |

|   |     | 7.3.5    | Visualisation                                                         | 141 |

|   |     | 7.3.6    | External process management                                           | 141 |

|   | 7.4 | Availa   | bility                                                                | 142 |

|   | 7.5 | Conclu   | isions                                                                | 142 |

| 8 | Use | cases    |                                                                       | 143 |

|   | 8.1 | Verific  | ation of asynchronous circuits                                        | 143 |

|   | 8.2 | Static 1 | Data Flow Structures simulation and verification                      | 144 |

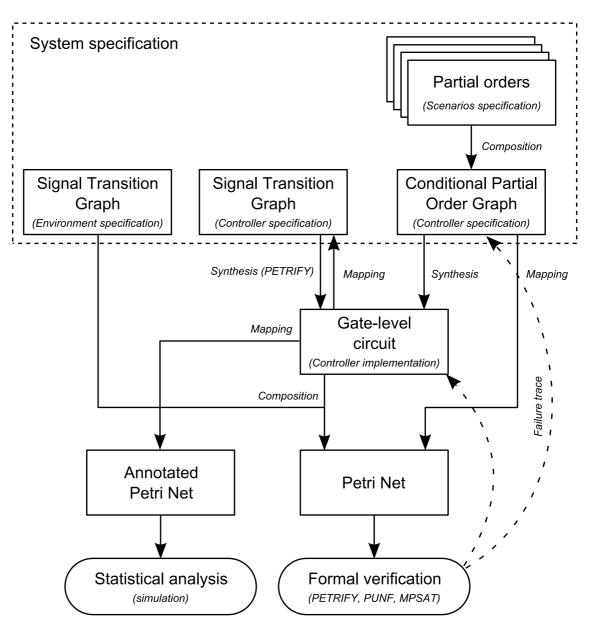

|   | 8.3 | Asyncl   | hronous circuit synthesis based on Conditional Partial Order Graphs   | 146 |

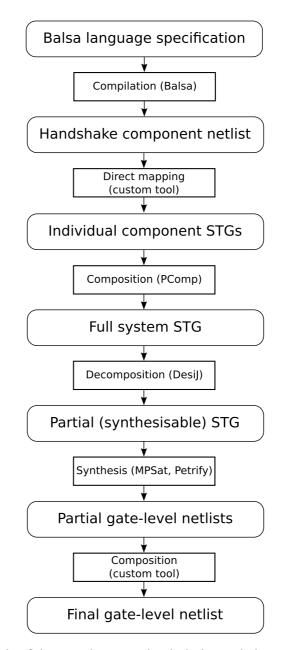

|   | 8.4 | Modifi   | cation of the workflow of Balsa asynchronous circuit synthesis system | 146 |

|   | 8.5 | A deve   | elopment environment based on the STG model                           | 148 |

|   | 8.6 | Conclu   | isions                                                                | 148 |

| 9 | Con | clusions | 3                                                                     | 150 |

|   | 9.1 |          | ary of the contribution                                               | 150 |

|   |     |          |                                                                       |     |

|   | 9.2               | Future                                                                                      | work                                                                                                                                                         | 152                                                                                                                                          |

|---|-------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| A | Wor               | kcraft ı                                                                                    | ıser manual                                                                                                                                                  | 154                                                                                                                                          |

|   | A.1               | Installa                                                                                    | ation and system requirements                                                                                                                                | 154                                                                                                                                          |

|   |                   | A.1.1                                                                                       | Setting up the Java Runtime Environment                                                                                                                      | 154                                                                                                                                          |

|   |                   | A.1.2                                                                                       | Distribution structure                                                                                                                                       | 155                                                                                                                                          |

|   |                   | A.1.3                                                                                       | Plug-in reconfiguration                                                                                                                                      | 156                                                                                                                                          |

|   |                   | A.1.4                                                                                       | Launching Workcraft                                                                                                                                          | 156                                                                                                                                          |

|   | A.2               | Comm                                                                                        | and-line mode                                                                                                                                                | 157                                                                                                                                          |

|   | A.3               | GUI m                                                                                       | ode                                                                                                                                                          | 158                                                                                                                                          |

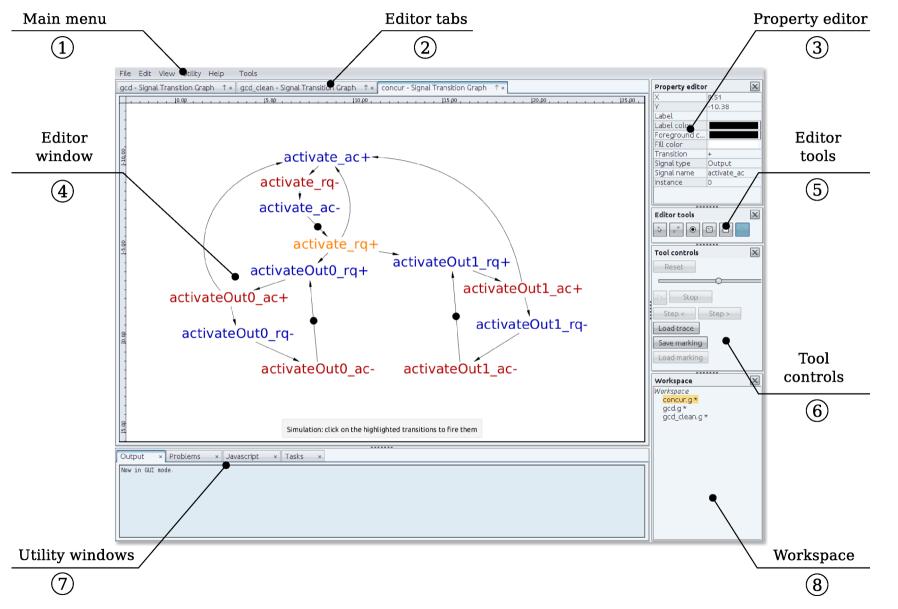

|   |                   | A.3.1                                                                                       | User interface overview                                                                                                                                      | 158                                                                                                                                          |

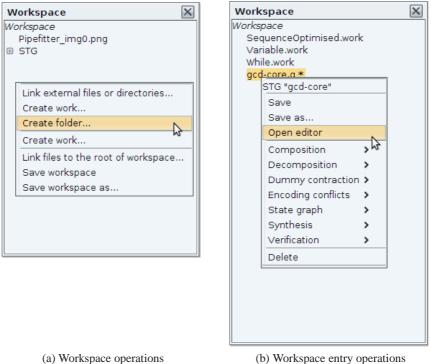

|   |                   | A.3.2                                                                                       | Workspace                                                                                                                                                    | 161                                                                                                                                          |

|   |                   | A.3.3                                                                                       | Working with models                                                                                                                                          | 163                                                                                                                                          |

|   |                   | A.3.4                                                                                       | Changing the user interface layout                                                                                                                           | 166                                                                                                                                          |

|   |                   | A.3.5                                                                                       | Changing the look and feel of the interface                                                                                                                  | 167                                                                                                                                          |

|   |                   |                                                                                             | Workcraft                                                                                                                                                    | 170                                                                                                                                          |

| R | - H.VTP           | nnino v                                                                                     |                                                                                                                                                              | 169                                                                                                                                          |

| B |                   | 0                                                                                           |                                                                                                                                                              | <b>169</b>                                                                                                                                   |

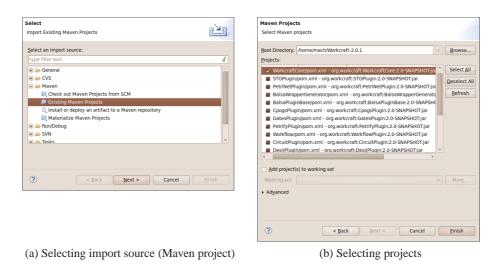

| B | Exte<br>B.1       | Buildir                                                                                     | ng Workcraft                                                                                                                                                 | 169                                                                                                                                          |

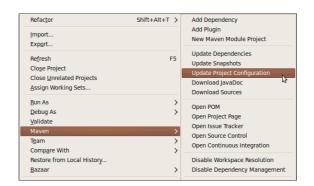

| B |                   | Buildin<br>B.1.1                                                                            | ng Workcraft                                                                                                                                                 | 169<br>170                                                                                                                                   |

| B |                   | Buildin<br>B.1.1<br>B.1.2                                                                   | ng Workcraft                                                                                                                                                 | 169                                                                                                                                          |

| B |                   | Buildin<br>B.1.1                                                                            | ng Workcraft       Creating a code branch       Building with Maven       Building Workcraft using the Eclipse integrated development environment            | 169<br>170<br>170                                                                                                                            |

| B | B.1               | Buildin<br>B.1.1<br>B.1.2<br>B.1.3                                                          | ng Workcraft       Creating a code branch       Building with Maven       Building Workcraft using the Eclipse integrated development environment      (IDE) | 169<br>170<br>170<br>171                                                                                                                     |

| B |                   | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin                                               | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> </ol>                                                                  |

| B | B.1               | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1                                      | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> </ol>                                                     |

| B | B.1<br>B.2        | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1<br>B.2.2                             | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> <li>175</li> </ol>                                        |

| B | B.1               | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1<br>B.2.2<br>Adding                   | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> <li>175</li> <li>176</li> </ol>                           |

| B | B.1<br>B.2        | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1<br>B.2.2<br>Adding<br>B.3.1          | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> <li>175</li> <li>176</li> <li>177</li> </ol>              |

| B | B.1<br>B.2<br>B.3 | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1<br>B.2.2<br>Adding<br>B.3.1<br>B.3.2 | Ing Workcraft                                                                                                                                                | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> <li>175</li> <li>176</li> <li>177</li> <li>179</li> </ol> |

| B | B.1<br>B.2        | Buildin<br>B.1.1<br>B.1.2<br>B.1.3<br>Creatin<br>B.2.1<br>B.2.2<br>Adding<br>B.3.1<br>B.3.2 | ng Workcraft                                                                                                                                                 | <ol> <li>169</li> <li>170</li> <li>170</li> <li>171</li> <li>173</li> <li>175</li> <li>175</li> <li>176</li> <li>177</li> </ol>              |

|   |     | B.4.2   | Implementing the connection methods | 182 |

|---|-----|---------|-------------------------------------|-----|

|   |     | B.4.3   | Defining editable properties        | 184 |

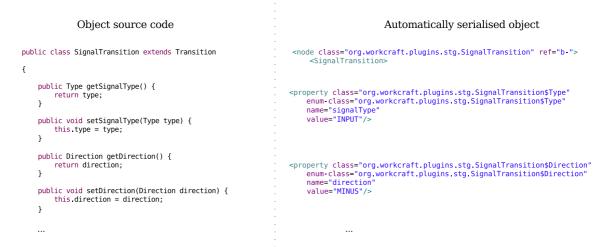

|   |     | B.4.4   | Using the automatic serialisation   | 185 |

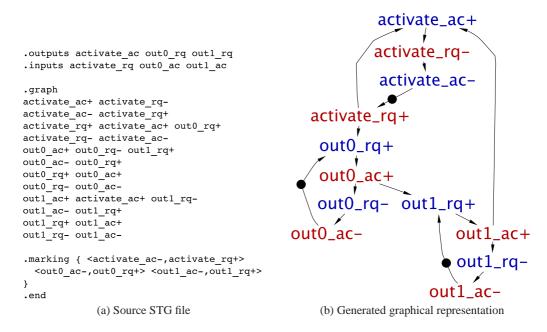

| С | Wor | king wi | th Signal Transition Graphs         | 197 |

|   | C.1 | Using   | the STG editor interface            | 197 |

|   |     | C.1.1   | STG editor tools                    | 198 |

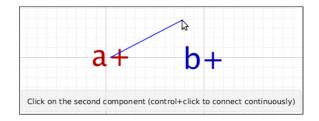

|   |     | C.1.2   | Assigning signal names and types    | 199 |

|   |     | C.1.3   | Placing tokens                      | 200 |

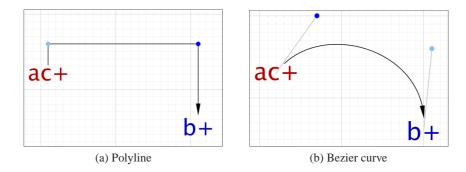

|   |     | C.1.4   | Changing arc shapes                 | 200 |

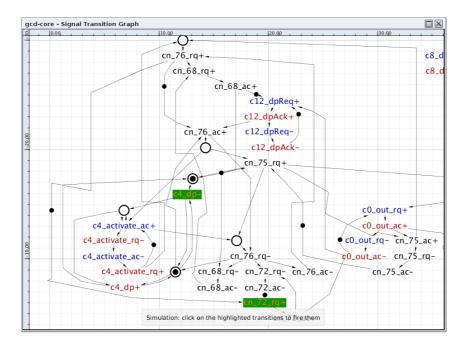

|   | C.2 | Simula  | ation                               | 201 |

|   | C.3 | Using   | tools                               | 202 |

|   |     | C.3.1   | Visual layout                       | 202 |

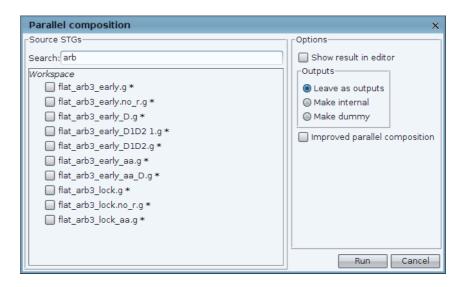

|   |     | C.3.2   | Parallel composition                | 203 |

|   |     | C.3.3   | Decomposition                       | 204 |

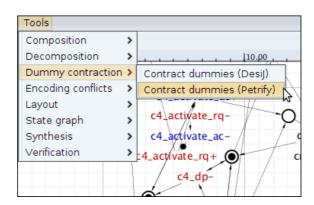

|   |     | C.3.4   | Dummy contraction                   | 205 |

|   |     | C.3.5   | CSC conflict resolution             | 206 |

|   |     | C.3.6   | Deadlock detection                  | 207 |

|   |     | C.3.7   | Reachability analysis               | 207 |

|   |     |         |                                     |     |

### Bibliography

209

# **List of Figures**

| 1.1  | Architecture of an ARM-based system-on-a-chip.                                | 2  |

|------|-------------------------------------------------------------------------------|----|

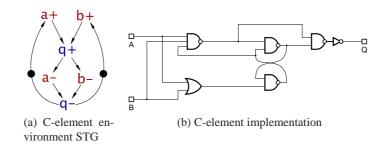

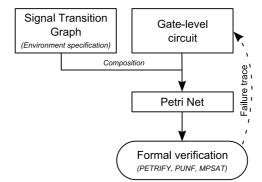

| 1.2  | A circuit model specified using a gate-level net-list and an environment STG  | 9  |

| 1.3  | The interaction between different formalisms.                                 | 9  |

| 1.4  | Schematic of the asynchronous circuit design technique called "resynthesis"   | 11 |

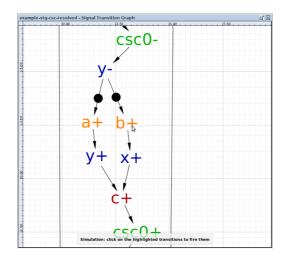

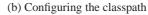

| 1.5  | Interactive STG simulation. Note that the enabled transitions (a+ and b+) are |    |

|      | highlighted                                                                   | 12 |

| 2.1  | Handshake protocols                                                           | 21 |

| 2.2  | Data protocols                                                                | 22 |

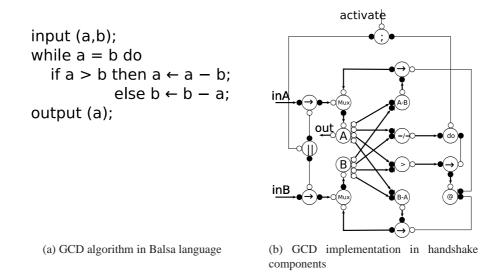

| 2.3  | An implementation of the greatest common divisor (GCD) algorithm in Balsa     | 24 |

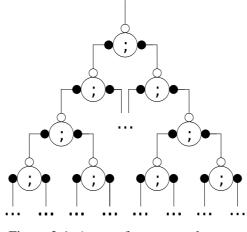

| 2.4  | A tree of sequence elements                                                   | 25 |

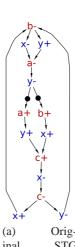

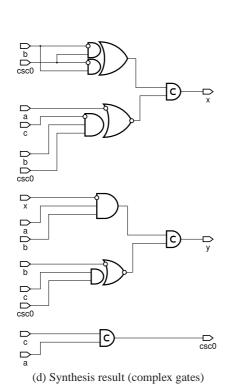

| 2.5  | Logic synthesis                                                               | 27 |

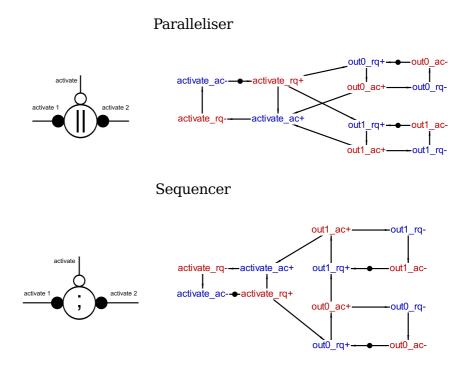

| 2.6  | Handshake components and their corresponding STGs                             | 29 |

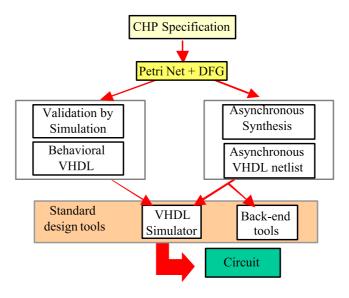

| 2.7  | Balsa design workflow                                                         | 31 |

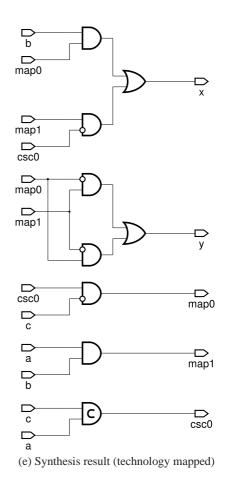

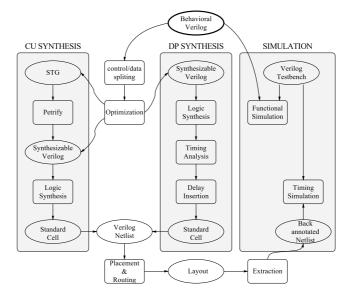

| 2.8  | VeriSyn                                                                       | 32 |

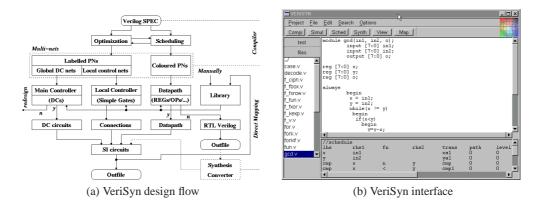

| 2.9  | VeriMap design flow                                                           | 33 |

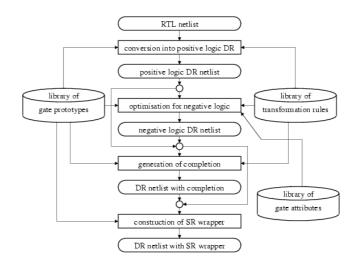

| 2.10 | Pipefitter design flow.                                                       | 34 |

| 2.11 | TAST design flow                                                              | 34 |

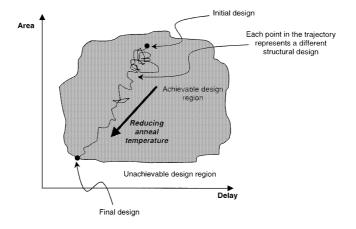

| 2.12 | MOODS design space traversal algorithm                                        | 35 |

| 2.13 | Composition of a circuit and its environment in Versify                       | 37 |

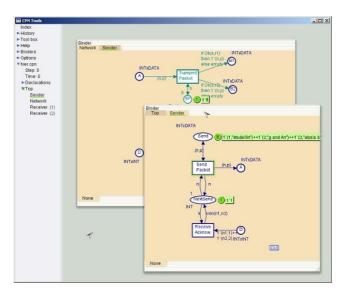

| 2.14 | CPN Tools GUI                                                                 | 38 |

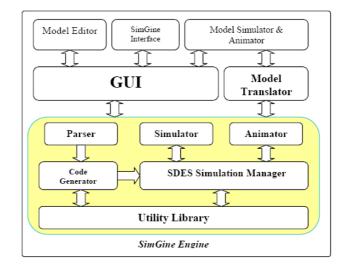

| 2.15 | PDETool architecture                                                          | 40 |

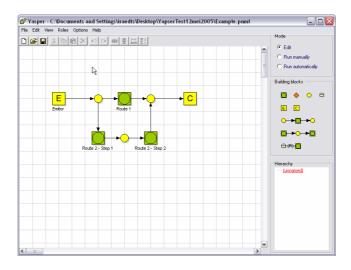

| 2.16 | Yasper GUI                                                  | 41 |

|------|-------------------------------------------------------------|----|

| 2.17 | Draw-Net GUI                                                | 42 |

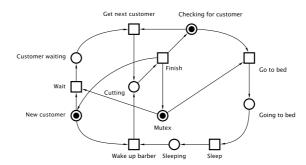

| 3.1  | The Sleeping Barber's Shop                                  | 45 |

| 3.2  | Petri net model                                             | 46 |

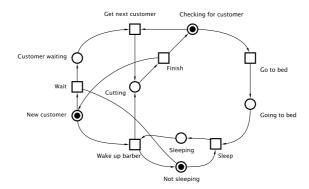

| 3.3  | Improved Petri net model                                    | 47 |

| 3.4  | A Petri net model with a complementary place and a read arc | 48 |

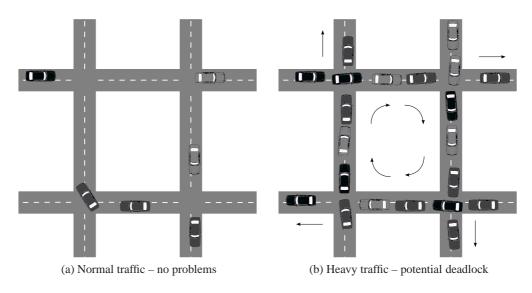

| 3.5  | The gridlock problem                                        | 49 |

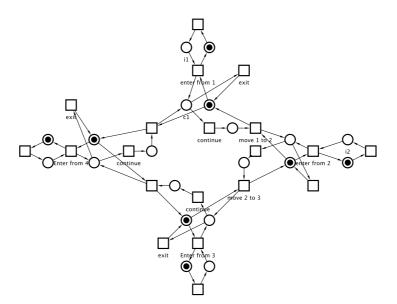

| 3.6  | A Petri net model of four intersecting roads                | 50 |

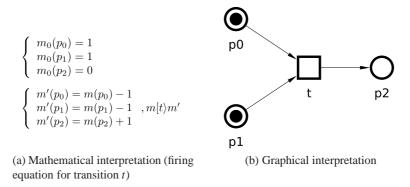

| 3.7  | Graphical representation of an STG                          | 51 |

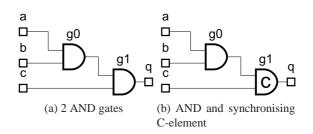

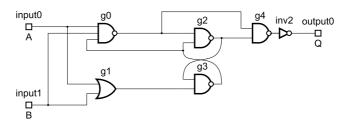

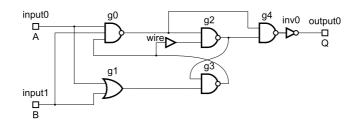

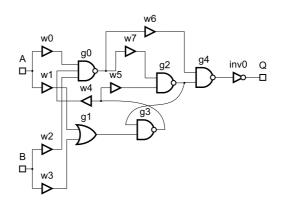

| 4.1  | An intuitive implementation of 3-input AND gate             | 56 |

| 4.2  | Examples of elementary cycles in circuit Petri net          | 59 |

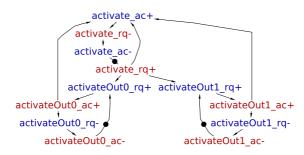

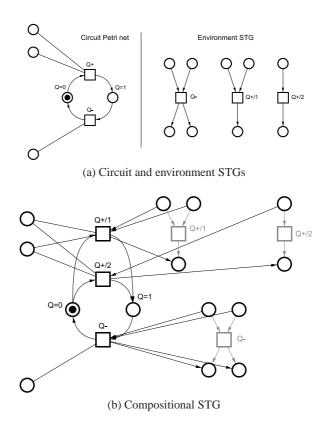

| 4.3  | Composition of circuit and environment STGs                 | 61 |

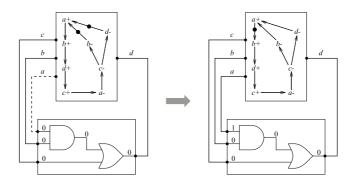

| 4.4  | Read arcs complexity reduction                              |    |

|      | (a) multiple read arcs associated with one place            |    |

|      | (b) only one read arc per place                             | 61 |

| 4.5  | Non-semi-modular states                                     | 63 |

| 4.6  | A C-element interface STG                                   | 65 |

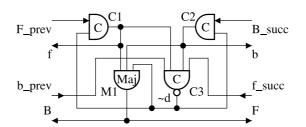

| 4.7  | NAND C-element implementation                               | 66 |

| 4.8  | NAND-OR C-element implementation                            |    |

|      | (no wire delays)                                            | 67 |

| 4.9  | NAND-OR C-element implementation                            |    |

|      | (wire delay present on one fork only)                       | 68 |

| 4.10 | NAND-OR C-element implementation                            |    |

|      | (full set of wire delays)                                   | 68 |

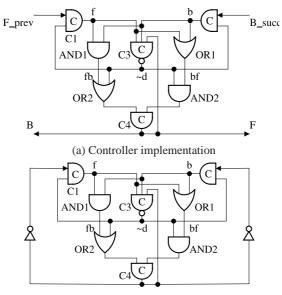

| 4.11 | A counterflow stage controller                              | 69 |

| 4.12 | Revised counterflow stage controller                        | 69 |

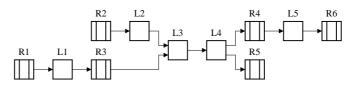

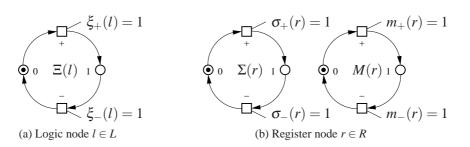

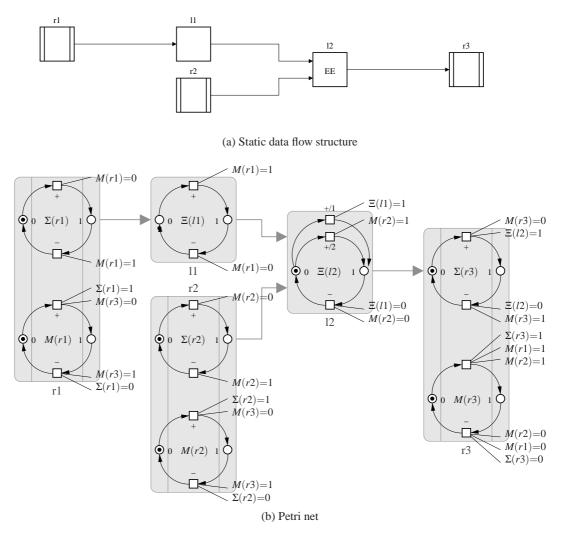

| 5.1  | SDFS example                                                | 76 |

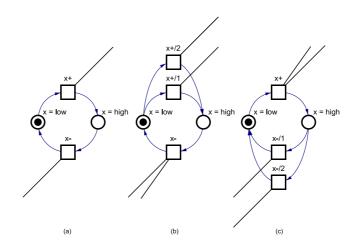

| 5.2  | Behaviour of a register                                     | 79 |

| 5.3  | Atomic token SDFS example                                                    | 80  |

|------|------------------------------------------------------------------------------|-----|

| 5.4  | Spread token SDFS example                                                    | 83  |

| 5.5  | Behaviour of counterflow register                                            | 90  |

| 5.6  | Counterflow SDFS example                                                     | 91  |

| 5.7  | Combined spread token and counterflow SDFS example                           | 99  |

| 5.8  | Underlying STG for spread token SDFS                                         | 99  |

| 5.9  | Mapping SDFS with spread token semantics into Petri net                      | 101 |

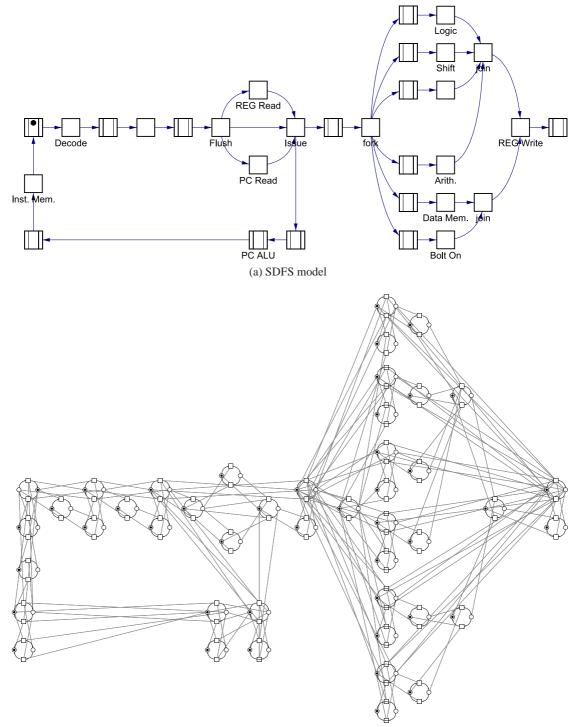

| 5.10 | ARISC processor                                                              | 103 |

| 5.11 | Graphical representation of a control node                                   | 108 |

| 5.12 | Graphical representation of the push and pop nodes                           | 109 |

| 5.13 | Implementation of the multiplexer and demultiplexer using dynamic components | 111 |

| 5.14 | Petri net mapping of the dynamic elements                                    | 111 |

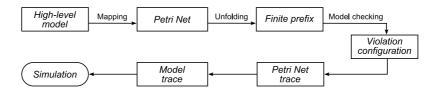

| 6.1  | High level model verification workflow based on Petri nets                   | 114 |

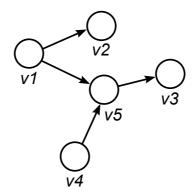

| 6.2  | A directed graph                                                             | 115 |

| 6.3  | Different interpretations of a Petri net                                     | 116 |

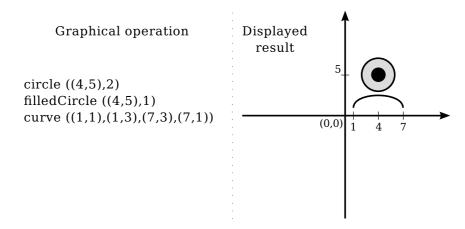

| 6.4  | An example of a graphical operation                                          | 117 |

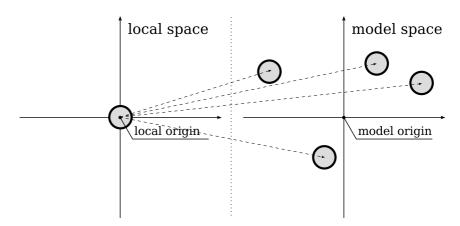

| 6.5  | Combining a local space drawing function with a transformation               | 118 |

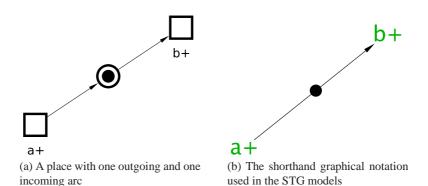

| 6.6  | Graphical notation violating the one-to-one correspondence                   | 121 |

| 6.7  | A Petri net model visualised using the SDFS graphical notation               | 121 |

| 6.8  | An example of the hierarchical arrangement of graph nodes                    | 122 |

| 6.9  | Verification of a gate-level model using a logic network                     | 128 |

| 6.10 | Verification of an SDFS model using a logic network                          | 129 |

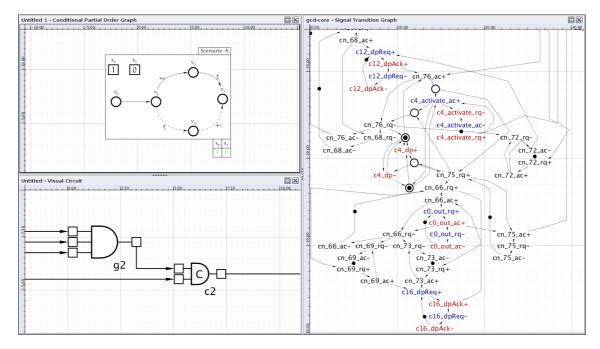

| 7.1  | Working with three different model types simultaneously                      | 132 |

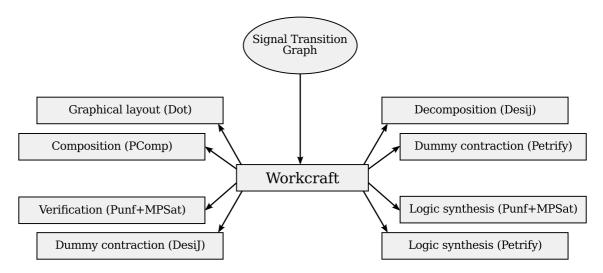

| 7.2  | The tool integration aspect of Workcraft                                     | 134 |

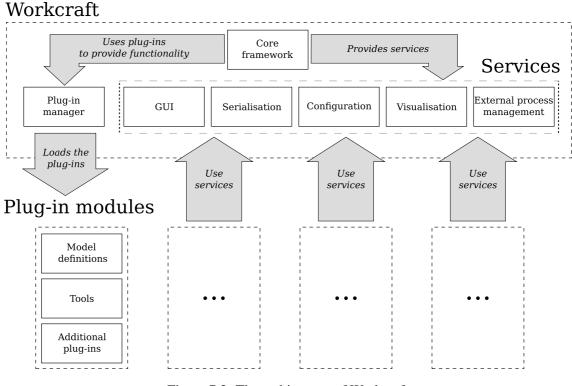

| 7.3  | The architecture of Workcraft                                                | 137 |

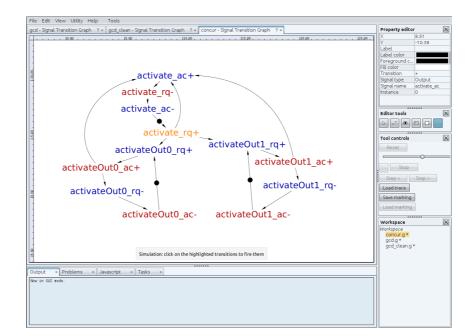

| 7.4  | The graphical user interface of Workcraft                                    | 139 |

| 7.5  | The property editor                                                          | 140 |

| 7.6  | An example of automated serialisation                                        | 140 |

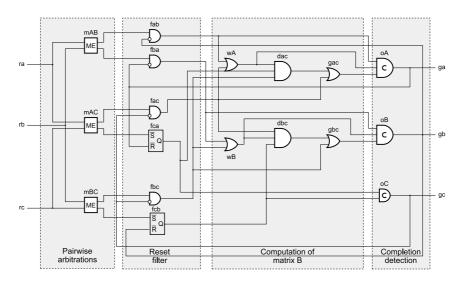

| 8.1                                                                                                                                | Implementation of a 3-way flat arbiter                        | 144                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

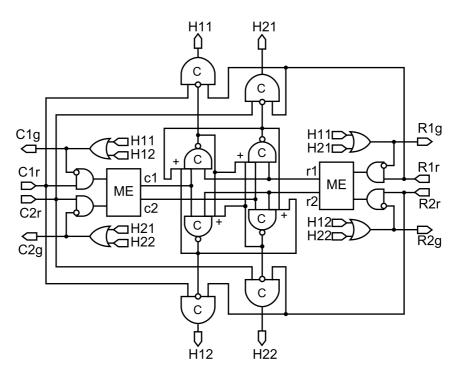

| 8.2                                                                                                                                | Implementation of a multi-resource arbiter                    | 145                                                                                                                                          |

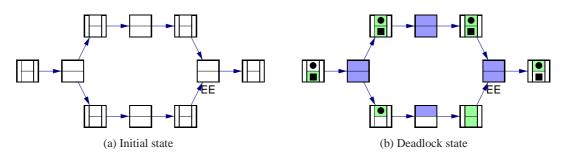

| 8.3                                                                                                                                | Counterflow SDFS verification example                         | 145                                                                                                                                          |

| 8.4                                                                                                                                | The STG specifications of handshake components                | 147                                                                                                                                          |

| 8.5                                                                                                                                | A complex model interoperability example                      | 149                                                                                                                                          |

| A.1                                                                                                                                | The Workcraft distribution structure                          | 155                                                                                                                                          |

| A.2                                                                                                                                | Workcraft running in the interactive command-line mode        | 157                                                                                                                                          |

| A.3                                                                                                                                | A script for automated generation of SVG images from .g files | 159                                                                                                                                          |

| A.4                                                                                                                                | The main window of Workcraft                                  | 160                                                                                                                                          |

| A.5                                                                                                                                | The workspace window and its context menus                    | 162                                                                                                                                          |

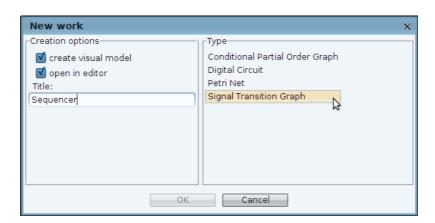

| A.6                                                                                                                                | The "New work" dialogue                                       | 163                                                                                                                                          |

| A.7                                                                                                                                | The model import dialogue                                     | 164                                                                                                                                          |

| A.8                                                                                                                                | The model export sub-menu                                     | 164                                                                                                                                          |

| A.9                                                                                                                                | The editor tools window with a hotkey tool-tip                | 164                                                                                                                                          |

| 1 1.7                                                                                                                              |                                                               |                                                                                                                                              |

|                                                                                                                                    | The set of tools applicable for the current model (an STG)    | 165                                                                                                                                          |

| A.10                                                                                                                               |                                                               | 165<br>165                                                                                                                                   |

| A.10<br>A.11                                                                                                                       | The set of tools applicable for the current model (an STG)    |                                                                                                                                              |

| A.10<br>A.11                                                                                                                       | The set of tools applicable for the current model (an STG)    | 165                                                                                                                                          |

| A.10<br>A.11<br>A.12                                                                                                               | The set of tools applicable for the current model (an STG)    | 165<br>166                                                                                                                                   |

| A.10<br>A.11<br>A.12<br>B.1                                                                                                        | The set of tools applicable for the current model (an STG)    | 165<br>166<br>171<br>172                                                                                                                     |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2                                                                                                 | The set of tools applicable for the current model (an STG)    | 165<br>166<br>171<br>172                                                                                                                     |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2<br>B.3                                                                                          | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> </ol>                                                                  |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2<br>B.3<br>B.4                                                                                   | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> <li>174</li> </ol>                                                     |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5                                                                            | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> <li>174</li> <li>174</li> </ol>                                        |

| <ul> <li>A.10</li> <li>A.11</li> <li>A.12</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>B.6</li> </ul> | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> <li>174</li> <li>174</li> <li>176</li> </ol>                           |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7                                                              | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> <li>174</li> <li>174</li> <li>176</li> <li>177</li> </ol>              |

| A.10<br>A.11<br>A.12<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8<br>B.9                                                | The set of tools applicable for the current model (an STG)    | <ol> <li>165</li> <li>166</li> <li>171</li> <li>172</li> <li>173</li> <li>174</li> <li>174</li> <li>176</li> <li>177</li> <li>187</li> </ol> |

| B.12 A progress monitor implementation                      | 191 |

|-------------------------------------------------------------|-----|

| B.13 An example <i>ModelDescriptor</i> implementation       | 192 |

| B.14 An example <i>VisualModelDescriptor</i> implementation | 193 |

| B.15 A visual node implementation                           | 194 |

| B.16 An example <i>NodeGenerator</i> implementation         | 195 |

| B.17 An example <i>PropertyDescriptor</i> implementation    | 196 |

|                                                             | 107 |

| C.1 The STG editor tools                                    | 197 |

| C.2 Creating a connection                                   | 198 |

| C.3 Editing signal transitions                              | 199 |

| C.4 Arcs drawn using different shapes                       | 200 |

| C.5 Editor window in simulation mode                        | 201 |

| C.6 Simulation tool controls                                | 201 |

| C.7 The settings window                                     | 202 |

| C.8 Automatic STG layout generation using Dot               | 203 |

| C.9 STG selection for parallel composition                  | 204 |

| C.10 DesiJ configuration window                             | 205 |

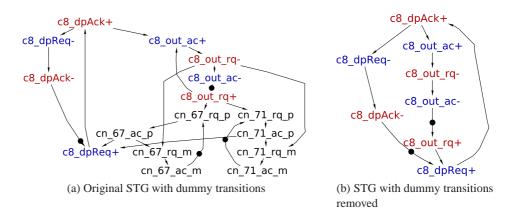

| C.11 Dummy contraction example                              | 206 |

| C.12 Failure trace report                                   | 207 |

| C.13 MPSat configuration interface                          | 208 |

## **List of Publications**

### Conference papers

- 2007 Workcraft: A Static Data Flow Structure Editing, Visualisation and Analysis Tool (Ivan Poliakov, Danil Sokolov, Andrey Mokhov), In Petri Nets and Other Models of Concurrency (ICATPN '2007)

- 2007 Asynchronous Data Path Models (Danil Sokolov, Ivan Poliakov, Alexandre Yakovlev), In Proceedings of the Seventh International Conference on Application of Concurrency to System Design (ACSD '07)

- 2008 Automated Verification of Asynchronous Circuits Using Circuit Petri Nets (Ivan Poliakov, Andrey Mokhov, Ashur Rafiev, Danil Sokolov, and Alex Yakovlev), In Proceedings of the 2008 14th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC '08)

- 2008 Static Data Flow Structures with Dynamic Elements (Ivan Poliakov, Danil Sokolov, Alex Yakovlev, Charles Brej), *In Proceedings of the 20th UK Asynchronous Forum (UKAF '2008)*

- 2009 Workcraft a Framework for Interpreted Graph Models (Ivan Poliakov, Victor Khomenko, Alex Yakovlev), In Proceedings of the 30th International Conference on Applications and Theory of Petri Nets (PETRI NETS '09)

### Journal papers

2008 Analysis of Static Dataflow Structures (Danil Sokolov, Ivan Poliakov, Alex Yakovlev), Fundamenta Informaticae, Vol. 88, No.4, pp. 581-610, IOS Press

### Public tool demonstrations

- 2007 Design and Testing in Europe (DATE)

- 2007 International conference on Petri Nets and Other Models of Concurrency (ICAPTN)

- 2009 International Conference on Applications and Theory of Petri Nets (PETRI NETS)

2008 – 2011 IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC)

### **Chapter 1**

# Introduction

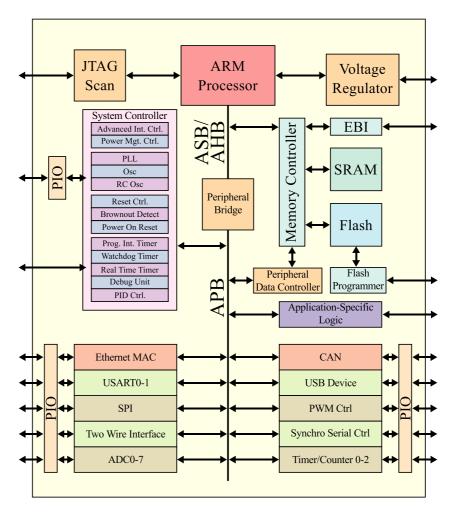

With the continuous increase of the number of transistors that can be put on a single VLSI chip, configurations known as system-on-a-chip (SoC) are becoming more and more popular [96]. Such systems consist of a number of interconnected heterogeneous blocks, such as processors, memory and I/O controllers, built as a single chip (Figure 1.1)<sup>1</sup>. Tighter integration reduces the size of the system and the cost to produce, resulting in portable, high-performance and power efficient consumer products, such as modern smartphones and tablet PCs.

Most of the circuits produced by industry today are synchronous. The operation of their components is controlled by one or more globally distributed periodic signals called clock. Combining pre-designed components into a globally clocked SoC is not a trivial task. Each component (usually called an *IP core*) is designed for a certain clock frequency, and its correct functionality relies on the clock signal being delivered at the same time to all parts of the system. But it is not always possible to use a common clock frequency for the whole SoC. Additionally, the variations in interconnects between IP cores lead to the clock skew problem: reliable distribution of the global clock signal becomes an extremely complex task when the size of the system is in the order of billions of transistors [48, 113].

Therefore, when designing such systems, it is no longer possible to rely solely on the traditional approach of using the globally distributed clock signal.

Solving the problem of communication between the various IP cores clocked with different

<sup>&</sup>lt;sup>1</sup>Image by Colin M.L. Burnett, used under the terms of GFDL: http://www.gnu.org/copyleft/fdl.html

Figure 1.1: Architecture of an ARM-based system-on-a-chip.

frequencies, some potentially self-timed, and all running in parallel becomes one of the central requirements for a successful IC design.

One of the widely accepted solutions to this problem is the use of asynchronous circuits to bridge the IP cores, resulting in what is called a GALS (globally asynchronous, locally synchronous) design [37]. In a GALS system, each synchronous block is interfaced with an asynchronous wrapper that provides communication facilities between blocks in an asynchronous manner.

Asynchronous logic holds several important advantages over synchronous designs. For example, in the context of SoCs, asynchronous circuits can be made to interface with a clocked circuit independent of the clock frequency. Without an asynchronous communication layer, communication between blocks with unrelated clock frequencies (e.g. 333 MHz and 500 MHz) would be very hard to implement efficiently. Having a reliable method of interfacing blocks with arbitrary frequencies not only eliminates the need for the global clock, but greatly increases the potential for component re-use.

A logical evolution of the GALS paradigm is a fully self-timed system, where components do not have local clocks but instead operate asynchronously, using causal relations between events. In addition to better modularity and the lack of clock distribution problem, fully asynchronous circuits possess properties that may be invaluable for certain applications. Among such properties are the inherent concurrency which can exploit parallelism, generally lower power requirements, better tolerance to voltage fluctuations and the ability to automatically adjust operating speed according to changing environmental conditions [85, 43, 110, 118]. These properties allow asynchronous circuits to be used not only in systems where robust concurrent operation is important (e.g. SoCs), but also in specialised devices, such as those operating on harvested power, where a synchronous circuit would be unusable. The absence of the global clock results in lower electromagnetic interference, as well as better device security due to resistance to power analysis attacks (e.g. differential power analysis [71]) – a property that is essential for security-sensitive applications [78].

Unfortunately, asynchronous design technology has its own share of drawbacks that prevent the technology from becoming mainstream. Mitigating some of these problems, which are outlined further in this chapter, is the motivation for this work.

### 1.1 Motivation

The complexity of the asynchronous circuit design process is generally seen as a major drawback preventing the wider adoption of this technology by the industry. There are numerous factors contributing to this perception, and one of the most important ones is the lack of appropriate design tools. The availability of mature, robust tools for the design of synchronous circuits is much higher than that of the tools aimed at an asynchronous approach. In fact, many asynchronous design groups rely on modifying the tools that exist for synchronous design. Because those tools will treat an asynchronous circuit as if it were synchronous, various tricks and workarounds are required to ensure the correct functionality of the resulting design. In many cases, such workarounds are inefficient. Additionally, important design stages, such as asynchronous logic verification, may be very difficult to integrate into the design flow.

Tools that are available specifically for the purpose of asynchronous logic design tend to suffer from limited efficiency due to the phenomenon of state space explosion [117]. This often means that the designer of an asynchronous system is forced to design or verify parts of the circuit manually to overcome these limitations, which is not only time-consuming, but also implies that the designer must have vast knowledge and experience to produce reliable solutions.

The design process of any relatively large asynchronous circuit generally consists of three stages: behavioural specification, implementation and verification. During specification, the expected behaviour of the circuit is described using either a general-purpose hardware description language, such as Verilog [114], VHDL [87] and SystemC [53], or a language designed specifically for asynchronous circuits, such as Tangram [119] or Balsa [47]. The high-level language description is decomposed into a set of communicating processes, or components. The interaction between the processes is captured using a formal model. Numerous formalisms are used for this purpose in different design flows, including Petri nets [84, 90], Signal Transition Graphs [126], process algebras [24, 29], Communicating Sequential Processes [56] and other. Different parts of the system may be described using different formalisms, in contrast to synchronous systems, where the finite state machine (FSM) model is most often the fundamental construct underlying

the whole design process.

For implementation, the specifications of control and data paths are extracted from the formal model. The control and data paths are implemented and optimised separately to improve the design features of each path independently. For example, the control path is often optimised for low latency and size, while the data path is optimised for power consumption and throughput. There are two distinct methodologies used to obtain the implementation of the control and data paths: logic synthesis [68, 41] and direct mapping [47, 119, 106]. In direct mapping, elements of the formal model are mapped into pre-designed components using one-to-one correspondence. In logic synthesis, the implementation is produced through the analysis of the state graph of the system. Logic synthesis produces more efficient solutions, however it is only applicable for small controllers due to its algorithmic complexity. Direct mapping method is very fast and may be used to build very large circuits, but it often produces slow circuits.

To formally verify an asynchronous circuit, various schemes are applied to mathematically prove that the circuit does not exhibit incorrect behaviour following any possible input sequence. Completely automated verification of a complete system is often computationally infeasible because of the state space explosion phenomenon. The designer must be able to produce such abstractions of the system that are small enough for automated verification but are still representative of the actual behaviour of the modelled system. In practice, many levels of abstractions may be required to adequately model and analyse the system in question.

For large projects, it is often a mixture of various formalisms, implementation techniques and verification methods that is used to produce the final design. There is no universally accepted design workflow for asynchronous systems. Despite the fact that a robust theoretical and technological kernel exists for the most of the individual tasks outlined above, a truly complete production pipeline, such that would cover all stages from specification to verification to mapping the net-list to silicon, is indeed very hard to set up. The fragmented state of the tool base is one of the reasons for that. There is not a package, either commercial or open-source, targeted at asynchronous circuit design, that could be compared to the complete synchronous design solutions provided by companies such as Synopsys, Cadence, or Mentor Graphics. Instead, there exists a multitude of standalone tools, coming mostly from academia, that target one particular task without much regard to interaction with other tools that may be doing tasks that precede or follow it in the design process. It is up to the designer to organise such an interaction, which may not be a trivial task; unless such an interaction is automated, it quickly becomes very cumbersome. In addition, the tools coming from the academic environment are mostly focused on solving the mathematical and algorithmic problems and rarely focus on the aspects of user interaction. The interfaces to those tools are mostly command-line- or file-based, which may be daunting even to an experienced user. The output often requires post-processing to become human readable.

The complexities in the asynchronous circuit design therefore exist not only on the purely computational level, but also on the level of organisation of the human-machine interaction during the design process. This concern is the main motivation behind this work.

The specific problems that will be addressed in this thesis are outlined below. They include the automation of specific tasks related to asynchronous circuit design, assisting in the organisation of interaction between existing tools, providing user friendly visual representation of various formal models and the results of their analysis using techniques such as interactive simulation and visualisation of violation traces.

#### **1.1.1** Automated verification of asynchronous circuits using Petri nets

The designs of relatively large circuits are often hierarchical and compositional. Individual blocks of such designs are built after their sub-blocks have been designed and validated. Appropriate forms of interface of the sub-blocks are required, in which the behavioural complexity of the internal implementation of sub-blocks is hidden behind a subset of interface signals. For example, one can abstract away from the timing conditions used inside the sub-blocks, thereby considering the system at the higher level of abstraction from the point of view of its delay-independent behaviour. Conversely, the design may assume a block to be operating in a delay-independent context but the actual internal behaviour of the implementation needs to be validated in terms of its freedom from hazards.

Compositional approach can be achieved in different ways depending on the modelling method used for verification. For example, in the context of Petri nets, a block with an implementation that satisfies its Petri net based specification can be represented in a complex design not by the Petri net model of its implementation but rather by the Petri net specification, which can be significantly more compact, thereby helping to reduce the complexity of analysis at the higher level.

Aside from good support for modularity, the choice of Petri nets as the verification back-end for asynchronous circuits is justified for several other reasons. A gate-level circuit implementation can be efficiently converted into a Petri net model. Once such a model is obtained, it is very flexible with respect to the methods that can be applied for analysis. For instance, it is possible to compose the Petri net model of a circuit with a Petri net model of its environment, with the model of another circuit, or even with a net generated from a totally different formalism to produce the model of the complete system. Alternatively, the net may be simplified using techniques such as dummy contraction [99] and serve as an environment specification for another model.

The flexibility also comes from the very rich tool base. There are a large number of tools that apply drastically different techniques for analysis (LoLA [101], MPSat [68], Petrify [41], etc.), which provides the possibility to choose the tool that copes best with the structure of the system in question. In addition to performance considerations, modern Petri net tools support the verification of non-standard property specifications which may be very helpful during the debugging of specific systems [66].

Finally, it is possible to interpret a Petri net violation trace in terms of the signal switching activity in the original circuit, which makes it easy to present the verification result to the designer visually and using the original gate-level model.

# **1.1.2** Modelling, simulation and automated verification of the data path of asynchronous circuits

The synthesis of asynchronous control path is well developed and supported by tools, e.g., Petrify [41] and MPSat [68]. The synthesis of asynchronous data path, on the other hand, has not been studied as thoroughly. Usually, a designer makes the whole data path either *bundled-data* (to achieve a smaller size of the circuit) or *dual-rail* (to get an average-case performance and greater robustness to delay variations). In both cases the conventional EDA tools, such as Cadence or Synopsis, are used to obtain the data path combinational logic. The synchronous nature of those tools does not allow exploiting the full potential of the asynchronous data path. For instance, early evaluation cannot be controlled and influenced at an early synthesis stage. Data encoding is forced to single-rail, which is the norm for synchronous designs, but results in redundancy when the obtained circuits are converted to dual-rail.