# Strained Si Heterojunction Bipolar Transistors

By Mouhsine Fjer, BSc, MSc

# A Thesis Submitted to the Faculty of Engineering for Degree of Doctor of Philosophy

School of Electrical, Electronic and Computer Engineering

Newcastle University, UK

# Acknowledgements

This thesis would not have been possible without the continuous support that I received from many people, whom I will always be indebted to. First and foremost I would like to thank God who gives me the opportunity to take this challenging task. I would dedicate special thanks to my parent who supported me throughout my life.

Special thanks to my first supervisor Professor Anthony O'Neill, with whom I have worked for the last four years, starting from my master and throughout my PhD. I extremely fortunate to have had the pleasure to work with such an insightful advisor, who not only served as an excellent mentor, but has never hesitated to share his wisdom regarding both technical and non-technical matters. I would like also to thank my second supervisor Dr Sarah H. Olsen for her useful Input.

I wish to thank Dr Stefan Persson and Dr Enrique Escobedo-Cousin for their valuable contribution in this work, especially in mask design, interpreting material characterisation results and modeling. My thanks are extended to Laboratory staff from the University of Warwick for providing the wafer with epitaxial grown layers. I am further grateful to Dr Bengt Gunnar Malm, Dr Mikael Östling, Dr Per-Erik Hellström and Yong-Bin Wang from Royal Institute of Technology (KTH), Stockholm for their input in the fabrication of these devices.

For financial support, I would like to thank ESPRC for supporting me during this long journey.

Finally, I would like to express my deepest gratitude to my wife, brother, Uncles and all of whom have supported me throughout this experience.

### **Abstract**

This dissertation addresses the world's first demonstration of strained Si Heterojunction Bipolar Transistors (sSi HBTs). The conventional SiGe Heterojunction Bipolar Transistor (SiGe HBT), which was introduced as a commercial product in 1999 (after its first demonstration in 1988), has become an established device for high-speed applications. This is due to its excellent RF performance and compatibility with CMOS processing. It has enabled siliconbased technology to penetrate the rapidly growing market for wide bandwidth and wireless telecommunications once reserved for more expensive III-V technologies. SiGe HBTs is realised by the pseudomorphic growth of SiGe on a Si substrate, which allows engineering of the base region to improve performance. In this way the base has a smaller energy band gap than the emitter, which increases the gain. The energy band gap of SiGe reduces with increasing Ge composition, but the maximum Ge composition is limited by the amount of strain that can be accommodated within a given base layer thickness. Therefore, a new innovation is necessary to overcome this limitation and meet the continuous demand for high speed devices. Growing the SiGe base layer over a relaxed SiGe layer (Strain Relaxed Buffer) can increase the amount of Ge that can be incorporated in the base, hence, increasing the device performance. In this thesis, experimental data is presented to demonstrate the realisation of sSi HBTs. The performance of this novel device has been also investigated and explained using TCAD tool.

# **Symbols**

A Cross-section of the junction

A\* Richardson's constant

a<sub>Si</sub> Lattice constant of Si

a<sub>SiGe</sub> Lattice constant of Si<sub>1-x</sub>Ge<sub>x</sub>

a<sub>Ge</sub> Lattice constant of Ge

E<sub>a</sub> Activation energy

BV<sub>CEO</sub> Collector-emitter breakdown voltage at open base

BV<sub>CBO</sub> Collector-base breakdown voltage at open base

**β** Current gain

C Capacitance

C<sub>i</sub> Impurity concentration

C<sub>jc</sub> Base-collector depletion capacitance

D<sub>0</sub> Diffusion coefficient

D<sub>n</sub> Electron diffusivity

D<sub>p</sub> Hole diffusivity

D<sub>nb</sub> Electron diffusivity in the base

D<sub>pe</sub> Hole diffusivity in the emitter

D1 Distance to the collector

Distance to the base

$\Delta E_{gB}$  Reduction of the ban-gap of the base due to the presence of Ge

**ΔE**<sub>G</sub> Band-gap difference

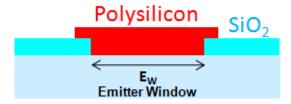

Band -gap narrowing caused by doping  $\Delta E_{G,H}$ **Conduction band discontinuity**  $\Delta E_{C}$ Valence band discontinuity  $\Delta E_V$ δ **Tunnelling coefficient** Fermi level  $E_{F}$ Electron quasi Fermi level  $E_{Fn}$ Hole quasi Fermi level  $E_{Fp}$  $\mathsf{E}_\mathsf{g}$ Band-gap Intrinsic Fermi level  $E_{i}$  $E_n$ **Electric field vectors Electric field vectors** Ep **Emitter window width**  $E_{W}$ ε **Electric field** f Frequency  $f_{C}$ **Corner frequency**  $f_{\mathsf{T}}$ **Cut-off frequency** Maximum oscillation of frequency  $f_{max}$ ħ **Reduced Planck's constant** Base current  $I_B$ **Collector current** Ic **Electron diffusion current** l<sub>n</sub> **Hole diffusion current**  $I_p$ Thermal generation current  $I_{R-G}$ J Net flux of the impurity material

**Collector current density**  $J_{C}$ **Electrons current density** Jn **Holes electron dnsity** Jp **Boltzmann's constant** k Κ Constant **Electron affinity** χ L Length **Hole diffusion length**  $L_{P}$ λ Thermal conductivity **Ideality factor** m **Electron mass**  $m_e$ **Electron mobility**  $\mu_{\mathsf{n}}$ Hole mobility  $\mu_{\mathsf{p}}$ **Emitter transit time**  $\tau_{\mathsf{E}}$ N region Region that is doped with donors impurity Acceptor concentration in the base  $N_a$  $N_a^-$ **Uncompensated acceptors**  $N_d^+$ **Uncompensated donor ions** Nab Base doping Density of state in the conduction band in the base layer  $N_{CB}$ Density of state in the valence band in the base layer  $N_{VB}$  $N_E$ **Emitter doping concentration**

Intrinsic carrier concentration

Intrinsic carrier concentration in the base region

ni

$n_{iB}$

$\mathbf{n}_{iE}$  Intrinsic carrier concentration in the emitter region.

n<sub>p</sub> Electron concentration in the P region

n<sub>ie</sub> Intrinsic carrier concentration at high doping level

n Electron concentration

N<sub>deff</sub> Effective doping concentration in the emitter

p Hole concentration

P region Region that is doped with acceptor impurity

p<sub>n</sub> Hole concentration in the N region

p<sub>p</sub> Hole concentration in the P region

Ps Power consumption

q Electronic charge

R Resistance

r<sub>B</sub> Base resistance

r<sub>be</sub> Base-emitter resistance

R<sub>th</sub> Thermal resistance

S<sub>IB</sub> spectral power density of the base current noise source

S<sub>IC</sub> spectral noise density of the collector current noise source

S<sub>ø</sub> Phase noise

T Temperature

T<sub>O</sub> Ambient temperature

τ Characteristic time constant of Lorentzian spectrum 1/f<sup>2</sup>

$\tau_n$  Electron life time

$\tau_p$  Hole life time

$\tau_B$  Base transit time

$U_{Auger}$  Auger recombination rate

U<sub>SRH</sub> Shockley-Read-Hall recombination rate

U<sub>n</sub> Electron recombination rates

U<sub>p</sub> Hole recombination rates

V Voltage

$V_{BE}$  Base-emitter voltage

v<sub>eff</sub> Saturation velocity

$v_n$  Mean electron thermal velocity

$v_p$  Mean hole thermal velocity

W<sub>p</sub> Width of the P region

W<sub>n</sub> Width of the N region

W Depletion layer width

W<sub>E</sub> Emitter width region

W<sub>B</sub> Base width region

W<sub>M</sub> Mesa length

# **Contents**

| Acknowledgements                                              | i    |

|---------------------------------------------------------------|------|

| Abstract                                                      | ii   |

| Symbols                                                       | iii  |

| Contents                                                      | viii |

| Chapter 1. Introduction                                       | 1    |

| 1.1 Introduction                                              | 1    |

| 1.2 History and development of Si bipolar junction transistor | 1    |

| 1.3 Impact of SiGe material on semiconductor technology       | 4    |

| 1.4 Project motivation                                        | 5    |

| 1.5 Conclusion                                                | 7    |

| 1.6 Reference                                                 | 8    |

| Chapter 2. Background                                         | 9    |

| 2.1 Introduction                                              | 9    |

| 2.2 PN junction                                               | 9    |

| 2.3 Basic operation of the Si BJTs                            | 15   |

| 2.4 Current gain                                              | 19   |

| 2.5 Epitaxial growth of silicon-germanium material            | 22   |

| 2.6 Band gap structure of the Si/SiGe structure               | 25   |

| 2.7 Dopant diffusion in SiGe                                  | 30   |

| 2.8 Performance of SiGe HBTs                                  | 34   |

| 2.9 BiCMOS technology using VS HBT                            | 36   |

| 2.10 Conclusion                                               | 39   |

| 2.11 Reference                                                | 40   |

| Chapter 3. Electrical & material characterisation of sSi HBTs | 43 |

|---------------------------------------------------------------|----|

| 3.1 Introduction                                              | 43 |

| 3.2 Collector layer design                                    | 44 |

| 3.3 Base layer design                                         | 45 |

| 3.4 Emitter layer design                                      | 45 |

| 3.5 Strain-relaxed buffer                                     | 46 |

| 3.6 Fabrication process steps                                 | 47 |

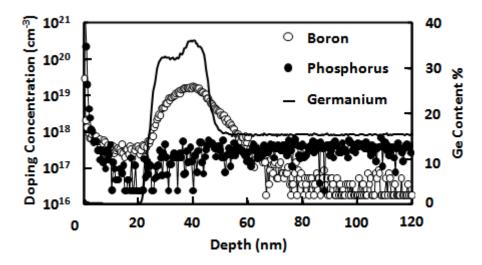

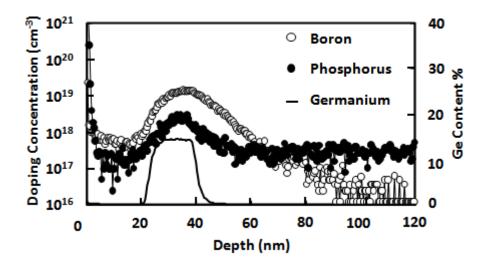

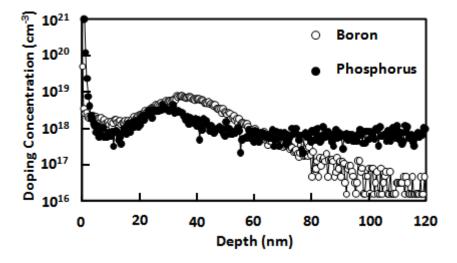

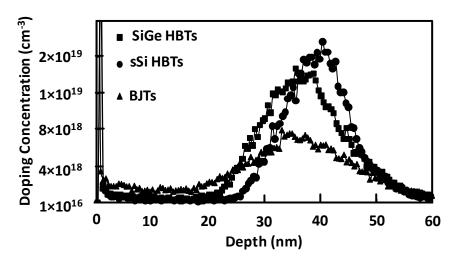

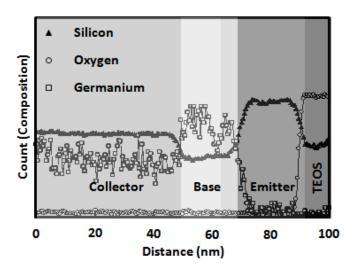

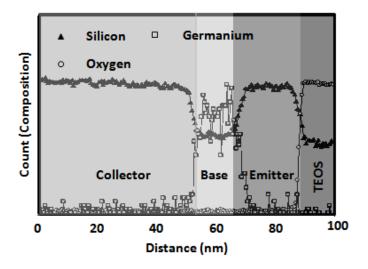

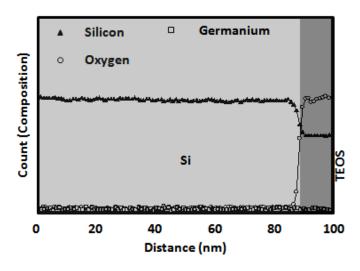

| 3.7 Material characterisation                                 | 49 |

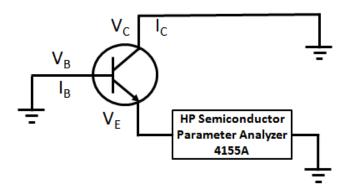

| 3.8 Characterization methods                                  | 54 |

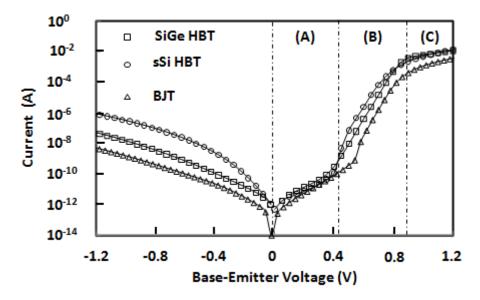

| 3.9 Gummel plot                                               | 55 |

| 3.10 Current gain                                             | 58 |

| 3.11 Ideality Factor                                          | 59 |

| 3.12 Emitter-base diode                                       | 60 |

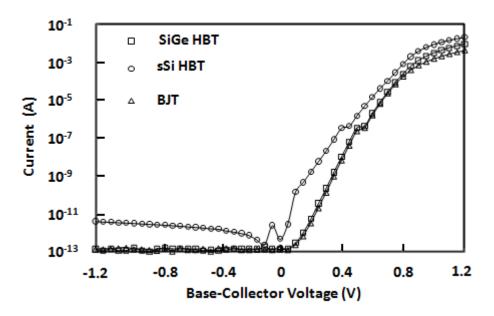

| 3.13 Collector base diode                                     | 62 |

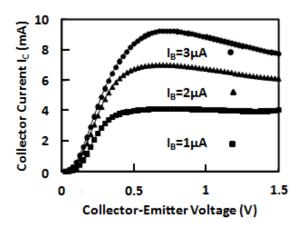

| 3.14 Common emitter characteristic                            | 62 |

| 3.15 Break down voltage                                       | 64 |

| 3.16 Impact of parameter design space                         | 67 |

| 3.17 Benefit of sSi HBT structure                             | 70 |

| 3.18 Deviation in the electric performance                    | 71 |

| 3.19 Conclusion                                               | 75 |

| 3.20 Reference                                                | 77 |

| Chapter 4. 2D simulation study of sSi HBTs                    | 81 |

| 4.1 Introduction                                              | 81 |

| 4.2 Physical model                                            | 82 |

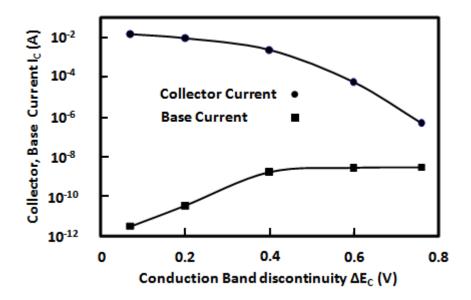

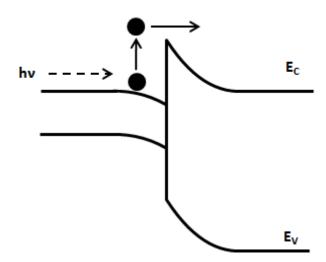

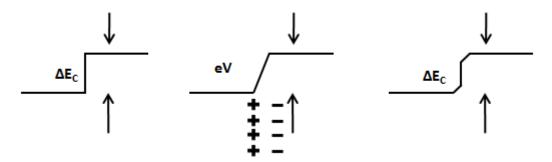

| 4.3 Impact of band-gap discontinuity                          | 84 |

| 4.4 Impact of the Polysilicon emitter                  | 87  |

|--------------------------------------------------------|-----|

| 4.5 Impact of Recombination                            | 89  |

| 4.6 Ge Profile and SIMS profile                        | 93  |

| 4.7 Self-heating                                       | 96  |

| 4.8 Limitation of the Si/SiGe system                   | 100 |

| 4.9 Ge/GaAs heterostructure system                     | 102 |

| 4.10 Conclusion                                        | 109 |

| 4.11 Reference                                         | 111 |

| Chapter 5. Low Frequency Noise in sSi HBTs             | 114 |

| 5.1 Introduction                                       | 114 |

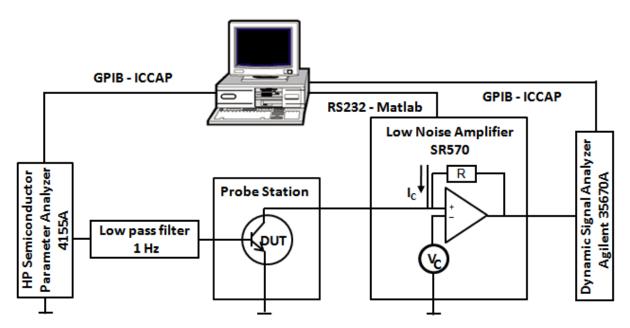

| 5.2 Measurement set-up                                 | 115 |

| 5.3 The base current dependence of low frequency noise | 121 |

| 5.4 Implication for circuit applications               | 128 |

| 5.5 Defect characterisation                            | 131 |

| 5.6 Generation-recombination noise                     | 134 |

| 5.7 Impact of processing on low frequency noise        | 136 |

| 5.8 Conclusion                                         | 140 |

| 5.9 Reference                                          | 142 |

| Chapter 6. Summary & Future work                       | 146 |

| 6.1 Summary                                            | 146 |

| 6.2 Future work                                        | 147 |

| Appendix                                               | 149 |

# **Chapter 1. Introduction**

### 1.1 Introduction

The transistor was probably the most important invention of the 20th Century. It is the key element of any integrated circuit. This device can operate as switch or amplify a signal. The transistor is considered as a perfect alternative to the vacuum tube, since it is small and consumes low energy compared to the vacuum tube. Since the first fabrication of the transistor, there have been an enormous number of developments in the design and the fabrication techniques.

Given the recent development and need in the communication market, the bipolar transistor, which is Si based, may not be able to meet the increasing demand for high speed devices. This has opened the door widely to the integration of the SiGe into bipolar technology, leading to the fabrication of Silicon Germanium (SiGe) heterojunction bipolar transistors (HBTs). This device exhibits high performance compared to Si bipolar junction transistors (BJTs). However, a continuous improvement of the SiGe HBT's performance required an increase of the Ge content in the base. This is not possible, since the amount of the Ge that can be used in SiGe HBTs is limited by the magnitude of the strain that can be accommodated within the base region. Using a Strain Relaxed Buffer (relaxed SiGe) as a virtual substrate (in place of Si) can allow more Ge to be introduced in the base layer.

### 1.2 History and development of Si bipolar junction transistor

The transistor is a three terminal, solid state electronic device. In a three terminal device we can control electric current or voltage between two of the terminals by applying an electric current or voltage to the third terminal. The transistor was not the first three terminal device. The vacuum tube triode preceded the transistor by nearly 50 years. They played an important role in the emergence of home electronics and in the scientific discoveries and technical innovations which are the foundation for our modern electronic technology. The vacuum tube triode also helped push the development of computers. They were used in several different computer designs in the late 1940's and early 1950's (In the late 1940's, big computers were built with over 10,000 vacuum tubes and occupied over 93 square meters

of space). But the limits of these tubes were soon reached. As the electric circuits became more complicated, one needed more and more triodes. Engineers packed several triodes into one vacuum tube to make the tube circuits more efficient. The vacuum tubes tended to leak, and the metal that emitted electrons in the vacuum tubes burned out. The tubes also required so much power that big and complicated circuits were too large and the energy consumption rate was high. The problems with vacuum tubes lead scientists and engineers to think of other ways to make three terminal devices. Instead of using electrons in vacuum, scientists began to consider how one might control electrons in solid materials, like metals and semiconductors.

In 1947, scientists working at Bell Telephone Laboratories were trying to understand the nature of electrons at the interface between a metal and a semiconductor (Germanium). They realized that by making two point contacts very close to one another, they could make a three terminal device - the first "point contact" transistor [1]. Although the first fabricated transistor was made using Ge, we actually live in silicon world. Greater than 95% of the semiconductor market uses the semiconductor Silicon (Si). This profound market dominance of Si rests on a number of surprisingly practical advantages that Si has over the other numerous semiconductors, including [2]:

- An extremely high quality dielectric (SiO<sub>2</sub>) can be grown on Si and used for isolation, passivation, or as an active layer (e.g., gate oxide).

- Si can be grown in very large, low defect single crystals, yielding many (low-cost) IC's per wafer.

- Si has good thermal properties allowing for the efficient removal of dissipated heat.

- Si can be controllably doped with both N and P type impurities.

- Si has excellent mechanical strength, facilitating ease of handling and fabrication.

- It is easy to make very low-resistance ohmic contacts to Si, thus minimizing device parasitic.

- Si is extremely abundant and easily purified.

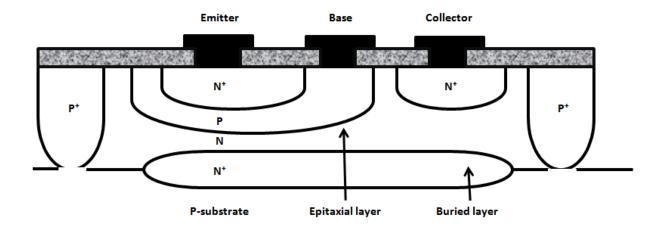

Since the fabrication of the first Si bipolar junction transistor, there have a large number of innovations and break-throughs. Bipolar junction transistors were typically formed as follows (assuming an NPN device). A patterned N subcollector is first formed on a P-type

silicon wafer by diffusion. An N-type epitaxy layer is then grown on top. A P-type pocket for the base region is then formed by diffusion. This is followed by the formation of an N-type emitter. The P-type region directly underneath the emitter forms the intrinsic base, while the remainder of the P-type pocket forms the extrinsic base as shown in Figure 1.

Figure 1: Cross-sectional view of a basic planar bipolar transistor

Typical emitter junction depth is about 500 nm, and typical intrinsic base width is about 250 nm [3]. The emitter and base region that are formed by the diffusion technique tend to be very wide, which slows down the device. However, the ion-implantation technique has allowed the production of narrow base and emitter regions [4]. Another development is the ability to grow a thin, heavily doped Si crystal epitaxially. High doping level means introducing more carriers which reduce of the base resistance and also the collector series resistance. The electrical isolation of the bipolar has also been subjected to some development. In the early stage, the device was junction-isolated using a P-type region. This region tends to be very large because the impurity diffuses laterally. For the isolation to be effective, the P-type region must completely surround the device. In addition, the isolation junction must be reversed biased by connecting the P-substrate to the most negative voltage in the circuit. Instead of using this method, which results in large isolation area, designers nowadays tend to use deep trench isolation. This method reduces the isolation area. The deep trenches are formed by first etching silicon trenches which are filled the trenches with oxide or a combination of oxide and polysilicon, followed by planarization using chemical-mechanical polishing [5].

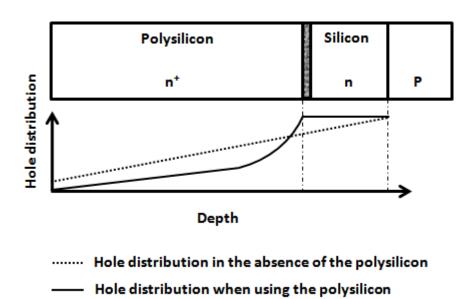

The next stage of the evolution of Si bipolar transistor was the integration of the polysilicon emitter. The early experiments treated the heavily doped N-polysilicon as a metal. Perhaps the most exciting finding of these experiments was that the N polysilicon contacts to Si did not behave like ohmic contacts at all. Minority holes injected from the base into the shallow N type emitter, instead of recombining at the polysilicon-silicon interface, as expected for an ohmic contact, recombine primarily inside the N polysilicon layer, leading to significant increase in current gain [6]. The use of polysilicon was not limited to the emitter; P-type polysilicon is also used between the intrinsic base and the base contact. This actually reduces the extrinsic base area, therefore reducing the parasitic capacitance. However, this may cause an increase of the base resistance [7].

### 1.3 Impact of SiGe material on semiconductor technology

While silicon dominates in mainstream integrated circuit microelectronics, there are areas of analogue electronics, especially in high frequency applications, that have allowed GaAs, InP and other materials to dominate smaller niche markets such as radio frequency and power amplifiers [2]. If the performance of Si transistors or circuits could be improved by the addition of another semiconductor material then numerous new applications could be opened up. Silicon Germanium (SiGe) is one such material which may be epitaxially grown on silicon wafers and allows engineering of the bandgap, energy band structure, effective masses, density of state and mobilities while fabricating circuits using conventional Si processing tools [1]. SiGe has moved from being a research material to an important material that is used in the manufacturing of different semiconductor devices. A thin SiGe layer grown as the base of a bipolar transistor on a Si wafer leads to the fabrication of devices known as SiGe HBTs. The performance can be greatly improved over a normal Si bipolar junction transistor because the base can be doped to larger densities which reduces the resistivity of the base and hence the RC time constant for switching. The reduced base resistance is also important for reducing noise in the transistors, an important parameter in analogue and RF applications [8]. It is also important to mention that grading the Ge content in the base then builds an electric field into the device, which accelerates the carriers across the base and therefore increases the speed of the transistor [9]. The reduced bandgap of the base also leads to an increase in the gain of the transistor, as the minority carrier concentration is inversely proportional to the band gap.

The use of SiGe is widespread in CMOS technology. The continuous development of CMOS technology was achieved by shrinking the device dimensions. However this approach has also turned out to be increasingly difficult. Therefore considering other techniques, such as improving the carrier mobility becomes important. On any CMOS chip with both P and N type transistors, the major limitation in the performance is the PMOSFETs. The mobility and effective mass of holes is much worse than the mobility and effective mass of electrons in Si. To balance the current drive in CMOS circuit design, the N and P transistors have to be sized and this greatly reduces the circuit performance. The limitation caused by the low mobility of the holes in the Si can be mitigated using SiGe in the source and drain to compress the silicon channel [10]. Since The hole mobility in this latter is known to be high compared to unstrained Si. Tensile strained silicon improves electron mobility and is used in NMOSFETs. Strained Si is considered as one of the leading techniques for improving the mobility of carriers and therefore enhancing the performance of MOSFETs.

### 1.4 Project motivation

Bipolar technology has been subjected to a large number of innovations in recent decades. One of the most significant break throughs, which has allowed a continuous improvement of the bipolar transistor, is the implantation and epitaxial techniques that allow the fabrication of a thin base layer. Another development is the implementation of the polysilicon emitter, which blocks the diffusion of minority carriers in the emitter, therefore increasing the current gain. However, these successive achievements may not be sufficient to meet the continuous demand of high speed devices.

The recent improvement of epitaxial growth techniques has lead to the fabrication of SiGe HBTs. This device is formed using a thin SiGe layer in the base region instead of Si, which is found in Si bipolar transistors. The small band-gap of SiGe results in an exponential increase of the minority carrier concentration in the base and therefore the collector current. The profile of the Ge concentration in the base can be constant. However it is also possible to be linear, leading to the formation of triangular or trapezoidal profiles. These profiles give rise to a drift field in the base region which aids the minority carrier transport through the base, therefore increasing the speed of the device. Many papers report that the performance of the SiGe HBT is proportional to the Ge content in the base; however increasing the amount

of the Ge is not an endless process. The grown layer of SiGe on Si substrate is under strain. An increase of the Ge content raises the amount of strain in the SiGe. The final result would be the formation of defects and relaxation of the SiGe layer. If these defects are in the active region of the wafer where the transistors are fabricated, they will often lead to a device failure. This is a clear barrier toward the improvement of SiGe HBTs.

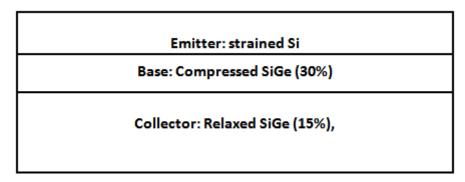

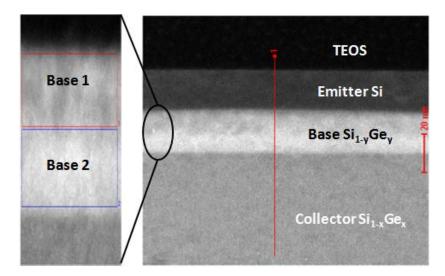

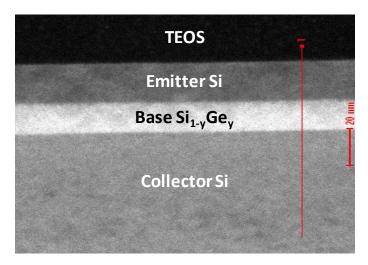

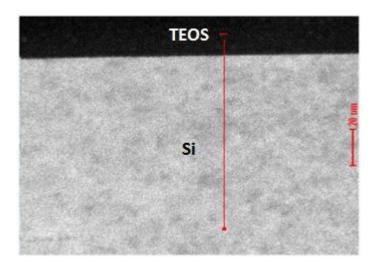

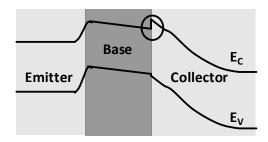

In order to improve the performance of SiGe HBTs, it is important to increase the Ge content in the base, while keeping the strain below a certain critical level. This can be achieved using a SiGe Strain Relaxed Buffer as a virtual substrate. In this case, the difference of the lattice constant between the base and collector is small which reduces the strain in the base. Therefore, the structure of the new device is as follows: relaxed SiGe in the collector compressed SiGe in the base and strained Si in the emitter. This device is called a strained Si HBT (sSi HBTs), Figure 2.

Figure 2: different layer forming sSi HBTs, The Ge composition values given here are indicative for a typical device.

The Strain Relaxed Buffer (SRB) has also been used in the fabrication of strained Si MOSFETs[11]. Current BiCMOS technology consists of the integration of SiGe HBTs and conventional MOSFETs. Using relaxed SiGe virtual substrates in the fabrication of sSi HBTs has raised the possibility of the integration of strained Si MOSFETs and sSi HBTs in one chip.

The dissertation is broken up into four sections:

- The basic equations that govern the operation of Si BJTs are developed. The impact

of the implementation of SiGe into bipolar technology is also presented along with

the properties of SiGe material.

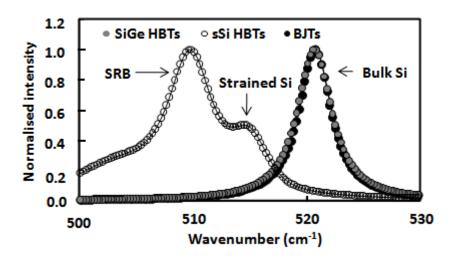

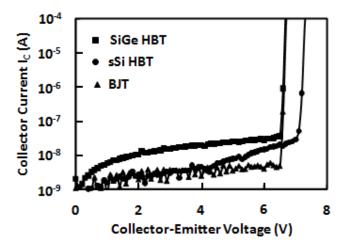

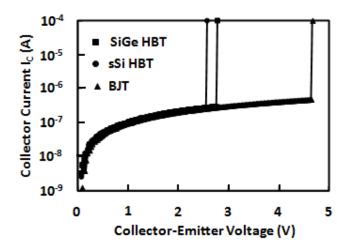

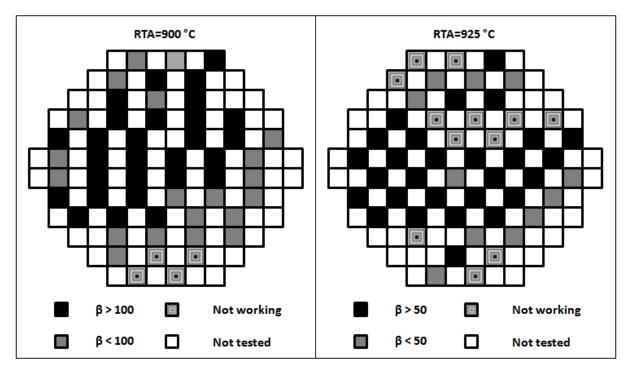

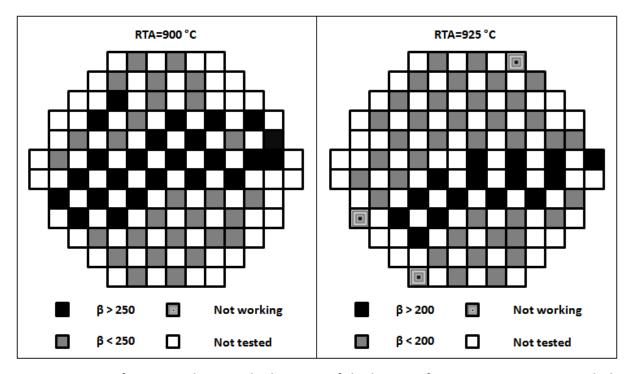

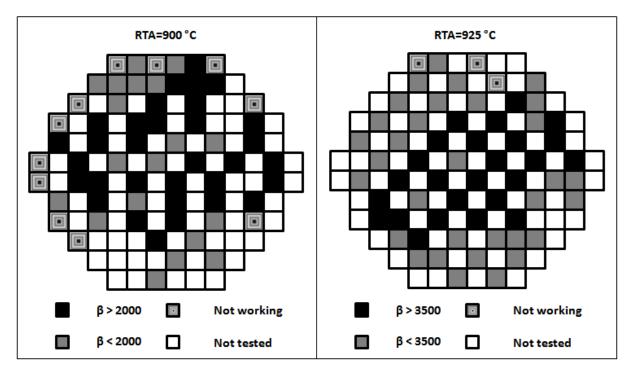

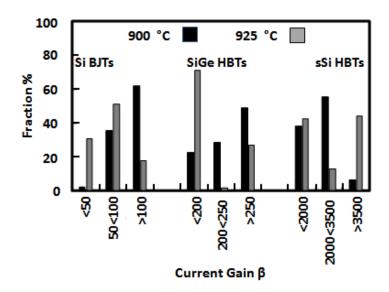

- Several experimental data (SIMS, TEM image, EELS and the Raman spectroscopy) are presented to confirm the fabrication of sSi HBTs. The Si BJTs, SiGe HBTs and sSi HBTs

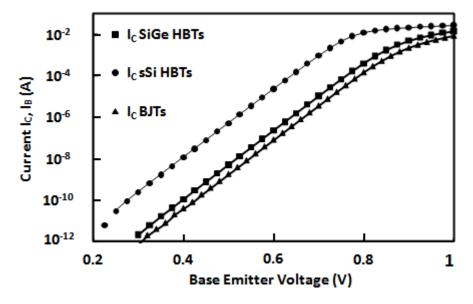

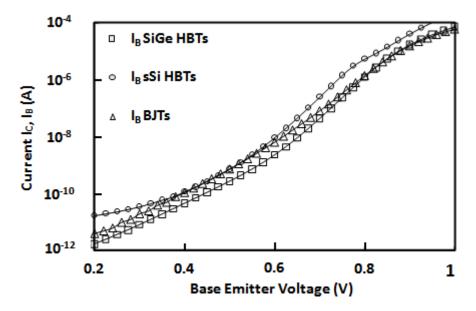

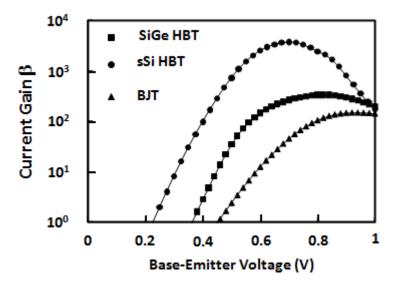

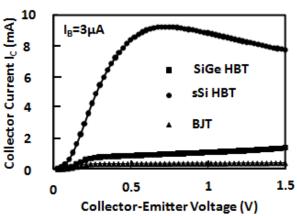

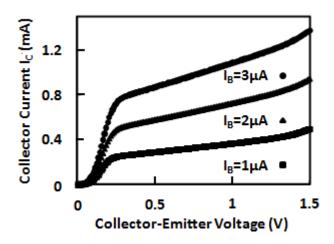

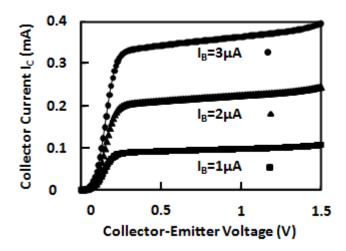

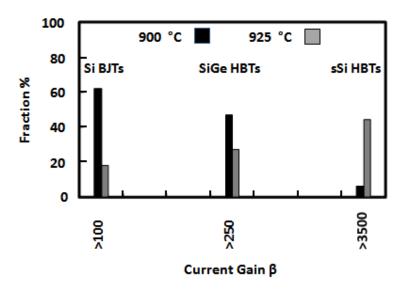

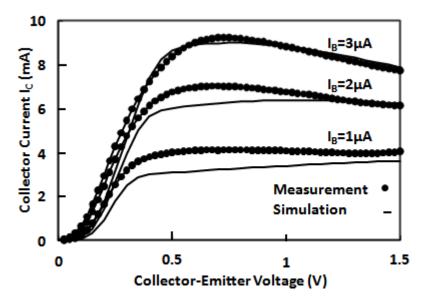

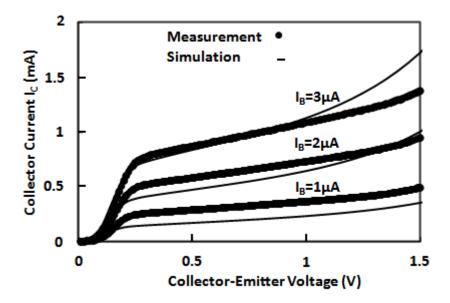

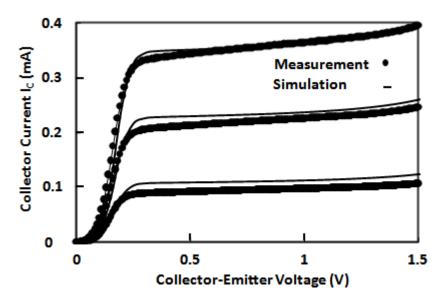

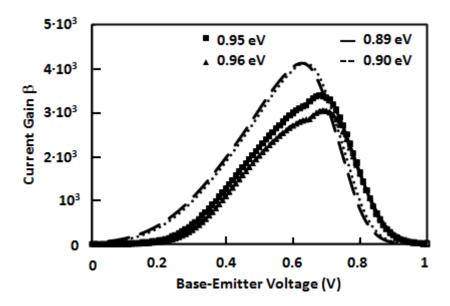

are compared in term of current gain. This comparison shows that this novel device exhibits a maximum current gain of 3700 compared with 334 for co-processed SiGe HBTs and 135 for Si BJTs. The common emitter characteristic has also shown that sSi HBTs suffers from the self heating.

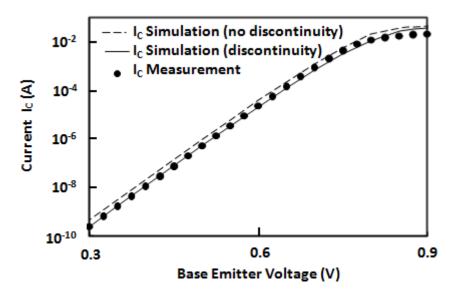

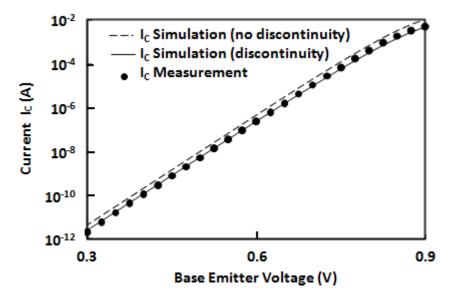

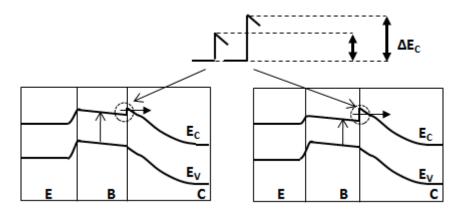

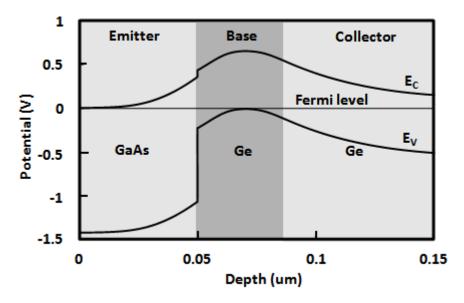

- 2D simulation of Si BJTs, SiGe HBTs and sSi HBTs is presented. MEDICI from Synopsys is used due its ability to consider the impact of the Ge content on the material properties and therefore on the device performance. An agreement between the experimental data and the simulation results is reported. This confirms that the band gap of the base layer is the main factor that causes the high performance of sSi HBTs. An investigation of the performance of HBTs based on Ge and GaAs is also reported showing that this device might have a good current gain. However the band discontinuity and more precisely the valence band discontinuity blocks this device from reaching its full potential.

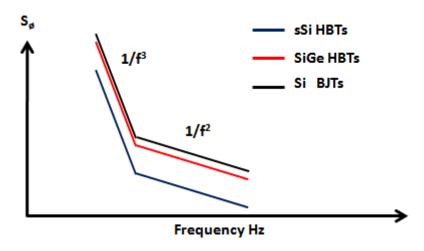

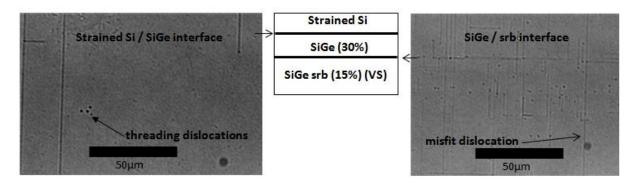

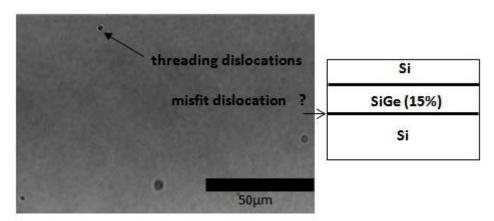

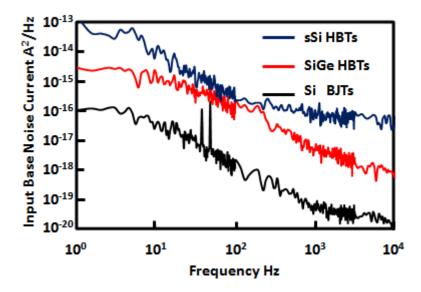

- The first comparison study of low frequency noise between sSi HBTs, SiGe HBTs, and Si BJTs is presented. This has shown that sSi HBTs exhibit higher low-frequency noise compared to control devices at fixed base current. The presence of a high concentration of defects that are caused by the strain-relaxed buffer is responsible for the low-noise performance of sSi HBTs. However, it is shown that this novel device demonstrates the lowest noise level (better noise performance) for the same collector current compared with the other control bipolar devices. The noise level in a circuit can therefore be reduced by using sSi HBTs as compared with either Si BJTs or SiGe HBTs. This results the high current gain of these devices. A relationship between low frequency noise and defects is shown by material characterization.

### 1.5 Conclusion

This chapter presents a summary of the development of bipolar technology. The performance of Si BJTs has improved significantly as a consequence of using novel designs and fabrication methods such as implantation and epitaxy. This chapter has also discussed the impact of SiGe on the bipolar transistor and also on CMOS technology. The limited amount of strain that can be accommodated in the SiGe base layer is seen as a real barrier to enhance the performance of HBTs. The SRB that is used as a substrate in the fabrication of strained Si MOSFETs is seen as a possible solution to the limitation of SiGe HBTs.

### 1.6 Reference

- [1] "Available at: www.nobelprize.org."

- [2] J. D. Cressler, "SiGe HBT technology: A new contender for Si-based RF and microwave circuit applications," *leee Transactions on Microwave Theory and Techniques*, vol. 46, pp. 572-589, 1998.

- [3] T. H. Ning, "History and future perspective of the modern silicon bipolar transistor," *IEEE Transactions on Electron Devices*, vol. 48, pp. 2485-2491, 2001.

- [4] P. Ashburn, SiGe Heterojunction Bipolar Transistors: John Wiley & Sons, ltd, 2003.

- [5] T. Vanhoucke and G. A. A. Hurkx, "A new analytical model for the thermal resistance of deep-trench bipolar transistors," *leee Transactions on Electron Devices,* vol. 53, pp. 1379-1388, 2006.

- [6] A. Zouari and A. Ben Arab, "Analytical Model and Current Gain Enhancement of Polysilicon-Emitter Contact Bipolar Transistors," *IEEE Transactions on Electron Devices*, vol. 55, pp. 3214-3220, 2008.

- [7] P. Pengpad and D. M. Bagnall, "Double-polysilicon self-aligned lateral bipolar transistors," *Journal of Materials Science-Materials in Electronics*, vol. 19, pp. 183-187, 2008.

- [8] H. A. W. Markus, P. Roche, and T. G. M. Kleinpenning, "On the 1/f noise in polysilicon emitter bipolar transistors: Coherence between base current noise and emitter series resistance noise," *Solid-State Electronics*, vol. 41, pp. 441-445, 1997.

- [9] G. Khanduri and B. Panwar, "An iteration approach for base doping optimization to minimize the base transit time in triangular-Ge-profile SiGeHBTs," *Solid-State Electronics*, vol. 51, pp. 961-964, 2007.

- [10] S. E. A. Thompson, M.; Auth, C.; Alavi, M.; Buehler, M.; Chau, R.; Cea, S.; Ghani, T.; Glass, G.; Hoffman, T.; Jan, C.-H.; Kenyon, C.; Klaus, J.; Kuhn, K.; Zhiyong Ma; Mcintyre, B.; Mistry, K.; Murthy, A.; Obradovic, B.; Nagisetty, R.; Phi Nguyen; Sivakumar, S.; Shaheed, R.; Shifren, L.; Tufts, B.; Tyagi, S.; Bohr, M.; El-Mansy, Y., "A 90-nm logic technology featuring strained-silicon " *IEEE Transactions on Electron Devices*, vol. 51, pp. 1790-1797, 2004.

- [11] O. M. Alatise, K. S. K. Kwa, S. H. Olsen, and A. G. O'Neill, "Improved Analog Performance in Strained-Si MOSFETs Using the Thickness of the Silicon-Germanium Strain-Relaxed Buffer as a Design Parameter," *IEEE Transactions on Electron Devices*, vol. 56, pp. 3041-3048, 2009.

# Chapter 2. Background

### 2.1 Introduction

Most semiconductor devices contain at least one PN junction. This junction is fundamental to the performance of functions such as rectification, amplification, switching and other operations in electronic circuits. Two physical phenomena are responsible for the flow of the current in the PN junction, drift and diffusion. Determining the basic equation that governs this junction is the first step to understand the operation of bipolar transistors.

The current gain and the cut-off frequency are the main parameters used to characterise the bipolar transistor. While the first parameter is viewed as the factor that reflects the DC performance of the device, the second characterises the speed of the device. The doping level in the emitter, base and collector in addition to the width of these regions represent the parameter design space that is used to enhance the device performance. However, increasing both the DC and AC performance leads to a conflict of parameter design space requirement. For instance, low base doping increases the current gain, however this results in a reduction of the base resistance and by consequence the cut-off frequency. This means that Si BJTs may not able to meet the continuous demand of high speed devices for the communication market. This has opened the door to the use new innovation methods to improve the performance of Si BJTs. The incorporation of SiGe in the fabrication of the bipolar transistor has lead to a new device known as the SiGe heterojunction bipolar transistors. This latter device has shown high DC and AC performance over Si BJTs. The impact of SiGe is not restricted to bipolar transistors. Indeed it improves the performance of MOSFETs and BiCMOS technology as well.

### 2.2 PN junction

A bipolar transistor is simply two back-to-back PN junctions. Hence it is important to study the electrical characteristic of this junction. One useful feature of the PN junction is that the current can only flow quite freely from the P to N direction when the P region has a relatively positive external voltage relative to N. This asymmetry of the current flow makes the PN junction very useful as a rectifier. When N and P region are brought together to

form the PN junction, diffusion of carriers takes place because of large carrier concentration gradients at the junction. Thus holes diffuse from the P side into the N side, and electrons from the N side into the P side as seen in Figure 2.1.

Figure 2.1: Separate P and N region and the direction of hole and electron diffusion current.

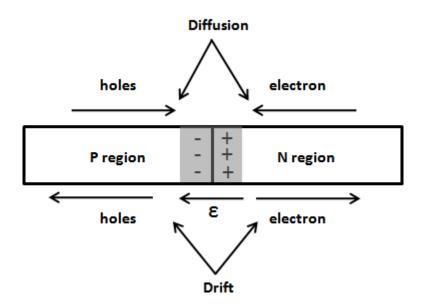

The resulting diffusion current cannot build up indefinitely, however, because an opposing electric field is created at the junction. Consider that electrons diffusing from N to P leave behind uncompensated donor ions  $N_d^+$  in the N material, and holes leaving the P region leave behind uncompensated acceptors  $N_a^-$ , it is easy to visualise the development of a region of positive space charge near the N side of the junction and negative charge in the P side. The resulting electric field  $\varepsilon$  is directed from the positive charge toward the negative charge. Thus  $\varepsilon$  is in the direction opposite to that of diffusion current for each type of carrier. Therefore, the field creates a drift component of current from N to P, opposing the diffusion current. Figure 2.2 illustrates a PN junction with the neutral regions of P type and N type material and also the depletion region (space charge).

The equilibrium state of the PN junction can be disturbed when applying an external voltage to it. There are two distinctive biasing conditions: one is the forward bias and the other is the reverse bias. In the first case the minority carriers are injected into P and N region. The injected carriers are supplied by the reservoir of the majority carriers, which in turn are supplied by the external voltage source. In the reverse biased case, the minority carriers are extracted from P and N region due to the enhanced electric field, leading to a small current. This current is reduces as the reverse biased is increases.

However, a very small reverse current does flow. This reverse saturation current depends only on the thermal generation of holes and electrons near the junction. This reverse saturation current is quite small but it increases with increasing temperature.

Figure 2.2: PN junction, direction of the hole and electron current (drift and diffusion)

The density of charge carriers is characterised by the Fermi level  $E_F$ . A change of the Fermi level, e.g. towards the conduction band, causes electron density to increase and hole density to decrease. Equation (2.1) and (2.2) represents the electron and hole density, respectively.

$$n = n_i \exp\left[\frac{(E_{Fn} - E_i)}{kT}\right]$$

(2.1)

$$p = n_i \exp \left[ \frac{(E_i - E_{Fp})}{kT} \right]$$

(2.2)

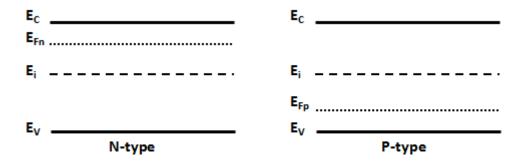

Where  $n_i$  is the intrinsic carrier concentration,  $E_i$  is the intrinsic Fermi level,  $E_{Fn}$  and  $E_{Fp}$  is the electron and hole quasi Fermi level, respectively. Figure 2.3 illustrate the band structure of P and N-type doped semiconductor.

Figure 2.3: Band structure of P and N-type doped semiconductor.

The product of equation (2.1) and (2.2) equation leads to equation (2.3) of the product pn

$$pn = n_i^2 \exp \left[ \frac{(E_{Fn} - E_{Fp})}{kT} \right]$$

(2.3)

Applying this product to the edges of the depletion region (at the position  $X_n$  and  $X_p$ ) leads to the following equations.

$$p_n(X_n)n_n(X_n) = p_p(X_p)n_p(X_p) = n_i^2 \exp\left(\frac{qV}{kT}\right)$$

(2.4)

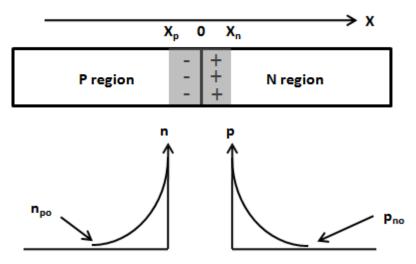

Where V is the voltage across the PN junction, q is the electronic charge,  $p_n$  and  $n_n$  are the hole and electron concentration in the N region, respectively. While  $n_p$ ,  $p_p$  are the electron concentration in the P region, respectively. It is important to mention that this product increases at forward. Figure 2.4 illustrates minority carrier distributions on the two sides of the PN junction for forward bias.

Figure 2.4: Distribution of the minority carrier under forward bias

The minority carrier concentration at the edge of the depletion region is higher than at equilibrium. For low injection of minority carries we can neglect changes in the majority carrier concentrations. Therefore it is possible to write:

$$n_n(X_n) = n_{no} \tag{2.5}$$

where,  $n_{no}$  is the electron concentration in the N region (at equilibrium). Similarly:

$$p_{p}(X_{p}) = p_{po} \tag{2.6}$$

Where,  $p_{po}$  in the hole concentration in the P region (at equilibrium).

At equilibrium (No external voltage), equation (2.4) can be written as follow

$$p_{no}n_{no} = p_{po}n_{po} = n_i^2$$

(2.7)

Where,  $p_{no}$  is the hole and electron concentration in the N region (at equilibrium) and  $n_{po}$  is the electron concentration in the P region (at equilibrium).

By considering equation (2.4), (2.5) and (2.7), it is possible to develop an equation for the electron concentration in the P region at the position  $X_p$  as follows:

$$n_{p}(X_{p}) = n_{po} \exp\left(\frac{qV}{kT}\right)$$

(2.8)

Similarly, using equation (2.4), (2.6) and (2.7) the hole concentration in the N region at the position  $X_n$  is given by the following equation.

$$p_{n}(X_{n}) = p_{no} \exp\left(\frac{qV}{kT}\right)$$

(2.9)

It is important to mention that equation (2.8) and (2.9) are developed under certain assumptions. The externally applied voltage appears totally across the immediate junction, therefore all parasitic resistances and associated voltage drops due to the current flow were assumed to be negligible. Moreover, the generation recombination phenomenon is considered negligible.

The majority carrier current from one side of the PN junction is the minority carrier current on the other side of the junction. The total current flow can therefore be found by simply adding the two minority diffusion currents:

$$I = I_n + I_n \tag{2.10}$$

Where  $I_n$  is the electron diffusion current and  $I_p$  is the hole diffusion current. Since the current is caused by the diffusion of the carriers, therefore the total current can be written as follow.

$$I = -qAD_{p}\frac{dp_{n}}{dx} + qAD_{n}\frac{dn_{p}}{dx}$$

(2.11)

Where q is the electronic charge, A is the cross-section of the junction,  $D_p$  and  $D_n$  are the hole and electron diffusivity, respectively. Taking in consideration the gradients from Figure 2.4 and substituting equation (2.8) and (2.9) into equation (2.11) gives the current voltage relationship of the PN junction.

$$I = qAD_{p} \frac{p_{no}}{W_{n}} \left[ exp \left( \frac{qV}{kT} \right) - 1 \right] + qAD_{n} \frac{n_{po}}{W_{n}} \left[ exp \left( \frac{qV}{kT} \right) - 1 \right]$$

(2.12)

Where W<sub>p</sub> and W<sub>n</sub> are the width of the P and N region, respectively.

The above equation can be rearranged in a simple form

$$I = qA[D_p \frac{p_{no}}{W_n} + D_n \frac{n_{po}}{W_n}][\exp(\frac{qV}{kT}) - 1]$$

(2.13)

If the N region width  $W_n$  is large compared to the hole diffusion length  $L_P$  and the P region width  $W_p$  is large compared to the electron diffusion length  $L_n$ . Then  $W_n$  should be replaced by  $L_p$  and  $W_p$  by  $L_n$ . According to this, the equation (2.13) can be rewritten as follows:

$$I = qA[D_p \frac{p_{no}}{L_p} + D_n \frac{n_{po}}{L_n}][\exp{(\frac{qV}{kT})} - 1]$$

(2.14)

The thermal voltage at room temperature (300 K) is 0.0259 V. In practice the applied voltage in the forward mode is higher than 0.7 V, therefore the term -1 is very small compared to exp (qV/kT) and it is reasonable to eliminate it (2.15).

$$I = qA[D_{p} \frac{p_{no}}{W_{n}} + D_{n} \frac{n_{po}}{W_{n}}][\exp{(\frac{qV}{kT})}]$$

(2.15)

In the reverse mode the term exp (qV/kT) becomes very small compared to -1, therefore equation (2.13) can be simplified to equation (2.16).

$$I = -qA[D_{p}\frac{p_{no}}{W_{p}} + D_{n}\frac{n_{po}}{W_{p}}]$$

(2.16)

The above equation was derived assuming no generation of carriers in the depletion layer. In an actual device, the thermal generation of carriers in the depletion layer should be taken into consideration. The current due to thermal generation ( $I_{R-G}$ ) increases with the width of the depletion layer W, which increases with the applied reverse bias. So, an  $I_{R-G}$  increase as reverse voltage is increased. Equation Figure 2.19 illustrates the thermal generation current.

$$I_{R-G} = -\frac{qAn_iW}{2\tau_o} \tag{2.17}$$

$$\tau_{\rm o} = \frac{\tau_{\rm p} + \tau_{\rm n}}{2} \tag{2.18}$$

$\tau_p$  and  $\tau_n$  are the hole and electron life time.

High current will pass through the diode when the applied voltage is equal (or higher than) the break down voltage of the PN junction. The current-voltage equation (2.16) does not obviously reflect this behaviour, because the break down phenomenon was not taken into consideration when developing this equation.

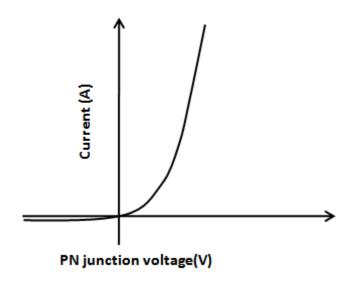

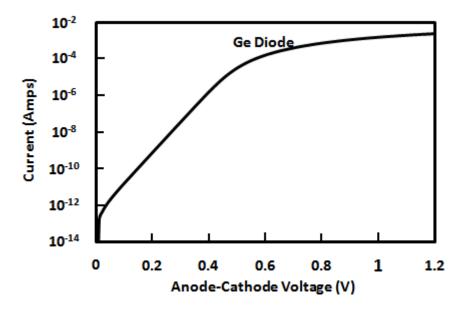

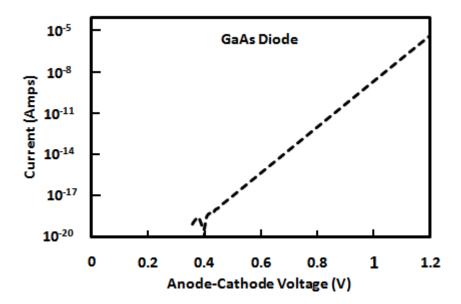

Figure 2.5 represents the current voltage relationship for PN junction.

Figure 2.5: Current-voltage characteristic for PN junction

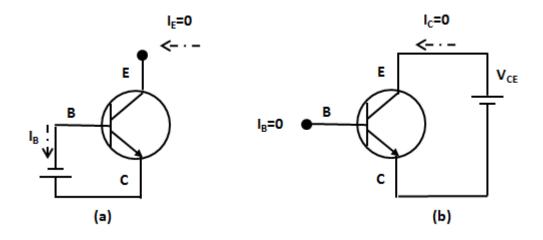

### 2.3 Basic operation of the Si BJTs

In order to use a bipolar transistor in a practical circuit, external bias must be applied to the emitter-base junction and collector-base junction. These two junctions provide four possible bias configurations. The forward active mode (The emitter-base junction is forward biased while the collector base is reversed biased) is the most useful arrangement. This is because in this configuration the gain of the transistor can be exploited to produce current amplification [1].

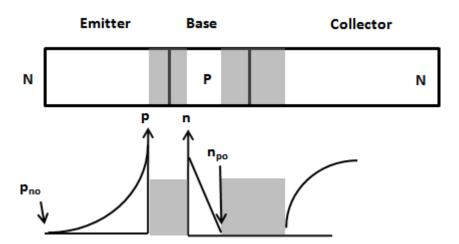

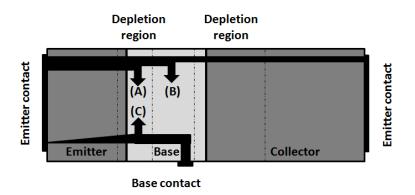

In the forward biased emitter-base junction, holes are injected into the N region (emitter) which form a minority (hole) carrier gradient. This causes a diffusion of holes and gives rise to the main component of base current. Meanwhile electrons are injected into the P base region. Some injected electrons recombine with holes in the base, but the majority diffuse through the base. Since the base-collector junction is reversed biased, these electrons are extracted from the base to the collector region forming the collector current. To have a good n-p-n transistor, it is preferable that almost all the electrons injected by the emitter into the base should be collected, thus the P type region should be narrow, and the hole life time should be long [2].

Figure 2.6 illustrates the minority carrier distribution, this figure shows that the diffusion of holes in the emitter is the source of the base current, while the diffusion of the electrons in

the base gives rise to the collector current. Consequently, it is possible to use equation (2.15) to write the base and collector current equations as follows:

$$I_{C} = -I_{n} = \frac{qAD_{nb}n_{iB}^{2}}{N_{a}W_{B}} \exp\left(\frac{qV_{BE}}{kT}\right)$$

(2.19)

Where  $D_{nb}$  the electron diffusivity in the base is,  $n_{iB}$  is the intrinsic carrier concentration in the base region.

$$I_{B} = -I_{p} = \frac{qAD_{pe}n_{iE}^{2}}{N_{E}W_{E}} \exp\left(\frac{qV_{BE}}{kT}\right)$$

(2.20)

Where  $D_{pe}$  the electron diffusivity in the emitter is,  $n_{iE}$  is the intrinsic carrier concentration in the emitter region.

Figure 2.6: minority carrier distribution in the emitter and base region (the base-emitter region is forward biased).

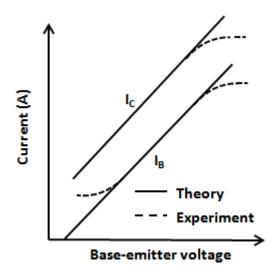

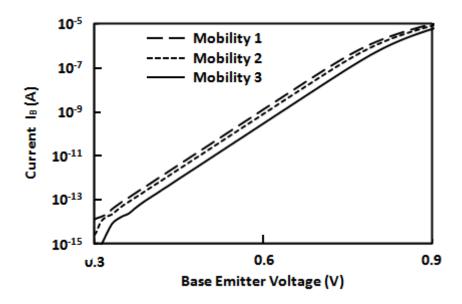

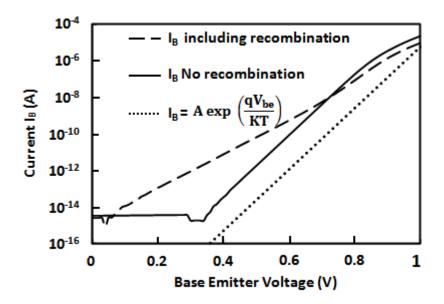

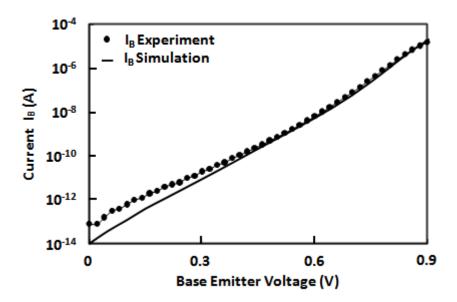

In practice however, the collector and base currents do not follow equation (2.19) and (2.20) at low and high base emitter voltage. Figure 2.7 represents the theoretical and the experimental Gummel plot (collector and base current).

Figure 2.7: comparison between the experimental and theoretical Gummel plot.

The first information to emerge from this comparison is the base current is usually higher than in the theoritical case at low base-emitter voltage. Moreover, both base and collector currents show a reduction at high voltage. The behaviour of the base current at low voltage, which exhibits an exp (qV/mkT), where 1<m≤2 dependence is caused by the recombination current in the depletion region as well as the extrinsic base. The parameter m is known as the ideality factor and it is equal to 1 in the case of pure diffusion current. The amount of deviation of the base current from the ideal behaviour depends strongly on the transistor structure, device structure and fabrication process. This parameter actually determines the physical properties of defects such as their position in the band gap, the concentration and the position in the device. This behaviour is widely known, not only in BJTs but also in HBTs using different material i.e. [Si/SiGe], [AlGaAs/GaAs] and [InGaP/GaAs] [3, 4].

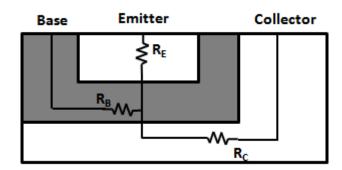

Figure 2.8 represents a schematic diagram illustrating the series resistance in a bipolar transistor.

Figure 2.8: Schematic illustrating the series resistance in bipolar transistor.

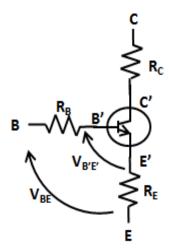

The modelling study that has been carried out earlier has ignored the impact of the series resistance, and it assumed that all external voltage actually appears across the PN junction [5]. This can be a good approximation only at low voltage. The influence of the series resistances on the transistor currents can be understood from the circuit diagram in Figure 2.9. The external connections to the transistor are the terminals C, B, and E, whereas the internal terminals of the ideal transistor that we have been discussing so far are the terminals C', B' and E'.

Figure 2.9: Circuit diagram showing internal collector, base and emitter series resistance

The relationship between the internal and external base-emitter voltage can be derived using Kirchoff's law:

$$V_{B'E'} = V_{BE} - I_B R_B - I_E R_E (2.21)$$

$$V_{B/E} = V_{BE} - I_{B}R_{B} - (I_{C} + I_{B})R_{E}$$

(2.22)

$$V_{B/E} = V_{BE} - I_B R_B - I_B R_E (1 + \beta)$$

(2.23)

Equation (2.23) shows that the voltage across the emitter-base junction  $V_{B'E'}$  is actually smaller than the external base–emitter voltage  $V_{BE}$ . Considering this result, the base and collector current can be written as follow:

$$I_{C} = \frac{qAD_{nb}n_{i}^{2}}{N_{a}W_{B}} \exp\left[\frac{q(V_{BE} - I_{B}R_{B} - I_{B}R_{E}(1+\beta))}{kT}\right]$$

(2.24)

$$I_{B} = \frac{qAD_{pe}n_{i}^{2}}{N_{E}W_{E}} \exp\left[\frac{q(V_{BE} - I_{B}R_{B} - I_{B}R_{E}(1+\beta))}{kT}\right]$$

(2.25)

Considering the series resistance, the base and collector current given by equation (2.24) and (2.25) are smaller that the given by equation (2.19) and (2.20).

### 2.4 Current gain

The current gain represents an important parameter to characterise the DC performance of a bipolar transistor. It is given by the ratio of the collector current to the base current. Using equation (2.19) and (2.20) the current gain is

$$\beta = \frac{I_C}{I_B} = \frac{D_{nb}W_EN_d}{D_{pe}W_BN_a}$$

(2.26)

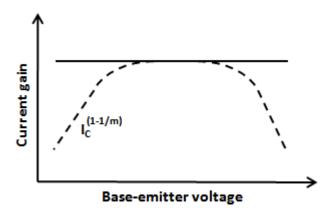

According to the equation above, the current gain is independent of the applied voltage. However, this is not the case in practice where the current gain is lower at low and high voltage. This is because of the behaviour of the base current and also of the collector and base current at high voltage. The behaviour of the current gain at low voltage can be predicted using the equations of the base and collector current. As was mentioned earlier, the ideality factor of the base current at low base-emitter voltage is generally higher than 1. Therefore it is acceptable to rearrange equation (2.20) to form the following equation:

$$I_{\rm B} \propto \exp\left(\frac{qV_{\rm BE}}{mkT}\right)$$

(2.27)

Where m is the ideality factor. In this case, the current gain is not independent of the voltage as shown by the following equation.

$$\beta = \frac{I_C}{I_B} \propto \frac{\exp\left(\frac{qV_{BE}}{kT}\right)}{\exp\left(\frac{qV_{BE}}{mkT}\right)}$$

(2.28)

The above equation can be simplified.

$$\beta = \frac{I_C}{I_B} \propto \exp\left[\left(\frac{qV_{BE}}{kT}\right)(1 - \frac{1}{m})\right] = I_C^{(1 - \frac{1}{m})}$$

(2.29)

Figure 2.10 represents a comparison between the experimental and theoretical current gain, which shows that the current is lower at low and high voltage.

Figure 2.10: comparison between the experimental and theoretical current gain.

The low current gain at the high base emitter voltage is caused by the deviation of the base and collector current from the ideal behaviour in this region.

Equation (2.26) illustrates the main design requirement of a bipolar transistor. In particular, the ratio  $N_d/N_a$  is of great importance. In order to increase the current gain, the emitter doping should be as high as possible. Meanwhile the base doping should be as low as possible. However both strategies have drawbacks. In the case of emitter doping, high doping will cause the band gap narrowing phenomenon. High doping concentration can perturb the perfect periodicity of the semiconductor and reduce its band gap. The intrinsic carrier concentration in this case is subjected to some changes as suggested by the following equation

$$n_{ie}^2 = n_i^2 \exp{(\frac{\Delta E_{G,H}}{2kT})}$$

(2.30)

where  $n_i$  is the intrinsic carrier concentration at low doping levels,  $n_{ie}$  is the intrinsic carrier concentration at high doping level and  $\Delta E_{G,H}$  is the band gap narrowing caused by doping. A simple way of modelling the band gap narrowing in the emitter is through an effective doping concentration in the emitter  $N_{deff}$  as reported by Kumar et al [6].

$$N_{deff} = N_d \frac{n_i^2}{n_{ie}^2} = N_d \exp(\frac{-\Delta E_{G,H}}{2kT})$$

(2.31)

The above equation clearly indicates that the band gap narrowing has the effect of reducing the current gain.

The resistance of a semiconductor bar with length L and cross-section A is given by the following equations:

$$R = \frac{1}{q(\mu_n n + \mu_p p)} \frac{L}{A}$$

(2.32)

Where  $\mu_n$  is the electron mobility,  $\mu_p$  is the hole mobility, n is the electron concentration and p is the hole concentration. Equation (2.32) shows that a reduction of the doping will decrease the hole or the electron concentration, which will lead to an increase of the resistance. Therefore, reducing the base doping to raise the current gain will cause an increase of the base resistance. This drop of the base resistance reduces the switching speed of the bipolar transistor. The base resistance combined with parasitic capacitance form an RC time constant which slow down the device. This impact can be seen clearly in equation (2.33).

$$f_{\text{max}} = \sqrt{\frac{f_{\text{t}}}{8\pi C_{\text{jc}} R_{\text{B}}}}$$

(2.33)

Where  $f_{max}$  is the maximum oscillation frequency,  $f_t$  is the cut-off frequency,  $C_{jc}$  is the base-collector depletion capacitance and  $R_B$  is the base resistance. So there is a clear conflict between the requirements for high speed and high current gain.

Another strategy that can be used to boost the current gain, is increasing the emitter depth and reducing the base width. The first option will lead to an increase of the emitter transit time as suggested by equation (2.34). This is extremely important parameter since it affects the speed of the device.

$$\tau_{\rm E} = \frac{W_{\rm E}W_{\rm B}}{2D_{\rm nb}} \tag{2.34}$$

Therefore, when designing a high speed bipolar transistor it is necessary to have a small emitter depth. The second option, which is reducing the base width, poses two issues. From the fabrication point of view it is difficult to fabricate a very thin base layer. This is because of the boron out-diffusion issue. The punch-through is an issue that may occur when having a very thin base layer. In the common emitter configuration, the emitter-base junction is forward biased. When the base-collector junction is reversed biased, this will increase the width of the depletion region of this junction. In the limit, this depletion region (collector-base) could extend across the whole width of the base and join up with the emitter-base depletion region [7]. In this case, the emitter and collector are connected together by a

single depletion region as illustrated in Figure 2.11. A large current will flow between the emitter and the collector which causes the device to fail.

Figure 2.11: Schematic illustration of a bipolar transistor operating in punch through.

The above discussion about the current gain has shown that there is a conflict in design requirements between high current gain and high speed devices. In order to boost both DC and AC performance of the device, a new approach needs to be applied.

### 2.5 Epitaxial growth of silicon-germanium material

The possibility to combine the low cost advantages of the Si-technology with the high performance nature of III-V or II-VI heterostructures is believed to improve silicon-based heterostructures devices [8]. The lattice mismatch between the lattice constant of Ge and Si which is 4.17 % has allowed the possibility to epitaxially grow strained SiGe layers on Si [9]. For many applications of lattice mismatched materials the use of Vegard's law is practical. This law expresses the linear interpolation of the lattice constant of alloys as a function of parameter x defining the chemical composition of the alloy (compound). For a binary compound Si<sub>1-x</sub>Ge<sub>x</sub> Vegard's law has the form

$$a_{SiGe} = a_{Si}(1 - x) + a_{Ge}x$$

(2.35)

Where  $a_{Si}$ ,  $a_{Ge}$  and  $a_{SiGe}$  are the lattice constant of Si, Ge and Si<sub>1-x</sub>Ge<sub>x</sub>, respectively. However, frequently a deviation from Vegard's law has to be considered for more exact analysis [10]. A systematic investigation of Si<sub>1-x</sub>Ge<sub>x</sub> thin film lattice properties as a function of the Ge content shows that the SiGe lattice constant can be fit by a parabolic relationship of the form [11]

$$a_{SiGe} = 0.002733 x^2 + 0.01992 x + 0.5431$$

(2.36)

where the lattice constants are expressed in nm

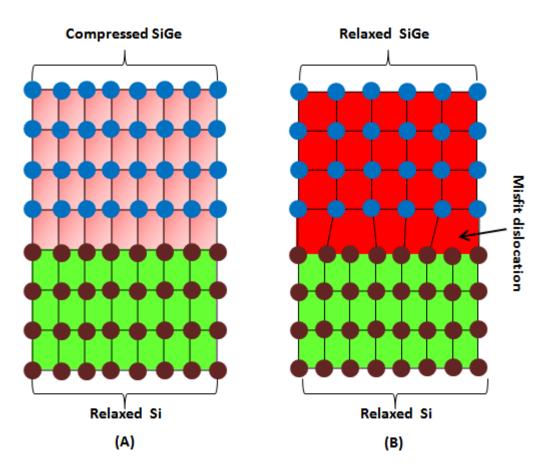

when the SiGe is deposited on a Si substrate, the mismatch may be accommodated in one of two ways [12]:

- The lattice mismatch strain can be accommodated by a tetragonal distortion of the

unit cell in the epitaxial layer. So that SiGe lattice constant fits to the Si lattice

constant as illustrated in Figure 2.12 (A). In this case the SiGe layer is under

compressive stress. This growth is perfect for the fabrication of the SiGe HBTs.

- Another mechanism for strain relaxation in thicker epitaxial layers is the introduction of misfit dislocations, which allows the epitaxial layer to relax toward its free lattice parameter trough the formation of misfit dislocation as illustrated in Figure 2.12 (B). This latter are basically where there is a missing or dangling bond in the lattice between two layers.

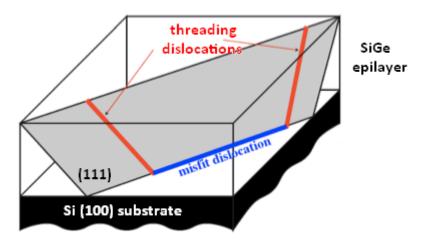

Figure 2.12: Schematic illustration of compressed (A) and relaxed SiGe (B).

The misfit dislocation can thread to the surface and lead to the threading dislocations as shown in the Figure 2.13. The grown SiGe in this case is relaxed, it is known as strain relaxed buffer (or virtual substrate). It is used to grow strained Si to enhance the mobility for MOSFETs technology. This work presents the first implication of strained relaxed buffer in bipolar technology. The existence of the misfit dislocations and threading dislocation represent the main problem with this system [13, 14]. The relaxation of the grown SiGe

layer take place only when its thickness is higher than specific thickness called the critical thickness.

Figure 2.13: Misfit and threading dislocation in Si/SiGe heterostructure [15].

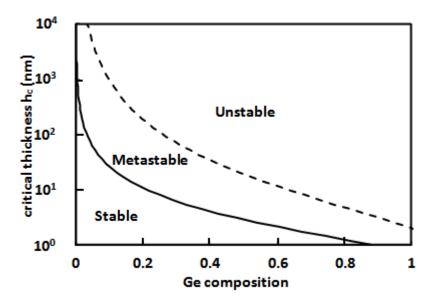

There has been much debate on the determination of the value of the critical thickness. Van der Merwe introduced the concept of critical thickness based on equilibrium theory. He defined critical thickness as the film thickness below which it was energetically favourable to contain the misfit by elastic energy stored in the distorted crystal [12]. Figure 2.1 illustrates the critical thickness.

Figure 2.14: Critical thickness of the SiGe layer [12].

The most important information to emerge from this data is that the critical thickness decreases with the increase of the Ge content. This is because the increase of the Ge content raises the lattice constant and therefore reduces the lattice mismatch between the

Si substrate and the SiGe. The final result is that the strain increases within the SiGe layer. It is important to keep the thickness of the SiGe leyer well under the critical thickness when designing a device based on SiGe herostructures. This is because the relaxation of the SiGe means the formation defects. If these defects are in the active region of the wafer where the transistors are fabricated, they will often lead to a device failure. These failures can be caused directly by the electronic states associated with the defects which leads to excessive leakage. Failure may also be less direct. During processing, the defects may trap other impurities in the wafer that contribute to these electronic states. This might also lead to excessive impurity diffusion during the processing which can change the physical structure of the transistor [16].

### 2.6 Band gap structure of the Si/SiGe structure

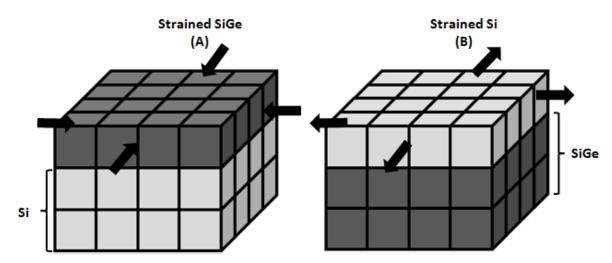

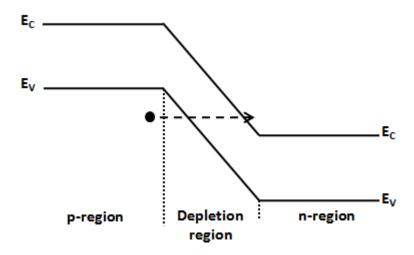

The 4.17% lattice mismatch between Si and Ge has been exploited in a variety of pseudomorphic Si/SiGe heterostructure. Either Si or SiGe, is strained to match the lattice constant (parallel to the interface plane) to that of the unstrained substrate material, SiGe or Si respectively. The lattice constant perpendicular to the interface also changes to compensate for this lateral strain in the active material. There are two main configurations of Si/SiGe heterostructure as illustrated in Figure 2.15. For the SiGe HBTs the configuration (A) is the important [17].

Figure 2.15: Schematic of the Si/SiGe heterostructure. Configuartion (A): strained SiGe on Si, Configuartion (B): strained Si on SiGe.

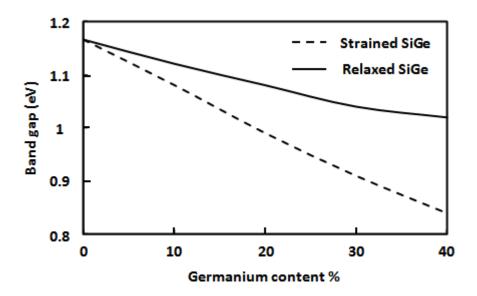

Since Ge has a significantly smaller bandgap than Si (primarily due to its larger lattice constant), it is not surprising that the bandgap of SiGe will be smaller than that of Si. The

strain in a pseudomorphic SiGe alloy, however, also plays an important role in shaping the final band alignment [11]. Figure 2.16 illustrates the band gap of strained and relaxed SiGe versus the Ge content.

Figure 2.16: Band gap as function of relaxed and strained SiGe.

It can be seen that in addition to the Ge content, the strain has a dramatic effect on the band-gap of SiGe. The variation of the band-gap of SiGe (at low temperature 4.2 K) with the Ge content can be described by the following empirical equation developed by Weber et. Al [18].

$$E_g(x, 4.2K) = 1.155 - 0.43 x + 0.206 x^2$$

(x < 0.85) (2.37)

To estimate the  $Si_{1-x}Ge_x$  band gap at higher temperatures, the relationship of temperature with the band gap of Si as shown below [17]:

$$E_g(x, T) = E_g(x, 0K) - \frac{4.73 \times T^2 \times 10^{-4}}{T + 636}$$

(x < 0.85) (2.38)

This reduction of the band-gap is clearly key to the importance of SiGe in the design of SiGe HBTs. The equation (2.39) represents the widely accepted expression of the collector current for SiGe HBTs. This equation shows that a reduction of the band gap corresponds with an exponential increase of the collector current.

$$I_{C} = qAexp \frac{qV_{BE}}{KT} \left[ \frac{D_{nb}N_{CB}N_{VB}}{W_{P}N_{o}} \right] exp \left[ \frac{-E_{g}}{KT} \right]$$

(2.39)

Where q is the electronic charge, A is the device area,  $D_{nb}$  is the diffusion coefficient of electron in the base (SiGe layer),  $W_B$  is the base width,  $N_{ab}$  is the base doping,  $V_{BE}$  is the

base-emitter voltage, k is Boltzmann's constant,  $N_{CB}$  and  $N_{VB}$  are the density of state in the conduction band and the density of state in the valence in the base layer, respectively and  $E_g$  is the band gap of the base layer. This equation also shows that the determination of the band gap plays a crucial role in the determination of the performance of the device.

There have been many investigations into the bandgap of pseudomorphically grown strained SiGe on a relaxed Si substrate, based on the performance of SiGe HBTs [19]. To extract the bandgap of the strained SiGe and doped SiGe three ways may be used. The first possibility is to measure I<sub>C</sub> at room temperature and to make reasonable assumptions for  $D_{nb}$ ,  $N_C$  and  $N_V$  in strained SiGe. With the help of a proper knowledge of the base width and doping density, which can be extracted using SIMS data, it is then possible to calculate the bandgap Eg [19]. This is the first way to determine Eg over the Ge content. The second way [19] is to make use of the temperature dependence of I<sub>C</sub>. For this, it is necessary to know the temperature dependence of  $D_{nb}$  in P type SiGe at the same doping concentration used in the transistor. Using this method one has to assume similar temperature dependences of the densities of states and Eg in SiGe as in Si. The advantage is that no knowledge about the base doping and thickness, the SiGe density of states and the absolute value of the diffusion coefficient of electron  $D_{nb}$  are needed [19]. The third possibility is to fabricate a similar all Si transistor [19]. By comparing the collector current of the Si transistor to that of the SiGe HBTs one can extract a Eg (SiGe) to Eg (Si) from the temperature dependence of the ratio of I<sub>C</sub> in the two devices. The drawback of this method is that one has to assume the same temperature dependence of D<sub>nb</sub> in Si and SiGe, which is improbable because of the additional effect of alloy scattering even at similar doping levels. Moreover it is technologically difficult to get an all-Si transistor with similar base doping. So usually N<sub>ab</sub> (base doping) of the Si transistor is much less than in the SiGe HBT which introduces an additional error. This explains the scattering of the value of the band gap of the strained SiGe that has been reported in many literatures.

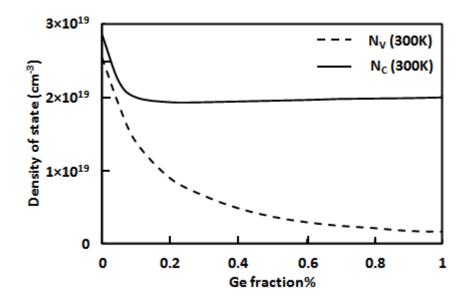

Another parameter of SiGe that is affected by the Ge content is the value of  $N_{CB}$  and  $N_{VB}$  (the density of states of the conduction and valence band). For Ge content approximately equal to 15 %, the value is of  $N_{CB}$  dropps to 2/3 of that of relaxed Si [20]. This is followed a by slight increase of its value ( $N_{CB}$ ) with the increase in Ge content. The value of  $N_{VB}$  dramatically decreases for Ge content less that 20 % as shown in Figure 2.17. This is

disadvantageous for SiGe HBTs, since this reduction of  $N_{VB}$  and  $N_{CB}$  will lead to a decrease of the intrinsic carrier concentration (in the SiGe base layer) and then of the collector current [17]. However, the impact of the density of states is considered to be minor compared to that of the band-gap.

Figure 2.17: Conduction and valance band density of state in SiGe [20].

The amazing advancements achieved in recent years in Si CMOS technology have come primarily from scaling, i.e. from reducing the critical dimensions of the transistors. This has been accomplished by advances in photolithography as well as innovations in the fabrication processes and the use of new materials and novel high dielectric constant materials for the gate insulator. Because it has become increasingly difficult to further reduce critical dimensions such as the gate oxide thickness, alternative ways of improving transistor performance are also being employed. One important approach is to increase the charge carrier mobility using strained Si [21].

An important benefit of compressed SiGe is that can be used to boost the performance of PMOS devices. On any CMOS chip, the major limitation in performance is the PMOS. The mobility and effective masses of holes are smaller than those of electrons in Si. To balance the current drive in CMOS circuit design, the NMOS and PMOS have to be scaled [22]. The changes in the band-gap of the strained SiGe effectively modifies the hole transport properties in the layer, giving chances to improve the performances of PMOS [23]. Leonardo et. al. report 2.5 × hole enhancement in SiGe over Si [24].

The epitaxial growth of Si on relaxed SiGe leads to the formation of tensile strained Si. This is because the lattice constant of Si is smaller than that of SiGe. The electron carrier mobility is known to be high in tensile strained Si compared to relaxed Si, hence, the importance of this material in the fabrication of N channel MOSFETs. This has been shown in many experimental reports [25].

Several groups have reported theoretical and experimental values of the strained Si band gap on SiGe substrates as a function of the Ge content of the relaxed SiGe substrates using different calculation methods that account for conduction band and valence band shifts. According to this literature, a strained Si band gap shrinkage is expected as the Ge composition is increased in the SiGe substrate i.e., as strain is increased [26]. Equation (2.40) illustrates the band gap of strained Si versus the Ge content at 300 K [17].

$$E_g(x) = 1.11 - 0.6 x$$

(2.40)

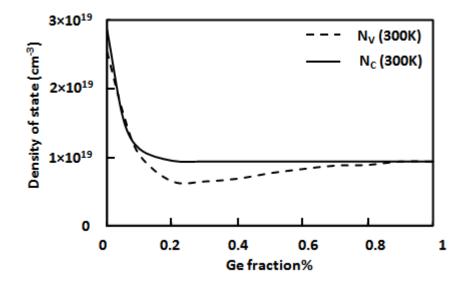

This change in the band gap leads to a reduction of the carrier effective mass and band scattering rates, and therefore an increase of the carrier mobility (electron and hole) [27]. This mobility increases with an increase in strain which is determined by the Ge content of a SiGe layer underneath strained-Si films [28]. Figure 2.18 shows also that  $N_V$  and  $N_C$  are smaller in strained Silicon compared to relaxed Si.

Figure 2.18: Conduction and valence band density of state in strained Si [20].

## 2.7 Dopant diffusion in SiGe

Every semiconductor device technology relies on the ability to fabricate well-controlled, locally doped regions of the wafer. The chemical impurities must first be introduced into some sections of the wafer. They must be active so they can contribute the desired carrier concentration. After the impurities are introduced they may redistribute in the wafer. This may be intentional or it may be a consequence of some other thermal process. In either event, it must be controlled and monitored. The motion of the impurity in the wafer occurs primarily by diffusion: any impurity that is free to move will experience a net distribution in response to a concentration gradient. The source of this movement is the random motion in the material. Since a high concentration region has more impurty atoms, there is a net movement of impurities away from the concentration maximum. This effect is not limited to impurities in semiconductors [16]. Fick's first law of diffusion given by equation (2.41) can also be used to describe heat transfer, the motion of electrons and gaseous impurities such as air pollution.

The basic equation that describes diffusion is Fick's first law [16]:

$$J = -D \frac{\partial C(x,t)_i}{\partial x}$$

(2.41)

Where  $C_i$  is the impurity concentration, D is the coefficient of diffusion and J is the net flux of the impurity material. The negative sign express the fact that there is net movement in the direction of decreasing concentration.

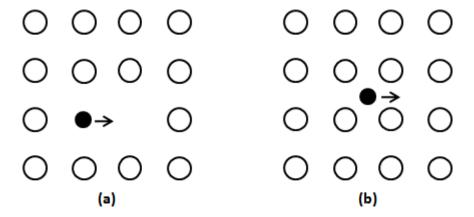

Diffusion in semiconductors can be visualised as atomic movement of the impurity in the crystal lattice by vacancies or interstitials. Figure 2.19 shows two basic atomic diffusion models in a solid. The open circles represent the host atoms occupying the equilibrium lattice positions. The solid dots represent impurity atoms. At elevated temperatures, the lattice atoms vibrate around the equilibrium lattice sites. There is a finite probability that a host atom acquires sufficient energy to leave the lattice site and to become an interstitial atom, thereby creating a vacancy. When a neighbouring impurity atom migrates to the vacancy site, as illustrated in Figure 2.19 (a) the mechanism is called vacancy diffusion. If an interstitial atom moves from one place to another without occupying a lattice site Figure 2.19 (b), the mechanism is interstitial diffusion. An atom which is smaller than the host atom

often moves interstitially [29]. The boron is known to diffuse on silicon using interstitial mechanism.

Figure 2.19: Atomic diffusion mechanisms for a two dimensional lattice. (a) Vacancy mechanism; (b) interstitial mechanism.

The logarithm of the diffusion coefficient for Si plotted against the reciprocal of the absolute temperature is known to give a straight line in most cases. This implies that over temperature range, the diffusion coefficient can be expressed as

$$D = D_0 \exp\left(\frac{-E_a}{kT}\right) \tag{2.42}$$

Where  $D_0$  is the diffusion coefficient in cm<sup>2</sup>/s and  $E_a$  is the activation energy in eV.

For the interstitial diffusion model,  $E_a$  is related to the energy required to move dopant atoms from one interstitial site to another. The value of  $E_a$  is found to between 0.5 and 2 eV in Si. For the vacancy diffusion model,  $E_a$  is related to both the energy of motion and the energy of formation of vacancies. Thus  $E_a$  for vacancy diffusion is larger than that for interstitial diffusion which is usually between 3 and 5 eV [29].

Understanding the dopant diffusion in SiGe, allows an accurate prediction of the doping profile after thermal annealing to be performed [30].

The nature of a Si/SiGe heterostructure introduces several complications to a dopant diffusion model as compared to diffusion in bulk Si. First, there is a so-called "chemical effect" caused by the introduction of Ge atoms [31]. The equilibrium concentration of self-interstitials and vacancies are closely related to the bonding energies of atoms. In covalent crystals, the heat of sublimation is equivalent to the energy needed for the rupture of half of the atomic bonds. The heat of sublimation values of pure Ge and Si crystals are, respectively,

equal to 374.5 and 455.6 kJ mol<sup>-1</sup>. Thus, the atomic bonding energy in relaxed SiGe is lowered by the presence of Ge atoms and it is expected that both interstitial and vacancy concentrations will increase [32]. Secondly, SiGe has a larger lattice parameter, so when it is grown epitaxially on a Si substrate, the SiGe layer will be biaxially strained in order to comply with the smaller lattice parameter of the Si substrate. This macroscopic strain may influence the diffusion process as well [31].

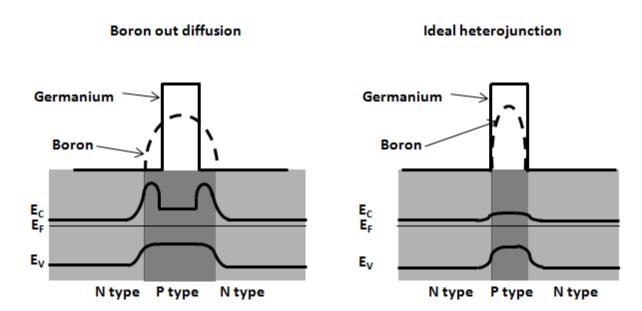

Moriya et al. [33] have found that the boron diffusion is retarded in strained SiGe. This is advantageous for SiGe HBT design, since it facilitate the design of a device with a very thin base layer which therefore decreases both the base resistance and transit time. This results in an increase of device speed. The retardation of the boron in SiGe helps also to prevent the formation of parasitic energy barriers. This occurs when the boron penetrates outside the SiGe layer [34]. In the extreme case, depletion regions (emitter/base and base/collector) are formed in the Si region and hence the Si band gap is obtained at this depletion region. On moving into SiGe layer, a decrease of the band gap is obtained, which lead to the formation of parasitic barriers as illustrated in Figure 2.20. Even a small amount of out diffusion is reported to degrade the collector current and therefore the current gain [34].

Figure 2.20: Parasitic barriers in SiGe HBTs.

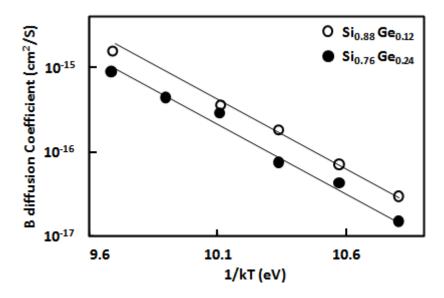

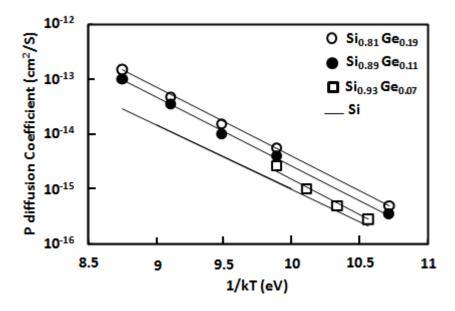

Figure 2.21 illustrates the impact of Ge content on boron diffusion over a wide range of temperature. This figure shows that the presence of Ge leads to a reduction of boron diffusion.

Figure 2.21: Boron diffusion in SiGe with different Ge content [35].

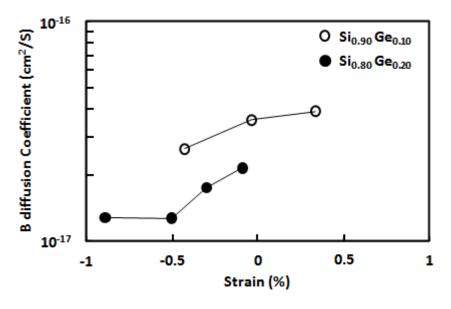

The work presented by Moriya et al. [33] did not separate the chemical influence and the strain influence on the boron diffusion, however this was done by Kuo et al. [36].

The strain dependence can be determined directly by measuring the diffusion in a SiGe layer grown pseudomorphically on a relaxed SiGe template. Varying the Ge content in the relaxed SiGe will allow a change in the amount of strain and also the type of the strain (compressive or tensile) in the pseudomorphic SiGe layer. Figure 2.22 represents the influence of the strain on boron diffusion at 800 °C. This data shows that the strain has a small impact on boron diffusion.

Figure 2.22: Influence of the strain on boron diffusion [36].

The impact of the Ge is not the same for all dopant species. Figure 2.23 shows that phosphorus diffusion is enhanced in SiGe relative compared to that in Si and the enhancement increases with increasing Ge content [31].

Figure 2.23: Phosphorus diffusion in SiGe [31].

#### 2.8 Performance of SiGe HBTs

The performance of semiconductor devices tends to improve as the dimensions shrink. This simple principle of scaling has been the key to the spectacular success of the semiconductor industry over the past half-century. It has worked for virtually all types of transistors, including the Si-based bipolar transistor [37].

Historically, scaling has run into difficulties many times in the course of bipolar technology evolution, which have been successfully overcome with help from material and structural innovations, such as the self-aligned base, poly emitter, and most recently, the SiGe base.

There has been tremendous progress in the ability to grow device quality SiGe films. The initial growth technique used was Si MBE [38], but this was replaced by high quality CVD techniques such as UHV/CVD. The ability to in situ dope SiGe films with B and P and incorporate C (to reduce the boron diffusivity) in the film has greatly extended the performance levels achieved [39]. The ability to grow high quality SiGe has lead to a successful fabrication of SiGe HBTs. This device consists of having a thin SiGe layer as base instead of Si for Si BJTs.

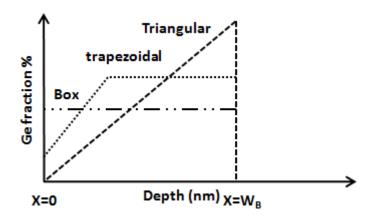

Bandgap engineering with the incorporation of Ge in the base of silicon bipolar transistors results in improved performance of these devices with only a modest increase in process complexity. The Ge content has tipically, one of three possible profiles as shown in Figure 2.24. The first one is the Box profile: the Ge content is constant throughout the base. The second is the triangular profile, where the Ge content changes linearly with depth. The third one is the trapezoidal, which is a combination of the triangular and box profile. The small band gap of the SiGe layer increases the amount of minority carriers injected into the base exponentially, thus causing an increase in the collector current for the same forward bias. In addition, the band gap grading gives rise to a drift field which aids the minority carrier transport through the base. The incorporation of a small amount of Ge into the Si in the base layer therefore greatly enhances the performance of the transistor [40]. Figure 2.24 illustrates the three possible profiles.

Figure 2.24: Different type of Ge profile (Box, Trapezoidal and Triangular) that can be used in bipolar technology.

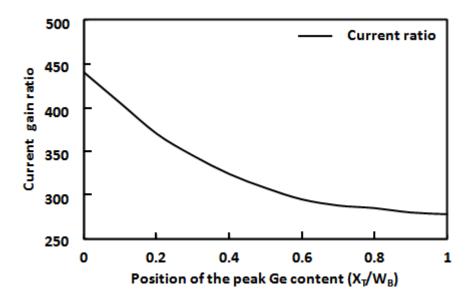

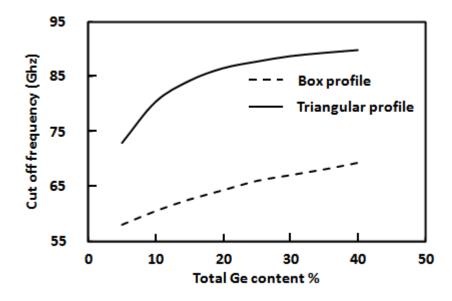

Generally, the use of Ge enhances both DC (current gain) and AC (cut-off frequency) performance of SiGe HBTs. However, triangular profile increases more the speed of the device while the box profile has great impact on the current gain of the device. Figure 2.25 shows the current gain ratio for SiGe HBTs and Si BJTs. This ratio decrease when moving from box profile to triangular profile. Figure 2.26 illustrates the cut off frequency of two SiGe HBTs with different profiles. While the speed of both devices increase with increase of Ge content in the base, it obvious that the use of a triangular profile leads to the highest cut- off frequency.

Figure 2.25: Plot of current gain ratio vs. position w, (that is, XT/WB) of the peak Ge content at the base of the SiGe HBT (w =0 for the box profile, w =1 for the triangular profile, trapezoidal otherwise) [41].

Figure 2.26: Cut off frequency versus Ge content for both Box and triangular profile [41].

# 2.9 BiCMOS technology using VS HBT

Silicon integrated circuits presently dominate the semiconductor industry. The two most important devices used in Si technology are field effect and bipolar transistors. For digital circuit applications, complementary metal oxide semiconductor (CMOS) technology dominates because of its low power dissipation and high density of integration However, MOS transistors have a number of disadvantages, foremost among which are limited drive

capability and limited high frequency performance. CMOS has been the work horse for microprocessors and static random access memories. Bipolar transistors with their high speed and high transconductance (therefore high current drive) have mostly been used in analogue applications. The main drawback in bipolar digital circuits is the high power consumption. To improve single chip functionality, bipolar complementary metal oxide semiconductor (BiCMOS) has been developed to combine the advantages of CMOS and bipolar devices.

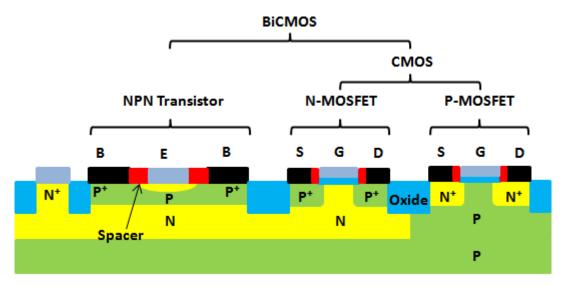

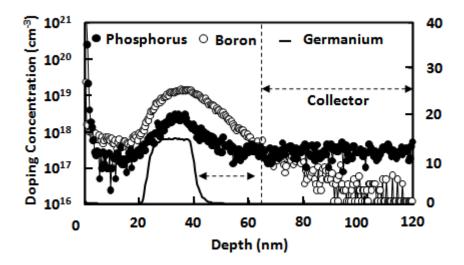

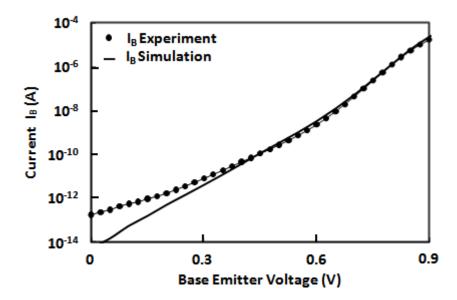

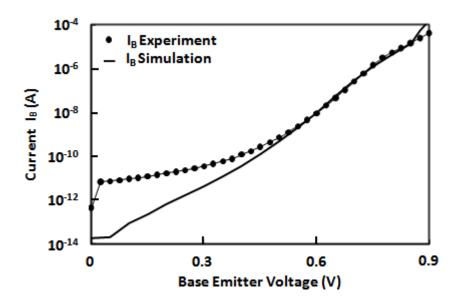

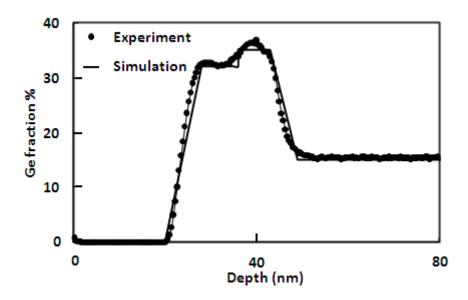

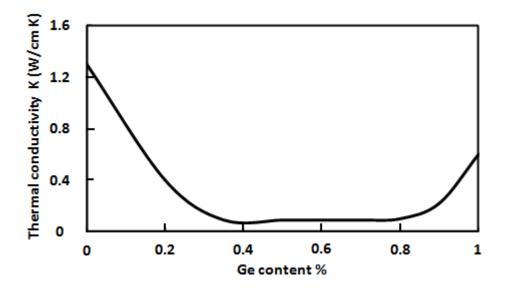

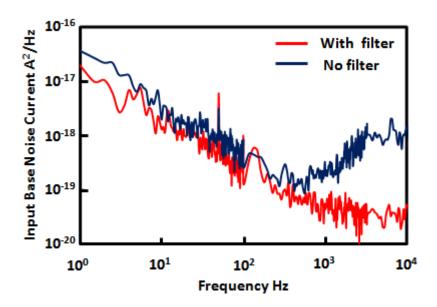

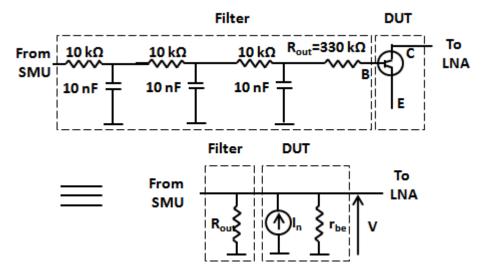

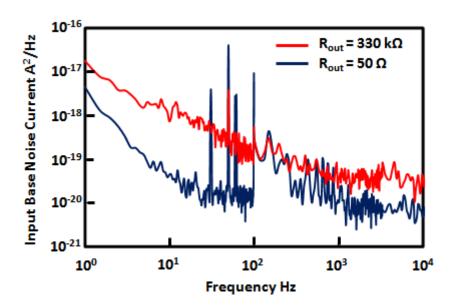

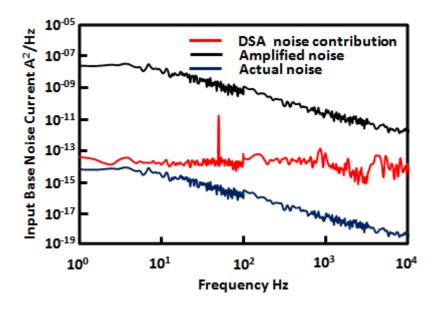

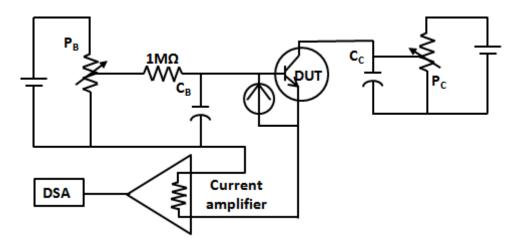

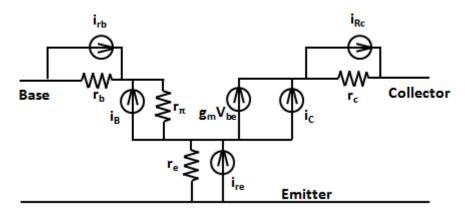

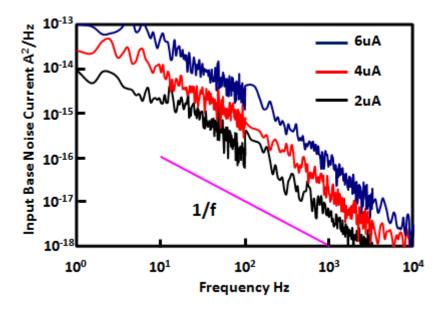

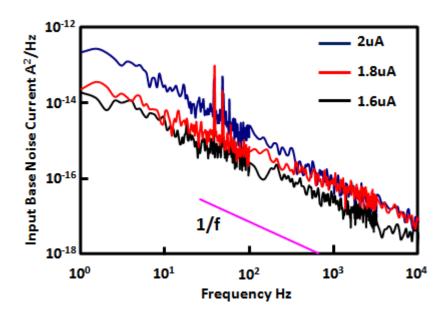

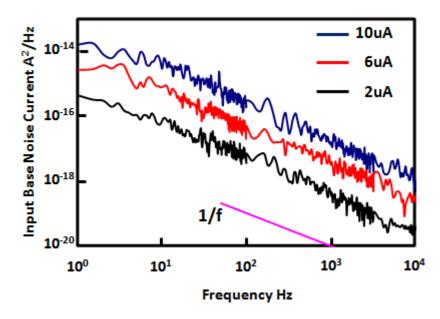

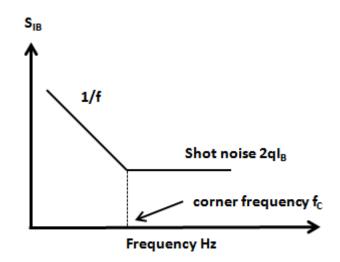

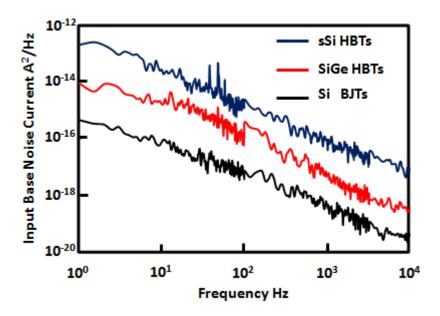

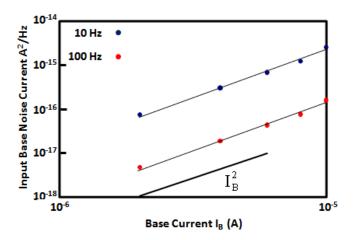

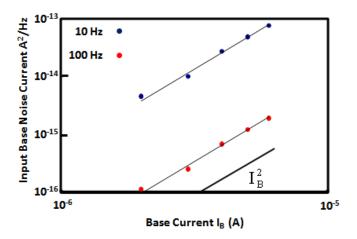

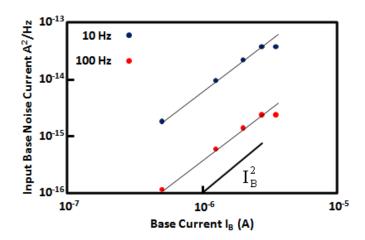

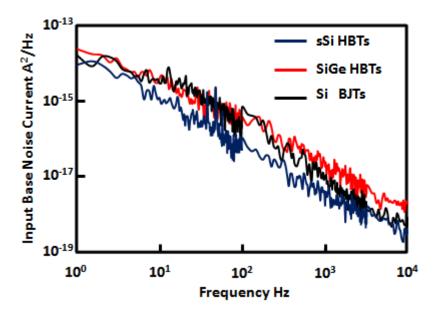

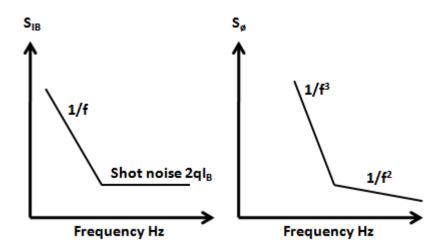

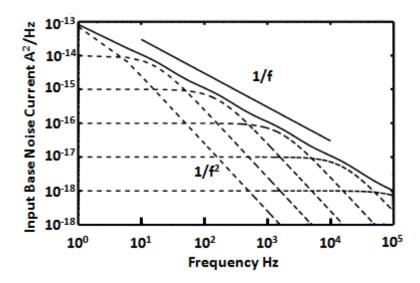

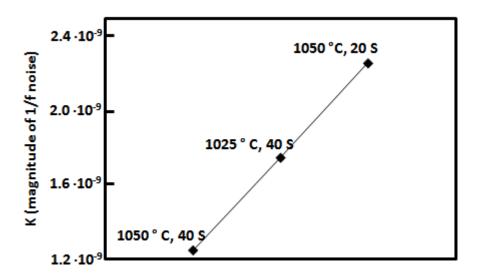

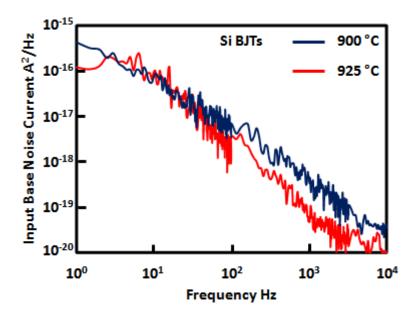

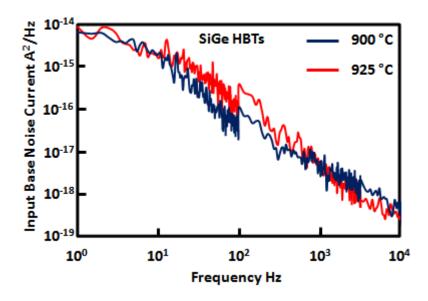

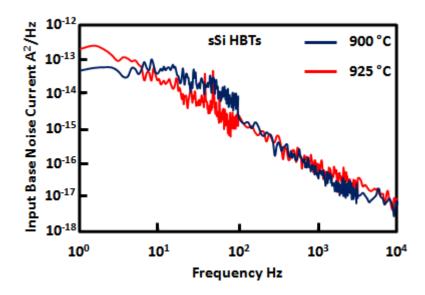

Figure 2.27: Structure of BiCMOS chip [1].