# UNIVERSITY OF NEWCASTLE UPON TYNE

## Department of Computing Science

# A Framework for Supporting Automatic Simulation Generation from Design

by

## Leonardus Budiman Arief

Ph.D. Thesis

July 2001

### Abstract

Building a new software system requires careful planning and investigation in order to avoid any problems in the later stages of the development. By using a universally accepted design notation such as the *Unified Modeling Language (UML)*, ambiguities in the system specification can be eliminated or minimised.

The aspect that frequently needs to be investigated before the implementation stage can be commenced concerns the proposed system's *performance*. It is necessary to predict whether a particular design will meet the performance requirement - i.e. is it worth implementing the system - or not. One way to obtain this performance prediction is by using simulation programs to mimic the execution of the system. Unfortunately, it is often difficult to transform the design into a simulation program without some sound knowledge of simulation techniques. In addition, new simulation programs need to be built each time for different systems - which can be tedious, time consuming and error prone.

The currently available UML tools do not provide any facilities for generating simulation programs automatically from UML specifications. This shortcoming is the main motivation for this research. The work involved here includes an investigation of which UML design notations can be used; the available simulation languages or environments for running the simulation; and more importantly, a framework that can capture the simulation information from UML design notation. Using this framework, we have built tools that enable an automatic transformation of a UML design notation into a simulation program. Two tools (parsers) that can perform such a transformation have been constructed. We provide case studies to demonstrate the applicability of these tools and the usefulness of our simulation framework in general.

### Acknowledgement

I would like to thank my supervisor, Dr. Neil Speirs for his guidance and useful feedbacks throughout my Ph.D. work. A lot of people at Newcastle University have also helped me towards the completion of this thesis, especially Prof. Isi Mitrani for explaining everything I need to know about simulation, Prof. Santosh Shrivastava and Dr. Mark Little for providing initial direction and one of the case studies, Prof. Cliff Jones for letting me finish my thesis while working as a research associate on his project, our librarian Ms. Shirley Craig for assisting me in finding references, and the Department of Computing Science for funding my Ph.D.

I would also like to acknowledge my colleagues for many fruitful and interesting discussions, in particular to Dr. Denis Besnard, Dr. Cristina Gacek, Mr. Tony Lawrie, Dr. Graham Morgan, Mr. Thomas Rischbeck, and Dr. Arnaud Simon. I am grateful to my friends, wherever they are now, for cheering me up and giving me comfort. Last but certainly not least, I would like to express my special gratitude to my Mom, without whose constant encouragement and prayer I would never finish this thesis.

## **Table of Content**

| 1. INTRODUCTION                                                           | 1  |

|---------------------------------------------------------------------------|----|

| 1.1. Overview                                                             | 1  |

| 1.2. Related Work                                                         | 2  |

| 1.2.1. Related Work outside UML                                           | 3  |

| 1.2.2. Related Work using UML                                             | 7  |

| 1.2.3. Relevance to this thesis                                           | 15 |

| 1.3. CHAPTERS PLAN                                                        | 16 |

| 2. DESIGNING A SOFTWARE SYSTEM                                            |    |

| 2.1. INTRODUCTION                                                         |    |

| 2.2. UNIFIED MODELING LANGUAGE                                            | 19 |

| 2.3. UML AND SYSTEM PERFORMANCE                                           | 25 |

| 3. SIMULATION TO PREDICT SYSTEM'S PERFORMANCE                             | 27 |

| 3.1. INTRODUCTION                                                         | 27 |

| 3.2. SIMULATION BASICS.                                                   | 29 |

| 3.2.1. What is simulation?                                                |    |

| 3.2.2. Advantages and Disadvantages of Simulation                         |    |

| 3.2.3. Types of Simulation                                                |    |

| 3.3. SIMULATION LANGUAGES/PACKAGES                                        |    |

| 3.3.1. C++SIM                                                             |    |

| 3.3.2. JavaSim                                                            |    |

| 3.4. SIMULATION SUMMARY                                                   | 41 |

| 4. FROM DESIGN TO SIMULATION                                              |    |

| 4.1. INTRODUCTION                                                         | 42 |

| 4.2. SIMML FRAMEWORK                                                      | 42 |

| 4.2.1. SimML Components                                                   |    |

| 4.2.2. SimML Actions                                                      |    |

| 4.3. USING THE SIMML FRAMEWORK TO GENERATE SIMULATION PROGRAM FROM DESIGN |    |

| 4.3.1. SimML Syntax                                                       |    |

| 4.3.2. Capturing SimML Notation from UML Design                           |    |

| 4.3.3. Transforming SimML Notation into Simulation                        |    |

| 5. UML-TO-SIMULATION TOOL IMPLEMENTATION                                  | 55 |

| 5.1. INTRODUCTION                                                         | 55 |

| 5.2. THE PARSER'S STRUCTURE                                               | 57 |

| 5.3. PERL IMPLEMENTATION                                     |     |

|--------------------------------------------------------------|-----|

| 5.3.1. PERL Basics                                           |     |

| 5.3.2. From SimML to C++SIM using PERL                       |     |

| 5.4. JAVA IMPLEMENTATION                                     |     |

| 5.4.1. Java Foundation Class (JFC) and Swing                 |     |

| 5.4.2. Our Approach in Building the UML/SimML Tool           |     |

| 5.4.2.1. Formulating a solution                              |     |

| 5.4.2.2. Java package for SimML                              |     |

| 5.4.2.3. Deriving SimML information from UML diagrams        | 91  |

| 5.4.2.4. Generating JavaSim code                             | 94  |

| 5.4.2.5. Building the UML/SimML Tool                         | 97  |

| 5.4.3. Using XML for storing SimML data                      |     |

| 5.5. SUMMARY                                                 | 110 |

| 6. CASE STUDIES                                              | 112 |

| 6.1. INTRODUCTION                                            |     |

| 6.2. SIMPLE QUEUEING SYSTEMS                                 |     |

| 6.2.1. Description of the Queueing Systems                   |     |

| 6.2.2. Queueing Systems Specification using UML/SimML        |     |

| 6.2.3. Simulation of the Queueing Systems                    |     |

| 6.2.4. Summary of the Queueing Systems case study            |     |

| 6.3. BT INTELLIGENT NETWORK (IN) APPLICATION                 |     |

| 6.3.1. Description of the BT IN Application                  |     |

| 6.3.2. BT specification using UML/SimML                      |     |

| 6.3.3. Simulation of the makeCall operation                  |     |

| 6.3.4. Summary of BT case study                              |     |

| 6.4. Voltan                                                  |     |

| 6.4.1. Description of the Voltan system                      |     |

| 6.4.2. Voltan system specification using the SimML framework |     |

| 6.4.3. Simulation of Voltan system                           |     |

| 6.4.4. Summary of Voltan case study                          |     |

| 6.5. SOME REMARKS                                            |     |

| 7. CONCLUSION                                                |     |

| 7.1. ANALYSIS OF THE SIMML TOOLS                             |     |

| 7.2. Further Work                                            |     |

|                                                              |     |

## **List of Figures**

| FIGURE 2-1: THE CLASS DIAGRAM NOTATIONS                                        | 20  |

|--------------------------------------------------------------------------------|-----|

| FIGURE 2-2: THE USE CASE DIAGRAM NOTATION                                      | 21  |

| FIGURE 2-3: THE SEQUENCE DIAGRAM NOTATION                                      | 22  |

| FIGURE 2-4: THE COLLABORATION DIAGRAM NOTATION                                 | 22  |

| FIGURE 2-5: THE STATE DIAGRAM NOTATION                                         | 23  |

| FIGURE 2-6: THE ACTIVITY DIAGRAM NOTATION                                      | 23  |

| FIGURE 2-7: THE PACKAGE DIAGRAM NOTATION                                       | 24  |

| FIGURE 2-8: OTHER USEFUL UML NOTATIONS                                         | 24  |

| FIGURE 3-1: THE CLASSIFICATION OF SIMULATION TYPE BASED ON EVENTS AND TIME     | 33  |

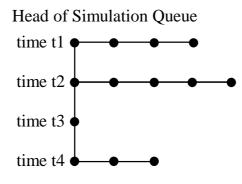

| FIGURE 3-2: SIMULATION QUEUE                                                   | 37  |

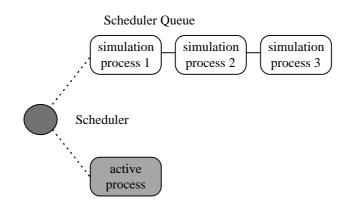

| FIGURE 3-3: SCHEDULER-PROCESS INTERACTION                                      | 37  |

| FIGURE 4-4: THE EBNF NOTATION FOR THE SIMML SYNTAX                             | 52  |

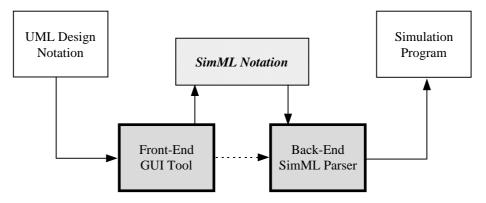

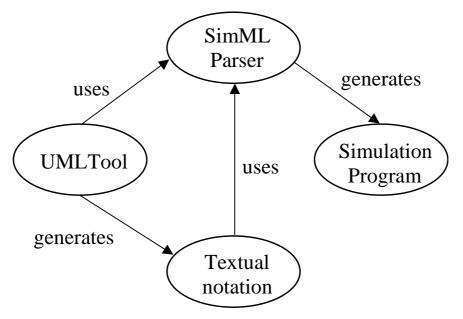

| FIGURE 5-1: UML TO SIMULATION PATH                                             | 55  |

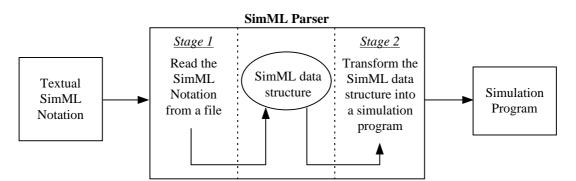

| FIGURE 5-2: THE TWO STAGES IN PARSING TEXTUAL SIMML NOTATION INTO SIMULATION   | 58  |

| FIGURE 5-3: AN OUTLINE FOR READING, EVALUATING AND ORGANISING DATA             | 64  |

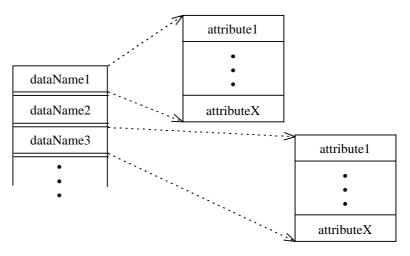

| FIGURE 5-4: THE DATA ARRAY                                                     | 69  |

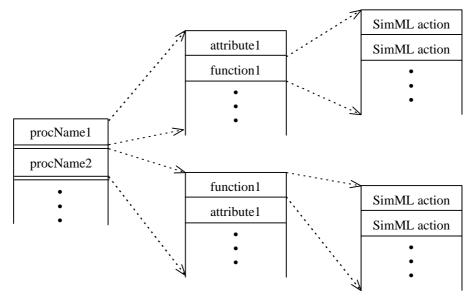

| FIGURE 5-5: THE PROCESS ARRAY                                                  | 70  |

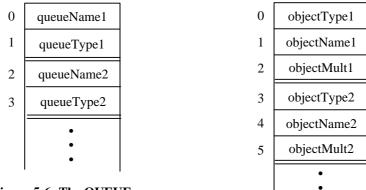

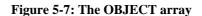

| FIGURE 5-6: THE QUEUE ARRAY                                                    | 71  |

| FIGURE 5-7: THE OBJECT ARRAY                                                   | 71  |

| FIGURE 5-8: THE RANDOMS ARRAY                                                  | 71  |

| FIGURE 5-9: THE STATISTICS ARRAY                                               | 71  |

| FIGURE 5-10: THE PATHS FOR GENERATING SIMULATION FROM UML                      | 88  |

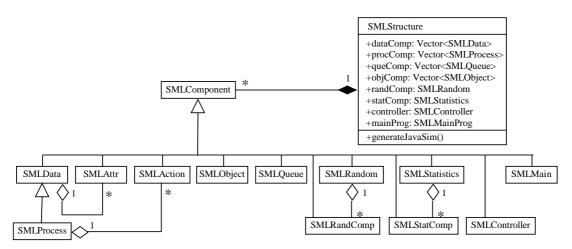

| FIGURE 5-11: THE CLASS DIAGRAM FOR THE SIMML COMPONENTS AND ACTIONS            | 91  |

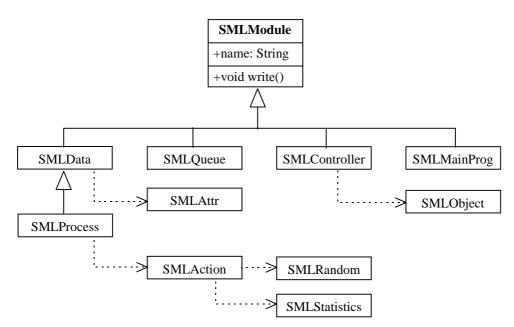

| FIGURE 5-12: MODULAR ORGANISATION OF THE SIMML COMPONENTS                      | 96  |

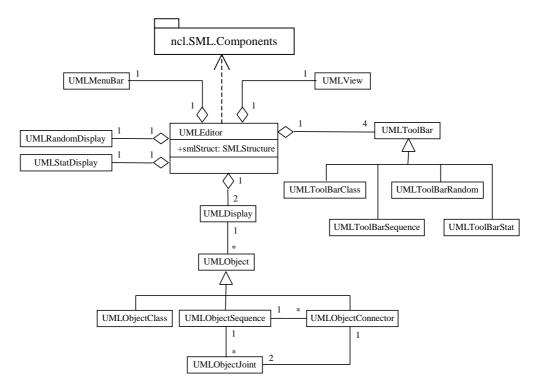

| FIGURE 5-13: THE STRUCTURE OF OUR UML TOOL                                     | 99  |

| FIGURE 5-14: THE PROPOSED LAYOUT OF THE UML/SIMML TOOL                         | 105 |

| FIGURE 5-15: A SNAPSHOT OF THE SIMML DTD                                       | 107 |

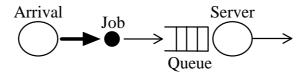

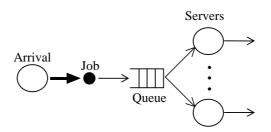

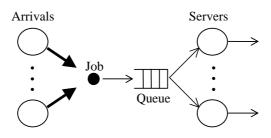

| FIGURE 6-1: A SYSTEM WITH ONE ARRIVAL AND ONE SERVER                           | 114 |

| FIGURE 6-2: A SYSTEM WITH MULTIPLE SERVERS                                     | 114 |

| FIGURE 6-3: A SYSTEM WITH MULTIPLE ARRIVALS AND SERVERS                        | 115 |

| FIGURE 6-4: THE CLASS DIAGRAM FOR "ONE ARRIVAL, ONE SERVER" SYSTEM             | 116 |

| FIGURE 6-5: THE SEQUENCE DIAGRAM FOR "ONE ARRIVAL, ONE SERVER" SYSTEM          | 117 |

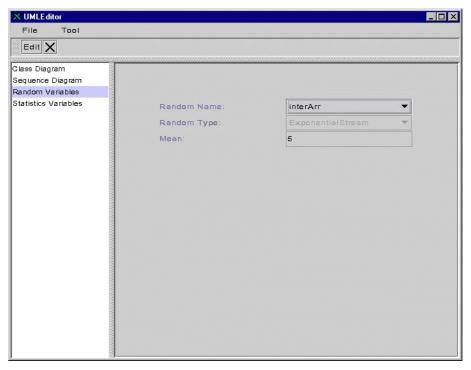

| FIGURE 6-6: THE RANDOM VARIABLES VIEW FOR "ONE ARRIVAL, ONE SERVER" SYSTEM     | 117 |

| FIGURE 6-7: THE STATISTICS VARIABLES VIEW FOR "ONE ARRIVAL, ONE SERVER" SYSTEM | 118 |

| FIGURE 6-8: THE CLASS DIAGRAM FOR "ONE ARRIVAL, MULTIPLE SERVERS" SYSTEM       | 119 |

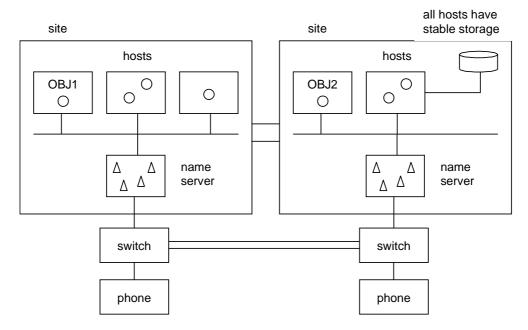

| FIGURE 6-9: THE ARCHITECTURE OF THE BT IN APPLICATION                          | 126 |

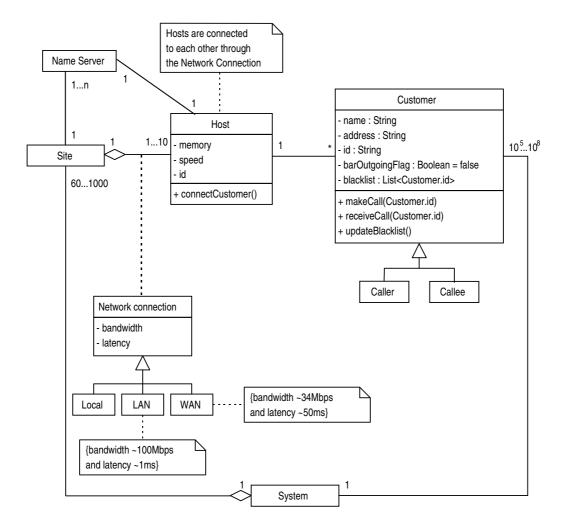

| FIGURE 6-10: THE CLASS DIAGRAM OF BT IN APPLICATION                          | . 127 |

|------------------------------------------------------------------------------|-------|

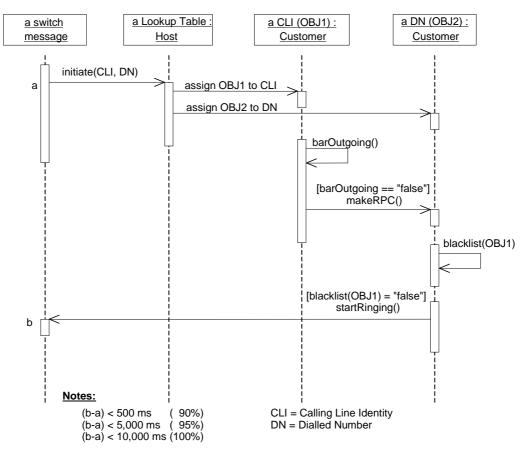

| FIGURE 6-11: THE SEQUENCE DIAGRAM OF BT IN APPLICATION                       | 128   |

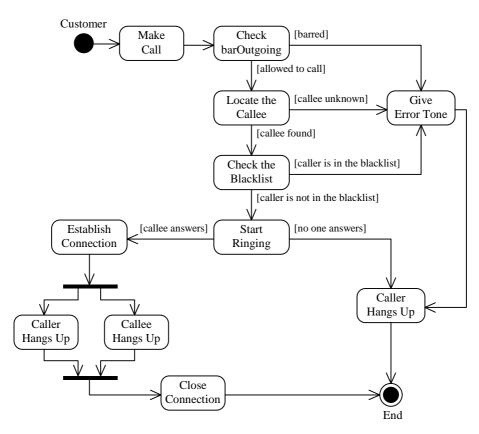

| FIGURE 6-12: AN ACTIVITY DIAGRAM FOR MAKECALL                                | 129   |

| FIGURE 6-13: THE CLASS DIAGRAM FOR THE MAKECALL OPERATION                    | . 130 |

| FIGURE 6-14: THE SEQUENCE DIAGRAM FOR THE MAKECALL OPERATION                 | 131   |

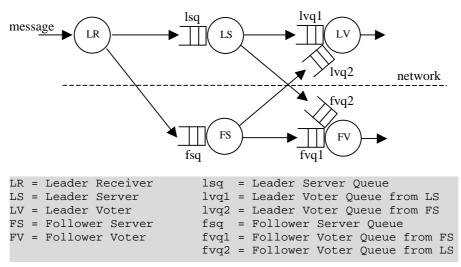

| FIGURE 6-15: A SIMPLIFIED ARCHITECTURE OF A SINGLE VOLTAN NODE               | 137   |

| FIGURE 6-16: THE SIMML NOTATION OF THE VOLTAN SYSTEM                         | 139   |

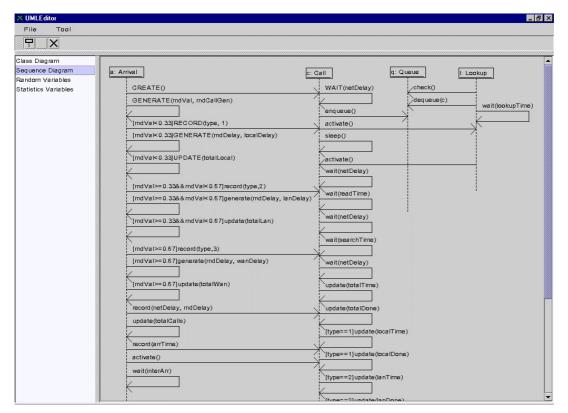

| FIGURE 6-17: SCREEN DUMP OBTAINED FROM RUNNING RUNSIM PARSER                 | 140   |

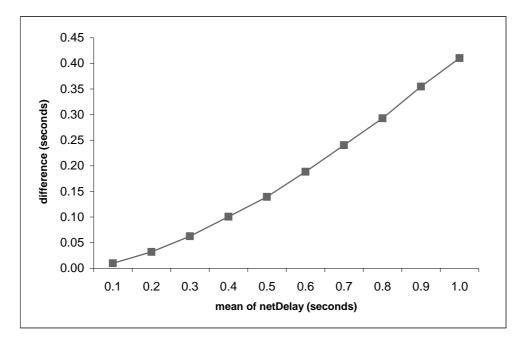

| FIGURE 6-18: EFFECT OF NETDELAY ON PERFORMANCE DIFFERENCE BETWEEN LEADER AND |       |

| FOLLOWER                                                                     | 142   |

## **List of Tables**

| TABLE 4-1: RANDOM NUMBER DISTRIBUTIONS SUPPORTED BY SIMML                    | 46  |

|------------------------------------------------------------------------------|-----|

| TABLE 5-1: PERL VARIABLE INDICATORS                                          | 60  |

| TABLE 5-2: THE FOUR VIEWS OF THE UML/SIMML TOOL                              | 104 |

| Table 6-1: Simulation results of One Arrival, Multiple Servers systems       | 123 |

| TABLE 6-2: SIMULATION RESULTS OF MULTIPLE ARRIVALS, MULTIPLE SERVERS SYSTEMS | 124 |

| TABLE 6-3: THE RANDOM VARIABLES USED IN THE MAKECALL SIMULATION              | 132 |

| TABLE 6-4: SIMULATION RESULTS OF THE MAKECALL OPERATION                      | 135 |

| TABLE 6-5: VOLTAN SIMULATION RESULTS WITH INCREMENTING NETDELAY              | 141 |

| TABLE 7-1: COMPARISONS BETWEEN RUNSIM AND UML/SIMML TOOLS                    | 145 |

## **Chapter 1**

### Introduction

#### 1.1. Overview

The construction of a new computer system is an inherently complicated process, hence it requires some careful planning and design. For example, in the area of distributed systems, a computer application usually needs to satisfy quite stringent requirements such as reliability, availability, security, etc. and the cost of building such an application will be quite high. It is therefore desirable to be able to predict the performance of the proposed system before the construction begins.

In order to solve this problem, it is important to evaluate the requirements of the new system and translate them into a specification for design purpose. The design process helps the system developers to understand the requirements better and to avoid misconceptions about the system. From the specification, a simulation program can be built to mimic the execution of the proposed system. The simulation run provides some data about the states of the system and from these data, the performance of the system can be predicted and analysed.

There is a drawback though as it is often difficult to transform the design specification into a simulation program. The specification is normally quite complex and different performance requirements (such as high availability, reliability, etc.), connection between components (network delay, partition, etc.) and fault tolerance (machine failures and repairs) require additional effort. On top of that, a new simulation program needs to be built each time for a different specification, and the system developer must also be familiar with the simulation techniques - which is not always the case.

The currently available design methods/tools (such as the *Unified Modeling Language* or UML [18, 31, 63, 64]) do not provide a way to automatically generate simulation programs from the specification. There has been some effort in eliminating this shortcoming in areas outside UML, such as in the Rapide [53, 54] and DisCo [40] projects, but at the time this Ph.D. project started, there was no tool available yet that is able to transform a system specification in UML (with certain performance requirements) into a simulation program. Since then, there have been some effort trying to address the lack of performance prediction features in UML, such as the work by the PERMABASE project [1-3, 72], Pooley and King [62] and Bondavalli et. al [15].

The aim of this Ph.D. study was therefore to produce a tool or method that allows software performance prediction to be incorporated into the UML design specification. To achieve this goal, the tool should be able to generate simulation programs from UML design specification without the necessity of the system designers to know how to code a simulation program. This tool should be suitable for a variety of system applications and will allow different performance requirements to be incorporated in the simulation.

#### **1.2. Related Work**

There have been some projects trying to incorporate software performance prediction into system design/specification by tackling the problems from many different angles. In relevance to my Ph.D. work, these related projects can be divided into two main

categories: those that do not use UML at all and those that use UML (to some degree) for specifying a system. The second has only emerged recently (since around 1999) and the number of projects that fall into this group has grown quite rapidly.

#### 1.2.1. Related Work outside UML

#### Rapide

*Rapide* is a computer language for defining and executing models of system architectures [53]. It introduces an *interface connection architecture* which means that all communication between modules is explicitly by connections between interfaces. Here, an architecture consists of a set of *specification modules (interfaces)*, a set of *connection rules* (for defining the communication between the interfaces), and a set of *formal constraints* which determines whether a pattern of communication is legal or illegal.

A *component* consists of a *module* and its *interface*. A module either encapsulates an executable prototype of the component or it describes the hierarchical architecture of the component (when a component is composed of other components). An interface defines what a module requires-from or provides-to other modules and connections are defined between the features in interfaces.

The Rapide language is accompanied by a set of tools which help in the specification, design and testing of software modules and architectures. In general, the Rapide language is composed of five sublanguages:

1. *The Type Language*: describes the interfaces of components. It supports object oriented and abstract data type styles of defining interfaces as well as multiple interface inheritance.

- 2. *The Pattern Language*: provides a general language for defining event-based reactive constructs or dynamic architectures.

- 3. *The Executable Language*: is used for writing executable modules which are defined by a set of processes which observe and react to events.

- 4. *The Architecture Language*: models interface connection architecture and it defines dataflow and synchronisation between modules.

- 5. *The Constraint Language*: provides features for specifying formal constraints on the behaviour of components and architectures.

The feature provided by Rapide is very extensive and Rapide provides a simulation tool using an event-based execution model or POSET (partially ordered set of events).

#### DisCo

*DisCo* (Distributed Co-operation) is a formal specification method for reactive systems which incorporates a specification language, a methodology for using this language for building specifications, and a tool for supporting the methodology [40].

It focuses on the collective behaviour of the objects, i.e. how they cooperate with each other. As well as supporting an object oriented approach, DisCo is based on the joint action approach which concentrates on the *interaction* between different components instead of the components themselves. This increases the level of abstraction, i.e. the bias towards particular hardware and software architecture is minimised.

The DisCo language supports modularisation (due to its object oriented paradigm) and incremental specification (which means that the level of the specification's details can be gradually increased until the desired level is met). A

DisCo specification consists of a set of *layers* (which are composed of classes and actions). New layers can be constructed by composing two or more separate layers or by refining existing layers (*superposition*).

The DisCo tool provides a way to validate a specification by using animated simulations. Animation makes specifications much more understandable and promotes communication between the people involved. The DisCo tool also supports graphical representation of execution scenarios (*Message Sequence Charts*). A short tutorial on DisCo is available at [46].

#### **AUTOFOCUS**

AUTOFOCUS is a tool prototype for the formally based development of reactive systems [36] - mainly in the area of distributed systems. It supports system development by offering integrated, comprehensive and mainly graphical description techniques for specifying both different views and different abstraction levels of the system. There are four different description techniques provided to cover the different views on the system:

- *System Structure Diagrams* (SSDs): describe the static aspects of distributed systems by viewing them as a network of interconnected components with an ability to exchange messages over their communication channels.

- *Data Type Definitions* (DTDs): represent the types of the data processed by a distributed system in a textual notation.

- *State Transition Diagrams* (STDs): describe the dynamic aspects, i.e. the behaviour of a distributed system and its components.

- *Extended Event Traces* (EETs): provides extra behavioural view of a distributed system (on top of STDs) through exemplary runs from a component-based view.

AUTOFOCUS supports component-oriented development of systems, where a component represents a structural part of the system, possibly described by different views using the description techniques above, which allow different levels of system granularity to be specified.

AUTOFOCUS uses prototyping and simulation approach for observing and validating the properties of a system being developed. To support this approach, AUTOFOCUS provides a tool component called "SIMCENTER" that facilitates:

- the generation of executable prototypes of systems or parts thereof,

- the execution of these prototypes in a simulation environment,

- the visualisation of the runs using the same description techniques as used for designing the system, and

- an optional connection between the simulation environment and third-party frontends such as multimedia visualisation tools or external hardware systems.

Both AUTOFOCUS and SIMCENTER are written entirely in Java programming language.

#### Architectural Modelling Box (AMB)

AMB is a modelling and design language that provides a unified basis for the design process as well as functional and quantitative analysis [44]. The aim of this project is to bring together the worlds of system designers and performance modellers by introducing a design language that includes quantitative properties of systems.

AMB is formed by a graphical language that models systems, their behaviour as well as other relevant data. In general, AMB models consist of two parts:

• *resource* or *entity* model: describes the *static* aspects of the system, i.e. its components, their physical properties and the way they can interact.

• *behaviour* model: describes the *dynamic* aspects, i.e. the processes or actions performed by the system, in terms of related activities.

Specifications written in the AMB design language can then be automatically translated into models for performance analysis (such as *graph models*, *timed Petri nets* or *hybrid models*) or for functional analysis. More "traditional" performance modelling formalisms (such as regular queueing networks or quantitative simulations) are not suitable for AMB's purpose because their expressive power is too limited to describe most of the aspects that AMB users are interested in.

#### 1.2.2. Related Work using UML

#### PERMABASE

The Performance Modelling for ATM Based Applications and Services (PERMABASE) project [1, 3, 72] was carried out by British Telecom and the University of Kent at Canterbury. The aim of this project is to provide performance feedback as part of the object-oriented design process for distributed systems through an automatic generation of performance model directly from the system design model.

This project tries to address the lack of use of physical environment (hardware) specification in distributed system designs. There are four model viewpoints identified here:

- 1. *Workload Specification*: specifies the "work force" (human operators or other systems) that drives the system; this includes classes of components considered as external to the system.

- 2. *Application Specification*: specifies the classes of components that constitute the software or logical behaviour of the system, i.e. the system logic components (software, firmware or hardware logic).

- 3. *Execution Environment Specification*: identifies classes of components that are physical components providing the resources used by the application during system operation, e.g. processors, networks and other resources that the system operates over.

- 4. *System Scenario*: defines the instances of declared components (of the three above) and the connections between them, which form a specific system architecture or configuration.

By combining the specifications of each of the viewpoints above, a *Composite Model Data Structure* (CMDS) of the entire system is obtained. The CMDS can then be checked for consistency and translated into a discrete event simulation or performance model of the system.

This project tried to use, and adapt if necessary, the UML notations for the representation of the four domain specification areas. For example, the Execution Environment Specification can be described using the *class* diagram, while the System Scenario view can be represented using the *deployment* diagram.

As a follow on from the PERMABASE project, Akehurst and Waters propose a list of UML deficiencies with respect to performance modelling [2].

#### **Pooley and King**

The goal of this work is to integrate performance estimation with the system design process [62]. It was suggested that successful effort toward this goal most likely come from projects that attempt to build performance analysis directly into accepted design method such as UML.

The UML *sequence* diagrams were initially thought to have the potential to generate and display useful information relating to performance. In the end, it was

decided that the sequence diagrams are more suited to being a display format rather than a detailed behavioural specification format. It is mentioned that the sequence diagrams have been used as traces of events generated from a simple discrete event simulator. The work have also found a mapping from the *deployment* diagram to queuing models, and have built a simulation library around *collaborations* with *state machines*.

The challenge lies in setting the foundation for an integrated performance engineering approach on the whole UML notation. The use of collaboration diagrams with embedded state machines seems very promising, as well as its extension to incorporate collaborations within deployment diagrams.

In a follow on paper [48], King and Pooley describes how UML designs can be transformed systematically into Petri nets. The UML diagrams of interest here are the *collaboration* and *statechart* diagrams, and the target of the transformation is Trivedi's SPNP [24] tool's variant of stochastic Petri nets. Further exploration of systematic mappings from UML is undertaken by developing a graphical front end. The possibility of employing layered queueing networks (on top of Petri nets) as the targets of UML transformation is also being investigated.

In [60], Pooley outlines a roadmap that shows how software performance can be integrated with software engineering process. Performance engineering is described as an experimental approach to predicting the likely performance of systems. It can involve building and monitoring the system under the workloads of interest, or using models to represent the system. Modelling has many advantages over building/monitoring, which makes it used in most of the work of interest to software engineering.

The challenge is to bring the worlds of software engineers and performance analysts together, which can be achieved by embedding performance analysis techniques into design methods and tools. As UML is rapidly being adopted as a design standard, the focus of the work should be on expanding or augmenting UML to allow performance related information to be incorporated into its design notation.

#### Bondavalli et.al.

This work aims to extend UML design toolkits with automatic dependability analysis tools to evaluate the various dependability attributes of the system under design [15, 16]. It is part of a European ESPRIT project called *HIDE* (High-Level Integrated Design Environment for Dependability) and one of the tools created in this project deals with an automatic transformation of UML diagrams into Timed Petri Net (TPN) models, which allow the modelling of activities whose duration is a random time.

The UML diagrams of interest here include mainly the structural diagrams, such as the *use case*, *class*, *object* and *deployment* diagrams, as well as behavioural diagrams, such as the *statechart* diagrams. Since standard UML does not include a notation for dependability aspects, it is necessary to provide minor extensions through standard extension mechanisms: *tagged values* and *stereotypes*. Tagged values are pseudo attributes assigned in the form of a pair "tag = value", while stereotypes introduce a high-level classification (meaning/usage) of model elements. The transformation of the relevant UML design diagrams into TPN models is performed in two stages:

#### • from UML to the Intermediate Model

First, the elements and relations of the UML design are projected into the Intermediate Model (IM), which is used to capture the dependability related

information. The IM is defined as a *hypergraph*, where each *node* represents an entity described somewhere in the UML structural diagrams, and each *hyperarc* represents a relation between the elements/nodes. IM nodes have a set of attributes attached to them, which describe their fault activation and repair process as well as the propagation process for a hyperarc. In other words, the IM is built by projecting the UML entities into IM nodes, and the structural UML relations into IM hyperarcs.

• from the Intermediate Model to TPN models

The hypergraph representing the IM is examined, and from there, a set of subnets for each IM element is generated. The TPN model can then be derived from all these.

More details on this tool, especially on the generation of the TPN models and the suitable Petri Net environments/tools can be found in [15].

#### Kähkipuro

In [45], Kähkipuro presents a framework for creating, using and maintaining performance models of object-oriented distributed systems. The architecture of this performance modelling framework consists of four main elements:

• The method of decomposition (MOD)

It provides the foundation of the framework by defining an algorithm for finding an approximate solution for performance models.

• UML based performance modelling techniques

These techniques provide the means for modelling complex information systems by using abstraction for separating application level issues from the use of technical resources. • Performance modelling methodology

This provides a link to the software engineering process by indicating how the proposed UML modelling techniques can be used at different stages of system development to produce useful performance models for the system.

• *Object-oriented performance modelling and analysis tool (OAT)*

The purpose of this tool is to automate some of the tasks required by the framework, such as:

- the transformation of UML based performance models into a format that is solvable by the MOD algorithm,

- the implementation of the MOD algorithm to produce an approximate solution for the performance model,

- the conversion of the solution into a set of relevant performance metrics that will be used in the performance modelling methodology.

There are four performance model representations used, each with its own notation and the mappings between them are defined by the framework architecture:

- 1. UML representation: describes the system with UML diagrams.

- 2. *PML representation*: provides an accurate textual notation for representing performance related items in the UML diagrams. The purpose of this representation is for filtering out the UML information that has no significance for performance modelling.

- 3. *AQN representation*: describes the system in an augmented queueing networks format that may contain simultaneous resource possessions and allows the MOD algorithm to solve the model.

4. *QN representation*: consists of separable queuing networks with mutual dependencies that correlate them to the same overall system.

The UML notations employed in this work are the *class* diagrams (for deriving the resources or queues), as well as the *collaboration* and *sequence* diagrams, which are used in conjunction with one or more workload specifications to describe the behaviour of the application and the infrastructure of the system. It is mentioned that the state and activity diagrams could also be used for expressing the performance related information conveniently.

#### Cortellessa and Mirandola

The work by Cortellessa and Mirandola [26] also attempts to provide an automatic translation of UML diagrams into a queueing network based performance model. The goal is to complement the UML notation with a methodology that encompasses the performance validation task (which includes model generation and validation) as an integrated activity within the development process.

The target performance model is based on the Software Performance Engineering (SPE) methodology, and composed of two parts: the *Software Model* (SM) based on *Execution Graphs* (EG); and the *Machinery Model* (MM), based on *Extended Queueing Network Models* (EQNM). By combining SM and MM, a complete (parameterised) EQNM based performance model is obtained, which is then solved using some well-known techniques.

The methodology outlined in this paper uses three main UML diagrams for extracting performance related aspects and integrating them into performance model:

- Use Case Diagram: for deriving the user profile and the software scenarios,

- Sequence Diagram: for deriving an Execution Graph,

• *Deployment Diagram*: for deriving an EQNM and to identify the hardware/software relationships that improve the accuracy of the performance model.

This methodology is yet to be implemented as a tool, and to achieve this, the authors believe that there are two steps to take:

- choosing an appropriate syntax to represent the UML diagrams involved (and perhaps some supporting data structures),

- studying the underlying syntax of the existing SPE tools in order to ease the translation from UML notation to a performance model representation.

#### Hoeben

This work developed a prototype tool that is able to translate a UML model of a system into a queuing network representation, which is then used to calculate the system's response time and utilisation [33].

The UML *use case* diagrams are used for capturing the tasks that the system has to complete (i.e. its workload), and the tool will calculate response times for each of these tasks. The *interaction* diagrams (i.e. the *sequence* and *collaboration* diagrams) provide the translation of user tasks to hardware resources. In order to avoid the diagrams becoming too big, multiple interaction diagrams are used to get the entire decomposition, where each diagram represents the behaviour of a single method. The *class* and *component* diagrams are not of great importance for performance estimation, but they are used to model information that is later used to understand the dynamics of the system. The *deployment* diagram convey the properties of the processors and network connections, which are useful in performance estimation. More information needed for performance estimation can be supplied using the standard extension

mechanisms, i.e. *tagged values* and *stereotypes*, but this only shows that there needs to be a more robust way for incorporating performance related information into UML design.

#### de Miguel et. al.

This paper introduces UML extensions for the representation of temporal requirements and resource usage and their automatic evaluation [27]. The interest of this work is on the specification of architecture and requirements of real-time systems, which pays special attention to timeliness, performance and schedulability.

Standard UML extension techniques (constraints, stereotypes and tagged values) are used for specifying a UML *profile* where they collectively specialise and tailor UML for specific domain process. *Constraints* represent specific semantics of modelling elements with linguistic notations, *stereotypes* define new metamodel constructors, and *tagged values* identify new parameters or information associated with the modelling elements.

UML diagrams are used as input for the automatic generation of scheduling and simulation models. The diagrams employed include the *class*, *collaboration* and *activity* diagrams. There are two tools used: *Analysis Model Generator (AMG)*, which implicitly defines a middleware model that affects the scheduling analysis; and *Simulation Model Generator (SMG)*, which allows an automatic generation of OPNET model.

#### **1.2.3.** Relevance to this thesis

We believe that software performance can be predicted using simulation approach. This belief is also shared by some of the related work above, and more discussion on simulation concepts and methodology is given in Chapter 3. The work by Bondavalli et. al. [15, 16] shows that the transformation from UML design notation into a performance model (in their case, it is a timed petri net) can be done in two stages. The first stage gathers information that is relevant for performance estimation from the UML notation, which is then stored into an *Intermediate Model*. The second stage converts the Intermediate Model into the desired performance model, which can then be evaluated and analysed to give the performance prediction. We consider our SimML framework (see Chapter 4) to serve the similar purposes as those of the Intermediate Model. The implementation of the SimML tools also follows the two staged approach, as illustrated in Chapter 5.

The SimML framework is also comparable to the PML (Performance Modelling Language) mentioned in [45]. The difference is that the goal of the SimML framework is for building simulation programs, while the PML framework aims to produce a performance model using queueing networks.

The importance of an ability to estimate the performance of a system (software) during its design stage is highlighted by the existence of workshops dedicated specifically for this topic, such as the one day workshop on *Software Performance Prediction extracted from Designs* held at the Heriot-Watt University in Edinburgh [47] and more recently, the *International Workshop on Software and Performance* (WOSP 2000) held in Ottawa, Canada [76]. These indicate that research on the approaches for incorporating software performance into software engineering/design is still an ongoing process and deemed useful so that it may provide many benefits for the software engineering community.

#### 1.3. Chapters Plan

The rest of this thesis is arranged as follows:

- Chapter 2 gives a brief introduction on software design, with the emphasis on the Unified Modeling Language (UML), which has become the standard notation for specifying software system.

- Chapter 3 presents the basics of stochastic simulation, which can be used in predicting the performance of a system before its is being constructed. This chapter also introduces two simulation languages/packages called C++SIM and JavaSim, which provide the simulation environments for this project.

- Chapter 4 outlines a framework called the Simulation Modelling Language (SimML) that has been constructed in this Ph.D. study and represents the core of the work. The SimML framework serves as a bridge that enables an automatic generation of a simulation program directly from a UML design specification.

- Chapter 5 discusses the implementation of two tools that can perform the automatic construction of simulation programs from UML notations using the SimML framework. The first tool is a PERL parser that is able to transform a textual representation of UML using the SimML framework into C++SIM programs; this tool serves as a pilot project to test whether the ideas presented in the SimML framework are workable or not. The success of the first tool led to the implementation of the second tool in Java that allows graphical UML notations to be transformed into JavaSim programs.

- Chapter 6 shows some case studies that have been performed to evaluate the usefulness of the tools described in Chapter 5, especially the second one.

- Chapter 7 provides some concluding remarks of the overall project and outlines some areas into which the project could be extended or researched further.

## **Chapter 2**

### **Designing a Software System**

#### 2.1. Introduction

The advancement of computer technology demands new systems to be built. New requirements are discovered and new, more efficient methods are available. The problem is that the requirements are usually presented in a plain language and hence they may contain many ambiguities. This may lead to a mismatch between the completed system and the proposed system as required by the customer.

It is therefore important to ensure that the system developer understands clearly what the system requirements are. To do this, the requirements must be transformed into a notation that can only be interpreted in one way and accepted universally. A formal method, such as VDM [43] or Z [50] is one possible candidate, but it is often too complicated and difficult to employ this method because it requires a good mathematical skill and a thorough analysis.

An alternative way is to use one of the design methods available in the area of Object Oriented Technology, such as the Coad/Yourdon [25], Booch [17], Object Modeling Technique (OMT) and OOSE methods (all briefly mentioned in [29]). The availability of several design methods brings the consequence that there is no standard design notation, i.e. a specification written/drawn in one method might not be understood by some system developers who normally use a different method. In around 1995, a new design method was developed by the people behind the Booch, OMT and OOSE methods with an aim to standardise the design notation. This method is called the Unified Modeling Language (UML) [18, 28, 29, 31, 63, 64] and it has been accepted as the standard modeling language by the Object Management Group (OMG). The rest of this chapter introduces UML by discussing the design notations available, why UML becomes popular and identifies things that are still missing from UML.

#### **2.2. Unified Modeling Language**

*Unified Modeling Language* (*UML*) is a language for specifying, visualising, constructing and documenting the artifacts of software [63]. It uses graphical notations to illustrate a system specification, and since the specification is usually very complex, there are several diagrams available to provide different views of the proposed system:

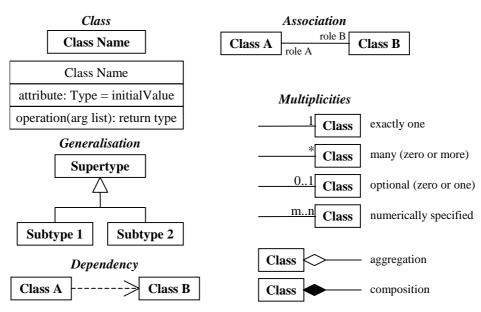

#### 1. Class diagram

A class diagram represents the static structure of a system which includes the static elements (*objects* or *classes*) of the system and the static relationships between them. A class represents a set of objects with similar structures (*attributes*) and behaviour (*operations*). Two or more classes can have a relationship between them and the relationship can be:

a) an association.

An association indicates the role a class plays in the relationship. On top of that, there are some additional notations available for the association, such as the *multiplicities* (which indicates how many instances a class can have in the association), *aggregation* (to show that one class is a collection of several

instances of the other class), *composition* (one class is a part of the other class) and *dependency* (to indicate that one class depends on the other).

b) a generalisation.

This captures the notion of *inheritance*; it shows the relationship between a more general element (the *supertype*) and a more specific element (the *subtype*). The subtype inherits the properties of its supertype and it may have some additional (more specific) information.

The notations for the class diagram can be seen in Figure 2-1.

Figure 2-1: The Class Diagram notations

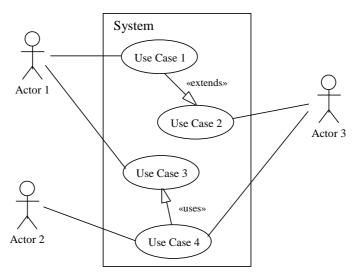

#### 2. Use Case diagram

It is often important to investigate the relationships between a system and its users. A use case diagram describes the functional requirements of a system and the interaction between the *actors*, the system modelled and the *use-case*. The actors could be human users or other computer systems, and they are the ones who carry out the use cases. A use case is a set of sequences of actions performed by the system that yield an observable result of value to a particular actor [29]. The use cases can have some relationships among them. The two most common ones are the *extends* and *uses* relationships: the *extends* relationship illustrates a use case that is similar to another use case, but it does a bit more, while the *uses* relationship indicates that one use case is using the features of the other use case (i.e. to avoid repeating the description of a same behaviour). The UML notation for the Use Case diagram is shown in Figure 2-2.

Figure 2-2: The Use Case Diagram notation

#### 3. Interaction diagram

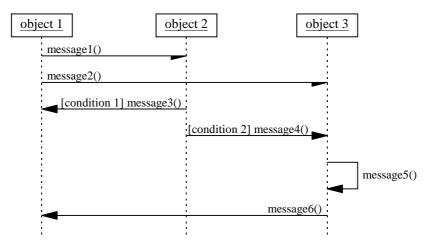

Interaction diagrams show the pattern of interactions between objects in a system. An *interaction* consists of *messages* that are exchanged among *objects* in order to achieve the desired result of an operation. There are two types of interaction diagrams:

a) Sequence diagrams: show the interactions in a time sequence.

In the sequence diagram, the objects are arranged horizontally (on top of the diagram) while the time line is shown vertically (normally proceeds down the page), one for each object. A message is represented by an arrow between the time lines of the objects, although in some occasion, an arrow can point to its own time line to indicate self invocation. An asynchronous message is

represented by a half-arrowhead. Conditions can also be included to indicate that the message is only sent if the conditions are satisfied. Figure 2-3 shows how the sequence diagram can be represented.

Figure 2-3: The Sequence Diagram notation

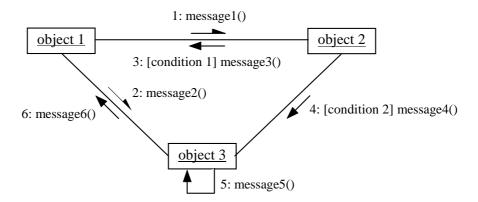

b) *Collaboration diagrams*: show the interaction in term of links between the objects.

As in the sequence diagram, objects are represented as icons (boxes with the objects' name underlined) and they interact with each other by exchanging messages. But there is no time line on the collaboration diagram, instead, the messages are given numbers to indicate their ordering. This makes it more difficult to see the sequence of messages, but on the other hand, the collaboration diagram makes it easier to see how the objects are linked together (Figure 2-4).

Figure 2-4: The Collaboration Diagram notation

#### 4. State diagram

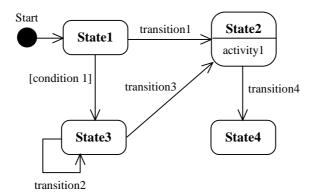

Every object has a *state* which can change if something (an event) happens to it. The state diagram describes the states that an object can get into and the interactions (*actions* and *activities*) that are involved to change the state. An action is associated with a *transition* (i.e. the changing from one state to another) while an activity is associated with the states. Figure 2-5 shows how a state diagram is represented in UML.

Figure 2-5: The State Diagram notation

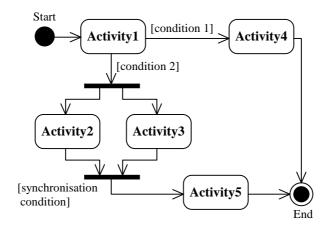

#### 5. Activity diagram

This diagram represent the activities that are triggered at the completion of an operation. An activity diagram is a variant of a state diagram but it emphasises on the actions, i.e. the activities that are performed to change the object states and the results of those activities (see Figure 2-6).

Figure 2-6: The Activity Diagram notation

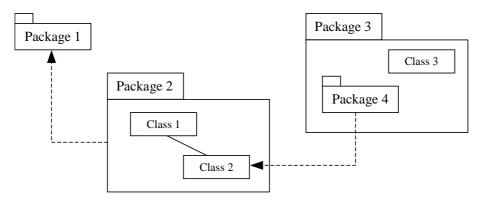

#### 6. Package diagram

As systems get more complex, it becomes more difficult to understand their structure, unless they are broken down into smaller manageable pieces or subsystems. A package diagram shows how system's classes are grouped together, along with the dependencies among them (Figure 2-7). This kind of diagram is useful when there is a large number of classes that are closely linked or depend on each other, so that they might be bundled together into higher level units.

Figure 2-7: The Package Diagram notation

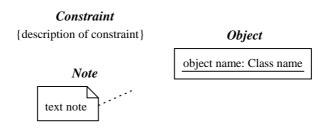

There are also some additional diagrams that can be used to provide more detailed explanation by adding notes or constraints (see Figure 2-8).

Figure 2-8: Other useful UML notations

UML has gained a wide acceptance since its introduction in 1995 and it has become a popular choice when it comes to selecting a design method. There are some reasons for this:

• The notations employed by the UML are reasonably simple yet they are powerful enough for complex specifications.

• It is an industry standard, so its notation will be understood by many people.

There are several tools available that make the job of drawing the UML diagrams easier, such as the *Rational Rose* tool [63], Together [59] and Argo/UML [71]. Each of these tools has its own benefits and drawbacks, but there is one thing that these tools - or UML in general - are still lacking, which is mentioned in the next section.

#### 2.3. UML and System Performance

UML helps the system developer to understand the specification better through multiple design diagrams. But UML cannot answer a question on how a particular design will perform. This is because UML does not incorporate performance related issues into its diagrams/notations. The problem is, it is often necessary to know beforehand whether a design will deliver its performance requirement or not, or whether one scenario will give a better performance than another.

There has been some work done in an attempt to predict a system's performance before the system is built. The PERMABASE project [1, 3, 72] puts the emphasis on the UML Implementation diagrams, namely the Deployment and Component diagrams to derive a system's performance model. The performance model can then be simulated using either using a *discrete event simulation* (DES) engine of SES/Workbench, or Coloured Petri-nets.

The work by Pooley and King [62] addresses the need to integrate performance engineering into software engineering. The general approach adopted in this work is to use UML designs as directly as possible in performance evaluation. The performance evaluation itself is obtainable using simulation methods or queuing network modelling approaches. In [15], Bondavalli *et. al.* describes a transformation from structural UML specification (mainly the Use Case and Deployment diagrams) into *Timed Petri Net* (TPN) models for the quantitative evaluation of dependability attributes.

These three are just some of the work attempting to incorporate software performance prediction into UML, more work that has been done along the similar line is outlined in Chapter 1.

The amount of related work done in the performance prediction area suggests that it is a useful thing to do with regard to UML. Our approach in tackling this problem is by using a simulation program to mimic the execution of the real system, hence enabling the system's performance to be analysed and calculated beforehand. This involves the generation of a simulation program from UML design specification, and this approach is discussed in the following three chapters. First though, it is appropriate to introduce the concept of simulation, which is covered in the next chapter.

## **Chapter 3**

### **Simulation to Predict System's Performance**

#### 3.1. Introduction

Predicting the performance of a system that is yet to be built is not a trivial task. First, it is necessary to determine which aspects of the performance are to be measured, such as reliability, availability, response time, etc. This is important because different system applications demand different performance requirements, for example, a telephone system needs to be highly available while a flight control system has more emphasis on its reliability. From there, a *workload* that the system will face can be determined. A workload typically includes the operations that are needed to be performed by the system, the time needed for each operation to be completed and the frequency of each operation. This is not an exhaustible list as more aspects are often considered depending on the system's requirement.

A system's workload specification needs to be analysed in order to obtain an estimate for the system's performance. There are several ways to predict the performance of a system based on its workload specification. One way is through an analytical method where the system's workload is derived mathematically by constructing a number of parameterised mathematical equations that approximate the workload characteristics of the system's components. This approach is often called *modelling* and it is explained in great detail in [49, 56, 57]. An example of how modelling is used for examining workload specification analytically is the MaStA (**Ma**ssachusetts **St** Andrews) cost model [65-67]. This was developed for modelling

the recovery of database systems. The MaStA model is used for comparing the performance (the cost) of several recovery mechanisms which are executed on different platforms to ensure that the performance is platform specific. The workload here is determined by the number of I/O operations involved in a particular recovery mechanism. The I/O operations can be divided into constituent independent I/O categories, such as data reads or commit writes, and the overall cost of a mechanism is equal to the sum of the costs of each category.

The analytical method requires a good mathematical knowledge and calculation, so it is valuable in a simple system but usually impractical or very difficult to use in a complex system. Another way of predicting system's performance is through *simulation*. This approach requires the construction of programs that capture the characteristics of the proposed system. Among other things, these characteristics include the workload of the system, which determines the simulation's results. The workload specifications can then be considered as the simulation's parameters, i.e. they must be known before the simulation can be performed. As with the analytical method, the simulation method requires some simplifying assumptions to make it easier to employ.

One feature of the simulation method is that it allows probabilistic nature of events or activities to be observed. This is a very important feature because a computer system, especially a distributed one, involves a lot of events that can happen at random, such as the system failures, the latency in the connections, job arrivals, the response times, etc. By knowing its probability or distribution function, an event can be modelled close to its real world counterpart. Running the simulation program with the parameters from the workload specification provides some data about the states of the system. These data reflect how the system cope against a particular load, and by performing further calculation and analysis on the data, we can predict the performance of that system.

The rest of this chapter introduces the basic concepts of simulation, its benefits and drawbacks - which motivate the work presented in this thesis, as well as the different simulation types encountered. This is then followed by an overview of the simulation environments (languages or packages) available, in particular those which were used in this thesis.

# **3.2. Simulation Basics**

## 3.2.1. What is simulation?

Simulation is "the imitation of the operation of a real-world process or system over time" [13]. The aim of simulation is to describe and analyse the behaviour of a system and explore the possible scenarios that can happen in the system (the "what-if" questions). Simulation allows different system designs to be investigated, and by analysing the simulation results, the performances of these systems can be compared. Therefore, simulation can be used as a decision making aid in choosing which system is to be implemented.

There are several underlying concepts in simulation, and in order to provide a better simulation understanding, these concepts or terminology are explained below:

- *model*: is a representation of an actual system.

- *system*: is a collection of entities which interact with each other, within some notional boundary, to produce a particular pattern of behaviour [14].

- *entity*: represents an object/component (with its interactions) that are considered important enough to be included in the model.

- *attribute*: a variable declared inside an entity/object, which describes the state of that entity.

- *system state variables*: the collection of all attributes of all entities. It is used to know what is happening within a system at a given point of time.

- *sample or operation path*: a realisation of system state variables. One simulation run generates one sample path and another simulation run of same system with different random numbers generates a different sample path of the same system.

- *event*: a change in the system state during the course of the sample path.

- *event time*: time at which an event occurs.

Simulating a system essentially means generating a sequence of event times with their appropriate events. How these event times are organised leads to several simulation types (see Section 3.2.3), but in general, the structure of a simulation run can be divided into three separate stages [14]:

#### 1. Initialisation.

This stage sets up the simulation model by obtaining the simulation parameters from the user. The system state variables (the variables for obtaining the simulation statistics) are declared and initialised in this stage.

#### 2. Dynamic stage.

The dynamic stage sets the model in motion, where the model is allowed to perform its dynamical behaviour until a fixed period of simulation time has elapsed or until a particular condition has been met (which is set in advance). Here, the system state variables are updated in a pre-determined way.

#### 3. Termination.

After the simulation run is completed (i.e. after the second stage above is finished), it is necessary to collect the system state variables, which are then analysed in order to work out the simulated system's performance.

These three stages serve as the skeleton for constructing simulation programs, whose details differ one from another according to the type of simulation they are meant to perform.

#### 3.2.2. Advantages and Disadvantages of Simulation

Modelling a system through simulation means replacing that system with one that is simpler and/or easier to study, yet equivalent in all important aspects. This is not an easy task to do, so it is a good idea to compare the advantages and disadvantages of simulation before we proceed any further.

#### Advantages

There are many advantages of using simulation, some of which are listed here:

- 1. It allows us to perform a controlled experiment upon the system by varying the simulation parameters. We can therefore investigate how the system will react under certain circumstances without committing the resources for implementing that system (which in the end might not be suitable).

- 2. Time can be compressed or expanded within the simulation, which means that we can thoroughly examine the states of the system in a suitable time frame.

- 3. There is a separation from the real system, i.e. the simulation will not disturb the operation of a real system (if there is one already running).

- 4. It can serve as an effective training tool.

- 5. Simulation can be used to diagnose problems that might occur in the system (e.g. a bottle-neck in a particular stage of the operation), hence a remedial action can be taken.

- 6. It helps other people to understand how the system works.

#### Disadvantages

Inevitably, there are some disadvantages that must be faced:

- 1. Building a simulation program is quite a difficult task and it often requires some specialised skills.

- 2. Interpreting the simulation results is not easy either.

- 3. It could be a time consuming and expensive: a new simulation program needs to be built for a different system.

- 4. Model parameters may be difficult to initialise. It is often necessary to obtain them from some experimentations or time-extensive analysis.

There are efforts in eliminating these disadvantages, for example, there exist some specialised software for simulation (*simulators*). Most of these tend to be commercial software that come with output analysis and/or animation tools, so they are generally expensive to purchase.

The work discussed in this thesis tries to solve the first and third disadvantages above by providing a tool that can be used for transforming a design notation automatically into simulation programs.

## **3.2.3.** Types of Simulation

Based on the ways the system states change during the simulation run, it is possible to categorise simulation model into three types:

- 1. *Discrete time*: the system is only considered at selected moments of time, which are usually evenly spaced. Only at these moments (called *observation points*) are the changes of the state recorded.

- 2. *Continuous time-continuous event*: the system states vary continuously with time; this kind of system is usually described by sets of differential equations.

- 3. *Continuous time-discrete event* (or more popularly termed just as *discrete event* simulation): the time is continuous but the state variables change only at those discrete observation points in time at which events occur. These observation points do not need to be equally spaced and can be of arbitrary increment. This kind of simulation is the one that is most commonly encountered.

The classification above takes into account the relation between the simulation events and the simulation time, which can be seen diagrammatically in Figure 3-1.

| avant | Discrete   | 1            | 3          |

|-------|------------|--------------|------------|

| event | Continuous | Not Possible | 2          |

|       |            | Discrete     | Continuous |

|       |            |              |            |

|       |            | time         |            |

Figure 3-1: The classification of simulation type based on events and time

A simulation consists of a series of interacting events that constitute the sample or operation path. Therefore, a *simulator* can be defined as a program that is devoted to the generation of operation paths [58]. It permits the creation of events, whose interactions are controlled in a timely manner using the internal clock. The simulator keeps an *event list* - the list of events that are scheduled to be executed at certain times during the simulation. Based on the approach on how the simulator schedules the events in producing the operation path (i.e. how the event list is organised), there are two types of simulation:

#### 1. event-oriented simulation.

Each event has an *event notice* which contains both the event's *type* and *time*. Each event type is in turn associated with a procedure which performs the actions required to handle that particular type of event, which include the scheduling of the next event of this type as well as the collection of the statistics. This procedure is invoked every time an event of the relevant type occurs.

There is also a *clock procedure* that controls the simulation by scanning the event list, finding the event notice with the smallest time (which is executed next), updating the simulation time and invoking the relevant event procedure. The event manipulations are therefore explicit. The operation path is obtained by taking a global view of everything that happens in the system.

#### 2. process-oriented simulation

A process is defined as a sequence of events where each event is accompanied by a set of actions. Each process is given an independent thread of control, so the management of events is implicit in the management of the processes. Hidden from us, there is still a clock that is advanced from event to event, as well as an event list which shows what is scheduled to happen at a particular time. The difference is that the event list now contains processes, ordered according to the time of the next events in their respective sequences. Each process keeps track on which action of its set is to be executed next.

Each time after the clock is advanced, the actions of the processes at the head of the event list are executed. If there are more than one process scheduled at the same time, the actions of all those processes are executed, in the order in which they appear in the list. The operation path of a process-oriented simulation is therefore obtained by the interacting of a number of processes running in (pseudo) parallel. More explanation on this kind of simulation is given in the discussion of the C++SIM package (Section 3.3.1). The rest of this thesis refers to the *process-based discrete-event* paradigm when discussing simulation.

# 3.3. Simulation Languages/Packages

A simulation program can essentially be built in any general purpose programming languages but this usually requires more effort. A simulation language/package aims to make the process of writing a simulation code easier by providing some of the standard simulator components as its language primitives or types. Overall, there are five facilities that a simulation language needs to provide [58]:

1. Entity manipulation.

This allows the creation and destruction of entities, as well as placing/removing them to/from their respective sets (stacks, queues, etc.).

2. Time and Event manipulation.

The task involves the maintenance of a clock and an event list, plus all the scheduling operations, such as finding the next event, removing current event and inserting a new event.

3. Random Numbers.

We talk about pseudo random numbers here, i.e. sequences of numbers that appear to be independent and randomly distributed. The simulation language needs to provide various discrete and continuous distributions and able to reproduce and change the sequences for different runs of the same simulation program.

4. Collection of Statistics.

This deals with the collection of data that can be used to work out the quantities of interest in the simulation.

5. Numerical computation.

It is often necessary to be able to implement various numerical algorithm which is useful for analysing the simulation results and generating specific random numbers.

The task of writing simulation programs can be made easier by using certain languages or packages that support the essential simulation features outlined above. There are several simulation environments that can be employed, but many are commercial ones, which tend to be very complex and often come with some animation tools. What is required for this project is just a simulation environment that supports the process based, discrete event simulation paradigm, such as SIMULA [61], Modsim [21], SimJava [34, 35], C++SIM [11, 52] or JavaSim [51]. The work illustrated in this thesis uses C++SIM and JavaSim, so the basic concepts of these two packages are given in the following sub-sections.

#### 3.3.1. C++SIM

C++SIM provides a discrete-event, process-based simulation facilities similar to SIMULA's [61] simulation class and libraries. It is written in standard C++ and since C++ compilers typically generate code which runs faster than similar SIMULA code, C++SIM would produce more efficient simulation codes.

The C++SIM environment uses active objects as the units of simulation. An *active object* is an object which has an independent thread of control associated with it, and it is used to convey the notion of 'activity' to the processes involved in the simulation. Active objects are created using threads (lightweight processes) and in C++SIM, they are used for:

#### 1. Simulation Scheduler

Simulation processes (see later) are managed by a scheduler and are placed on a scheduler queue (the event list). Figure 3-2 shows how a tree structure is used to organise the scheduler queue. Each node represents a process and the nodes at the same level of the tree have the same simulation time. Here, the processes are executed in a pseudo-parallel mode, i.e. only one process is activated at any instance of real time, but the simulation clock is only advanced when all processes have been executed for the current instance of simulation time.

**Figure 3-2: Simulation Queue**

Inactive process are placed into the scheduler queue and when the currently active process yields control to the scheduler (either because it has finished or been placed back onto the scheduler queue), the scheduler removes the process at the head of the queue and activates it (Figure 3-3). When there is no process left in the scheduler queue, the simulation will terminate. Please note that every simulation must start one scheduler before the simulation can begin.

Figure 3-3: Scheduler-Process Interaction

#### 2. Simulation Processes

C++SIM supports the process-oriented approach to simulation, i.e. each simulation entity can be considered as a separate process. These entities are represented by process objects: they are C++ objects which have an independent thread of control associated with them when they are created. Each process has a state and at any point during the simulation, a process can only be in one of the following states:

- a) *active*: the process has been removed from the head of the scheduler queue and its actions are currently being executed.

- b) *suspended*: it is on the scheduler queue and is scheduled to be active at a specified simulation time.

- c) *passive*: it has been removed from the scheduler queue and if it is not brought back to the queue by another process, it will not execute anymore.

- d) *terminated*: it is not on the scheduler queue and will not take any further part in the simulation.

C++SIM uses the object-oriented approach for developing the process objects by allowing classes to inherit the process functionality from a base class called Process. This class provides all required operations for the simulation system to control all of the processes in the simulation. The most important operations are:

- (i) Activate: activates a process. This is invoked by the currently active process which passes the control to the activated process.

- (ii) Passivate: removes the currently active process from the scheduler queue.Another process has to put this process back into the queue if it needs to be scheduled again in the future.

- (iii) idle: returns true or false to indicate whether a process is actually on the scheduler queue or not.

- (iv) Hold: reschedules the currently active process to be active a fixed units of time later.

- (v) Cancel: removes a process from the simulation queue or suspends it indefinitely if it is currently active.

- (vi) CurrentTime: returns the current simulation time which is useful for controlling action relative to a given time period.

Other operations and further explanation on the ones above are available in [11].

Any class derived from the Process class must supply a void Body()member function, within which its actions must be defined. These actions characterise the interactions among the processes in the simulation and these actions will be executed when the process to which they belong to is activated.

3. Main System Thread

This is a special thread which is used to initialise the threads used in the simulation. It is invoked in the main body of the simulation code and since this thread has the highest priority in the system, it is necessary to suspend it in order to allow other threads to run.

A more detailed description and some examples of C++SIM programs can be found in [11] and [52].

#### 3.3.2. JavaSim

JavaSim is a Java implementation of the original C++SIM simulation toolkit, which supports the discrete-event process-based simulation where each simulation entity can be considered as a separate process [51]. The simulation entities are therefore represented by process objects, which are actually Java objects that possess an independent thread of control associated with them when they are created. These "active objects" then interact with each other through message passing and other simulation primitives in order to realise the operation path of the simulation.

Like in the C++SIM environment, there is a JavaSim *scheduler* that manages the simulation processes (the active objects) and places these processes onto a *scheduler queue* (the event list). The processes are also executed in a pseudo-parallel mode.

The difference between the C++SIM and JavaSim environments lies on how the processes are derived from its base class. JavaSim calls its base class SimulationProcess while the C++SIM calls its Process class. There is also a difference on where the processes' behaviour is specified. In C++SIM, the user needs to implement a void Body() member function on any classes derived from the Process class. The JavaSim code on the other hand requires its process class to implement a void run() member function. The rest of the syntax remains pretty much the same for both environments. More details on the JavaSim processes can be found in [51].

The advantage of JavaSim over C++SIM is that JavaSim is easier to install and manage on any operating system (due to Java's portability), and with the *jar* (Java ARchive) facility, it is even possible to put the whole JavaSim package into one *jar* file. The *jar* facility also allows more than one packages to be put into one *jar* file, which means that the JavaSim package can be integrated with other packages to provide more customised features.

# **3.4. Simulation Summary**

Simulation can be used as a means for predicting a system's performance, but building a simulation program is not a trivial task and system developers usually are not familiar with the simulation concepts. It is therefore desirable to have a tool that can build a simulation program automatically from a design notation (which is easier to prepare and commonly understood by system developers).

The next chapter identifies a simulation framework that can serve as a bridge between design notation and simulation program. It will be demonstrated later that this framework can be used to build a tool that can automatically transform a design notation into a simulation program.

# **Chapter 4**

# **From Design to Simulation**

# 4.1. Introduction

It is often difficult to build a simulation program directly from a design specification. The specification is normally quite complex and in the case of the distributed system, different performance requirements (such as high availability over reliability, etc.), connection between components (network delay, partition, etc.) and fault tolerance (machine failures and repairs) require additional effort. On top of that, a new simulation program needs to be built each time for a different specification, and the system developer must also be familiar with the simulation techniques - which is not always the case.

A tool that can automatically transform a design notation into a simulation program is therefore desirable. Before such a tool could be built though, it is important to first identify the common simulation components along with the actions that can be performed among them. Based on these components and actions, a simulation framework can be specified, and this framework provides a foundation for an automatic generation of a simulation program from a design notation.

# 4.2. SimML Framework

We have constructed a framework called *Simulation Modelling Language* (SimML) [6, 7, 9, 10, 69] that classifies the simulation components into two main groups: *basic type* components and *auxiliary* components. The first group represents entities of a

simulation and they correspond to the classes of a simulation program; these entities are identified as PROCESS, DATA, QUEUE and CONTROLLER components. The second group is useful for representing the instances of active objects (processes) involved in the simulation - i.e. the instances of the simulation classes - as well as for specifying the simulation parameters and collecting the simulation statistics. This group includes the OBJECT, RANDOMS and STATISTICS components.