# Preventing State Divergence in Replicated Distributed Systems

by

Alan Tully

Ph.D. Thesis

)

September 1990

The University of Newcastle upon Tyne

Computing Laboratory

) ) )

N-Modular Redundancy (NMR) is a form of active replication in which each processor is replicated to form a node and each processor replica within the node executes the same set of software component replicas. Communication between nodes, in the form of messages, passes through a voting mechanism by which processor failures are masked. When the degree of replication is three, the technique is known as Triple Modular Redundancy (TMR) and can tolerate the failure of a single node processor.

For voting to be successful, non-faulty software component replicas must output identical messages in an identical order. If we assume that software components are *deterministic*, then we need only ensure that the replicas process identical input messages in an identical order. Such software components conform to the well understood and researched *state machine* model of active replication.

However, most distributed programs employ mechanisms not incorporated in the *state* machine model such as timeouts and prioritized messages. These potential sources of non-determinism could lead to a divergence of state among software component replicas which could then produce inconsistent responses to identical input messages, thereby defeating the NMR voting mechanism.

The main contributions of this thesis are:

)

)

0

)

)

- (i) To present an architecture for active replicated processing which may be applied to any distributed system.

- (ii) To present a more expressive, enhanced model for software components which incorporates non-determinism and show how a system of such software components may be replicated, using a single well-defined generic mechanism (the *order process*) to prevent state divergence. Since the problem of identical ordering can be formulated as the *interactive consistency problem* which is solvable in the presence of arbitrary (Byzantine) failures, the approach presented in this thesis, unlike any other published to date, is capable of tolerating such failures.

# Acknowledgements

Firstly I would like to thank my supervisor, Professor Santosh Shrivastava, for suggesting this area of research and for reading and commenting upon the numerous drafts of this thesis.

I would also like to thank Dr. Paul Ezhilchelvan, Dr. Neil Speirs, Dr. Stuart Wheater and Mark Little, for their many useful comments.

Finally I would like to thank my family for their support and encouragement, which they gave me during my studies.

Financial support for much of the work described in this thesis was provided by grants from the Science and Engineering Research Council and ESPRIT Project DELTA-4.

| Chapter 1: Introduction                                      | 1         |

|--------------------------------------------------------------|-----------|

| Chapter 2: Understanding Active Replication                  | 5         |

| 2.1 Introduction                                             | 5         |

| 2.2 The State Machine                                        | 5         |

| 2.3 Replicating the State Machine                            | 7         |

| 2.4 Interactive Consistency                                  | 8         |

| 2.4.1 Introduction                                           | 8         |

| 2.4.2 The Byzantine Generals Problem                         | 9         |

| 2.4.3 A Solution using Oral Messages                         | 11        |

| 2.4.4 A Solution using Signed Messages                       | 16        |

| 2.4.5 Summary                                                | 19        |

| 2.5 Total Ordering                                           | 19        |

| 2.5.1 Logical clocks                                         | 20        |

| 2.5.2 Approximately Synchronized Real-Time Clocks            | 22        |

| 2.6 Introducing Non-determinism into the State Machine Model | 24        |

| 2.6.1 Timeouts                                               | 24        |

| 2.6.2 Prioritized requests                                   | 25.       |

| 2.7 Summary                                                  | 26        |

|                                                              |           |

| Chapter 3 : Fault-Tolerant Architectures                     | 27        |

| 3.1 Introduction                                             | 27        |

| 3.2 The Tandem Non-Stop System                               | 29        |

| 3.3 The Sequoia Computer System                              | 31        |

| 3.4 The Stratus Computer System                              | 33        |

| 3.5 SIFT                                                     | 35        |

| 3.5.1 SIFT - An Extension                                    | 39        |

| 3.6 Mars                                                     | 41        |

| 3.7 FTMP                                                     | 42        |

| 3.8 FTP                                                      | 44        |

| 3.9 MAFT                                                     | 45        |

| 3.10 Delta-4 OSA                                             | 49        |

| 3.10.1 Active Replication                                    | 50        |

| 3.10.2 Passive Replication                                   | <i>52</i> |

| 3.11 Delta-4 XPA                                             | 54        |

| 3.12 Summary                                                 | 56        |

|                                                              |           |

| Chapter 4: System Architecture                               | 58        |

| 4.1 Introduction                                             | 58        |

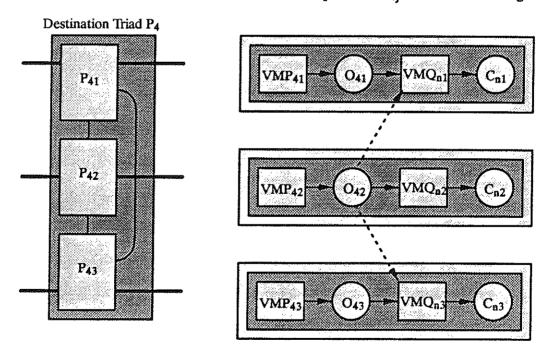

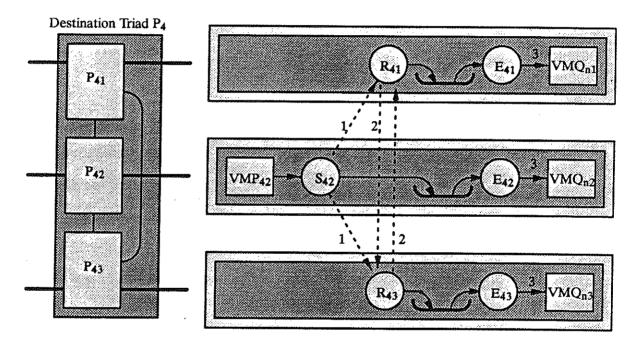

| 4.2 The Replicated Processing Model                          | 59        |

| 4.3 Processor Interconnection                                | 63        |

| 4.4 Signatures and Authentication                            | 70        |

| 4.4.1 Single-signed Messages                                 | 71        |

| 4.4.2 Double-signed Messages                                 | <i>72</i> |

| 4.5 Voting and Authentication                                | 74        |

| 4.5.1 Single-signed Messages                                 | <i>75</i> |

| 4.5.2 Double-signed Messages                                 | 77        |

)

Э

)

Ð

)

)

| 4.5.4             | Detection of Duplicate Messages      | 80  |

|-------------------|--------------------------------------|-----|

| 4.6               | A Dual Processor Derivative          |     |

| 4.7               | Summary                              | 87  |

| Chapter 5: The    | Order Process                        | 88  |

|                   | Introduction                         | 88  |

|                   | Order Process Structure              |     |

|                   | Atomic Broadcast Protocols           | 91  |

| 5.3.1             | First Protocol (omission)            | 93  |

| 5.3.2             | Second Protocol (timing)             | 96  |

| 5.3.3             | Third Protocol (Byzantine)           | 98  |

| 5.3.4             | Performance                          | 101 |

| 5.4               | Summary                              | 102 |

| Chanton 6 . Non   | -determinism in the Enhanced Model   | 102 |

| •                 | Introduction                         | 103 |

|                   |                                      | 103 |

| 6.2.1             | Enhanced Message Selection           | 103 |

| 6.2.2             | Blocking Input                       | 103 |

| 6.2.3             | <u> </u>                             | 105 |

| 6.2.4             | Replicating the Enhanced Model       | 107 |

| 6.2.5             | The Generic Input Function           | 107 |

|                   | Prioritized Input                    | 109 |

|                   | Asynchronous External Events         | 110 |

|                   | Non-deterministic Processing         | 113 |

|                   | Semaphores                           | 114 |

|                   | Real-Time Clocks                     | 115 |

|                   | Performance                          | 118 |

| 6.8               | Summary                              | 121 |

|                   | determinism in Programming Languages | 122 |

|                   | Introduction                         | 122 |

|                   | OCCAM                                | 122 |

|                   | Ada                                  | 124 |

| 7.4 (             | Other Languages                      | 127 |

| 7.5 S             | Summary                              | 127 |

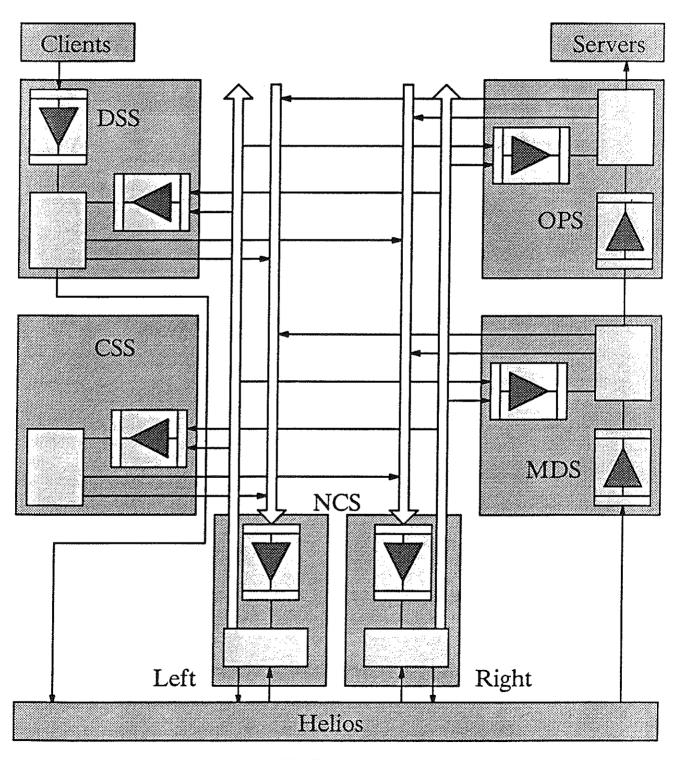

| Chapter 8 : Softw | are Architecture of a TMR Node       | 128 |

| 8.1 I             | ntroduction                          | 128 |

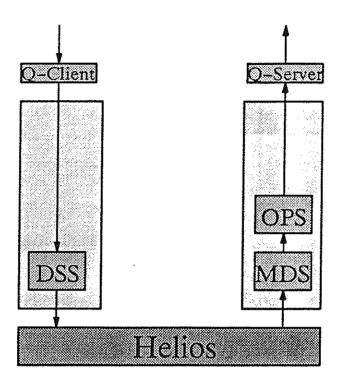

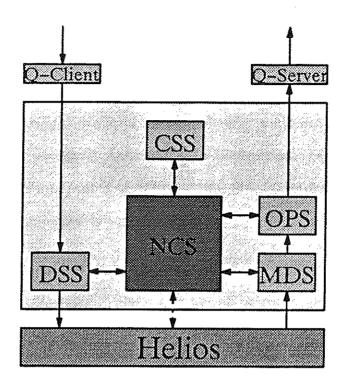

| 8.2 7             | The Helios Operating System          | 129 |

|                   |                                      | 131 |

| 8.4 T             | The Queue Server                     | 134 |

|                   | Building with Queue Servers          | 135 |

|                   |                                      | 137 |

| Chapter 9 : Concl | uding Remarks                        | 138 |

| Annendiy A • A C  | C++ Interface to Clients and Servers | 142 |

|                   | Introduction                         | 142 |

| A.2    | The Base Classes        | 142 |

|--------|-------------------------|-----|

| A.3    | The Derived Classes     | 149 |

| A.4    | Using the C++ Interface | 152 |

| A.5    | Summary                 | 153 |

| Refere | nces                    | 157 |

Э

Э

9

Э

)

)

J

# Chapter 1: Introduction

A large class of computer applications specify a performance requirement which far exceeds the capability of any single processor. Even as processors become faster due to new materials, fabrication methods and internal organization, new applications arise which continue to exceed current capabilities. It is for this reason that computer architects have turned to various forms of parallelism to satisfy their needs.

1

)

)

)

)

)

When parallel systems are designed, high performance is often achieved by using application-specific hardware and sacrificing versatility. With the advent of VLSI however, computing hardware costs have been reduced to such a level that large networks of general-purpose processors have become economically viable. A custom-designed system will always be able to out-perform a regular network of general-purpose processors. However, this apparent inefficiency may in many cases be offset by an increase in the number of processors. The reduction in design costs will more than pay for the moderate increase in hardware costs for a broad range of applications.

The construction of massive networks of processors raises the question of reliability. If a single processor failure results in the failure of the system as a whole then that system is of little practical use. Fault-avoidance techniques may be used to minimize the probability of failure but that probability cannot be made negligible in large and complex systems. Additional steps must be taken to ensure continuous system operation by providing tolerance to individual processor failures.

Fault-tolerance techniques which employ redundancy can prevent failure of a system in the presence of faults. *Passive replication* techniques provide for the re-execution of software components on a non-faulty processor. *Active replication* techniques replicate software components and concurrently execute each replica on an

1

independent processor. In this way, the failure of a bounded number of processors can be *masked* without a further time penalty. The latter solution is particularly attractive when the computing system must provide a *real-time* response to external events.

Some active replication techniques make the assumption that processors have fail-silent semantics. That is, a processor either produces the correct response (as specified) or no response at all. A minimum of m+1 software component replicas are necessary to tolerate m processor failures (in the worst case where m failures occur, the outputs of the one remaining non-faulty replica may be trusted). An alternative view assumes that processors have fail-arbitrary semantics (Byzantine failure [2][11]). That is, the behaviour of a faulty processor is undefined. A minimum of 2m+1 replicas are then necessary to tolerate m processor failures (in the worst case where m failures occur, the outputs of the remaining m+1 non-faulty replicas will still form a majority).

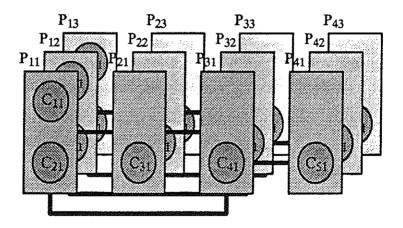

N-Modular Redundancy (NMR) is a form of active replication in which each processor is replicated to form a node and each processor replica within the node executes the same set of software component replicas. Communication between nodes, in the form of messages, passes through a voting mechanism by which processor failures are masked. When the degree of replication is three, the technique is known as Triple Modular Redundancy (TMR) and can tolerate the failure of a single node processor.

For voting to be successful, non-faulty software component replicas must output identical messages in an identical order. If we assume that software components are *deterministic*, then we need only ensure that the replicas process identical input messages in an identical order. Such software components conform to the well understood and researched *state machine* model of active replication [7] where, "Outputs of a state machine are completely determined by the sequence of requests it processes, independent of time and any other activity in the system".

However, most distributed programs employ mechanisms not incorporated in the state machine model such as timeouts and prioritized messages. These potential sources of non-determinism could lead to a divergence of state among software component replicas which could then produce inconsistent responses to identical input messages, thereby defeating the NMR voting mechanism. This thesis addresses the problem of preventing state divergence in active replicated processing using an enhanced processing model.

The main contributions of this thesis are:

)

)

)

)

- (i) To present an architecture for active replicated processing which may be applied to any distributed system (reported in [8]).

- (ii) To present a more expressive, enhanced model for software components which incorporates non-determinism and show how a system of such software components may be replicated, using a single well-defined generic mechanism (the *order process*) to prevent state divergence (reported in [9]). Since the problem of identical ordering can be formulated as the *interactive consistency problem* which is solvable in the presence of arbitrary (*Byzantine* [2]) failures, the approach presented in this thesis, unlike any other published to date, is capable of tolerating such failures.

The work reported in this thesis forms the basis of a practical architecture that the author and colleagues are implementing for a real-time application (initial work reported in [10]).

Chapter 2 introduces the state machine as a model for active replicated processing and shows how the consistent message ordering requirement of the replicated state machine may be achieved using solutions to the interactive consistency problem. Interactive consistency is examined in more detail using the well–known Byzantine Generals Problem analogy for which several solutions are then presented. Finally, expansion of the state machine model to incorporate non–deterministic mechanisms for real–time systems is considered, to show that consistent message ordering alone is not sufficient to prevent state divergence among process replicas.

Chapter 3 presents the architectures of several existing systems which employ a range of passive and/or active replication techniques to achieve fault-tolerance, with a view to showing how each prevents state divergence.

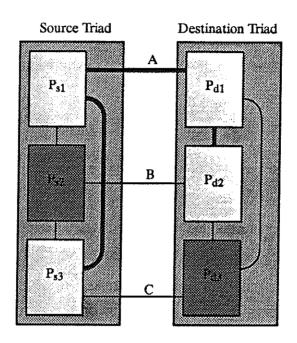

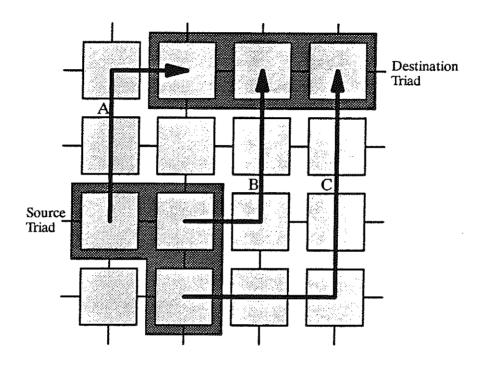

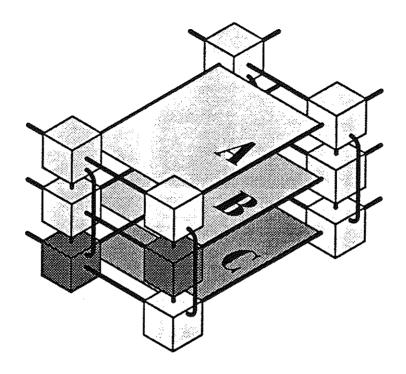

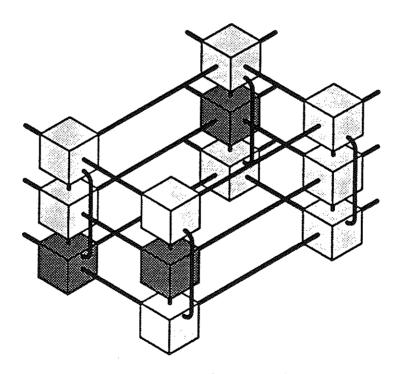

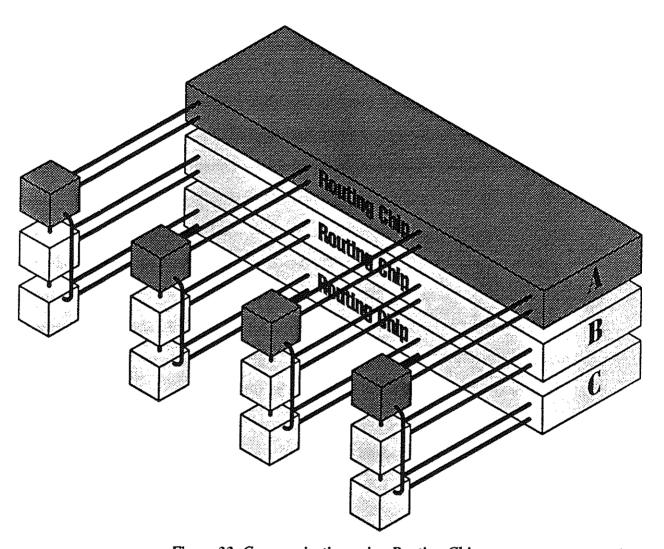

Chapter 4 describes the proposed architecture of a multi-processor distributed system designed to tolerate Byzantine faults. A processing model is presented then replicated using TMR techniques. A processor interconnection scheme is developed to support the replicated processing model which remains fully connected after one processor failure per TMR node. Finally, a degenerate form of the node is described in which process and processor triads are replaced by process and processor pairs to create a node with *fail-silent* semantics.

Chapter 5 introduces the order process as a mechanism for preventing state divergence in software components with non-deterministic message selection (state machine model) and shows how it may be implemented using protocols which tolerate various classes of faults, up to and including Byzantine faults.

In Chapter 6, the order process is used to prevent state divergence in an enhanced model which allows more complex message selection criteria (*generic input function*), asynchronous external events, non-deterministic processing, semaphores (to allow shared-memory inter-process communication) and real-time clocks.

Chapter 7 shows how the input constructs of several current languages may be mapped onto the generic input function. Because state divergence can be prevented when using the *generic input function*, it can also be prevented when executing the example constructs.

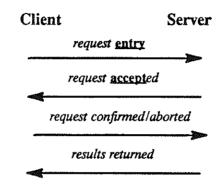

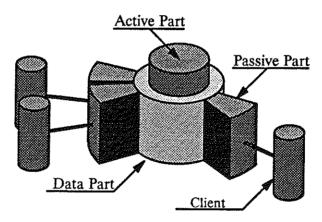

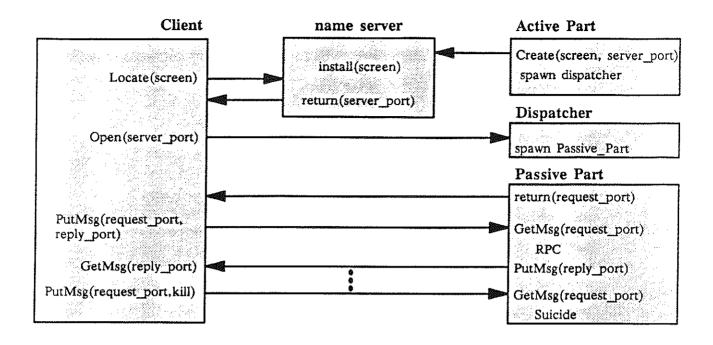

Chapter 8 describes a practical design of the mechanisms presented in this thesis using the *client/server* facilities provided by the Helios operating system.

Finally, Chapter 9 considers the implications of using the techniques presented in this thesis and reflects on possible future enhancements.

# **Chapter 2: Understanding Active Replication**

### 2.1 Introduction

.)

**)**

()

In active replication, all the non-faulty replicas must produce identical output messages in an identical order. This requires that non-faulty replicas carry-out identical processing on an identical sequence of identical input messages. The state machine model [7] to be discussed in this chapter provides a rigourous setting for explaining the principles of active replication. As will be shown, to support active replication, protocols for message agreement and order are required. These protocols can be formulated in terms of the interactive consistency problem which is also discussed in this chapter. Finally, limitations of the state machine model which make it less suitable for real-time distributed systems are discussed. The removal of these limitations will introduce problems of non-determinism amongst replicas, which must be addressed for active replication to be useful. Solutions to these problems will be developed in subsequent chapters of this thesis.

### 2.2 The State Machine

A state machine [7] consists of state variables which implement its state and commands which transform its state and produce output. A command, which is implemented by a deterministic program, is invoked by a request from a client. Multiple clients may make multiple concurrent requests but the commands will be executed strictly sequentially. Thus a state machine will possess the following property:

The outputs of a state machine are completely determined by the sequence of requests it processes, independent of time and any other activity in a system.

Requests are processed by a state machine in an order consistent with causality:

- O1 Multiple requests issued by a single client to a given state machine sm are processed in the order they were issued.

- O2 If the fact that request r was made to sm by client c could have caused a request r' to be made to sm by another client c', then r is processed before r'.

The scenario described by O2 is possible if the request r made to sm was followed by a request r'' made to some other state machine sm'' which then itself acted as a client c' by making the request r' to sm. Because the making of a request and the receipt of any reply are separated in the state machine model, it is possible for the request r' to arrive at sm before the request r. Messages cannot therefore be processed simply in the order in which they are received at sm.

A state machine may be expressed by a process accepting requests in the form of messages and performing the actions they specify as shown in Figure 1.

)

```

process state_machine

var m:message

cycle

receiveany(m)

action(m)

end

```

Figure 1 The State Machine

The message returned by a call to the function receiveany(m) must satisfy 01 and 02 and action(m) must satisfy P1.

# 2.3 Replicating the State Machine

A fault-tolerant state machine can be implemented by replicating it and executing each replica on a distinct processor in a distributed system. The outputs of the replicas may then be combined though voting to mask the failure of some of the processors executing state machine replicas. However, if voting is to be successful, it is necessary to ensure that non-faulty replicas produce the same outputs. If each replica starts in the same initial state and processes requests in the same order then because of PI, each will produce the same outputs. Thus a fault-tolerant state machine requires the fault-tolerant implementation of the *Order* abstraction:

Order Requests are processed in the same order by every non-faulty state machine replica.

This in turn requires the fault-tolerant implementation of the Agreement abstraction:

Agreement Every non-faulty copy of the state machine receives every request.

Agreement may be implemented by any protocol which allows the processor executing a client (the transmitter) to send a request (the value) to all the processors executing state machine replicas (the receivers) such that:

IC1 All non-faulty receivers agree on the same value.

)

)

)

If the transmitter is non-faulty then all non-faulty receivers use its value as the one they agree on.

These are the interactive consistency conditions of the *Byzantine Generals Problem* and may be satisfied using any of the solutions to that problem. Several solutions will be presented in Section 2.4.

Order may be implemented by assigning to each request a unique identifier and ensuring that state machine replicas process requests according to a total ordering relation on these identifiers. Total order is necessary as processing requests in the

order they are received by the replicas does not necessarily satisfy the *Order* abstraction. For example, two requests could be received by one state machine replica in one order while being received by another replica in the other order. Two methods of assigning unique identifiers at the point of issue (the client) will be presented in Section 2.5. Both methods satisfy *O1* and *O2*; the first uses logical clocks while the second uses approximately synchronized real-time clocks.

In Chapter 5, other practical solutions will be presented employing atomic broadcast protocols which simultaneously satisfy *Agreement* and *Order*.

Note that a client may itself be structured as a state machine and therefore it may also be made fault-tolerant through replication.

# 2.4 Interactive Consistency

### 2.4.1 Introduction

The Byzantine Generals Problem [2] has been proposed as an abstract way of expressing the interactive consistency problem encountered in distributed computing systems constructed using components which, when they fail, can exhibit arbitrary behaviour. As such, it provides a convenient way of relating the problems and algorithms of this thesis to each other and to the interactive consistency problem itself.

A loyal general may represent a correctly functioning processor while a traitorous general may represent a failed processor. The messages sent between processors are represented by orders sent from a commanding general to his lieutenant generals.

The *Byzantine Generals Problem* is introduced in Section 2.4.2 followed by solutions based on *oral* messages (Section 2.4.3) and *signed* messages (Section 2.4.4). Finally, the main findings of this section are summarized in Section 2.4.5.

# 2.4.2 The Byzantine Generals Problem

A number of divisions of the Byzantine army are camped outside an enemy city, each division commanded by its own general. The generals can communicate with each other only via messengers.

Each general  $g_i$  observes the enemy and independently forms an opinion  $v_i$  on whether the army should attack or retreat, then communicates  $v_i$  to the other generals  $g_i$  ( $i\neq j$ ) using messengers.  $g_i$  collects the opinions  $v_j$  of all the other generals from their messengers to form, along with his own opinion,  $V_i$ :

$$V_i = setof v_j for j = 1..n$$

(where  $n = the number of generals$ )

$g_i$  then performs a majority vote on  $V_i$  to reach a decision  $d_i$  on whether to attack or retreat:

$$d_i = maj V_i$$

)

}

)

)

Some of the generals will be loyal while some will be traitorous but the following conditions must always be satisfied:

condA All loyal generals reach the same decision,  $d_i$ .

condB A small number of traitorous generals cannot cause the loyal generals to reach a bad decision.

A decision to attack may be considered *bad* for example, if a large majority of loyal generals are of the opinion that the army should retreat (because the enemy is too strong). A decision to retreat may be considered *bad*, if a large majority of loyal generals are of the opinion that the army should attack (lest the enemy grow in strength).

A loyal general  $g_i$  will always send the same value of  $v_j$  to all the other generals. So if all generals are loyal, every general  $g_i$  will receive the same set of opinions and will therefore reach the same decision, satisfying condA:

for all

$$i = 1..n$$

and  $j = 1..n$   $V_i = V_j \Rightarrow maj \ V_i = maj \ V_j \Rightarrow d_i = d_j$

Now suppose that one general  $g_f$  is traitorous, he could send a different view of his opinion  $v_f$  to different generals. Some general  $g_i$  would then receive a different set of opinions  $(V_i)$  to some other general  $g_i$   $(V_j)$ . If the opinions of the loyal generals were divided equally between attack and retreat, then they may not reach the same decision, thereby violating condA:

$$V_i \neq V_i \Rightarrow \text{maj } V_i \neq \text{maj } V_i \Rightarrow d_i \neq d_i$$

Therefore to satisfy *condA* in the presence of a traitorous general:

cond1 Every loyal general  $g_i$  must receive the same set of opinions  $V_i$ .

That is, for every general  $g_i$ , whether or not loyal:

cond1' Every loyal general  $g_i$  must obtain the same value for  $v_i$ .

In satisfying *condA*, *condB* must not be violated. Therefore, for every loyal general g:

cond2 Every loyal general  $g_i$  must receive  $v_i$  uncorrupted.

Since conditions cond1' and cond2 are both conditions on the opinion  $v_j$  of general  $g_j$  as received by general  $g_i$ , the problem is reduced to ensuring that a general  $g_j$  may send his opinion  $v_j$  to the other generals. This problem may be re-phrased in terms of a commanding general  $g_j$  sending an order (use  $v_j$  as my opinion) to his lieutenants. This is known as the *Byzantine Generals Problem*:

### Byzantine Generals Problem

A commanding general must send an order to his lieutenant generals such that the following conditions are satisfied:

IC1 All loyal lieutenants obey the same order.

IC2 If the commanding general is loyal, then every loyal lieutenant obeys the order he sends.

Conditions IC1 and IC2 are called the *interactive consistency* conditions, and are identical to the message-based formulation presented in Section 2.3.

Conditions *condA* and *condB* may then be satisfied by repeatedly applying some solution to the *Byzantine Generals Problem*, with each general in turn acting as the commander.

Two solutions will now be considered; one using *oral* messages and the other using signed messages. The reader is referred to [2] for a formal proof of the algorithms.

# 2.4.3 A Solution using Oral Messages

It is assumed that a general may send a message directly to any other general and that messengers are loyal (a traitorous messenger may be modelled by the traitorous general who sent him). So a traitorous general cannot interfere with the communication between any other generals. It is therefore assumed that:

Al Every message that is sent is delivered correctly.

A2 The receiver of a message knows who sent it.

It is further assumed that:

A3 The absence of a message may be detected.

Satisfying A3 is not straightforward; a general cannot detect, in finite time, that a message will never arrive. But, if the time taken for the generation and transmission of

a message by a loyal general is bounded to some fixed value  $\Delta$ , then a general may assume that any message arriving after  $\Delta$  must be from a traitorous general and may be discarded. A message is therefore assumed to be absent if it does not arrive by  $T + \Delta$ , where T is the time of transmission. For such timeouts to be meaningful, all generals must know the actual time of transmission T. The value of T may be implicit (eg periodic) or explicitly contained within the message (timestamp). In the later case the general would have to receive at least one copy of the message, either direct or via another general (otherwise he could not determine T). In either case, each general measures time by his own clock, so the clocks of all loyal generals must be synchronized to within some bounded time  $\epsilon$  (see Section 5.3).

If a traitorous commanding general does not send an order to one of his lieutenants, the lieutenant assumes *retreat*.

For a solution to the *Byzantine Generals Problem* satisfying *IC1* and *IC2* using oral messages, which tolerates m traitorous generals, there must be at least 3m + 1 generals in total.

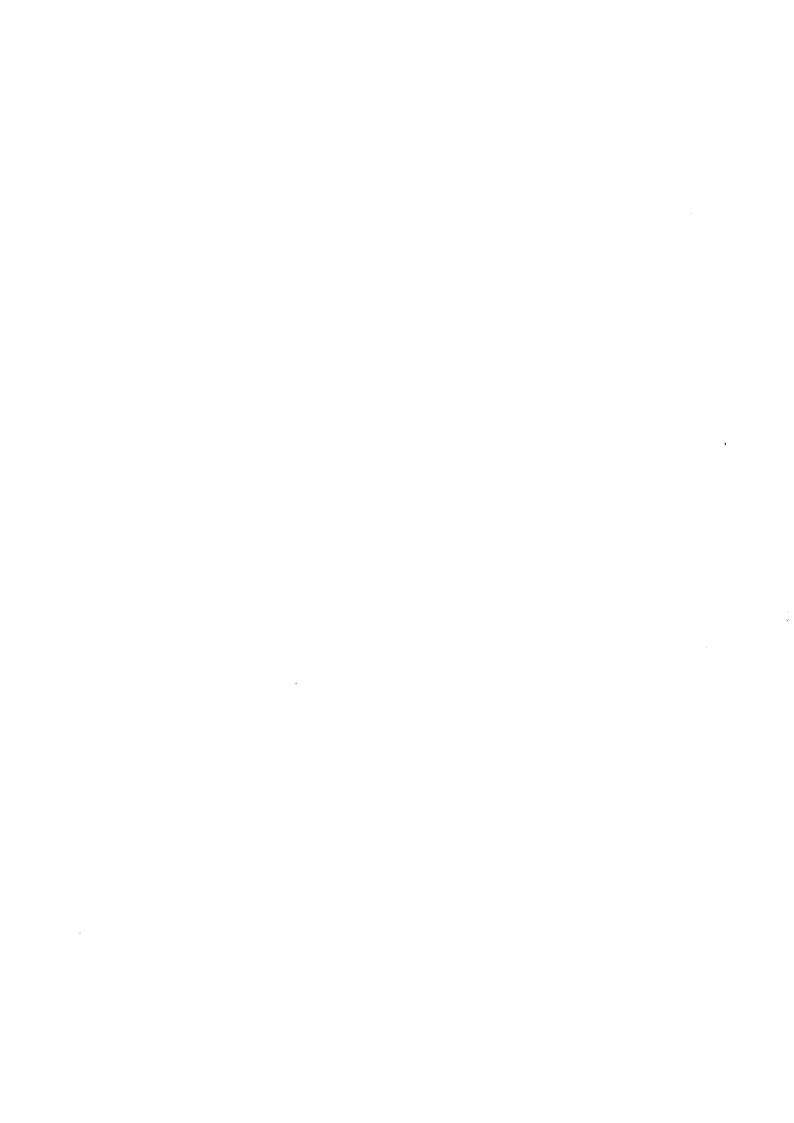

Figure 2 Insufficient Generals for Oral Messages

Consider the converse case (n < 3m + 1) from the point of view of lieutenant L1 as shown in Figure 2, where n = 3 and m = 1.

Each general executes the appropriate 2-stage algorithm of Figure 3. The timeout clause is necessary to handle a traitorous general who refuses to send (commander) or relay (lieutenant) an order.

In the scenario of Figure 2(a), the commander is loyal and in stage 1 orders attack, but the traitorous lieutenant L2 lies to the loyal lieutenant L1 in stage 2 by saying that he received the order to retreat. In the scenario of Figure 2(b), the commander is traitorous and orders L1 to attack while ordering L2 to retreat in stage 1. In stage 2, L2

)

)

)

)

```

process commander

var v:order

cycle

formulate_order(v)

Stage 1

send to all lieutenants(v)

end

end

process lieutenant

var v, v', vc:order

cycle

within t do

receive_from_commander(v)

Stage 1

timeout

v = retreat

od

send to other lieutenant(v)

within t do

receive from other lieutenant(v')

Stage 2

timeout

v' = retreat

od

v_c = decide order(v,v')

end

end

```

Figure 3 Oral Message Algorithms

correctly informs L1 that he received the order to *retreat*. These two scenarios appear exactly the same to L1. Hence he doesn't know the identity of the traitorous general nor what message was sent to L2. Hence to satisfy IC2, L1 must obey the order received

directly from the commander in both scenarios, that is to *attack*. The scenarios of Figure 2 may be repeated from the point of view of L2 and by a similar argument, it may be shown that L2 must also obey the order received directly from the commander. But in Figure 2(b), the order is to *retreat*. Therefore in the scenario of Figure 2(b), L1 will *attack* while L2 will *retreat*, violating IC1.

The scenarios of Figure 2 may be modified by substitution to prove the impossibility of satisfying IC1 using oral messages with 3m generals of which m are traitorous. The algorithm of Figure 3 will then require more stages (see [2]).

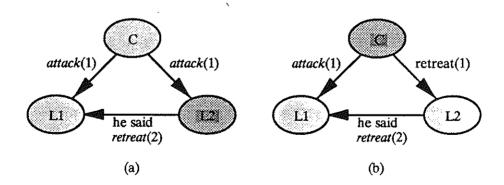

Now consider the case where n = 3m + 1, shown for m = 1 in Figure 4.

Figure 4 Sufficient Generals for Oral Messages

Each general executes the appropriate 2-stage algorithm of Figure 5.

In the scenario of Figure 4(a), the commander is loyal and sends the order to attack to all the lieutenants in stage 1. In stage 2, the loyal lieutenants L1 and L2 relay the order he said attack to each other and to the traitorous lieutenant L3, while L3 sends an arbitrary order to L1 (y) and L2 (x). After stage 2, each lieutenant has a set of three opinions. Each lieutenant may then perform a majority vote on the set to reach a

decision. Both the loyal lieutenants have a majority of attack opinions and will therefore reach the same decision, to attack, thereby satisfying IC1 and IC2.

```

process commander

var v:order

cycle

formulate_order(v)

Stage 1

send to all lieutenants(v)

end

end

process lieutenant

var v, v', v", vc:order

cycle

within t do

receive_from commander(v)

Stage 1

timeout

v = retreat

send_to_other_lieutenants(v)

par

within t do

receive_from_other_lieutenant(v')

timeout

v' = retreat

Stage 2

od

within t do

receive from other lieutenant(v")

timeout

v" = retreat

od

endpar

v_c = maj(v, v', v'')

end

end

```

Figure 5 Oral Message Algorithms

Now consider the scenario of Figure 4(b), where the commander is traitorous and sends conflicting orders  $\{x,y,z\}$  to its lieutenants in stage 1. In stage 2, the loyal lieutenants each correctly relay the order they received in stage 1. After stage 2, each lieutenant has a set of three opinions. Each lieutenant may then perform a majority

vote on the set to reach a decision. All the lieutenants have the same set of opinions  $V = \{x,y,z\}$  and will therefore reach the same decision (maj  $\{x,y,z\}$ ) thereby satisfying IC1. Condition IC2 does not apply because the commander is traitorous.

The scenarios of Figure 4 may be modified by substitution to prove the validity of satisfying IC1 and IC2 using oral messages with 3m + 1 generals of which m are traitorous. The algorithm of Figure 5 will then require more stages (see [2]).

# 2.4.4A Solution using Signed Messages

As was shown by the scenarios of Figure 2 and Figure 4, it is the ability of the traitorous general to lie which makes the *Byzantine Generals Problem* impossible for  $n \le 3m$ . This ability may be restricted by enabling the generals to sign a message under the assumption that:

- A4 (a) A loyal generals signature cannot be forged.

- (b) Any alteration of the contents of a signed message can be detected.

- (c) Any general can verify the authenticity of another generals signature.

A solution to the Byzantine Generals Problem now exists for the case  $n \ge m + 2$ .

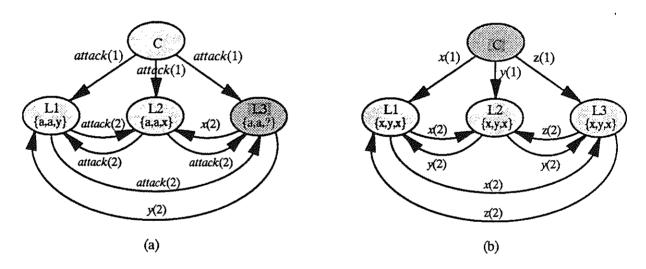

Consider the case where n = 3 and m = 1 as shown in Figure 6.

Each general executes the appropriate 2-stage algorithm of Figure 7.

In the scenario of Figure 6(a), the commander is loyal and in stage 1 orders attack. In stage 2, the traitorous lieutenant L2 tries to lie to the loyal lieutenant L1 by saying that he received the order to retreat, as he did in Figure 2(a). However, by assumption A4, L1 will now be able to detect a corruption of the message which may then be discarded. After stage 2, the loyal general L1 will hold the single command attack: C sent directly by the loyal general. L1 may then obey the command, satisfying IC1 and IC2.

In the scenario of Figure 6(c), the commander is loyal and in stage 1 orders *attack*. In stage 2, the traitorous lieutenant L2 refuses to relay an order to the loyal lieutenant L1.

After stage 2, the loyal general L1 will hold the single command attack:C (as in Figure 6(a)) sent directly by the loyal general. L1 may then obey the command, satisfying IC1 and IC2.

In the scenario of Figure 6(b), the commander is traitorous and orders L1 to attack while ordering L2 to retreat in stage 1. Both orders carry the valid signature of the commander. In stage 2, the loyal lieutenants correctly relay the order they received in stage 1. After stage 2, each loyal lieutenant has two conflicting commands bearing the valid signature of the commander. They may therefore deduce that the commander is faulty, and assume the default order to retreat, thereby satisfying IC1. Condition IC2 does not apply because the commander is traitorous.

Figure 6 Sufficient Generals for Signed Messages

In the scenario of Figure 6(d), the commander is again traitorous and orders L2 to retreat in stage 1, while refusing to send an order to L1. In stage 2, L1 relays the command to L2 but L2 has nothing to relay to L1. After stage 2, both the loyal

lieutenants will hold the single command retreat: C sent by the traitorous general. Both

```

process commander

var v:order

cycle

formulate order(v)

Stage 1

append_signature_to(v)

send_to_all_lieutenants(v)

end

end

process lieutenant

var v, v', vc:order

cycle

within t do

receive_from_commander(v)

Stage 1

timeout

if received_from_commander(v) then

if not authentic(v) then discard(v)

else

append_signature_to(v)

send to other lieutenant(v)

endif

endif

within t do

Stage 2

receive_from_other_lieutenant(v')

timeout

od

If received_from_other_lieutenant(v') then

if not authentic(v') then discard(v)

endif

endif

If received from commander(v)

or received_from_other_lieutenant(v')

then v_c = decide\_order(v,v')

else v<sub>c</sub> = retreat

endif

end

end

Figure 7 Signed Message Algorithms

```

may then obey the order, satisfying IC1. IC2 does not apply because the commander is traitorous.

Finally, if the commander is traitorous and refuses to send any order (not shown in Figure 6), both the loyal generals will obey the default order, to retreat.

The scenarios of Figure 6 may be modified by substitution to prove the validity of satisfying IC1 and IC2 using signed messages with m + 2 generals of which m are traitorous. The algorithm of Figure 7 will then require more stages (see [2]).

### 2.4.5 Summary

It has thus been shown that interactive consistency, satisfying the conditions ICI and IC2, may be maintained in the presence of m traitors when there are at least 3m + 1 generals (oral messages) or m + 2 generals (signed messages). Therefore the conditions condI' (and hence condI) and cond2 of the original problem are satisfied under the stated fault assumptions. Since every loyal general receives the same set of opinions (as a lieutenant to each general in turn), by applying maj V(i), they will all reach the same decision (satisfying condA), either to attack or retreat. If there are at least 2m + 1 generals, then the loyal generals will be in a majority and a small number of traitorous generals (any minority) cannot cause this to be a bad decision (satisfying condB). Thus to satisfy condA and condB, there must be at least 3m + 1 generals using oral messages or 2m + 1 generals  $(2m + 1 \ge m + 2)$  using signed messages.

### 2.5 Total Ordering

$\odot$

**(**(

The discussion that follows shows how 01 and 02 may be met by the total ordering of client requests.

A client must be able to assign a unique identifier to each request it produces. This identifier will consist of the identity of the client c, the identity of the state machine sm along with a timestamp t which is unique for the given pair (c, sm). Requests from a given client c may be then ordered according to timestamp at sm, satisfying O1.

However, if requests from multiple clients are to be ordered to satisfy O2, the timestamp attached to a given request r by a client c must be greater than that carried by any communication previously received by c (a communication could be received by c if c was itself to act as a state machine to other clients).

If two requests are received by sm bearing identical timestamps then their order of acceptance is unimportant and may be decided by some deterministic algorithm to ensure the replicas make a consistent choice. The choice may be based on the unique client identifier (the clients thus assume a priority).

In the following sections, two total ordering methods will be presented. The first, which uses logical clocks, does not require processor clock synchronization but has difficulty in determining when a request may be accepted (stability) in the presence of faulty processors. The second, which uses approximately synchronized real-time clocks, does not suffer from the stability problem associated with logical clocks but incurs the unavoidable overheads associated with processor clock synchronization.

### 2.5.1 Logical clocks

A logical clock [5] is a mapping F of events E to integers I:

$$I_n = F(E_n)$$

In the state machine context, an event may be the issue of a request or the receipt of some communication. For any two distinct events  $E_i$ ,  $E_k$ :

$$F(E_j) \neq F(E_k)$$

Further, if  $E_i$  could have caused  $E_k$  then:

$$F(E_i) < F(E_k)$$

Logical clocks may then be implemented using counters. Every client  $c_m$  has its own counter  $C_m$  whose values are taken from the set of integers. Every request issued by a client carries the current value (timestamp) of its counter and the identity of the client. The counter is modified according to to counter-update rules:

CUI  $C_m$  is incremented after after each event at  $c_m$ .

CU2 Upon receipt of a message with timestamp  $\tau$ ,  $C_m$  is updated further:

$$C_m = \max(C_m, \tau) + 1$$

The logical clock (timestamp + client identifier) may then be used to impose a total ordering on events, and hence requests to a given state machine *sm* may be ordered, satisfying *O1* and *O2*.

However, there is a problem. To satisfy O1 and O2, a state machine cannot accept a given request  $r_s$  until it is no longer possible for another request to arrive bearing a lower or equal timestamp. This is termed stability and occurs only under the following conditions:

CONI The state machine has received at least one request from every client in the system.

CON2 The timestamps carried by the latest request from each other client are all greater or equal to that carried by  $r_s$ .

)

If any client omits to send a request for some period,  $r_s$  cannot become stable, so all clients must periodically make null requests to all state machines. However, the failure of a single client could prevent the issue of null request and hence prevent  $r_s$  becoming stable.

This problem can be solved in the presence of fail-stop failures by sm setting a separate timeout on the receipt of the null request from each client. A timeout would

indicate failure of a client. No further requests could be received from that client so  $r_s$  could become stable.

This problem can only be solved in the presence of arbitrary (Byzantine) failures if the non-faulty state machines can agree on whether or not the timeout has occurred then ignore all further requests from the failed client.

### 2.5.2 Approximately Synchronized Real-Time Clocks

Each processor has its own real-time clock and the clocks of all processors are synchronized to within some known bound  $\epsilon$ . Each clock increases monotonically in steps of  $\delta_t$ . Every request issued by a client carries the current value (timestamp =  $\tau$ ) of its clock and the identity of the client.

O1 will be satisfied if a client makes no more than one request between successive clock ticks. O2 will be satisfied if the clock synchronization error  $\epsilon$  is less than the minimum time necessary to deliver a request  $(\Delta_{min})$  from client c to state machine sm. If  $\Delta_{min}$  were less than  $\epsilon$ , and the clock of sm lagged behind the clock of c by  $\epsilon$ , then a request r issued at local clock time  $t_c$  (=  $\tau$ ) could be delivered to sm at a its local clock time  $t_{sm}$  where:

$$t_{sm} < t_c$$

The state machine could then issue a request r' as a consequence of receiving r which carried a timestamp lower than that of r, violating O2.

As with logical clocks, to satisfy OI and O2, a state machine cannot accept a given request  $r_s$  until it is no longer possible for another request to arrive bearing a lower or equal timestamp  $(\tau)$ . If through clock synchronization the maximum time necessary to deliver a request  $(\Delta_{max})$  from client c to all non-faulty state machines is bounded, then  $r_s$  may be accepted when the local clock  $t_{sm}$  satisfies:

Stability 1

$$T_{sm} > \tau + \Delta_{max} + \epsilon$$

)

)

This requirement forces the state machine to delay all requests by up to  $\Delta_{max} + \epsilon$ . The delay may be reduced if an additional stability test is included based on the conditions *CON1* and *CON2* specified for a system employing logical clocks.

Stability 2 A request r is additionally stable at state machine replica sm if a request bearing an equal or larger timestamp has been received from every other client in the system.

The first stability test can be made to tolerate a range of faults from fail-silent to arbitrary (Byzantine) if requests are delivered using an Atomic Broadcast Protocol as described in Section 5.3. In general, however, as the range of tolerable faults is increased, the time elapsed before a request becomes stable is also increased. The second stability test breaks down in the presence of faults as it did for logical clocks, described in the previous section. But since this is an optimization on the first test, no additional steps need be taken to make it fault-tolerant. In the presence of faults all requests would still become stable according to the first test.

# 2.6 Introducing Non-determinism into the State Machine Model

When replicating a state machine for fault-tolerance it is necessary to ensure that non-faulty replicas produce the same outputs. As has been shown, this is achieved by ensuring that:

The outputs of a state machine are completely determined by the sequence of requests it processes, independent of time and any other activity in a system.

Order Requests are processed in the same order by every non-faulty state machine replica.

P1 is achieved by processing requests sequentially and ensuring that each command is implemented by a deterministic program. Order is achieved by total message ordering, thereby depriving the state machine of any control over the selection of requests.

Most distributed systems intended for real-time applications employ mechanisms which are prohibited by the state machine model. For example, *PI* would be violated by internal concurrency, timeouts or asynchronous external events (interrupts), while Order could be violated by prioritized requests or timed access restrictions. If such distributed systems are to be replicated for fault-tolerance, the State Machine Model must be enhanced to incorporate these mechanisms.

To illustrate how such mechanisms could defeat successful voting, timeouts and prioritized requests will now be considered.

### 2.6.1 Timeouts

Suppose that a state machine has been designed to manage some external device, such as a robot arm. The state machine is replicated and the outputs of the replicas combined through voting by the arm control circuit. In response to a

move\_to(new\_position, t) request from a client, the state machine must perform some iterative calculation to decide the most efficient route (avoiding obstacles) then issue a sequence of outputs to move the arm to the new position before time t. The task of the state machine is thus to calculate the best route in the available time. The command required to service the request could be programmed as in Figure 8.

```

process state_machine

var m:message

cycle

receiveany(m)

switch (m.request)

...

case move_to:

calculate(route, m.new_position)

deadline = m.t - time_needed_for_move

while time < deadline

do improve(route, m.new_position)

output(route)

...

end

```

Figure 8 The Non-deterministic State Machine

The total number of iterations performed by the state machine will depend on other processor activity and may vary between replicas. It is thus possible for the replicas to produce different opinions on the best route (output). This could defeat the voting mechanism, even in the absence of faults.

# 2.6.2 Prioritized requests

· )

)

9

)

)

Suppose that the robot arm of Section 2.6.1 continuously receives independent move\_to requests from a number of clients. At any point in time, there will be a number of requests pending. But their order in the queue may not correspond to the order of their deadlines, so instead of processing requests in the order dictated by the receiveany(m) function (total ordering), requests must be selected by the state machine, after taking into account the deadline associated with the move. Selecting

requests in this way effectively assigns a level of priority to each request according to its deadline parameter and requires a prioritized search of the queue of pending requests.

However, although requests are delivered to state machine replicas in the same order, the time at which a given request is delivered to a given replica relative to the time of its search may vary. So at the time of search, the replica queues may not be consistent. It is therefore possible that the highest priority request selected by one replica is not present in the queue of another replica at the time of its search. In this case, the other replica will select a different request so their outputs will differ, thereby defeating the voting mechanism, even in the absence of faults.

# 2.7 Summary

A fault-tolerant state machine can be implemented by replicating it and executing each replica on a distinct processor in a distributed system. For voting to be successful, non-faulty replicas must produce the same outputs. This may be achieved by the total ordering of requests to make request selection deterministic and by the prohibition of internal non-determinism.

However, most distributed systems employ mechanisms which would, if incorporated directly into the state machine model, introduce possible sources of non-determinism. This non-determinism could lead to a divergence of state among the state machine replicas. They could thereafter produce inconsistent outputs which would defeat the voting mechanism.

If non-deterministic behaviour is to be introduced into the state machine model, steps must be taken to ensure that state divergence does not occur, so that the replicas continue to produce consistent outputs. A solution will be presented in Chapter 6.

# **Chapter 3: Fault-Tolerant Architectures**

### 3.1 Introduction

)

)

)

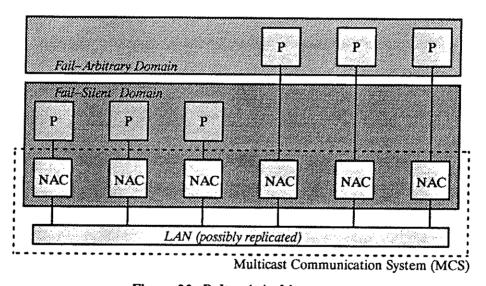

Many fault tolerant distributed systems have been implemented under the assumption that processors have *fail-silent* semantics, that is they fail *cleanly* by just stopping [17][26][31][32][46][47][78]. Such a restricted view is hard to justify in computer systems intended for mission and life critical applications where failure probabilities in the range  $10^{-6}$  to  $10^{-10}$  per hour are often specified [28][37]. It is then preferable to design and implement such systems under a totally unrestricted fault assumption namely, that a failed processor can behave in an arbitrary manner. In the literature this failure mode is often referred to as the *Byzantine* failure mode [2] (see Section 2.4).

Replicated processing with majority voting, *N*-modular redundant (NMR) processing [1], is a technique which enables the construction of systems which tolerate Byzantine processor failures. NMR techniques have already been applied successfully to distributed and multi-computer systems [6][21][28][37][47] including real-time control applications such as railway signalling [79]. When the degree of replication is three the technique is known as *Triple Modular Redundancy* (TMR).

The communication of information between processors required to perform majority voting is similar to that required to solve the *interactive consistency problem* (see Section 2.4). However, there is one fundamental difference which affects the complexity of the solution and the minimum number of processor n necessary to tolerate m failures [30].

In the *interactive consistency problem*, loyal generals can legitimately form a different opinion on whether to attack or retreat. To ensure that all loyal generals make the same decision it is necessary to ensure that all loyal generals possess the same set of

opinions (V<sub>i</sub> in Section 2.4) before performing a majority vote. This may be achieved by repeatedly applying stages 1 and 2 (more for m > 1) of the Byzantine Generals Problem solution, once for each general. The minimum number of processors n necessary to tolerate m failures is  $n \ge 3m + 1$  using oral messages or  $n \ge 2m + 1$  using signed messages as discussed in Section 2.4.

With NMR processing on the other hand, it may be assumed that all loyal generals share the same opinion (non-faulty processors produce the same output message). So, if the loyal generals are in a majority, their common opinion will form a majority, irrespective of the opinions of the traitorous generals. A majority vote may thus be performed after repeatedly applying only stage 1 of the Byzantine Generals Problem solution, once for each general. The minimum number of processors n necessary to tolerate m failures is  $n \ge 2m + 1$  using oral messages (signed messages become necessary only if processors are not directly connected).

Thus when the problem of state divergence is disallowed or prevented, the *interactive* consistency problem cannot occur and such an NMR processing system may be constructed using only 2m + 1 processors.

Several existing fault-tolerant systems will now be examined, with a view to showing how each prevents state-divergence.

The systems may be divided into four groups.

In the first group (Tandem, Delta-4 OSA passive model), processors are assumed to have *fail-silent* semantics, allowing passive replication techniques to be used (since outputs from a functioning processor are by definition correct), so non-determinism within process replicas cannot cause state divergence.

In the second group (SIFT, Mars, Delta-4 OSA active model), process replicas are constrained to be deterministic and cannot therefore cause state divergence. However,

in SIFT and Mars, communication between concurrently executing processes is asynchronous, another possible source of non-determinism which must be tackled if state divergence is to be prevented.

In the third group (FTMP, FTP, Sequoia, Stratus), process replicas operate in *lock-step* execution (micro-frame synchronization [35]). and special hardware is used to synchronize asynchronous events (eg. interrupts and timeouts) to the processor instruction stream so process replicas are interrupted at the same point in their execution. Therefore non-determinism within process replicas cannot cause state divergence.

In the fourth group (Delta-4 XPA, MAFT), agreement protocols are executed on behalf of the process replicas, to resolve non-determinism and prevent state divergence.

# 3.2 The Tandem Non-Stop System

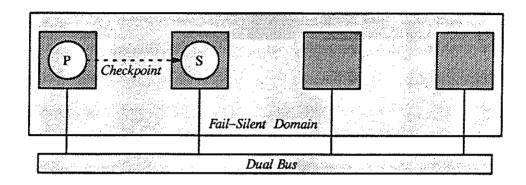

The Tandem Non-Stop system [14][15][17][18][24][26] is a commercial distributed computing system for on-line transaction processing. When the system was designed in the mid 1970s the view was taken that active replication of processes through hardware redundancy would not be cost effective for that application. So, Tandem assumes that processors have *fail-silent* semantics, then uses passive replication to tolerate failures. A simplified representation of the Tandem architecture is shown in Figure 9.

A Tandem system consists of 2 to 16 processing modules connected via dual busses (The Dynabus). Each processing module consists of a single processor with its private memory. Multiple Tandem systems may be connected by a replicated fibre-optic ring to increase the number of processing modules. All inter-processor communication is performed by passing messages on Dynabus.

Each process is duplicated to form primary and secondary replicas. The primary replica *P* executes the algorithm of the process and periodically checkpoints its state to the secondary replica *S*. The secondary replica, which resides on another processor, uses these checkpoints to update its own state. The secondary replica does not execute the algorithm of the process and hence does not consume processor time (except when receiving checkpoints).

Figure 9 Tandem

)

Every processor periodically (once per second) transmits an *I'm alive* message which is monitored by all processors. It is assumed that the absence of such a message (detected by timeout) indicates the failure of that processor. When a failure is detected, processors participate in an interactive consistency algorithm to agree on the failure. Then each processor checks to see if it maintains a secondary replica for any primary on the failed processor. If it does, the secondary replica is activated, beginning execution at its last checkpoint. The secondary replica now becomes the new primary, but without a secondary of its own (failure of the new primary cannot be tolerated).

When the failed processor recovers or is replaced, it again periodically transmits an *I'm alive* message. This is detected by the new primary and causes a new secondary replica to be created on the formerly failed processor, thereby regaining fault-tolerance.

The secondary replica has its path of supposed execution imposed by the primary replica (through a sequence of checkpoints), so the path of execution of the primary may be non-deterministic without causing state divergence.

# 3.3 The Sequoia Computer System

)

)

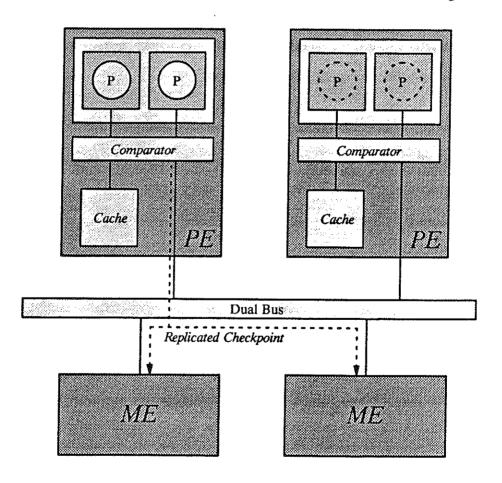

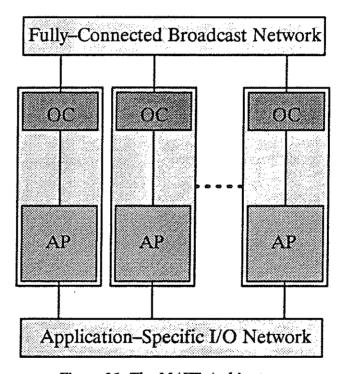

Sequoia [24][25][27] is another commercial distributed computing system for on-line transaction processing which, like Tandem, uses passive replication to tolerate failures. However, whereas Tandem assumes that processors have *fail-silent* semantics, Sequoia assumes that processors have *fail-arbitrary* semantics and employs active replication (a processor pair) to implement a processor with real *fail-silent* semantics. A simplified representation of the Sequoia architecture is shown in Figure 10.

Figure 10 Sequoia

A Sequoia system consists of a number of processing elements (PEs) and memory elements (MEs), connected via a dual bus. Each PE is constructed using two processors which operate in *lock-step* execution. A comparator detects any difference in their behaviour and ensures that PEs have *fail-silent* semantics.

Each PE contains a cache memory. A process P executing on a PE uses this cache memory to store its data; all read and write requests operate on the cache. Periodically, the contents of the cache are flushed to two distinct MEs, thereby establishing a replicated checkpoint.

The code of a process is stored in an ME. If a PE fails, each process residing on the failed PE is restarted on another PE, beginning execution at its last checkpoint.

When implementing a PE with *fail-silent* semantics, only the failure of a whole processor is considered. Failures of MEs or busses, on the other hand, are dealt-with on a much finer granularity.

Data is protected by error-detecting codes while stored in a PE cache, in an ME or while in transit over a bus. The hardware implementing storage and data paths is partitioned such that no two bits of the same byte have a common component. Thus failure of a single component can only produce a single-bit error in any byte and all such errors are detectable. If an error is detected, the byte may be discarded and the component which sent it then has *fail-silent* semantics.

If an ME fails, a PE can always obtain data from the other ME to which it checkpoints. Read-only data is treated as a special case; it is not checkpointed. Consequently, it is stored on only one ME. If that ME fails, the data is restored from disc.

All Sequoia components thus have *fail-silent* semantics, either through active replication (PEs) or error detection (MEs and busses). Replication of all code and data, using checkpoints and disc back-ups, ensures that the execution of a failed process may be resumed elsewhere.

Processors within a PE operate in *lock-step* execution and receive exactly the same input data. External events are synchronized to this execution, so non-determinism within process replicas cannot cause state divergence among process replicas.

In the event of a failure, execution of a process is resumed by another PE. The new process inherits its history (its imaginary path of execution) from the old process via the latest checkpoint, so the path of execution of the process may be non-deterministic without causing state divergence.

# 3.4 The Stratus Computer System

)

)

)

)

)

)

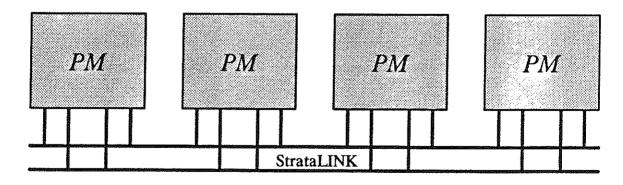

The Stratus computer system [15][16][18][24] is another commercial distributed computing system for on-line transaction processing. Stratus assumes that processors have fail-arbitrary semantics and employs active replication (a processor pair) to implement a processor with real fail-silent semantics (like Sequoia). Active replication is then used again to mask the fail-silent failure of a processor pair.

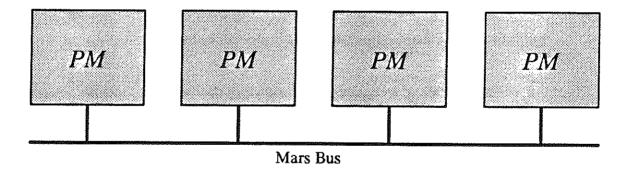

A Stratus system consists of a number of processing modules (PM) connected by a dual bus called StrataLINK, as shown in Figure 11.

Figure 11 The Stratus Computer System

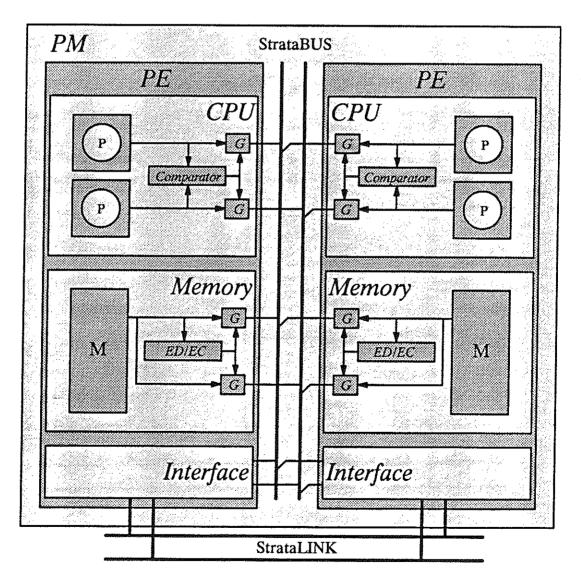

Each processing module consists of two identical processing elements (PE), connected by a dual bus called StrataBUS, as shown in Figure 12.

Each processing element consists of a number of components (CPU, memory etc) which constitute the smallest replaceable unit (SRU) of the system.

A CPU component is constructed from two identical processors operating in *lock-step* execution (like Sequoia). The outputs of the two processors are compared in hardware. As long as they match, outputs are gated onto StrataBUS. If a disagreement is detected, the outputs are not propagated, the component is isolated from StrataBUS and thus has *fail-silent* semantics.

Figure 12 A Stratus Processing Module

A memory component contains error detection/correction circuits which prevents the propagation of erroneous data. A memory component therefore also has *fail-silent* semantics.

Stratus may also contain a number of other component types (not shown) such as disc controllers. In all cases, components have *fail-silent* semantics.

When a component in a PE issues/receives a message on StrataBUS, the corresponding component (in the other PE of the same PM) also issues/receives the same message (in the absence of failures). So when a single failure occurs, there is always at least one message issued/received and the failure is masked.

The processors which make-up the two CPU components in a processing module are fed exactly the same inputs in the same order in *lock-step*. Thus all four processors in a processing module operate in *lock-step* execution. Processes may therefore contain non-determinism without causing state-divergence.

#### 3.5 SIFT

:)

.)

()

)

)

SIFT (Software Implemented Fault Tolerance) [17][19][28] is an ultra-reliable computer for critical aircraft control applications.

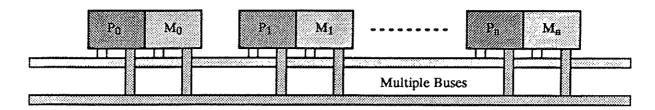

The physical architecture of the SIFT system is shown in Figure 13. It is composed of a number of processors  $P_i$ , each with its own memory  $M_i$ . Processors and memory are connected to a number of data busses. A processor may read or write its own memory but may only read the memory of other processors.

Every processor executes one or more processes. Every process is replicated and each replicate executed on a different processor. Processes are iterative in nature. Each process repeatedly inputs data, performs some calculation and outputs the results. Data produced by a process replica is deposited in its own memory. Data to be input by

Figure 13 The Physical Architecture of SIFT

a process is read from the memory of several replicas. Each read operation is performed over a different bus, and the results combined through majority voting to produce a single input to the process. In this way, the failure of a single process replica (through the failure of its host processor) or the failure of a bus will be masked.

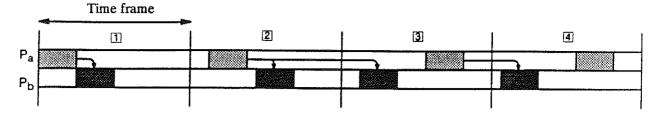

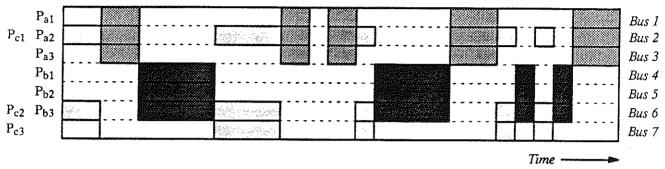

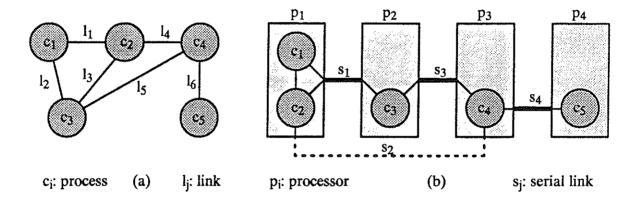

An iteration rate is specified for each process. The scheduler guarantees that a particular iteration of a task will be completed within the *time frame* for that iteration. Execution may take place at any point during the *time frame* but the results will be available by the end. Now suppose that a process  $P_a$  provides input data for another process  $P_b$  and that both processes have the same iteration rate, Figure 14 depicts four successive *time frames* in their execution. In some *time frames*  $P_a$  will complete before  $P_b$  and in others the converse will be true and the order may vary among the replicas of a process. If  $P_b$  were to take its data directly from  $P_a$ , this data could be from the same iteration (*time frames* 1 and 2) or from the previous iteration (time frames 3 and 4), as shown by the curved arrows in Figure 14. Since the order of execution may vary among replicas, some replicas will use data from the same iteration and some from the previous iteration. Unchecked, this could lead to state divergence within the replicas.

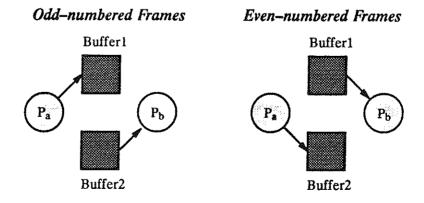

The problem is solved by the double-buffering of results passed from  $P_a$  to  $P_b$ , as shown in Figure 15. During odd-numbered *time frames*  $P_a$  outputs data to *buffer 1* while  $P_b$  inputs data from *buffer 2*. During even-numbered *time frames*  $P_a$  outputs data to *buffer 2* while  $P_b$  inputs data from *buffer 1*. In this way, the replicas of  $P_b$  will all use

3)

)

)

)

)

)

Figure 14 Process Execution

the data produced by P<sub>a</sub> in the previous iteration and state divergence will be prevented.

The clocks of all processors are *loosely* synchronized to within  $50\mu s$  (clock synchronization is another form of the *interactive consistency problem*, discovered and solved by the SIFT designers). So the time frames of different processors will also be synchronized to within  $50\mu s$ . Now suppose the clock of  $P_b$  is running  $50\mu s$  faster than that of  $P_a$  and  $P_a$  outputs its data to the buffer right at the end of a *time frame* (as determined by the clock of  $P_a$ ). If  $P_b$  inputs its data from the buffer right at the start of a *time frame* (as determined by the clock of  $P_b$ ), it could precede the data output by  $50\mu s$  and the data would thus be two iterations old. It is necessary therefore to separate the input and output of data by, for example, preventing the inputting of data until at least  $50\mu s$  into the *time frame*. The proportion of the *time frame* available for input is then reduced by  $50\mu s$ .

Figure 15 Double-buffering

SIFT processes must be deterministic. However, non-determinism may be incorporated into process scheduling by synchronizing asynchronous events to time-frame boundaries. In this way, either all process replicas will see a given event at the start of their execution, or none will.

With the bus-based SIFT architecture, data values are fetched from other processors and voted when required, incurring a delay. In a development of SIFT [29], the data is broadcast and voted in advance. So when required, it is available locally without a delay.

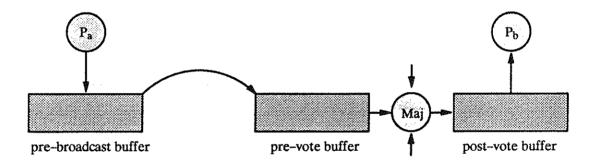

The double-buffering scheme of Figure 15 is not sufficient and must be expanded, as shown in Figure 16.

Figure 16 Modified Buffering

Now suppose that a process  $P_a$  provides input data for another process  $P_b$ .  $P_a$  places its data in the *pre-broadcast buffer* some time during its *time-frame* of execution. At the end of that *time-frame*, the data is broadcast to the processor executing  $P_b$ , where it is placed in a *pre-vote buffer*. When a majority of data copies have been received from replicas of  $P_a$ , the data is placed in the *post-vote buffer*. The broadcasts and voting take place during the *time-frame* following that in which  $P_a$  is executed, so the data is not available to  $P_b$  until the end of that *time-frame*.  $P_a$  and  $P_b$  should not therefore be scheduled for adjacent *time-frames* unless additional double-buffering is available.

## 3.5.1 SIFT - An Extension

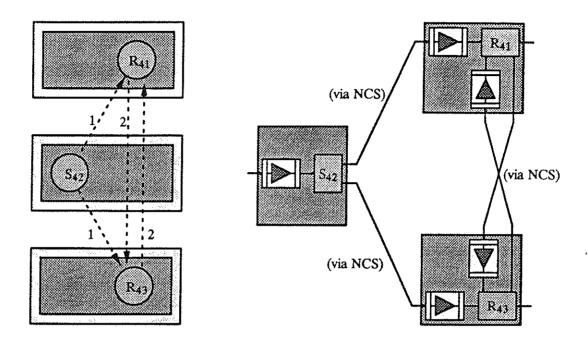

A number of modifications to the SIFT strategy were proposed in [80] in order that some of its disadvantages may be overcome while still preventing state divergence. In both the modifications presented in this section, the process need not be iterative and no planned scheduling is necessary. But the rather restrictive assumption is made that a message cannot be lost, only corrupted.

In the first modification, two additional assumptions are made:

- Al A process P<sub>a</sub> may send a message to the replicas of another process P<sub>b</sub> in an indivisible way.

- A2 The replicas of  $P_b$  process messages in an identical order.

The assumptions can be satisfied by centralizing communication. The multiple bus structure of SIFT is replaced by a single bus. To satisfy AI, a message is broadcast to either all of the replicas of  $P_b$  or none of them (bus failures are not considered). To satisfy A2, a replica of  $P_b$  will attach a *timestamp* to every message it receives and process messages from various sources in order of their *timestamps* (oldest first). Since the *timestamps* are only used by the processor which appended them, their absolute value is unimportant and hence there is no need for the synchronization of processor clocks.

It may be noted that the author has in fact described an atomic broadcast (see Section 5.3) which relies on trusted hardware for its implementation (the bus). The assumptions AI and A2 are satisfied by the atomicity and order properties of the atomic broadcast. The third property of the atomic broadcast, termination, is not considered. The replicas of  $P_a$  will each try to broadcast the same data, so in the absence of faults, each replica of  $P_b$  will receive three copies of every message and a mechanism for duplicate removal is necessary.

)

Although this solution removes some of the restrictions of the original SIFT approach to preventing state divergence, the requirement for a single bus creates a single point of failure and does not lend itself to the construction of massively parallel systems.

In the second solution, the need for a single bus is removed. A process  $P_b$  no longer has direct access to the output data of  $P_a$ . Instead, the replicas of  $P_b$  periodically perform an *interactive consistency* algorithm to agree on a set of messages which have arrived at or are about to arrive at  $P_b$ . They then independently order the set using some

deterministic algorithm, appending a sequence number to each message and processing them in order of sequence number.

Any implementation of the *interactive consistency* algorithm would have to solve the *Byzantine Generals Problem* of Section 2.4.2. In fact, the second solution to preventing state divergence is similar to ours except that the messages are *atomically broadcast* periodically in *batches* (instead of singly in advance), sequence numbers are used to order messages (instead of a *queue*), the process model is limited to *blocking* input (see Section 6.2.1) and the clocks of <u>all</u> processors must be synchronized.

#### 3.6 Mars

The Maintainable Real-Time System (Mars [31][32][33]) was designed for real-time control applications where reliability, availability and safety are of paramount importance. The simplified physical architecture of a Mars cluster is shown in Figure 17.

Figure 17 A Mars Cluster

It consists of a number of processors which are assumed to have *fail-silent* semantics, connected via a TDMA bus, called Mars Bus. A number of Mars clusters may be connected in a hierarchical structure (not shown).

The clocks of all processors are synchronized to create a fault-tolerant global timebase called system time. The scheduling of tasks is pre-planned and conforms to

one of a finite set of schedules, which may be changed to give the system a new phase or mode.

Processes communicate using state messages and event messages. The semantics of a state message is similar to that of a global variable. That is, a new version of a particular state message updates (overwrites) an old one and state messages are not consumed when read. The semantics of an event message is similar to that of a conventional message. That is, event messages are queued and an event message is consumed when read.

All messages carry a validity timestamp which, when it expires, causes a state message to become invalid or an event message to be discarded.

Mars uses active replicateion. If processes were allowed immediate access to messages, state divergence could occur, because message arrival is asynchronous with respect to process execution. Instead, all messages are buffered. Periodically, a clock-driven interrupt routine is executed which acts on all buffered messages to create a new *image set*, representing a new global state.

Process scheduling, bus scheduling and clock-driven interrupts are all synchronized. So when process replicas perform a *read* operation, they will all read from the same image set and state divergence will be prevented.

### **3.7 FTMP**

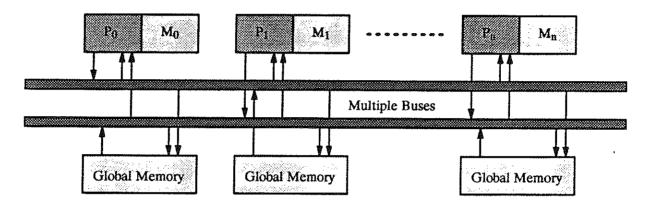

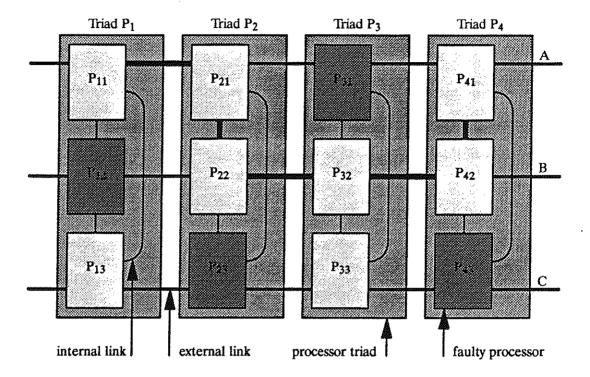

The Fault Tolerant Multiprocessor (FTMP) [17][19][34] was designed as part of a commercial aircraft fly-by-wire program. The physical architecture of an FTMP system is shown in Figure 18.

Like SIFT, it is composed of a number of processors P<sub>i</sub>, each with its own memory M<sub>i</sub>, collectively termed a processing module. Unlike SIFT however, only processors are

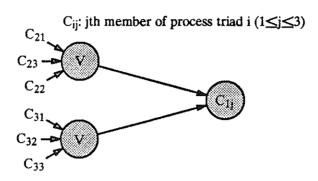

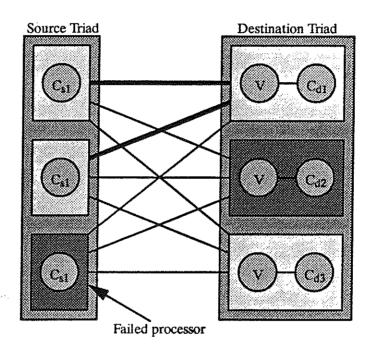

connected to the multiple data busses, the memory remains private to its attached processor. Instead, there are a number of global memory modules, also connected to the multiple busses and accessible to all processors. Any module, whether a processing or memory module, may receive data on all busses but may send data on only one (the choice of this bus is quasi-static but reconfigurable). Modules are logically grouped into triads such that each member sends its data on a different bus.

Figure 18 The Physical Architecture of FTMP

Every processor executes exactly one process (at any given point in time). Every process is replicated (to degree of three) and each replica executed on a different member of a processor triad. When a process triad sends a message to another triad, three messages are sent, one from each replica. These three messages will necessarily be sent on different busses (a bus triad). Each replica in the destination triad receives all three messages, one from each bus, combining them in hardware to form a majority. As with SIFT, the failure of a single process replica (through the failure of its host processor) or the failure of a bus will be masked. Although the majority is formed by hardware, each member of the destination triad has its own voter. So a failure of the voter will be treated as a failure of the attached module, ie there is no *trusted* hardware.

All module clocks are *tightly* synchronized using a fault-tolerant hardware clock. So the processes of a triad remain in *lock-step* execution and will perform data input and output requests synchronously. Although process triads operate independently, their

access to the multiple busses is strictly controlled such that the processors of a triad are granted access simultaneously and exclusively, even if the two bus triads concerned have no common members (as shown in Figure 19 for process triads  $P_a$ , and  $P_b$ ). That is, at any point in time, there may only be one active bus triad.

Figure 19 Bus Activity

Although there are multiple busses as in SIFT, the enforced sequentially of bus traffic limits the bandwidth to that of a single bus no matter how many busses are available. This bandwidth would be insufficient for large systems.

Bus transfers thus constitute an ordering mechanism which eliminates the possibility of state divergence within *deterministic* process replicas by centralizing communication in a way reminiscent of that described in Section 3.5.1. Note that the system behaves as though three *atomic broadcasts* were being performed in parallel, one from each of the replicas.

Because the members of a processor triad operate in *lock-step* execution, processes may contain *non-determinism* without causing state divergence.

#### 3.8 FTP

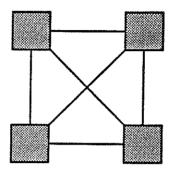

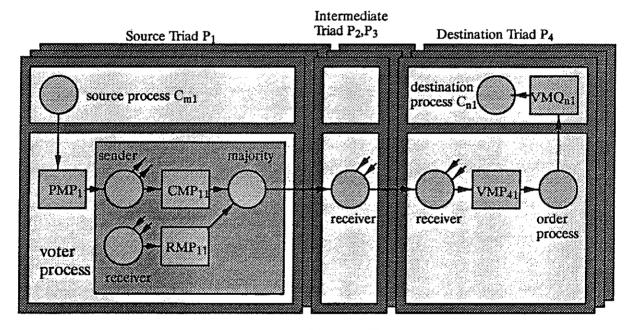

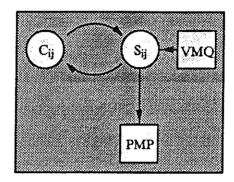

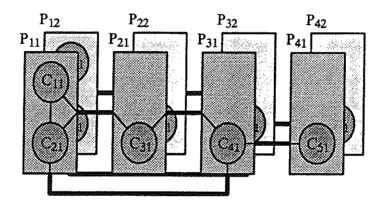

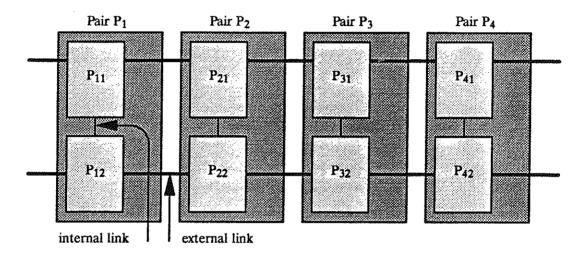

The Fault Tolerant Processor (FTP) [19][35][36] is a derivative of FTMP designed for nuclear power plant applications. The system consists of four processors which are fully connected as shown in Figure 20.