## DESIGN AND DEVELOPMENT OF

# **ALGORITHMS FOR**

# FAULT TOLERANT DISTRIBUTED

# **SYSTEMS**

Paul D. Ezhilchelvan

Ph.D. Thesis

NEWCASTLE UNIVERSITY LIBRARY 089 05273 X THESIS L3517

University of Newcastle upon Tyne

**Computing Laboratory**

September 1989

## ABSTRACT

This thesis describes the design and development of algorithms for fault tolerant distributed systems. The development of such algorithms requires making assumptions about the types of component faults for which tolerance is to be provided. Such assumptions must be specified accurately. To this end, this thesis develops a classification of faults in systems. This fault classification identifies a range of fault types from the most restricted to the least restricted. For each fault type, an algorithm for reaching distributed agreement in the presence of a bounded number of faulty processors is developed, and thus a family of agreement algorithms is presented. The influence of the various fault types on the complexities of these algorithms is discussed. Early stopping algorithms are also developed for selected fault types and the influence of fault types on the early stopping conditions of the respective algorithms is analysed. The problem of evaluating the performance of distributed replicated systems which will require agreement algorithms is considered next. As a first step in the direction of meeting this challenging task, a pipeline triple modular redundant system is considered and analytical methods are derived to evaluate the performance of such a system. Finally, the accuracy of these methods is examined using computer simulations.

## **ACKNOWLEDGEMENTS**

A special debt of gratitude is due to Professor Santosh Shrivastava for his continuous and constructive advice in supervising this thesis. In particular, his scrupulous reading and criticisms of preliminary drafts have provided me with invaluable guidance. I am grateful to him for his comments and criticisms. I am pleased to acknowledge that Professor Shrivastava and I collaborated for the work on fault classification.

I am also grateful to my colleague Dr. Isi Mitrani with whom I established a very fruitful collaboration for the work on performance evaluation. My thanks are also due to Professor Brian Randell for his technical advice during my research work and for his careful reading of earlier versions of some of the chapters in this thesis.

I would like to thank all my colleagues at the Computing Laboratory who discussed with me the work described in this thesis. In particular, I wish to thank Dr. Neil Speirs for his careful reading of some of the crucial parts of my thesis, that revealed some inaccuracies in the text.

I also acknowledge my wife who typed some parts of my thesis and gave constant encouragement. The UK Science and Engineering Research Council (SERC), and the DELTA-4 consortium of ESPIRIT research programme are also acknowledged for their financial support.

Finally, my namaskhaars are offered to the Almighty.

## CONTENTS

| Chapter 1. Introduction                          | . 1 |

|--------------------------------------------------|-----|

| Chapter 2. A Classification of Faults in Systems | 12  |

| 2.1. Introduction                                | 12  |

| 2.2. Components and Their Behaviour              | 13  |

| 2.2.1. Fault/Failure Classification              | 15  |

| 2.2.2. Fault/Failure Ordering                    | 19  |

| 2.2.3. Selfchecking Components                   | 22  |

| 2.2.4. Selecting Fault Models for Components     | 24  |

| 2.3. Replicated Responses                        | 25  |

| 2.3.1. Fault/Failure Classification              | 27  |

| 2.3.2. Fault/Failure Ordering                    | 31  |

| 2.4. Composite Components                        | 33  |

| 2.4.1. Processor with a Clock                    | 33  |

| 2.4.1.1. Types of Clock Faults                   | 34  |

| 2.4.1.2. Types of Processor Faults               | 36  |

| 2.4.2. Processor Interconnections                | 37  |

| 2.4.2.1. Processors with Unreplicated Responses  | 37  |

| 2.4.2.2. Composite Component with Replicated     |     |

| Responses                                        | 38  |

| 2.5. Concluding Remarks                          | 41  |

----

| Chapter 3. A Family Of Agreement Algorithms                  | 42 |

|--------------------------------------------------------------|----|

| 3.1. Introduction                                            | 42 |

| 3.2. Assumptions                                             | 46 |

| 3.2.1. Clock Synchronism                                     | 46 |

| 3.2.2. Message Signatures and Authentication                 | 46 |

| 3.2.3. Bounded Communication Delay                           | 48 |

| 3.2.4. Message Timestamps                                    | 50 |

| 3.2.5. Unanimity and Validity Conditions                     | 50 |

| 3.3. Consistent Omission Fault                               | 52 |

| 3.3.1. Algorithm ACO - Algorithm (for)                       |    |

| Consistent Omission (Faults) .                               | 52 |

| 3.4. Consistent Value Fault                                  | 53 |

| 3.5. Consistent Timing Fault                                 | 54 |

| 3.5.1. Algorithm ACT-1 for Consistent Timing Faults          | 55 |

| 3.5.2. Algorithm ACT-2 for Overloaded Processors             | 61 |

| 3.6. Consistent Emission Fault                               | 67 |

| <b>3.6.1.</b> Algorithm ACE-1 for Consistent Emission Faults | 69 |

| <b>3.6.2. Algorithm ACE-2 for Overloaded Processors</b>      | 75 |

| 3.7. Omission Fault                                          | 80 |

| 3.7.1. Algorithm AO for Omission Faults                      | 81 |

| 3.8. Value Fault                                             | 83 |

| 3.8.1. Algorithm AV for Value Faults                         | 84 |

| 3.9. Timing Fault and Emission Fault                         | 87 |

| 3.10. Byzantine Fault                                        | 87 |

| <b>3.10.1. Algorithm AB for Byzantine Faults</b>             | 88 |

| 3.11. The Generic Algorithm                                  | 89 |

| 3.11.1. Discussions                                          | 94 |

| 3.12. Concluding Remarks                                     | 97 |

|                                                              |    |

| Omission and Timing Fault Types .                         | 99         |

|-----------------------------------------------------------|------------|

| 4.1. Introduction                                         | 99         |

| 4.2. Assumptions and Notations 10                         | 03         |

| 4.3. Permanent Omission Fault Tolerant Algorithm 10       | 05         |

| 4.3.1. Correctness of the Algorithm 10                    | 09         |

| 4.4. Omission Fault Tolerant Algorithm 1                  | 17         |

| 4.4.1. Correctness of the Algorithm 1                     | 18         |

| 4.5. Timing Fault Tolerant Algorithm 12                   | 20         |

| 4.5.1. Correctness of the Algorithm 12                    | 23         |

| 4.6. Consistently Late Timing Fault Tolerant Algorithm 12 | 26         |

| <b>4.6.1. Assumptions</b>                                 | 26         |

| 4.6.2. Development of the Algorithm 12                    | 27         |

| <b>4.6.3.</b> The Algorithm                               | <b>3</b> 0 |

| 4.6.4. Correctness of the Algorithm 13                    | 32         |

| 4.7. Concluding Remarks 13                                | 36         |

|                                                           |            |

| Chapter 5. Performance Evaluation 13                      | 38         |

| 5.1. Introduction                                         | 38         |

| 5.2. Distributed Replicated Processing Systems 14         | 40         |

| 5.3. Model Definition 14                                  | 45         |

| 5.4. Analytical Approximations 14                         | 49         |

| 5.4.1. Operative State Distribution for Model 0 1         | 54         |

| 5.4.2. Operative State Distribution for Model 1 18        | 57         |

Chapter 4. Early Stopping Agreement Algorithms under

| 5.5. Experimental Results                 | 159 |

|-------------------------------------------|-----|

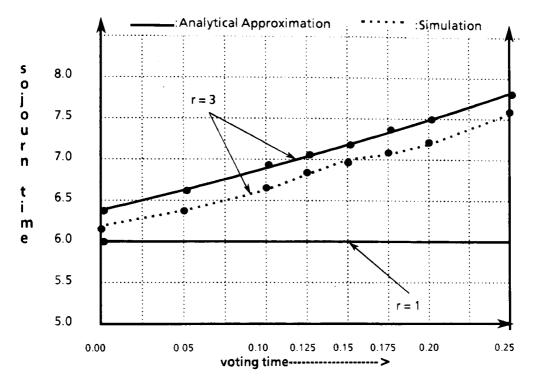

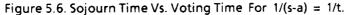

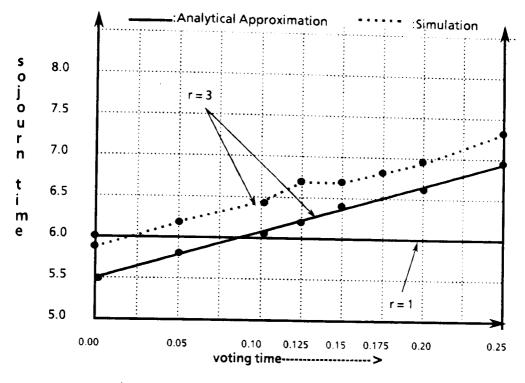

| 5.5.1. Results for Model 0                | 161 |

| 5.5.1.1. Group 1                          | 161 |

| 5.5.1.2. Group 2                          | 166 |

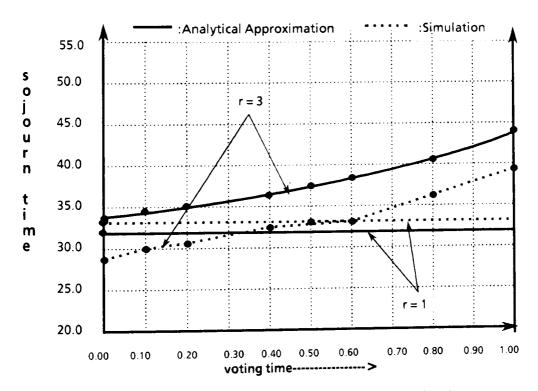

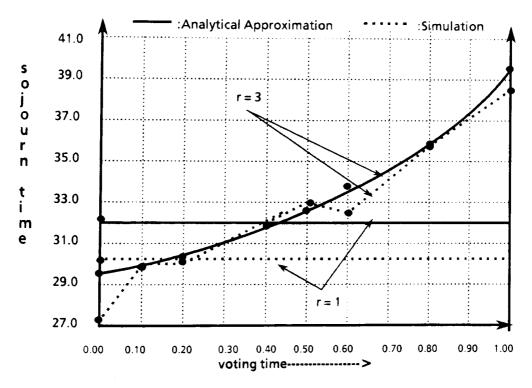

| 5.5.2. Results for Model 1                | 171 |

| 5.5.3. Computer Times for Simulations and |     |

| Analytical Estmations                     | 175 |

| 5.6. Concluding Remarks                   | 176 |

| Chapter 6. Conclusions                    | 178 |

| 6.1. Directions for Further Research      | 183 |

|                                           |     |

| References                                | 186 |

.

.....

#### **CHAPTER 1**

## **INTRODUCTION**

A system can be considered to be made up of a set of components which interact under the control of a design. A component of a system is a system by itself and can be considered, where appropriate, to be atomic with the implication that any further decomposition of a component is of no interest and can be ignored. According to the terminology presented in [Ander81, Lapri85], *faults* in a system are the (potential or actual) causes of the failures of the system. A violation from the specified behaviour of a system will be termed a *failure*. Given the complexity of modern computing systems, one approach for making them reliable is to accept that despite whatever efforts that have been made to avoid or remove faults, systems can nevertheless remain potentially faulty and to incorporate provisions to enable the system to cope with the faults that remain or develop. This approach is termed the fault tolerance approach and is generally considered to be necessary for building systems that can be assured of providing a high degree of operational reliability to the user(s) of the system.

A given component can usually fail in many different ways. That is, a faulty component can have many failure modes. Thus, in order to be able to provide any kind of guarantee of service, the designer of a fault tolerant system should specify not only the maximum number of components that he presumes might be faulty, but also the types of failures a faulty component is presumed to have. In other words, the fault tolerance specification should state explicitly the type and number of component failures a system is supposed to tolerate. Then, provided the actual component failures that occur do not violate these assumptions and the fault tolerance strategies are correctly designed, the overall system will not fail. Putting this another way, it is meaningless to claim that a system is fault tolerant, without indicating the assumptions that have been made regarding the number and types of component failures that could occur.

#### 1.1. Fault and failure classification

A distributed system will be defined as a collection of autonomous processors which can communicate with each other, and each of which can provide one or more services and can cooperate with other processors on a common goal or task [Enslo78]. By considering processors as components in a distributed system, different types of processor failures have been considered in the literature. One of the most restricted failure types is an omission failure [Mohan83] whereby a faulty processor fails by producing no output for a given input that requires an output to be produced by the processor. A fault that causes such a failure will be called an omission fault. When a processor's omission failure persists for all such inputs, the processor will be said to have failed in a permanent omission manner. With subtle differences, a permanent omission failure has been termed in the literature as processor crash, halting failure [Birma87], fail-silent failure [Powel88], and fail-stop failure [Schli83]. Failures of these types are relatively easy to tolerate when compared to Byzantine failures. A Byzantine failure is caused by a Byzantine fault and is any violation of the specified behaviour. A Byzantine faulty processor is customarily considered to be capable of being malicious in trying to "sabotage" any fault tolerance provisions in the system. Faults that can appear to be of malicious nature were first discussed in [Daly73, Davie78] and have been considered, for example, in the

design of SIFT system [Wensl78] and in [Lampo82] where the name "Byzantine" was coined.

A significant advantage to be gained by assuming that processors may have Byzantine failures is that the analysis required for justifying the fault assumptions made about the processors of systems used in life critical systems is greatly simplified. In order to consider anything less than Byzantine failure behaviour on the part of a processor in the design of a fault tolerant system, one must provide a convincing argument (based on knowledge of the processor's design, its components, and any provisions that the design considers for faults in these components) of why it can fail only in some restricted manner. Since, in the Byzantine fault model, no assumption needs to be made about failure modes of a processor, system analysis is simplified. However, attempts to build systems which can tolerate Byzantine failures of processors involve a significant cost in terms of the number of redundant processors required in the system, and of message and time complexity in providing the system services. For example, when processors are considered to suffer only omission failures, only one (redundant) processor is required in addition to the number of processors that are assumed to fail in providing a service; when Byzantine failures are considered, the nonfaulty processors in the system should form a majority if they are to produce identical outputs for a given input (as in systems with majority voting [Lyons62]), and they should out-number the faulty processors by more than three to one [Pease80] if their outputs are unlikely to be identical (such as outputting the reading of a local clock [Lampo85]).

In the design of a reliable, but not life critical systems, provisions for tolerance to Byzantine failures may be sacrificed in the interest of economic considerations. In such a situation, if omission failures are considered to be too restrictive, then the design of a fault tolerant system requires a realistic means of identifying failure types that are more restricted than in the Byzantine model and less restricted than in the omission model. In this thesis we present, in chapter 2, a fault and failure classification using "expected-value" and "timing" as the two properties of a component's response. The resulting fault and failure classes are ordered according to their relative restrictiveness. Examples are drawn from distributed systems. We further extend this classification to apply to a particularly important type of components that are required to provide replicated responses. Our fault and failure classification is an improvement over [Mohan83, Crist85], and our earlier classification in [Ezhil86]. An interesting observation from our classification of faults and failures is that for a given problem in distributed computing one can design a family of algorithms - from relatively simple ones tolerating failures of restricted types to increasingly complex ones tolerating failures of less restricted (and unrestricted) types. One such fundamental problem considered here will be the agreement problem.

### 1.2. The agreement problem and algorithms

Processors in a distributed system cooperate on a common goal or a task. Fundamental to such cooperation is the problem of agreeing on a piece of data upon which a computation depends. For example, the data managers in a distributed database system need to agree on whether to commit or abort a given transaction [Gray79]. In a replicated database system, the processors need to agree on an identical sequence of incoming transactions [Garci86], and might need to agree on where a particular piece of data (a file, for example) is supposed to reside [Giffo79, Popek81]. In a flight control system for an airplane [Wens178], the engine control module and the flight surface control module need to agree on whether to continue or abort a landing in progress. The key point is not *what* the processors are agreeing on but that they must all come to the *same* conclusion.

An obvious approach to achieving agreement is for the processors to vote and agree on the majority value. In the absence of faults, this works fine, but in a close election, the vote of one faulty processor can swing the outcome. Suppose distinct non-faulty processors receive conflicting votes from a faulty processor, then they might reach conflicting conclusions and hence fail to reach agreement. Thus specific algorithms need to be developed to guarantee that non-faulty processors reach agreement by arriving at the same conclusion. This problem is called the agreement problem [Lampo82] or the interactive consistency problem [Pease80] in the literature and can be briefly described as follows: A processor, called the sender, in a distributed system of at least three processors wants to disseminate a value to all other processors. The non-faulty processors in the system, which are at least two in number, will be said to have reached agreement on the sender's value if they all decide on the same value, and on the sent value if the sender is non-faulty. Extending a solution to the agreement problem mentioned above into a general context where every processor can act as a sender is straightforward.

The agreement problem has been studied under a variety of assumptions mainly concerning the synchrony of processors and message communication and the types of faults processors and communication medium are subjected to. (A brief survey is presented in [Fisch83a].) This thesis presents, in chapters 3 and 4, deterministic algorithms developed for a distributed system where relative processing speeds of, and message communication delays between, processors are assumed to be known and bounded. An upper bound on the number of processors that can possibly fail is also assumed. Execution of these algorithms will guarantee agreement in a known and bounded time interval. Algorithms are developed in two contexts: the sender processor's broadcast time is not known, and is known, to other processors a priori. Algorithms designed in the context of unknown broadcast time can be developed into broadcast protocols as in [Crist85] which can provide agreement and ordering abstractions [Schne86] which are essential for constructing systems with replicated processing. In this context, in chapter 3, we develop agreement algorithms, and show them to be correct, for faults of each type defined in our classification and thus present a family of agreement algorithms illustrating the relative complexity of these algorithms.

Solutions to the agreement problem when the broadcast time of the sender is known can be useful in systems such as a distributed database system where data managers have a prior knowledge of the time the agreement on commit or abort decision for a given transaction should commence. When processors in a distributed system know the sender's broadcast time a priori, it may be desirable to have them reach agreement early, when the actual number of failed processors is less than the expected. Agreement algorithms that guarantee an early agreement in the presence of less-thanexpected number of processor failures are called early stopping algorithms [Dolev82a]. In an execution of an early stopping algorithm, non-faulty processors may reach agreement at different timing instants; some can be earlier than the others. So, these algorithms are useful in applications where processors, following an agreement, carry out actions that need not be timecoordinated. In distributed transaction commit, for example, non-faulty processors need not commit (or abort) a transaction at a coordinated time, so long as they all decide to do, and eventually do, the same thing; therefore, a

non-faulty processor can commit a transaction and continue processing as soon as it has reached a commit decision and thereby knows that all other non-faulty processors will eventually commit the transaction. For such applications, early stopping algorithms can be used to make the processors reach agreement as early as possible. The authors of [Dolev82a] considered Byzantine failures for developing an early stopping algorithm. In chapter 4 of this thesis, we consider a few restricted types of failures and provide early stopping algorithms that are faster than the ones reported in the literature for these failure types.

### 1.3. Performance evaluation

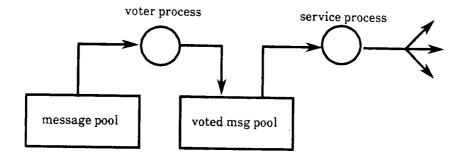

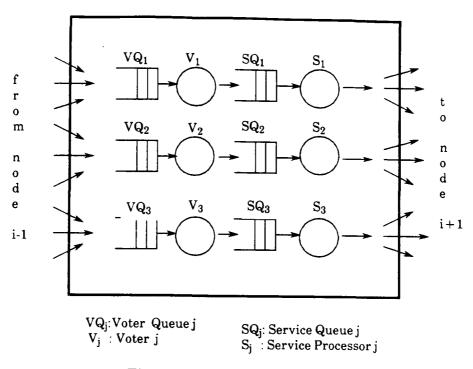

The agreement algorithms presented in chapters 3 and 4 are useful in constructing systems with replicated processing. Replicated processing with majority voting - N modular redundant processing - provides a powerful means of constructing fault tolerant systems [Mathu70, Carte79]. In N modular redundant processing, NMR processing for short, a given computational task is carried out in N, N  $\geq$  3, processing modules. These modules must not have any common mode of failures so that they can fail independently of each other. The results produced by these modules will be subject to a majority vote to obtain the final result. A majority vote is possible, and the final result will be correct, if (i) at least majority of the processing modules are non-faulty and (ii) non-faulty processing modules are to produce identical results. Thus, in NMR processing, tolerance can be provided to failures of at most less than half the number of modules and the failures may even be of Byzantine type.

Fundamental to the fault tolerance capabilities in NMR processing is that non-faulty modules produce identical results for a given computational task. Modules may maintain some state information which can affect

processing of a computational task and hence the results produced. In the case of a deterministic processing model, when non-faulty modules with identical state information process a given computational task, they undergo identical state transitions and produce identical results. Given that processing is deterministic and non-faulty modules have identical initial state information, it is necessary to guarantee that non-faulty modules process the computational tasks in an identical order. When modules can receive task messages from multiple sources or from a single source via different communication paths, they cannot be expected to receive task messages in an identical order. This means that non-faulty modules should agree on the processing order for every given task message to be processed. If it cannot be guaranteed that a source will provide different modules with task messages of identical contents, then non-faulty modules should not only agree on the processing order for a task message but also on the contents of the task message. The agreement algorithms presented in chapter 3 can be used to meet these requirements in systems with NMR processing.

The common form of NMR processing in practical systems is triple modular redundant processing, TMR processing for short, where three processing modules are used to process the computational tasks concurrently. FTMP (Fault tolerant Multiple processor) [Hopki78] achieves fault tolerance through TMR processing and is one of the early practical systems developed for flight control applications. The cost of fault tolerance in TMR processing (NMR processing in general) is mainly the redundant processing modules, the majority voters, and the time taken to agree on, and order, the input messages and to perform majority voting. This time overhead, among other factors, influences the response time for a given computational task - the overall time taken for the final (voted) result of a computational task to be obtained.

Consider a computational task being carried out by a TMR node - a triad of processors grouped for TMR processing. The three processors of the TMR node need not produce their results exactly at the same time, since their processing speeds may be different and they cannot be guaranteed to start processing the task exactly at the same time. Consequently, they may be producing their results to a voter at different timing instants. A majority vote for the final result cannot be carried out until at least two of the three processors have produced their results. If any one of these two processors has failed by producing incorrect results, then the results from the third processor has to be waited for, before performing a majority vote. Thus, the response time of a TMR node not only gets influenced by the time taken to carry out majority voting, agreement and ordering (on input messages) but also varies depending on whether all three or just two processors in a TMR node are non-faulty. This means that an evaluation of response times needs to consider the operational status of processors in the node. Thus, performance evaluation of a system with replicated processing should take into account of a number of factors such as voting times, processor failure modes and failure probabilities, processing and message transmission times, etc. This is a challenging task.

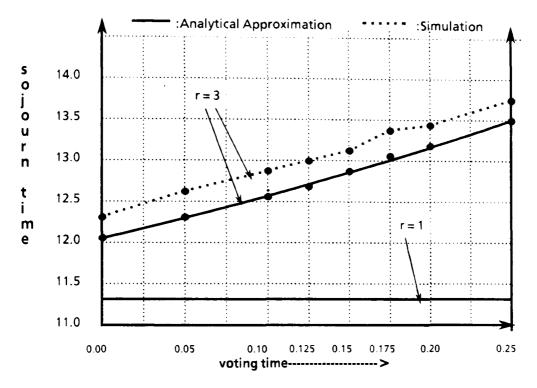

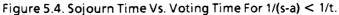

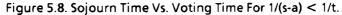

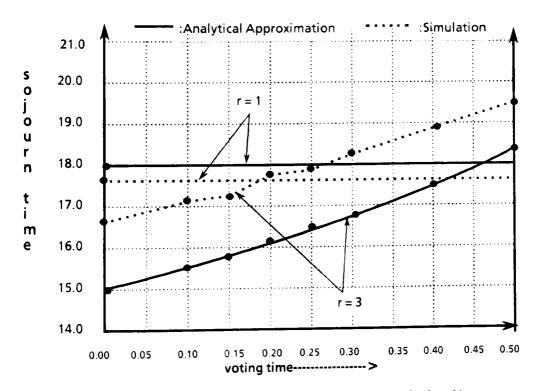

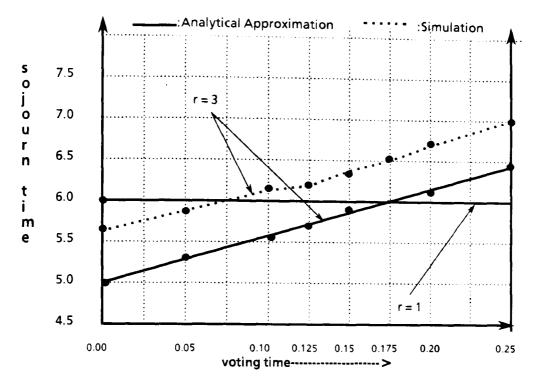

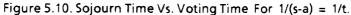

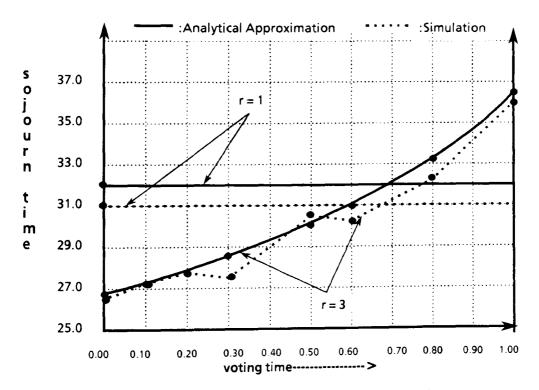

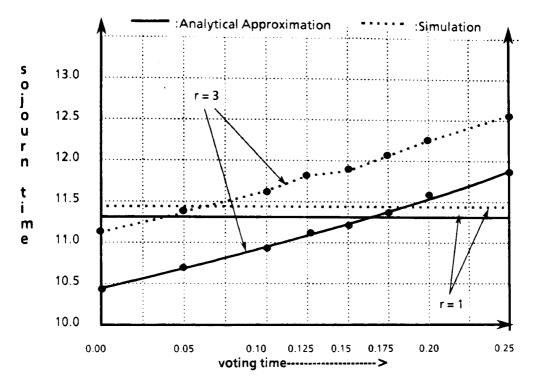

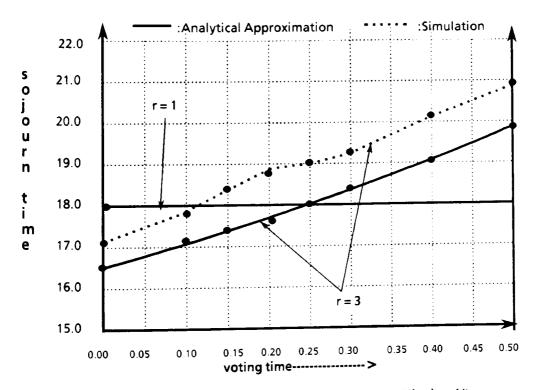

In chapter 5 of this thesis, we study the performance of a distributed replicated system that is made up of a collection of TMR nodes connected in tandem. We present analytical methods to evaluate the performance of such a TMR pipeline system. The derivation of these methods involve analytical approximations, the accuracy of which is examined by computer simulations. Despite their simplicity and roughness due to approximations, the analytical methods presented here can be observed to be quite accurate in estimating system performance measures. These methods can serve as alternatives to simulation methods, when the latter are considered to be expensive to carry out. We also examine the influence of majority voting times and processor failure rates on system performance. It should be mentioned here that performance evaluation of distributed replicated systems have not (yet) been reported in the literature and our work presented in this thesis, to the best of our knowledge, is the first of its kind.

To summarise the ideas presented in this thesis: A classification of component faults and failures is presented. Agreement algorithms are developed in the two contexts defined by whether the sender's broadcast time is or is not known to other processors in the system a priori. In the first context early stopping algorithms are developed for failures of selected types. In the second context, algorithms are developed for failures of each type defined in our classification - thus a family of algorithms is presented. Next we consider the problem of evaluating the performance of distributed systems which require agreement protocols. Analytical methods for evaluating the performance of a pipeline TMR system are derived based on some approximations, and the accuracy of these approximations is examined using computer simulations. The approximations turn out to estimate performance fairly accurately.

#### 1.4. Thesis organisation

In the next chapter, we present a classification of component faults and failures using "expected-value" and "timeliness" as the two properties of a component's response. We extend this classification to apply to components required to produce replicated responses. The different fault types defined are ordered in the form of a lattice according to their relative restrictiveness and the unrestricted type is shown to be Byzantine. Based on the fault and failure classifications for components with replicated and unreplicated responses, a fault analysis of composite components made up of potentially faulty components is performed. Composite components subject to such a fault analysis are a processor considered to be made up of computational unit and digital clock, and a distributed system made up of processors and communication subsystem.

In chapter 3, deterministic agreement algorithms tolerant to processor faults are developed in the context of the sender's broadcast time not being known a priori. The types of processor faults considered will be the ones that are defined in chapter 2. A generic algorithm is presented to collectively represent algorithms tolerant to different types of processor faults. Based on the generic algorithm, the influence of processor fault types on algorithm complexity is discussed. For processors in a distributed system having a prior knowledge of sender's broadcast time, early stopping agreement algorithms are presented in chapter 4. Only selected types of processor faults are considered. The early stopping capabilities and message requirement of algorithms presented in this chapter will reveal the fact that each algorithm has been developed making complete use of the distinct features that characterise the respective types of faults tolerated. Chapter 5 presents analytical methods for estimating the performance of a pipeline TMR system. Two system models are studied: in the first model faulty processors stay faulty until the observation period, and in the second faulty processors are repaired after a finite and random delay. The accuracy of analytical approximations involved in the derivation of the analytical methods is examined by computer simulations. Performance estimates obtained by analytical methods are observed to be reasonably close to simulation estimates. The influence of majority voting times and processor failure rates on system performance is also observed. Chapter 6 concludes the thesis and suggests directions for further research.

### CHAPTER 2

## A CLASSIFICATION OF FAULTS IN SYSTEMS

## 2.1. Introduction

A fault tolerant computing system must be capable of providing specified services in the presence of a finite number of component failures. In order to be able to provide any kind of guarantee of services, the system designer must specify what kinds of, and how many, component failures the system is intended to tolerate. Suppose a system is constructed out of n components, then its fault tolerance specification could be along the lines that if there are no more than f component failures (where f < n) and if each failure is of an assumed type, then the system will continue to function as specified. That is, the type of component failures a system is supposed to tolerate has to be stated explicitly. A given component can usually have many failure modes (that is, a failed component can behave in one of many different ways) some of which can be relatively easier to tolerate than others; at the same time, certain failure modes of a component are likely to occur with greater probability than others. Given that the failure data of system components, such as, failure modes and their probability of occurrences are available, the design of a reliable system will often involve making engineering judgements regarding the classes of component failures for which tolerance is to be provided. For example, if a particular type of component failure is hard to tolerate and if the probability of occurrence of such failures is extremely small, then, in applications that are not life critical, provisions for tolerating that type of failure may well be sacrificed in the interest of economic and performance considerations. An interesting observation is that for a given system function (e.g. maintaining consistency of replicated data in a distributed system), one can design a *family of algorithms* - from relatively simple ones tolerating restricted types of failures to increasingly complex ones tolerating less restricted (and unrestricted) types of failures.

In this chapter, we present a classification of component failures which we believe provides a convenient and realistic means for specifying faulty behaviour of components and for designing corresponding fault tolerant algorithms. Section 2.2 presents this classification. In section 2.3, we extend our classification to apply to a particularly important class of components that are required to provide *replicated responses*. In the following section we study the behaviour of systems composed of possibly faulty components. Section 2.5 concludes this chapter.

## 2.2. Components and Their Behaviour

A system can be considered to be made up of a set of components which interact under the control of a design. A component of a system is a system by itself and can be considered to be atomic with the implication that any further decomposition of a component is of no interest and can be ignored. A component's behaviour in response to an input from the environment will be defined by the component's specification prescribing state transitions and a real time interval within which the transitions should occur in response to a given input. Following the terminology developed elsewhere [Ander81, Lapri85], a component *fails*, when its behaviour deviates from that specified. The term *fault* will be used to refer to the cause of the failure. Consider an input that requires the component to produce an output. A *non-faulty* component, by definition, will produce (i.e. respond with) an output that is in accordance with the specification. The response of a faulty component, on the other hand, need not be as specified. Following [Kopet85], we will consider the response of a component for a given input to be correct, if not only the output value is as expected, but also the output is produced on time. Formally, a component's correct response will be defined as follows:

#### **Definition: Correct Response**

Let a component receive at time  $t_i$  an input requiring an output from the component and as a result respond by producing an output with value vat time  $t_j$ ,  $t_j > t_i$ . For that input, the response is correct iff:

(i) the value is as expected: v = w, where w is the expected value consistent with the specification; and,

(ii) it is produced on time:  $t_{\min} \le t_j - t_i \le t_{\max}$ , where  $[t_i + t_{\min}, t_i + t_{\max}]$  is the interval during which the specified output is expected to be produced; and  $t_{\min}$  ( $t_{\min} > 0$ ) and  $t_{\max}$  ( $t_{\max} > t_{\min}$ ) are constants denoting respectively the minimum delay time and maximum delay time for the output. A component's correct response for an input requiring an output can be expressed concisely as:

CR: v = w and  $t_{\min} \leq t_j - t_i \leq t_{\max}$ .

For notational convenience, CR will also be denoted as:

#### CR: expected - value and ontime.

The minimum delay time,  $t_{\min}$ , indicates that the output of a component cannot be produced instantaneously but must experience a finite minimum

delay of non-zero amount. The maximum delay time,  $t_{max}$ , indicates the upper bound on the output delay.

The above definition is based on the expected input-output behaviour of the component and does not refer to any internal state transitions caused by inputs. There can, however, be inputs that may require the component to behave by making appropriate changes in its internal state and by producing no output. The value w, and the quantities  $t_{max}$ ,  $t_{min}$  in the above definition are meaningful only when output values are expected to be produced by the component in response to inputs. This also implies that the definition is directly applicable to "demand driven" components: components that produce outputs in response to having received an input. However, there are also *autonomous components*, such as clocks, which continuously produce outputs. A treatment on the behaviour of such components will be presented in section 2.4.

#### **Definition: Incorrect Response**

A response will be said to be incorrect, if either the output value or the output timing or both are incorrect. The output value will be termed incorrect, if the value of the output produced is not the expected value consistent with the specification, i. e.  $v \neq w$ ; similarly, the output timing will be said to be incorrect, if the output is produced outside the expected interval, i.e. either  $t_j - t_i < t_{\min}$  (early) or  $t_j - t_i > t_{\max}$  (late).

## 2.2.1. Fault/Failure Classification

In the following, five classes of faults are presented. This classification has been developed by considering failures in the value domain, in the time domain, and then in both the domains. Our classification of faults is based on, and an improvement over, earlier work reported in [Mohan83, Crist85, Ezhil86].

### **Omission Fault/Failure**

A fault that causes a component not to respond to an input and, thereby, fail by not producing the expected output will be termed an *omission fault* and the corresponding failure an *omission failure*.

A component with an omission fault behaves in a very simple fashion: either a correct response is produced or no response is produced. A processor that (perhaps momentarily) stops functioning, a sensor that occasionally fails to produce output signals, and a communication link which loses messages are examples of components with omission faults. In the literature, many fault tolerant algorithms can be found to have been designed under this fault assumption.

## Value Fault/Failure

A fault that causes a component to respond, for a given input, within the correct time interval but with an incorrect value will be termed a *value fault*. The corresponding failure will be called a *value failure* which, using our notation, is defined as:

VF:  $v \neq w$  and  $t_{\min} \leq t_j - t_i \leq t_{\max}$ .

= **not** expected - value **and** ontime.

A processor producing erroneously computed values on time, a timely delivery of a corrupted message by a communication link are examples of value failures.

## **Timing Fault/Failure**

A timing fault causes a component to respond to a given input with the correct value but outside the correct interval (either early or late). The corresponding failure will be called a *timing failure*:

TF:

$$v = w$$

and  $(t_j - t_i < t_{\min} \text{ or } t_j - t_i > t_{\max})$ .

= expected-value and not ontime.

For example, an overloaded processor producing correct values with excessive delay and a fast timer which sends an early timeout signal, will be said to have suffered timing failures. A timing failure in which the response is produced late (early) will be called a late timing failure (an early timing failure). A late timing failure is also referred to as a performance failure [Crist86].

### **Emission Fault/Failure**

A component with an *emission fault* fails by producing an incorrect response to a given input. The corresponding failure is called an *emission failure*. Using our notation, an emission failure is:

$EF = \mathbf{not} CR$

$= v \neq w \text{ or } (t_j - t_i < t_{\min} \text{ or } t_j - t_i > t_{\max}).$

= not expected - value or not ontime.

An emission fault can cause a component to emit a response which can be incorrect in the value as well as in the time domains. Emission failures are a combination of value and timing failures. An overloaded processor that responds too late to a given input with erroneously computed values can be said to suffer an emission failure. Note that from the definitions of VF, TF, and EF, we have:

VF implies EF and TF implies EF.

Thus, value and timing failures (faults) are special cases of emission failures (faults).

### Byzantine (or General) Fault/Failure

In the above four failure classes, a component's failure modes have been defined by analysing the properties of an output for a given input. It is also possible to consider a faulty component to fail in an "arbitrary" manner, i.e., in a manner that cannot be perceived within the framework of the above failure classes. For example, a failed component may produce an output without a valid input. All such failure modes that cannot be considered to be in the above four failure classes will be included in the last *general* fault class:

A Byzantine fault causes a component to violate the specified inputoutput behaviour in any manner and a Byzantine failure will be any violation of a component's specified input-output behaviour.

By definition,

EF implies BF, where BF is a Byzantine failure.

Note that it is not generally feasible to enumerate all possible failure modes of a faulty component. A Byzantine faulty component is customarily considered in the literature to be capable of being "malicious" in its responses to its environment. The following examples of a faulty processor's behaviour in a distributed system can be considered to be malicious: a processor  $P_i$  masquerading as processor  $P_{j,j} \neq i$ , and  $P_i$  altering source/destination of a message it is relaying. Faults of malicious nature were first discussed in [Daly73, Davie78] and have been considered in system designs such as SIFT [Wensl78], and in algorithms for reaching agreement in a distributed system [Lampo82].

#### 2.2.2. Fault/Failure Ordering

A Byzantine fault causes any violation of a component's specified input-output behaviour; as such, no restrictions are applicable in the resulting faulty behaviour. All other fault types preclude certain types of faulty behaviour, the omission fault type being the most restrictive. Thus the omission and Byzantine faults represent two ends of the fault classification spectrum, with the other fault types placed in between. The relationship between the five types of faults can be further developed as follows.

If an omission failure can be interpreted as equivalent to 'producing a null value at some finite time', then it can be defined as follows:

OF: v = NULL and  $t_i < t_j < \infty$ .

Since v = NULL implies  $v \neq w$ , an omission failure as defined above can be seen as a special case of an emission failure: OF implies EF.

OF can also be shown to be a special case of VF, by reasoning as follows:

In a value failure, the incorrect output value can be a null value. Define a proper subset of value failures in which the output values are *NULL* as:

$VF_{null}$ : v = NULL and  $t_{\min} \le t_j - t_i \le t_{\max}$ .

By definition,  $VF_{null}$  implies VF and also implies OF. A null value produced on time is the same, for all practical reasons, as a null value produced at any time. Therefore,  $VF_{null}$  in which a null value is produced on time can be treated to be the same as (v = NULL and  $t_i < t_j < \infty$ ), and therefore to

represent OF itself; so OF implies VF in practice.

If an omission failure can be interpreted as equivalent to 'producing some value at the time of infinity', then, it can be defined also as:

*OF*:  $(v \neq NULL \text{ and } t_j = \infty)$ . Since  $t_j = \infty$  implies  $t_j - t_i > t_{max}$ , an omission failure as defined above can be seen as a special case of an emission failure: *OF* implies *EF*.

It can also be shown that OF implies TF, by using arguments similar to those employed to show that OF implies VF:

Define a proper subset of timing failures in which  $t_j = \infty$  as:

$TF_{null}: \{ v = w \text{ and } t_j = \infty \}.$

By definition,  $TF_{null}$  implies TF and also implies OF. For all practical purposes, producing the correct value at time  $\infty$  has the same meaning as producing any value at time  $\infty$ . Therefore  $TF_{null}$  in which the expected value is produced at time  $\infty$  can be considered to be equivalent to  $\{v \neq NULL \text{ and } t_j = \infty\}$  and to represent OF itself; thus, OF implies TF in practice.

Thus, omission faults (failures) can be treated as a special case of, and hence a proper subset of, emission, value, and timing faults (failures). From their definitions, value and timing faults (failures) can be seen to form a proper subset of emission faults (failures).

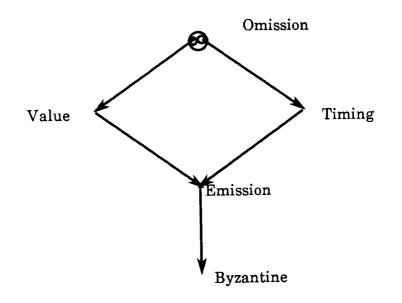

The relationship among these five types of faults (failures) can be expressed by the ordering diagram shown in figure 2.1, where an arrow from A to B,  $A \rightarrow B$ , indicates that fault (failure) of type A is a special case of, or a proper subset of, fault (failure) of type B and therefore fault assumptions of type B are less restrictive than those of type A. In the figure, the two circles in omission type represent  $VF_{null}$  and  $TF_{null}$  which, by definition, form proper subsets of omission type and, in practice, become omission type itself. Note that the ordering relation  $\rightarrow$  is transitive. From the ordering diagram, it can be stated that an algorithm designed to tolerate f, f > 0, value (or timing) failures can also tolerate f omission failures; similarly an algorithm designed tolerate f emission failures can also tolerate f failures of either omission, value, or timing failures, and finally an algorithm designed to tolerate f Byzantine failures can tolerate f failures of any type.

Figure 2.1. Fault/Failure Ordering Diagram.

### Remarks

#### 1. Output Sequences

The above classification is based on the behaviour of a component with respect to a single input. When a sequence of inputs over a given time interval is considered, the type of fault suffered by a faulty component will be the most restrictive (or the least serious) one (as per the ordering diagram in figure 2.1) of which all types of failures occurred during the interval can be considered to be special cases. For example, if, over a given time interval, value and timing failures have occurred, then the component will be said to have suffered emission failures during that interval; if value and omission are the types of failures, then the component will have suffered value failures. If a given type of faulty behaviour persists for a "sufficiently lengthy" sequence of inputs, then the failures can be classified as a permanent failure of that type. A permanent omission fault causes the component to halt functioning for ever. In the literature, it is called a *crash* failure or a *fail-silent* failure [Powel88].

#### 2. Outputs with no timing requirements

There may be situations where a component's responses do not need to follow the rigid timing requirements specified here. Under these circumstances, a timing failure cannot be defined and the component can only suffer three types of failures, namely, omission, value, and Byzantine.

#### 2.2.3. Selfchecking Components

The fault/failure classification can be applied to understand and specify the behaviour of components with builtin redundancy (for selfchecking) where the redundancy is employed to minimise the likelihood of the occurrences of failures of certain types. For example, consider a component with value checks; for valid inputs, such a component is designed to produce either "normal values" or "value exceptions" - the expected values when failures within the component occur for which a degree of tolerance has been provided. A component with dual processors and a comparator that compares the output values of both the processors and outputs a value exception whenever a disagreement is detected can be such a component. It can suffer only timing failures, provided the comparator is non-faulty and no more than one processor fails; given these fault assumptions for the comparator and processors, the overall behaviour of this selfchecking component is CR or TF:

(expected - value and ontime) or (expected - value and not ontime), where the expected - value is given by:

normal-value or value-exception.

That is, such a component produces the normal value or a value exception either on time or not on time. Another example of a selfchecking component will be a processor with a 'watch-dog' timer that is used to prevent timing failures by signalling a 'timing-exception' whenever the processor is deemed not capable of producing its output on time. Thus the expected behaviour of such a processor in the value domain includes generating a response indicating a timing exception. The watch-dog timer cannot, however, detect the processor's value and Byzantine failures. Given that the processor does not suffer Byzantine failures and the watch-dog timer is nonfaulty, the overall behaviour of such a processor will be *CR* or *VF*:

(expected - value and ontime) or ( not expected - value and ontime), where the expected - value is given by:

normal-value or timing-exception.

That is, such a selfchecking processor produces timely responses which could be wrong in the value domain. If a processor has been constructed with both value and timing checks, then this means that its expected behaviour in the value domain is extended to include the production of value and timing exceptions (or simply failure exceptions). A fail-stop processor [Schli83] is an example of a component proposed with value and timing checks and to raise a failure exception, in case the possibility for producing an incorrect response is detected. It is also designed to stop responding for ever to input requests after having raised a failure exception.

#### 2.2.4. Selecting Fault Models for Components

In the fault classification presented here, a Byzantine fault has been defined to be a fault which can cause the component to fail in any manner. Choosing the Byzantine fault model for components will mean that no restrictive assumption need be made regarding the components' failure modes. In practice, the type of failures that a component may be assumed to suffer should be decided by considering engineering factors such as the failure data of the component (i.e. failure modes and probability of their occurrences), and application specific details such as the task load the component is designed for, safety factors, and the consequences of the component failing in a manner other than what was assumed. If the failure data are not available or if it is judged that it is not safe to predict the failure modes given the criticality of the application at hand, it will be appropriate to expect the component to fail in Byzantine manner; otherwise, faults of appropriate non-Byzantine class can be chosen to model the component's faulty behaviour. A choice of value, timing, or emission faults can be refined, if necessary, with a set of additional assumptions to precisely model the faults of a component. For example, it is common, in a value fault model, to restrict the failure modes by assuming that corruption of a message by a communication link are limited such that mechanisms such as checksums can be utilised for error detection. In [Veris89], value failures of processors and communication links which result in detectable message corruption are classified as *syntactic* failures.

#### 2.3. Replicated Responses

In this section the fault classification is extended to a particularly important type of systems where components are required to produce replicated responses for a given input. For example, in triple modular redundant systems, a processor is required to send its output to three other processors; similarly, when processors (considered as components in a distributed system) are taking part in some agreement protocol, every processor is required to send its output to every other processor in the system.

Consider a component that is required to produce a replicated response containing r individual outputs, where  $r, r \ge 1$ , is the specified replication level, as a result of receiving an input at time  $t_i$ . We will use the following vector notation to specify the replicated response:

$V = \{v_1, v_2, \cdots, v_r\}$ , where  $v_k$  is the value of the kth,  $1 \le k \le r$ , individual output.

$T_j = \{t_j 1, t_j 2, \cdots, t_j r\}$ , where  $t_j k$  is the time at which the kth individual output appeared.

#### **Definition: Correct Replicated Response**

Let a component receive at time  $t_i$  an input requiring a replicated response. For that input, the replicated response with value V at time  $T_j$  is correct iff:

(i) the output value is correct: V = W, where W is the vector of expected output values; and

(ii) the output timing is correct:  $t_i + t_{\min} \le t_j k \le t_i + t_{\max}$ , for all  $t_j k$ ,  $1 \le k \le r$ , in  $T_j$ , where  $t_{\min}$ ,  $t_{\max}$  are as defined in the definition for correct unreplicated responses in section 2.2.

Note that, by definition, W has the property that  $w_P = w_k = w$ , for all  $p,k, 1 \le p,k \le r$ .

### **Remark:** The skew interval

In a correct replicated output, all individual outputs are produced with the correct, hence identical, values and on time but not necessarily at 'the same time'; thus, for any two of the r individual outputs:

$0 \leq |t_j p - t_j k| \leq t_{\max} - t_{\min}, \text{ for all } p, k, 1 \leq p, k \leq r.$

The interval 0...S, where  $S = t_{max} - t_{min}$ , will be called the *skew inter*val within which all individual outputs are expected to be produced.

#### **Definition: Incorrect Replicated Response**

An incorrect replicated response is defined first by defining failures in value and time domains:

The output value V will be termed incorrect, if  $V \neq W$ , i.e. there exists some p,  $1 \le p \le r$ , such that  $v_P \ne w$ .

The response time  $T_j$  will be termed incorrect, if there exists some p,  $1 \le p \le r$ , such that:

$t_{jp} < t_i + t_{\min}$  (response too early), or

$t_{ip} > t_i + t_{max}$  (response too late).

A replicated response will be said to be incorrect, if either V or  $T_j$  or both are incorrect.

## **Definition:** Consistently Incorrect Replicated Responses

For replicated responses, it is possible to consider a restricted violation of the specification by considering the notion of *consistent incorrectness* among individual responses of an incorrect replicated response:

In a replicated response, the output value V is said to be consistently incorrect, if,

- (i) V is incorrect, and

- (ii) for all  $p,k, 1 \le p,k \le r$ , vp = vk

That is, all individual output values are *identically* incorrect. Similarly, the response time  $T_j$  of a replicated response is said to be *consistently incorrect*, if

- (i)  $T_j$  is incorrect, and

- (ii) for all  $p,k, 1 \leq p,k \leq r$ ,  $|t_jp t_jk| \leq S$ .

That is, while the response is not produced on time, all of the individual responses are produced within the skew interval. A replicated response is said to be *consistently incorrect*, if:

- (i) V is consistently incorrect and  $T_j$  is correct, or

- (ii) V is correct and  $T_j$  is consistently incorrect, or

- (iii) both V and  $T_j$  are consistently incorrect.

## 2.3.1. Fault/Failure Classification

A given replicated response being consistently incorrect in the value domain or in the time domain or in both the domains is a special case of it being incorrect respectively in the value domain or in the time domain or in both the domains. As our fault classification is based on the input-output behaviour of a component, the definition of consistently incorrect responses will give rise to a set of fault types that were not defined for components with unreplicated responses. With the definitions of correct, consistently incorrect, and incorrect responses, the following nine classes of faults will be identified for components with replicated responses.

## **Consistent** Omission Fault/Failure

Faults of this type cause a component to fail by not responding to a given input and, consequently, by not producing a response when a replicated response is expected. The corresponding failure will be termed a *consistent omission* failure. A processor that has stopped functioning, a processor that occasionally fails to broadcast a message are examples of components with consistent omission faults.

## **Consistent Value Fault/Failure**

A consistent value fault causes a component to respond to a given input by producing a replicated output on time but with identically incorrect values. That is, in a consistent value failure, V is consistently incorrect and  $T_j$  is correct. A processor broadcasting an incorrectly computed value is an example of a consistent value failure.

# Consistent Timing Fault/Failure

A consistent timing fault causes a consistent timing failure in which V is correct and  $T_j$  is consistently incorrect. This fault type causes a component to produce correct values either too early or too late, but within the

specified skew interval. A processor with too many computational tasks can suffer a consistent timing failure, when it produces a replicated output with correct values during the interval  $[t+\delta, t+\delta+S]$  instead of [t, t+S], where  $\delta$ is the excess delay due to processor overloading.

A consistent timing failure in which outputs are produced late (early) will be called a consistently late timing failure (a consistently early timing failure).

#### **Consistent Emission Fault/Failure**

A consistent emission fault causes a component to produce a consistently incorrect response for a given input. In a consistent emission failure, V and/or  $T_j$  will be consistently incorrect. An overloaded processor that broadcasts erroneously computed values suffers a consistent emission failure.

### **Omission Fault/Failure**

An omission fault causes an omission failure in which none or some of the individual outputs of a replicated response are not produced. A processor that occasionally stops functioning while outputting the individual outputs of a replicated response is an example of a component suffering an omission failure. An omission fault can cause a consistent omission failure and hence is more general than a consistent omission fault.

# Value Fault/Failure

A value fault causes a component to respond with incorrect values on time. In a value failure, V is incorrect and  $T_j$  is correct and but any two individual outputs of a replicated output need not be identical. For an example of value failure, consider a processor broadcasting a message to a group of processors to which it is connected by point to point links. A broadcast will then consist of sequentially transmitting a copy of the message held in a buffer to each member of the group. Such a processor can suffer a value fault if the buffer gets corrupted during a broadcast. Value failures (faults) subsume consistent value failures (faults).

#### **Timing Fault/Failure**

A timing fault causes a component to respond with correct output value at incorrect time. In a timing failure, V is correct and  $T_j$  is incorrect, and any two individual outputs need not appear within the skew interval.

In the previous example of a value failure, instead of buffer corruption, if the processor slows down (due to overloading), then the individual outputs may not be produced within the skew interval. Timing failures (faults) subsume consistent timing failures (faults).

# **Emission Fault/Failure**

An emission fault causes a component to produce an incorrect response for a given input. Both value and timing failures are special cases of an emission failure.

#### Byzantine (or General) Fault/Failure

A Byzantine fault, as in the case of unreplicated responses, is defined to be the most general fault that can cause the component to deviate from the specified input-output behaviour in any manner; the corresponding failure is defined to be a Byzantine failure which will include the component producing arbitrary responses when no input was supplied and producing responses with 'malicious' intentions. The behaviour of a "traitorous general" in the Byzantine generals problem of [Lampo82] is a classic example of how a processor with Byzantine faults can be malicious in its responses to other (faulty or non-faulty) processors in a distributed system.

# 2.3.2. Fault/Failure Ordering

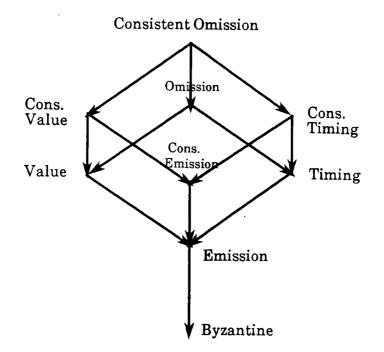

When a consistent omission failure is interpreted as a failure of producing null output values (identically incorrect values) at any time after the input was supplied, or as a failure of producing identically correct or incorrect output values at time  $\infty$ , it can be seen to form a special case of failures of every other consistent type. By their definitions, consistent omission, consistent value, consistent timing, and consistent emission types of faults/failures are respectively special cases of omission, value, timing, and emission types of faults/failures. The ordering diagram shown in figure 2.2 indicates the 'special case' relationship between various classes of faults and failures. As in figure 2.1, an arrow from A to B,  $A \rightarrow B$ , in figure 2.2 indicates that faults/failures of type A are a special case of faults/failures of type B, and the ordering relation  $\rightarrow$  is transitive.

Figure 2.2. Fault/Failure Ordering Diagram For Replicated Responses.

# **Remark: Output Sequences**

As in the case of components with unreplicated responses, the above classification is based on the behaviour of a component with respect to a single input; and, when a sequence of replicated responses over a given time interval is considered, the type of failure suffered by a faulty component will be the most restrictive one (as per the ordering diagram in figure 2.2) of which all types of failures occurred during the interval can be considered to be special cases. Note that an unreplicated response becomes a special case of a replicated response, when r, the degree of replication, is taken to be 1. When r becomes 1, a component's omission, value, timing, and emission failures can be respectively regarded as: consistent omission, consistent value, consistent timing, and consistent emission failures. Thus, a sequence of replicated and unreplicated responses over a given time interval can also be treated as a sequence of replicated responses and, thereby, the type of fault suffered by the component during that interval can be determined from the ordering diagram in figure 2.2. For example, if, over a given time interval, value and timing failures have occurred for unreplicated responses and consistent timing failures for replicated responses, the component will be said to have a consistent emission fault during that interval; if value and (consistent) omission are the types of failures respectively for unreplicated and replicated responses, then the component will have a (consistent) value fault; if Byzantine and consistent omission failures occur while producing respectively unreplicated and replicated responses, the component becomes Byzantine faulty.

#### 2.4. Composite Components

Following the classification of faults and failures of a single individual component, the behaviour of composite components made up of potentially faulty components is investigated. To start with, the behaviour of a processor is studied by considering a digital clock as one of its components. The study is then extended to a distributed system which is considered to be made up of processors and communication links.

# 2.4.1. Processor with a Clock

A processor, P, will be considered to be made up of two components: (i) computational and communication unit, CCU, that processes computational tasks and handles communication with the environment, and (ii) a digital clock, CL, that measures the passage of real time and provides the current

time. CCU can use CL to read the current time or to measure time intervals. For some specified  $\rho$ ,  $0 < \rho << 1$ , a correct clock measures the passage of one time unit when a real time period between  $(1 - \rho)$  and  $(1 + \rho)$  has elapsed [Ellin73]. It is natural to model a digital clock as an *autonomous* component - a component that produces outputs (display of current time) not by receiving input requests but simply in response to the passage of real time. One such model is developed here. It is nevertheless possible to model a digital clock as a demand driven "time server" device that outputs current time only for an input request.

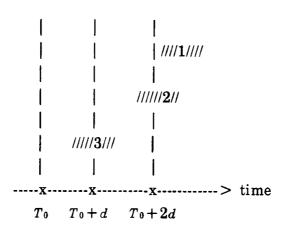

## 2.4.1.1. Types of Clock Faults

A clock's display of current time will be its response produced at every given timing instant. Such a sequence of responses will start from  $T_0$ reflecting the time  $t_0$  when the clock started functioning. Thus, a digital clock is an autonomous component which, once turned on, is expected to produce an infinitely long sequence of responses of monotonically nondecreasing values such that the output value of every response (i.e. the value displayed) at any given timing instant will indicate the clock's measurement of the passage of real time from  $t_0$  to that timing instant. If T is the value displayed at real time  $t, t \ge t_0$ , then the response will be said to be correct iff:

CR1 (measurement of time):

$T_0 + (t - t_0)/(1 + \rho) \le T \le T_0 + (t - t_0)/(1 - \rho)$  and,

CR2 (monotonic display):

$T \ge T^-$ , where  $T^-$  is the display value at  $t^-$ ,  $t^- = t - \Delta t$ , as  $\Delta t \to 0$ .

While condition CR1 states the correctness requirement for the measurement of the passage of real time, condition CR2 ensures that values displayed are monotonically non-decreasing. For example, a clock that showed  $T_1$  and  $T_2$  respectively at t- and t such that

$T_0 + (t - t_0)/(1 + \rho) \le T_2 < T_1 \le T_0 + (t - t_0)/(1 - \rho)$  can satisfy CR1, due to non-zero  $\rho$ , but will not satisfy CR2.

It can be seen from CR1 that the correctness of an output value (T) and the instant of time the output value is produced (t) are interdependent and, hence, value and timing failures cannot occur independently of each other; in other words, an occurrence of a value failure will imply that of a timing failure and *vice versa*. Thus, according to our fault/failure classification, CL can have the following three types of faults/failures: omission, emission, and Byzantine.

A clock that occasionally fails to display the current time will be said to have an omission fault and a clock that fails to display the current time for a "sufficiently long time" will be said to have a permanent omission failure. An emission failure is the clock producing an incorrect response, i.e., **not** (CR1 and CR2). A Byzantine faulty clock can fail in any manner and no assumption can be considered on its failure modes. For a clock, there is little difference between an emission fault and a Byzantine fault. A proper subset of emission failures can be identified by considering emission failures in which only CR1 is violated, i.e. (**not** CR1 **and** CR2). Such failures will be referred to as *monotonic emission failures*. For example, a fast or slow clock or a clock that stops by displaying the same value (running infinitely slow) are examples of clocks with monotonic emission faults. In the following analysis of *P*'s behaviour, *CL* is considered to have omission, monotonic emission, and Byzantine types of faults/failures.

#### 2.4.1.2. Types of Processor Faults

The faulty behaviour of a processor (P) with a clock, can be studied in terms of the types of faults in its components CCU and CL. Suppose that CCU is non-faulty and CL is faulty. An omission faulty CL will make P to suffer at most omission failures (P's computational results that do not involve the use of CL will be correct and be produced on time). Suppose that CL has a monotonic emission fault. When CCU uses the CL's display as a value in its computation (e.g. to generate a sequence number), P can suffer a value failure. If CL is used by CCU to set timeouts, then a fast or slow clock can result in P's timing failure. Thus a monotonic emission faulty CL can make P emission faulty. A Byzantine failure in CL may result in a Byzantine failure in P. When CCU is faulty and CL is non-faulty, P will suffer the types of faults in CCU. An interesting observation is that when CL becomes unduly faster or slower, P can suffer an emission failure - quite a serious type of failure - even when CCU is non-faulty.

When both CCU and CL are faulty, it is possible for the failures of one component to mask or nullify that of the other component. For example, a permanent omission failure in CCU will make P also to suffer that type of failure, irrespective of the types of faults in CL; similarly, fast computation by CCU and a slow CL may nullify failures of each component resulting in P producing a timely response. However, the possibilities of components' failures nullifying each other cannot be relied upon to happen all the time and, therefore, P should be considered to be faulty for all practical purposes. Thus, except in the case of the CCU having a permanent omission fault, the types of faults in P will be the least serious one which, according to the ordering diagram in figure 2.1, subsumes the types of faults in CCU and CL, given that every fault type is considered to subsume itself and that monotonic emission fault of CL is taken to be equivalent to, and represented as, emission fault in figure 2.1. For example, when both CCU and CL have omission faults, P will suffer failures of omission type; if CCU has timing faults and CL monotonic emission faults, failures of P will be of emission type.

# 2.4.2. Processor Interconnections

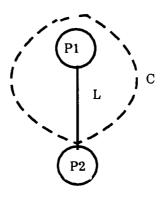

#### 2.4.2.1. Processors with unreplicated responses

Consider first the behaviour of a component C composed of a processor P1 and a link L that connects P1 to a second processor P2 (see figure 2.3). The function of L is merely to transmit the outputs of P1 to P2.

Figure 2.3. A Three Component System.

When one component in C is faulty the other one is non-faulty, C will suffer the type of faults suffered by its faulty component. Suppose that both P1 and L are faulty. A permanent omission failure in L will cause C also to have a permanent omission failure, irrespective of the type of fault in P1. If it can be assumed that faulty L cannot generate messages on its own accord, then a permanent omission failure in P1 will also mean that C as a whole has a fault of that type. Excepting the above two cases, the fault type of C will be the least serious type which, according to the ordering diagram in figure 2.1, will subsume the types of faults suffered by P1 and by L.

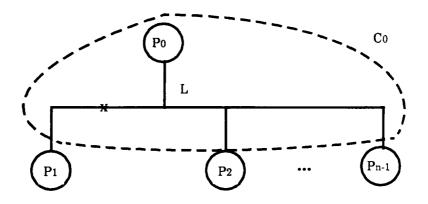

#### 2.4.2.2. Composite component with replicated responses

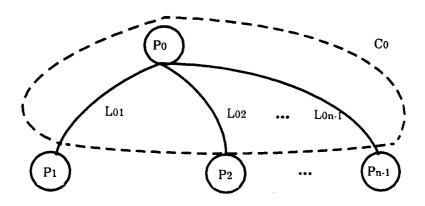

To analyse the faulty behaviour of a processor-link component producing replicated responses, consider a distributed system made up of n processors,  $P_0$ ,  $P_1$ ,  $\cdots$ ,  $P_{n-1}$ , capable of exchanging messages using a communication medium L. Suppose that a composite component  $C_0$  is made up of processor  $P_0$  and L. Let L, as shown in figure 2.4, be a bus capable of providing a broadcast service.

Figure 2.4. Components With Replicated Responses.

Suppose that  $P_0$  is faulty and L is non-faulty; then  $C_0$  will suffer the same fault as in  $P_0$ . Similarly, if  $P_0$  is non-faulty and L is faulty, then the type of fault in L will be the fault type of  $C_0$ . Since  $P_0$  is not responsible for replicating its outputs, its fault types can only be consistent or Byzantine;

but those of L can vary from consistent omission to Byzantine. A fault in L can cause the failures of L not to be consistent. If, for example, there is a break at the place (x) shown in the figure, L may fail by delivering  $P_0$ 's output to all processors other than  $P_1$ . When both  $P_0$  and L are faulty, the fault type of  $C_0$  can be determined as discussed in the previous subsection.

It is interesting to observe that if L is assumed to be reliable and if  $P_0$  is faulty, then  $C_0$  can fail only in consistent or Byzantine manner. Suppose the functionality of L is further enhanced such that processors receiving a message can authenticate the identity of the sender of the message, then faulty  $P_0$  cannot masquerade as any other processor. The DELTA-4 distributed system[Powel88] is such a system where the communication subsystem has been designed to be reliable and with the authentication facility thereby considerably reducing the probability of masquerading Byzantine failures occurring in the system. Instead of making L reliable, if  $P_0$  is made reliable, then the overall faulty behaviour of  $C_0$  can still encompass all possible failure modes.

Suppose that processors in a distributed system are connected by links such that there exists a communication path between any two processors in the system. The communication paths will be made up of links and, if necessary, processors which will be expected to relay messages according to some routing algorithm.

Figure 2.5. Components With Replicated Responses.

In figure 2.5,  $L_{0i}$  represents the logical communication path between  $P_0$ and  $P_i$ ,  $i \le i \le n-1$ . If any  $L_{0i}$  is faulty, then the fault type will be determined by the type of faults in processors and in links that make up  $L_{0i}$  and the fault analysis of  $L_{0i}$  will be similar to that discussed for the unreplicated case. Suppose that the composite component  $C_0$  is made up of  $P_0$  and communication paths,  $L_{01}, L_{02}, ..., L_{0(n-1)}$ , incident on  $P_0$ , and  $P_0$  produces replicated output by sending a copy of the message through each communication path. Then the fault types of  $P_0$  can vary from consistent omission to Byzantine. As before (discounting permanent omission failures in all  $L_{0i}$ 's), the fault type of  $C_0$  will be the least serious one which, according to the ordering diagram in figure 2.2, will subsume the type of faults in all faulty components of  $C_0$ . For example, if  $P_0$  has consistent value faults and some  $L_{0i}$  is faulty with omission (emission) faults, then  $C_0$  will be considered to have value (emission) faults.

A similar fault analysis can be performed for composite components  $C_1, C_2, ..., C_{(n-1)}$  constructed respectively with  $P_1, P_2, ..., P_{(n-1)}$  and

communication paths incident on them. Such a fault analysis of composite components in terms of constituent components can provide useful insights on the faulty behaviour of the composite components. Given the nature of processor interconnections and the type of faults that might be suffered by processors and communication links or bus, the behaviour of one processor with respect to other processors can be analysed.

This section has illustrated how the fault classification scheme presented here can be applied to develop accurate fault models of composite components. Precise specifications of component faults can be exploited to develop efficient fault tolerant algorithms as illustrated in the next two chapters.

# 2.5. Concluding Remarks

Using 'timeliness' and 'expected value' as the specified properties of a component's response, we have presented five types of faults for components with unreplicated responses and extended the classification to nine types of faults for components with replicated responses. These classifications together with the fault lattices presented represent one of the main contributions of this chapter. We have also discussed how faulty behaviour of a component can be determined, given the fault types of its constituent components. This was illustrated by constructing fault models of clocks and processors in a distributed system. Our fault classification provides a very convenient means not only for specifying the faulty behaviour of components but also for the construction of increasingly more sophisticated fault tolerant algorithms tolerating faults of increasingly more complex types. This will be demonstrated by the fault tolerant agreement algorithms presented in the following two chapters.

# CHAPTER 3

# FAMILY OF AGREEMENT ALGORITHMS

#### 3.1. Introduction

Reaching agreement in the presence of faults is a fundamental problem in fault tolerant distributed computing. The agreement problem originally formulated as the interactive consistency problem [Pease80] and later as the Byzantine Agreement problem [Lampo82] can be described as follows: A distributed system is made up of n, n > 2, processors capable of communicating with each other only by message passing. Among these n processors in the system, one processor is designated as the sender and the other processors as receiver processors. The sender wants to disseminate some value to all receiver processors. The difficulty is that some processors, possibly including the sender, may be faulty and that a non-faulty processor cannot ascertain which other processors are faulty. When the sender is faulty, it cannot be guaranteed that all non-faulty receiver processors receive the same value directly from the sender. Thus it is necessary to develop an agreement algorithm that can be executed by receiver processors to guarantee that the following conditions will be met in the presence of at most f, f< n-1, faulty processors:

C1 all non-faulty receiver processors decide on the same value, and

C2 when the sender is non-faulty, all non-faulty receiver processors decide

- 42 -

on the value sent.

By C1, it is ensured that all non-faulty receiver processors reach a *unanimous* decision on a value; by C2, it is guaranteed that if the sender is non-faulty, then every non-faulty receiver processor reaches a *valid* decision by deciding on the value sent by the sender. When C1 and C2 are met, the agreement will be said to have been reached (on the sender's value) by non-faulty receiver processors. When the sender is non-faulty, C2 implies C1.