# ACTION-REPLAY : A REAL-TIME DEBUGGING TECHNIQUE

Nikos G.K. Kanellopoulos

| NEWCASTLE UPON TYNE<br>UNIVERSITY LIBRARY<br>ACCESSION No. |    |

|------------------------------------------------------------|----|

| 81-14239                                                   | NR |

| LOCATION<br>Thesis<br>L2521                                |    |

A thesis submitted for the degree of Doctor of Philosophy in Computing Science at the University of Newcastle-upon-Tyne. December, 1981.

To my family and friends.

## ACKNOWLEDGEMENTS

The author acknowledges the advice and encouragement of Mr. N. Ghani, Mr. J.G. Givens, Mr. K. Heron and Dr. C.R. Snow.

Thanks are also given to Ageliki, Athena, Gregory, Helen, Marcia, Maria, Toula and Vasiliki for their continued support expressed materially and spiritually throughout this Ph.D. study.

# **ABSTRACT**

Currently available microcomputer development systems/tools become rather inefficient when employed to debug real-time malfunctions; that is, intermittent or even unrepeatable hardware/software malfunctions encountered in time-critical applications. A new debugging technique, namely the Action-replay Debugging Technique, is proposed which can efficiently deal with a large class of these malfunctions.

The aim of the Action-replay Debugging Technique is to provide an environment which is suitable for real-time debugging. In particular, an identical processor to the target, or a simulator of it, is forced to re-execute, or **Action-replay**, repeatedly and at any desirable speed the exact program path which the target processor traversed during the original interaction with its real-time environment. During successive "Action-replays" the user can investigate the system's behaviour (including timing characteristics) without real-time constraints which normally exist in time-critical applications.

# ABBREVIATIONS

| CPU  | :  | central processor unit.      |

|------|----|------------------------------|

| DMA  | :  | direct memory access.        |

| DSL  | :  | digital systems laboratory.  |

| ECL  | :  | emitter coupled logic.       |

| LED  | :  | light emitting diode.        |

| LSI  | :  | large scale integration.     |

| MMU  | :  | memory management unit.      |

| MPU  | :  | micro-processor unit.        |

| MSB  | :  | most significant bit.        |

| MSI  | :  | medium scale integration.    |

| MTS  | :  | Michigan terminal system.    |

| PTR  | :  | paper tape reader.           |

| RAM  | :  | random access memory.        |

| ROM  | :  | read only memory.            |

| SSI  | :  | small scale integration.     |

| TTL  | :  | transistor-transistor logic. |

| VDU  | :  | video display unit.          |

| [n]  | :  | reference number.            |

| (# n | ): | section number.              |

| (An  | ): | appendix number.             |

# SUMMARY

The development of microcomputer based real-time systems, being a complex process involving simultaneous design of both hardware and software, demands sophisticated debugging tools. However, a study undertaken at the start of this research work has revealed that currently available microcomputer development systems/tools cannot efficiently debug real-time malfunctions.

An analysis of the debugging process follows in order to reveal the differences between conventional and real-time debugging and with emphasis on the debugging tool capabilities, the availability of which should make efficient real-time debugging possible. In particular, real-time debugging presents two basic problems, namely **Execution Unrepeatability** and **Transparent Accessing of Program Status Information.** If efficient real-time debugging is to be achieved, the debugging system must be able to deal with these two problems.

Thereafter, a debugging system is proposed based on a new debugging technique, namely the Action-replay Debugging Technique. This technique allows real-time debugging to take place within a non-real-time environment, thus providing a "transparent" solution to the above mentioned In particular, a snapshot of the target system problems. state is saved together with a complete record of all external stimuli as seen by the target CPU during the real-time execution which follows. At the end of the program execution "Action-replay" may commence. That is, having reset the target system state to that given in the above mentioned snapshot, an exact reconstruction of the captured external stimuli is initiated which forces the target processor, or a simulator of it, to re-execute an identical program path with that which the target processor traversed during the original interaction with its real-time environment. successive "Action-During

replays" of the suspect program path the user can investigate the program's behaviour without real-time constraints which normally exist in time-critical applications.

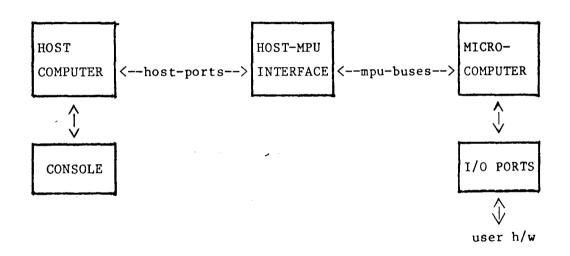

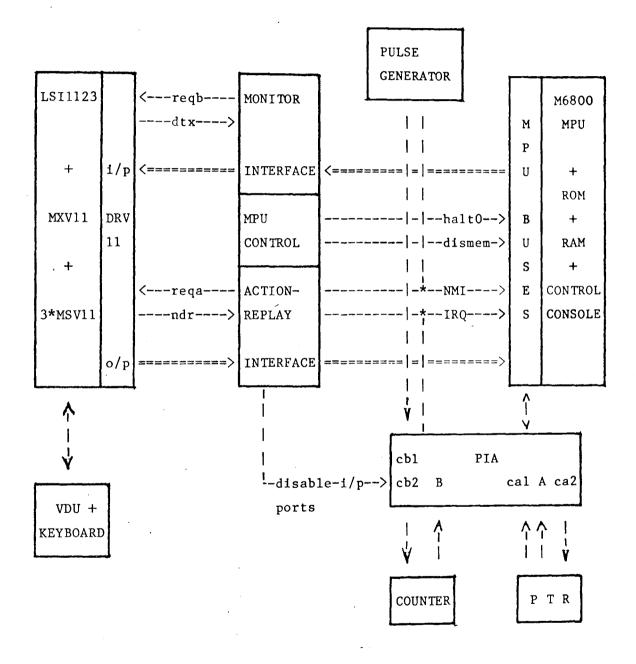

Having defined the most important aspects of the Actionreplay Debugging Technique, an Action-replay Prototype System is then developed, based on the "semi-resident approach"; that is, a host computer is connected to the target computer via an intelligent interface, namely the Host-MPU Interface. The target and host computers are the M6800 microcomputer and the LSI11/23 minicomputer respectively. The Host-MPU Interface complexity is kept at minimum levels, but even so it is necessary to employ more than 150 SSI/MSI TTL integrated circuits in the design.

Thereafter, three case studies are undertaken in an attempt to evaluate the Action-replay Debugging Tech-These studies show that the Action-replay Debugnique. ging Technique can indeed aid real-time debugging of software (as well as hardware) malfunctions by providing a debugging environment which encourages the user to embark into a systematic and efficient debugging process; debugging the same malfunctions via conventional debugging methods would require a vast amount of trace memory for providing less efficient diagnostic facilities. In particular, the erroneous program behaviour can be kept in a stable condition so that particular symptoms relating to particular faults can be focussed upon and analysed; that is, the user is not confused by rapidly changing symptoms.

Finally, the Action-replay Debugging Technique limitations are discussed and recommendations are given for overcoming these limitations and for upgrading the Action-replay Debugging Process in future implementations.

# TABLE OF CONTENTS

| 1. INTRODUCTION                                  | 1 |

|--------------------------------------------------|---|

| 1.1. Program Development                         | 2 |

| 1.1.1. Program Design                            | 3 |

| 1.1.2. Program Validation                        | 4 |

| 1.1.3. Program Debugging                         | 6 |

| 1.1.4. Program Performance Evaluation            | 8 |

| 1.2. Microcomputer Development Tools             | 8 |

| 1.2.1. Hardware Consoles 10                      | 0 |

| 1.2.2. Software Consoles 10                      | 0 |

| 1.3. Research Direction 10                       | 6 |

| 2. REAL-TIME DEBUGGING PROCESS 13                | 8 |

| 2.1. Debugging Process Analysis 18               | 8 |

| 2.1.1. Conventional Computer System Debugging 18 | 8 |

| 2.1.2. Real-time Computer System Debugging 20    | 0 |

| 2.2. Real-time Debugging Tool Capabilities 22    | 2 |

| <b>2.3.</b> Summary                              | 4 |

| 3.  | ACT  | ION-REPLAY DEBUGGING TECHNIQUE                      | 25         |

|-----|------|-----------------------------------------------------|------------|

| 3   | .1.  | External Stimuli Real-time Monitoring               | 27         |

|     | 3.1  | 1. Input Port Data Monitoring                       | 28         |

|     | 3.1  | .2. Interrupt Monitoring                            | 2 <b>9</b> |

|     | 3.1  | .3. DMA Input Data Monitoring                       | 33         |

| 3   | .2.  | Program Path Action-replay                          | 34         |

|     | 3.2  | 1. Hardware Simulator Approach                      | 34         |

|     | 3.2  | 2. Software Simulator Approach                      | 35         |

| 3   | .3.  | Action-replay Verification                          | 36         |

| 3   | .4.  | Program Status Information Non-real-time Monitoring | 36         |

|     | 3.4. | 1. Monitoring Conditions Evaluation 3               | 37         |

| 3.4 | .2.  | Program Status Information Formating and Displaying | 37         |

| 3   | .5.  | Correction Verification                             | 38         |

| 3   | .6.  | Summary                                             | 38         |

| 4.  | ACT  | ON-REPLAY DEBUGGING SYSTEM                          | 40         |

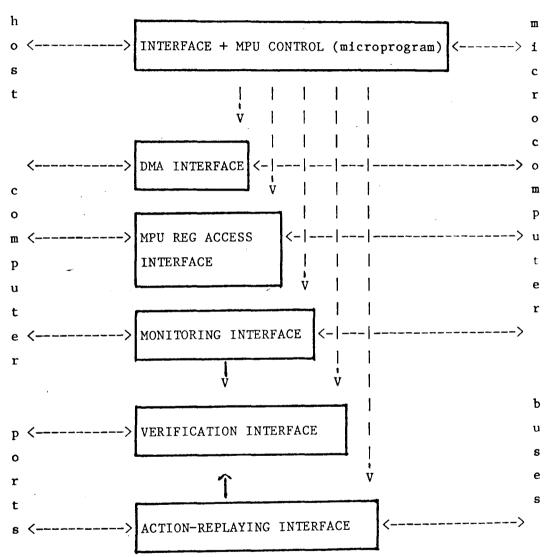

| 4   | .1.  | System Functions                                    | 40         |

| 4   | .2.  | System Organisation                                 | 40         |

| 4   | .3.  | Monitoring Interface                                | 43         |

| 4.4.    | Action-replaying Interface                 | 44 |

|---------|--------------------------------------------|----|

| 4.5.    | Verification Interface                     | 45 |

| 4.6.    | Summary                                    | 46 |

| 5. ACT. | ION-REPLAY SYSTEM IMPLEMENTATION           | 47 |

| 5.1.    | Assumptions                                | 47 |

| 5.2.    | Target Computer System                     | 48 |

| 5.2     | .1. Target Computer System Hardware        | 49 |

| 5.2     | .2. Target Computer System Software        | 49 |

| 5.3.    | Host Computer System                       | 51 |

| 5.3     | .1. Host Computer System Hardware          | 51 |

| 5.3     | .2. Host Computer System Software          | 52 |

| 5.3     | .3. Trace Memory Organisation              | 53 |

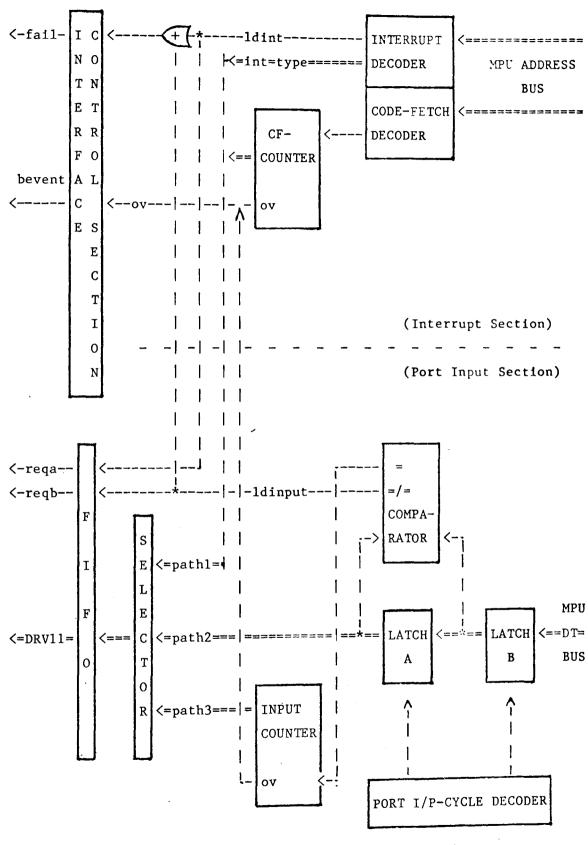

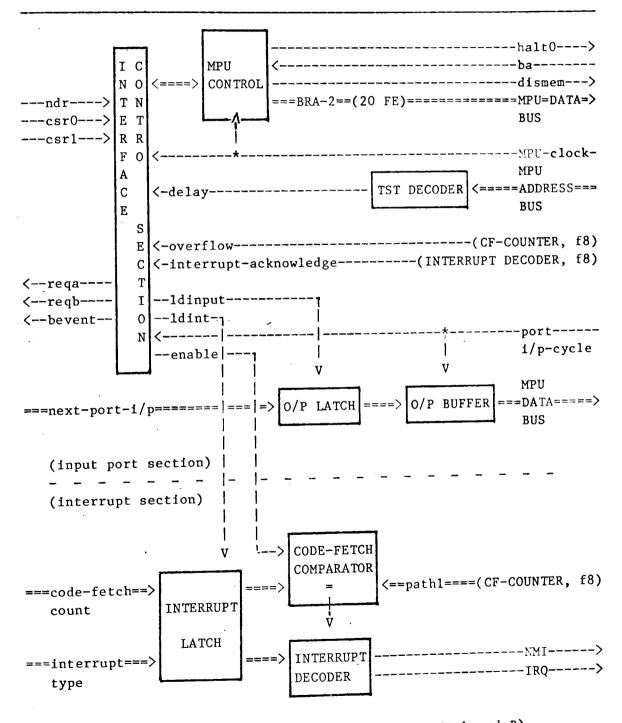

| 5.4.    | LSI11/23-M6800 Interface Implementation    | 55 |

| 5.4     | .1. Monitoring Interface Implementation    | 55 |

| 5.4     | .2. Action-replay Interface Implementation | 57 |

| 5.4     | .3. Action-replay Interface Operation      | 61 |

| 5.5.    | Performance Evaluation                     | 62 |

| 5.5     | .1. Experiment A                           | 63 |

| 5.5     | .2. Experiment B                           | 65 |

| 5.6.    | M6800 Action-replay System Limitations     | 67 |

| 5.7.   | Summary                                       | 68 |

|--------|-----------------------------------------------|----|

| 6. ACT | ION-REPLAY TECHNIQUE EVALUATION               | 69 |

| 6.1.   | Case Study I                                  | 70 |

| 6.2.   | Case Study II                                 | 74 |

| 6.3.   | Case Study III                                | 76 |

| 6.4.   | Action-replay Debugging Technique Limitations | 80 |

| 6.5.   | Summary                                       | 81 |

|        |                                               |    |

| 7. CON | CLUSIONS                                      | 82 |

| 7.1.   | Implementation Dependent Features             | 82 |

| 7.1    | .1. Monitoring Phase                          | 83 |

| 7.1    | .2. Action-replay Phase                       | 84 |

| 7.2.   | Alternative Implementation                    | 86 |

| 7.3.   | Action-replay Debugging Process Upgrading     | 88 |

## CHAPTER 1

#### **1 INTRODUCTION**

As we move into the LSI age of computer technology, hardware cost is decreasing rapidly as a result of employing massproduction processes and automating techniques within these processes. The selling cost of a **microprocessor unit** (MPU), which is the major product of the LSI technology, becomes almost negligible when compared to the development cost of the user system (hardware interfaces and driving software). If some kind of cost balance is to be achieved user system development time, being proportional to development cost, should be kept to a minimum level.

According to past statistical studies on hardware/software development [19], debugging represents more than 1/3 of the overall system development effort; the other 2/3 being the design and construction of the overall system. One way of reducing development cost, therefore, is to improve debugging efficiency; that is, to detect and correct in a short time the maximum number of design and construction errors.

It goes without saying that it is desirable to produce programs containing minimum errors in the first place. A lot of emphasis has been given in the past into the development of design methodologies and tools aiming towards the realisation of the above notion (section #1.1). In practice, however, not only the design process is extended further, due to the extra effort required for the necessary formalisation, but unfortunately not all errors are eliminated. Hence, the need for efficient debugging tools (# 1.2), the absence of which has forced debugging to become a rather specialised and, therefore, an expensive process requiring experienced system designers.

As will be shown in section #2.1 of this thesis, the need for efficient debugging tools becomes even more apparent within **Real-time Systems;** that is, either feedback or open-loop control systems of asynchronous characteristics where the controlling system component (the computer) is directly influenced by the response of the system component which is either under control (e.g., an autopilot computer and the airplane), or simply monitored (e.g., an alarm system).

Currently, real-time debugging is increasingly required in microcomputers which, due to their low cost, are heavily involved in real-time applications. Hence, microcomputer real-time debugging is focussed upon in this research work although a major part of the ideas presented apply to any computer system which is employed in a real-time application (\*).

Before presenting the basic organisation of a selection of currently available microcomputer debugging systems (# 1.2) a number of definitions will be stated concerning the program development process in general.

#### 1.1 Program Development

Program Development is the process of "Designing" a program (# 1.1.1), "Validating" the logical correctness of its implementation (# 1.1.2), "Debugging" it (# 1.1.3) and evaluating its "Performance" (# 1.1.4).

Either a **Top-down** or a **Bottom-up** strategy may govern the overall program development process [47,51]. During the former strategy the program main procedure (i.e., the top-most

<sup>\*</sup> Throughout this thesis a computer controlled real-time application is also referred to as either "user application" or "target application".

level) is developed first in the chosen programming language. Then, the program sub-procedures are developed which are also split up, and so on, until the entire program is developed. At each development level, "dummy" procedures substitute those program procedures which have not yet been developed. During the latter strategy the exact opposite happens.

The **Stepwise Refinement** program development strategy [49] is similar to the Top-down strategy; the basic difference being not having to work in the programming language. For example, one might use plain English statements describing the function to be performed at each level. When bottom level is reached, the algorithm is translated into programming language code.

If the program is deliberately split into well defined sections (modules), which are developed quite separately, only being brought together when they have all been found to work individually, then that is Modular Programming.

Finally, Structured Programming [8,22,32,48] is another method of program development; at each step of the development the logically decomposed into program can be distinct substructures whose correctness is manifest by the structure of the program itself. The Principle of Data Abstraction is often used in conjunction with structured programming, thus forming a powerful tool for designing programs (Explicit Data That is, data is defined by specifying the way Abstraction). it is represented on store and stating all possible operations Then, implementation details are ignored by thinking on it. solely in terms of meaningful operations performed upon the data than in terms of actual data. Data Abstraction may also be implemented within programming languages in the form of arrays, records, etc (Implicit Data Abstraction).

#### 1.1.1 Program Design

Program Design is the process of constructing a program according to application requirements.

The program design process is divided into two stages, namely

the Analysis and Synthesis stages. During the former design stage a study of the available program requirements is undertaken yielding in the generation of static specifications (implementation independe specifications) for all program modules/sub-modules. During the latter design stage conversion of program static specifications into procedural specifications (implementation dependent specifications) and thereon into programming language code takes place.

#### 1.1.2 Program Validation

Program Validation is the process of ensuring that the program performs the intended logical functions. The program validation process is divided into two stages, namely the **Verification** (or Proving) and **Testing** stages.

The former stage is a theoretical approach to program validation usually employed when the program domain is rather large and therefore testing cannot cover all possible cases. Hence, the program correctness is verified either by developing mathematical proofs (static approach) or by giving emphasis to the correct design of the program (constructive approach).

The latter stage is an empirical approach to program validation useful for checking programs with small finite number of program paths (in practice it is used to show the presence of errors rather than their absence). Hence, the program is tested for logical correctness by evaluating its response to a selected set of input data. According to whether a Top-down or a Bottom-up development strategy is employed, this input data stream consists of "real" and "symbolic" data correspondingly (except during the "system testing" stage of the Bottom-up strategy when the data has the form of "real" input).

A variety of program testing techniques are available [26] which are divided into two major categories, namely **Internal Testing**, during which the internal program structure is examined (e.g., path, branch and module testing), and **External Testing**, during which the set of input data is formed by extreme values (acceptance and confidence testing). Information of the following nature should be generated during testing [38] :

- \* scope, purpose and objectives of testing.

- \* hardware/software resources required during testing.

- \* execution order of tests.

- \* set of input data forming each test.

- \* data to be collected during each test.

- \* success criteria of a test.

- \* procedure followed if a test fails.

- \* test verification method.

**Programming Errors** may be divided into four main categories according to where along the development process they are introduced.

- 1) Requirement : failure to satisfy the application Errors requirements when generating the program requirements (including performance requirements).

- 2) Specification : failure to satisfy the program require-Errors ments when generating the static specifications.

- 3) Design Errors : failure to satisfy the static specifications when generating the procedural specifications.

- 4) Implementation : failure to satisfy the procedural Errors specifications in the implementation of the program algorithm resulting in incorrect data/control flow. Implemen-

tation errors are subdivided further into categories such as missing/extra/wrong program paths and actions within a path, which may be caused by various reasons (e.g., flowchart misinterpretation, undefined/multidefined/misspelled identifiers, improper/omitted variable initialisation, incorrect branch-tests, etc.).

# 1.1.3 Program Debugging

Program Debugging [15,16] is the process of locating and correcting programming errors sensed either during the initial program execution, or during program testing, or later on during program maintenance.

In **Top down Debugging** the main routine is debugged first and, as soon as a subroutine is coded, is debugged as part of the existing "debugged" program. Any data used has the same form as input for the final program. However, when the program is developed by a team of programmers, debugging of a particular program module may be delayed because subroutines, which communicate with this module, must be developed first.

In **Bottom-up Debugging** each program module/subroutine is debugged separately (**Module Debugging**) in artificial environment which generates input for the module in question. Only later on when all the modules are put together and debugged as a whole (System Debugging) data has the form of "real" input.

Debugging via **Inspections** [11,40] is a well organised, efficient and economical method based on team discussions taking place throughout program development. The team is formed by the Moderator (manages the team), Designer (produces the program design), Implementor (translates design into code) and Tester (tests the product). The process is described in terms of operations, namely the Overview (general discussion about program), Preparation (individual education), Inspection (find errors), Rework (fix errors), Follow-up (ensure all fixes are applied correctly).

**Code Walk-throughs** [40] are similar to Inspections but less formal (the structure of the team and the objectives for each operation differ in different places).

In debugging via **Desk Executions** [31] the program statements are simulated manually one by one while the current value of each variable is recorded on paper (one column for each variable). When **On-line/Interactive Debugging** is employed program status information is monitored either in between, or during program execution sessions.

**Breakpoints** stop program execution for subsequent **Program Status Information** monitoring. In there simplest form are that of **Address Breakpoints;** the address of the current instruction is compared either by software or hardware with a set of preselected addresses (located in the "breakpoint table") and in the event of a "match" program execution is stopped and control is transferred to the monitoring system.

**Stop-conditions** activate the Breakpoint facility at the occurrence of one/many pre-selected conditions (e.g. a number of clock counts after a particular event has occurred, during a particular memory cycle, etc.).

Dumps record information about a "failing" state of computation (all or a selected part of store). Some examples of Dumps are the **Post-mortem Dump**, which is initiated after the termination of the user program, the **Snapshot Dump**, which is initiated at an intermediate execution point, and the **Comparison Dump**, which provides only the difference between the current computational state and a preselected one captured by a previous dump.

**Traces** provide a sequential record of program activity obtained during execution. Program-variable Trace, Instruction Trace, Subroutine Trace, are examples of Traces. Hence, Dumps are used to find wrong quantities, while Traces provide checks on specific code modules involving those quantities.

Intermediate output statements record intermediate data values of selected program variables during execution by being inserted at carefully selected places amongst the code in question. These statements can be conditional and therefore left within the final version of the program for maintenance purposes (e.g., to collect output used in confidence checks). The main advantage of this technique is that it is independent of program language and produces meaningful output which is in a format easily readable by the programmer (unlike traces).

**Debug-messages** provide useful information about the program under suspicion in the form of State-diagrams, Tree-diagrams, functional descriptions, and records of relevant reference information (decisions taken, results obtained during the debugging of a particular program module, etc.).

# 1.1.4 Program Performance Evaluation

Program Performance Evaluation is the process of checking non-logical correctness of programs.

Expected utilisation of resources, such as overall execution time response to external stimuli, data throughput rates, required memory size, etc., is checked via a number of different software techniques. For example, execution statistics are collected by inserting software counters at key locations within the user code [21,43].

# 1.2 Microcomputer Development Tools

Microcomputer systems are increasingly more involved in the control of real-time applications and are interfaced to unaccountable real-time environments; hence, the appearance of time-dependent bugs which are usually accompanied with the problem of repeatability. Unlike conventional digital systems, microprocessor systems often involve simultaneous hardware and software implementation (and therefore debugging); software bugs may be taken as hardware malfunctions or vice-versa. In addition, problems such as accessing Program Status Information, controlling program execution and user interfacing (command language, Program Status Information display format, etc.), which were tackled in conventional systems via sophisticated operating systems, now emerge in the microcomputer world.

If only for the above reasons debugging such systems require a

high degree of hardware and software expertise. Therefore, it was realised early in the evolution of the microcomputer that there is a need for different debugging tools than those used in conventional systems.

Initially, application software was written in а CTOSE development mode; that is, a host computer (maxi/mini) was used to assemble/compile the source program and even simulate its execution for debugging purposes. The obvious advantage of this method was that some of the software needed was already available within the chosen host system (e.g., file management and editing facilities). Any problems arising later on while the target MPU was executing the object code were tackled using either storage oscilloscopes or logic ana-These devices, because they operate down at the **lysers** [42]. binary system level, some-times octal/hexadecimal representation is provided (e.g., the HP 1610B logic analyser), and can only capture a very small "trace" of the original execution (usually 64 execution steps), are very inefficient as far as software debugging is concerned. Even during hardware debugging, and especially when a large number of control signals is to be monitored, the interpretation of the captured data is very difficult because the information shown on the screen is limited to a large number of binary/hexadecimal digits with no reference whatsoever to corresponding signal-names or other target system information.

Therefore, it was realised that some means of controlling and monitoring the target MPU was required for debugging purposes. Initially, **microcomputer analysers**, which are logic analysers specially tuned to microcomputer needs, were developed. These devices, apart from monitoring facilities can also provide minimal control over the program execution. Later on a more substantial breakthrough was the development of **Microcomputer Debugging Consoles.** These consoles, according to their organisation, are divided into two main categories, namely the **Hardware Consoles** and the **Software Consoles.** Some examples of both kinds of consoles are given below in an attempt to show the variety of debugging techniques used and discuss their organisation. A hardware console [16] is based on a front-end panel (LEDs+switches) and attached to the target MPU buses via a dedicated hardware interface which not only takes care of the data traffic across itself but also controls the MPU in question. Both actions are initiated via certain signals generated by the panel control keys.

A hardware console, being part of the target microcomputer. has the advantage of debugging the suspect software within the real environment (Resident Approach). Its simplicity allows a cheap construction and, therefore, is quite popular especially amongst amateurs. Furthermore, its hardware interface is usually fast enough to be employed in a primitive type of critical-time debugging. On the other hand its functionality is limited due to the inflexible input/output device used and the lack of computing power; only basic debugging functions are available, such as MPU initialisation, singlestep/continuous user program execution and direct memory access (useful for both hardware and software debugging since it is hardware driven). Any further debugging capability, such as accessing of MPU registers, would involve either additional hardware or a specially written program executed by the target MPU itself (e.g., NIKBUG [28]). In addition, the "hardness" of the console-MPU interface makes it impossible to attach a hardware console to different kinds of MPUs without major re-design of the interface. This inflexibility may be tackled successfully by employing a microprogrammable version of the console-MPU interface (Firmware Console [28]) whose properties could be changed to suit different MPU-types.

### 1.2.2 Software Consoles

A software console is based on a flexible input/output device, such as a TTY, utilising the computing power of a processor to perform various tasks, including debugging. In particular, either a host computer is employed (Cross Approach), or the target MPU itself (Resident Approach), or both (Semi-resident Approach). **Cross Approach** : In the cross approach the debugging process is controlled by the "debug" section of the host software. The host development system itself is a microcomputer based on an MPU functionally identical to the target one. This implies that, in addition to executing its operating system, the host MPU directly executes the target application software.

For example, Intel's INTELLEC MDS [27] and Motorola's **EXORciser** [37] microcomputer development systems employ the computing power of the 8080/8085 and M6800 MPUs respectively. These MPUs, not only provide the required software development environment (file handling, cross-assembly, etc.) but also execute the produced 8080/6800 code under the control of the "system monitor" and "EXbug" monitors respectively.

Resident Approach : In the resident approach the debugging process is controlled by a Monitor program which is loaded onto the target system together with the application software. Following the availability of increasingly more microcomputer support software (even high level language compilers are provided within microcomputer systems) the development of resident debugging consoles is not surprising.

Motorola's monitor, called **MIKBUG** [37], takes control either on "reset" or by executing a Software Interrupt Instruction (SWI) placed by the user at a key point within the program (primitive "breakpoint" facility). The software interrupt forces the MPU status into the system stack before passing control to MIKBUG which, responding to user commands entered via a serial asynchronous line, supplies some basic debugging functions such as accessing both memory and MPU-register contents (found in the stack). Control is passed back to user program by executing an "Return from Interrupt" instruction (RTI) which restores the MPU status.

The **BEDBUG** monitor [13] (implemented on the M6800 microcomputer) controls user-program execution by inserting automatically dummy SWI instructions in between user instructions. Control is passed to BEDBUG, as explained in the previous paragraph, which updates the display memory and then receives user debug commands. The output device used is not a TTY but a memory-mapped character display. At the end of a debugging cycle, an RTI instruction is executed passing control to the next user instruction. Apart from the usual capabilities found amongst monitor programs, the Bedbug monitor provides of continuous display user-program status information (snapshots), object code disassembly and software breakpoint table using user-defined symbols for address identification.

The **ALADDIN** debugging system [12] is also based on a monitor program whose main difference from other monitors is that a location independent breakpoint facility is employed. In particular, debugging assertions, which describe logical relations among various components of the program state, are inserted in between assembly language statements. The user program is executed via interpretation because the ALADDIN execution handler must have control of the CPU between execution of successive object code instructions in order to evaluate the assertions and suspend execution of the target program if the outcome is false.

The SOLDA monitor [7] employs the source language debugging technique [41]. That is, all debug information is referred to the source listing and not to the machine language version of the program. In particular, the program is written in highlevel-language (ESPRINT in this case) and during its compilation debugging code is inserted in between statements. The generated object code is linked with parts of the SOLDA system before being loaded into the memory. During debugging the user enters commands which, after being interpreted by SOLDA, are executed under its close supervision.

Semi-resident : In the semi-resident approach the debug-Approach ging process is controlled by the "debug" section of the host operating system as with the cross approach. However, the application software is executed by the target computer, which is connected to the host system, and not by the host processor. Various ways of connecting the two systems exist some of which are given below.

Many microcomputer development systems are attached to the target system via either a ROM socket (ROM Emulator), or an MPU socket (In-circuit Emulator). The advantage of the ROM emulator is that it replaces the target system ROM with RAM which can be separately loaded and accessed. An in-circuit emulator [30] emulates under real-time conditions the functions of the missing MPU chip by employing either the same MPU model as the one used in the target system, or bit-slice architectures which mimic the target MPU functions. The software debug functions of the host development system may then be extended into the target system. However, debugging of real-time applications remained difficult. Hence, a realtime trace interface is usually employed which, in conjunction with the in-circuit emulator, captures the state of the MPU buses for a fixed number of clock cycles prior to an execution break.

For example, Intel's INTELLEC MDS [27] microprocessor development system is equipped with a dedicated in-circuit emulator, namely the ICE-80 which amongst other capabilities can capture 44 machine cycles in real time thus permitting limited realtime debugging.

The **HP-6400** [25] and **TECTRONIX-8002/8001** [45] development systems use a generalised version of the in-circuit emulator technique. In particular, they can cope with different MPU types by employing the corresponding in-circuit emulator (based on an identical MPU chip) and changing some of the system software (e.g., cross-assembler).

A similar debugging approach is employed within the AMPL TI-9900 Microprocessor Prototyping Laboratory [46]; the difference being that interactive emulation and trace control is achieved via an in-circuit emulator which is supported by a high level interpretative debug language, the AMPL. The AMPL is an expression-oriented structured language and not a command oriented monitor as in most microcomputer development systems. The user may enter an AMPL debug statement (or a block of debug statements) which is interpreted by the system software. A debugging activity may then be performed without close user supervision.

An interesting version of the semi-resident approach is that employed by MicroAde [6]; the host system (DEC PDP-11 controlled by RT-11 operating system) is connected to the target microcomputer via а standard serial asynchronous line. Although this type of interface ensures microcomputer independence at hardware level (a serial link is available within most MPU systems) both the host software and the target-MPU software must be adjusted appropriately. The former, apart from its general purpose run time system, interactive debugging system, user communication system, and other utility programs such as loader, editor, PROM programmer and floppy disk driver, requires a cross-assembler for the generation of the target MPU object code (program modules are written in target The latter, apart from its native MPU assembly language). monitor, requires a "debug interface" program which controls any interaction between the host debugging system and, via the native monitor, the user application programs. MicroAde also provides memory reference via user-set symbols, automatic execution of test sequence and result comparison against a preestablished record, test log, input/output simulator and finally MicroCOBOL, which enables the user to write microcomputer independent programs in COBOL syntax (these programs are compiled into MPU independent intermediate code, which is loaded into target memory together with the MPU dependent MicroCOBOL interpreter).

The Millennium Micro System Emulator [34] is also a generalised version of the in-circuit emulation technique but with the flexibility built-in in the in-circuit emulator end and not in the host development system end; that is, it is a stand-alone in-circuit emulator which is connected to any dedicated host computer via an asynchronous serial line (RS-232), thus transforming it into a universal development system. The above programmability is achieved via bit-slice processor techniques. Finally, as with other in-circuit emulators, the Millennium Emulator has an optional real-time trace facility, which is one of the most advanced that currently exist. In particular, this trace facility employs a l28-location trace memory, event detection consisting of two comparators capable of performing either (=) or ( $\langle \rangle$ =) or ( $\rangle$ =) operations between address/data/control lines and user preset values, detection of fetch/memory/IO cycles, and a further detection of a pass count of n events and/or a delay count of n clocks. A combination of the above events may be chosen for trace qualification while a count of either real-time, or one of the above events may be made between two points in a program or between events.

A serial asynchronous line is also used by the CONTEXT microcomputer development system [44] for connecting the host computer (DEC PDP-11) to any target MPU. Program modules are written in CORAL-66, compiled into PDP-11 code, and run under the RSX 11-M operating system and a package of software aids (MASCOT). When all modules are completed and satisfactorily tested within the host, the corresponding CORAL-66 compiler is employed to translate them into target MPU code, which is transferred via the link to the target MPU. At this point the source language debugging technique is employed; that is, as far as the user is concerned the CORAL-66 version of the program is executed and not the target MPU code. Test are then run under CONTEXT control and via the TTY link. A monitor program, previously loaded into the micro, collects and passes information back to the host via the link for displaying and monitoring purposes.

Approaches : The main advantage of the cross approach Comparison is that the application software is designed, written and debugged into a host environment which, provides many development software packages and sophisticated input/output devices. Mainly for reasons of economics these tools could not have been made available in a user system. However, if the produced software does not work first-time in the application environment (and this is very often the case) debugging becomes rather difficult especially for real-time applications.

With the **resident approach** on the other hand, the application software is executed within the real environment; a desirable property since simulation cannot cover all real-world situations. However, a lot of system processing time is allocated for the upkeep of the resident monitor which controls the debugging process and, therefore, this approach is not appropriate for time-critical applications.

The semi-resident debugging approach combines the "best of both worlds"; that is, the powerful software development tools of a host computer and the capability of debugging the latest version of the program within the real environment (host and However, as can be target computer are coupled together). seen from the examples given above, a small monitor program is usually required within the target system for collecting program-status information and driving the Host-MPU link (MicroAde and CONTEXT systems). Therefore, debugging a program without slowing down its execution (Real-time Debugging) is not possible; only in the case of the in-circuit emulation technique, where a trace memory is incorporated into the system and assuming that it is possible to employ sophisticated monitoring conditions in order to counterbalance the limiting amount of this trace memory, real-time debugging is possible. However, even systems that satisfy the above assumption (e.g., the Millennium Emulator) cannot cope with certain aspects of real-time debugging such as MPU-registers monitoring (see Chapter 2).

## 1.3 Research Direction

An analysis of the debugging process follows in Chapter 2 of this thesis with emphasis on the debugging tool capabilities, the availability of which should make efficient real-time debugging possible. In Chapter 4, a debugging system is proposed based on a new debugging technique (Chapter 3) which is suitable for interactive debugging of real-time microcomputer systems at the source language level. Finally, in Chapter 5 a prototype real-time debugging system is developed, which is then evaluated in Chapter 6.

### CHAPTER 2

#### 2 REAL-TIME DEBUGGING PROCESS

The degree of efficiency of the real-time debugging process depends not only on factors such as the quality of the program, the programmer's open-mindness and knowledge in relation to both the application problem and the operational environment, the kind of the real-time application, the type of the error in question, etc., but also on the capabilities of the debugging tools.

#### 2.1 Debugging Process Analysis

An analysis of the debugging process follows in order to reveal the differences between conventional and real-time debugging and, consequently, decide on the basic capabilities which a real-time debugging tool should have.

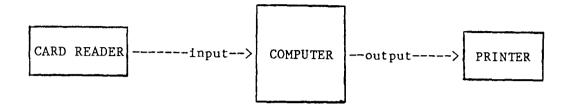

### 2.1.1 Conventional Computer System Debugging

Figure 1 shows a computer system suitable for running programs of non-real-time nature and interfaced to some external hardware, partitioned into well defined independent modules (e.g., card reader, printer), which is controlled by the system's utility software. The target program is defined by what the user wants to do, the processor employs known semantics for program interpretation, the initial state of the system is known, the input to the program is well defined and, therefore, this is a **Deterministic System**. Hence, a complete description of what the system should do can be derived at any stage of the software development process.

Abnorma1 termination of program execution, generation of "strange" output, wrong sequencing of operations, etc., indicate the existence of at least one program error. Past psychological studies [19] have shown that programmers debug their programs by initially trying to understand the actual behaviour of the "wrong" program version. During this program behaviour analysis one subconsciously attaches a value to each program module indicating the probability of having (or not having) an error. After comparing all available Program Status Information with the expected program state, derived from the description of what the program is supposed to do, these values are either increased or decreased; an action which influences the progress of the debugging process. Then, after deciding on the type of Program Status Information to be monitored and on the execution interval during which this monitoring is to take place, a program re-execution is initiated which, because the system is deterministic, follows the original program path; that is, a malfunction occurring within a deterministic system is repeatable.

Therefore, a number of re-executions may be initiated, during each of which different Program Status Information in monitored, until a "mismatch" between the current program state and the expected program state is detected, which hopefully will lead to the error in question.

A variety of systems are available allowing Program Status Information monitoring of programs written in low level languages (# 1.2.2), or modern high level languages for that matter [15,43], running in conventional processor systems under the control of either a Monitor program or an operating system.

Microcomputer engineers usually employ the **Single-stepping** execution technique for Program Status Information monitoring. That is, the user decides that the probability of an error occurring at a particular point within a program module is rather high, allows execution to continue until just before this point (up to which program behaviour is understood) planning to execute one instruction at the time thereon and collect Program Status Information for debugging purposes. Address Breakpoints control this activity.

Single-stepping, being a rather mechanical and slow process, is an inefficient technique as far as Program Status Information monitoring is concerned and in the world of large conventional systems has been replaced long ago by other more efficient techniques (# 1.1.3) such as tracing, dumping, monitoring of inter-module message flow, etc; although some times single-stepping is currently used when debugging CPU hardware. However, as will be shown in the next section, these techniques are not suitable for real-time debugging.

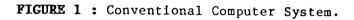

### 2.1.2 Real-time Computer System Debugging

Sophisticated operating systems have been traditionally provided, among other reasons, for handling real-time applications. However, real-time debugging remained a complex process.

Figure 2 shows a similar computer system to that of Figure 1 interfaced to a real-time application which normally consists of interacting hardware modules which the user program controls and which interact further with the real-time environment (it is assumed that the utility input/output devices are controlled by the operating system).

The input to the computer system is a function of the target hardware's timing/functional characteristics and also, if a feedback control is employed, a function of the control output of the computer system itself. Therefore, this input cannot defined unless a complete description of the target be In practice, however, the target hardware is available. hardware behaviour is unpredictable either because most of the applications involve simultaneous software and real-time hardware development (i.e., complete hardware description candescription not be derived), or because hardware yet

correctness cannot be guaranteed due to its high complexity and to uncertainty as to its response to a certain combination of real-time external events (highly asynchronous characteristics). Therefore, real-time systems are usually **nondeterministic;** a complete description of what the system should do at a specific instant in time cannot be guaranteed that it can be derived.

The non-deterministic nature of real-time computer systems implies that it is difficult to predict "expected" program states, against which any captured Program Status Information should be compared in order to decide that the program is (or is not) behaving properly. In other words, it is particularly difficult to decide on the type of the required Program Status Information; very often the wrong Program Status Information is monitored which does not help in the detection of the existing error. However, it is more than likely that the program path execution is unrepeatable and, therefore, additional program status information cannot be obtained.

**Execution unrepeatability** forces the programmer to increase the Program Status Information amount which is monitored and this presents various problems associated with trace memory overflowing (# 2.1.1); not to mention that most of the obtained information is bound to be irrelevant to the malfunction in question and, therefore, misleading (even in cases where **Trace Formaters** are available).

Even if the execution of the program path in question is repeatable, the currently available Program Status Information monitoring techniques introduce a considerable time-overhead to the target program execution time in cases where extensive monitoring is required (# 1.1.3). Consequently, the relationship between the program and its external environment is altered, making diagnosis of intermittent and other timedependent faults under these conditions impossible. Hence, the unrepeatability problem discussed above persists.

The "stack" arrangement found in most modern MPU designs, forms a good environment for subroutine usage (including

interrupt routines). The result is that modular programming and, therefore, modular debugging is encouraged. However. microcomputer real-time debugging becomes critical only when program modules have been linked together (System Debugging) and the entier program is executed within the target environ-That is, only when both the target application timing ment. and the program timing are coupled together forcing the occurrence of unprecedented timing errors. This implies that a cross-simulator can be used initially, for checking the logical correctness of each program module, until the complete program is available. Only then, it is necessary to transfer the program to the target environment for subsequent real-time debugging.

This thesis, is concerned with real-time debugging and, therefore, it is assumed that the program development has reached the System-Debugging level and that it has been transferred to the target environment for subsequent real-time debugging, which by its very nature is performed "on-line" (Interactive Debugging).

### 2.2 Real-time Debugging Tool Capabilities

Due to human memory and processing capacity limitations programmers are trying to detect only one error at a time and are focusing their attention on a local region of code. This also implies that specific information is usually requested from the debugging tool employed.

Obviously, selective monitoring is desirable during real-time debugging. This implies that monitoring must be controlled by evaluating logical conditions which relate program-status information elements to user-predetermined addresses/constants or other Program Status Information elements. The conditions involved should also specify the information type to be monitored (e.g., all the values which a particular variable acquires), the origin of the monitor activity (e.g., at the entrance of a subroutine, after an interrupt, etc.) and its duration in terms of either time or event occurrences (e.g., for a period of "n" clock-cycles, as soon as another condition is met, etc.).

Selective real-time monitoring of Program Status Information MPU registers) is (excluding currently implemented via hardware techniques (e.g., Millennium Emulator (# 1.2.2)). However, there is a limit to the number of operands which a logical condition can have, depending on the amount of hardware that is available for its evaluation. A software implementation would be more flexible but would slow down program execution which is not acceptable for real-time system debugging (# 2.1.2). Furthermore, because in practice realtime program behaviour is unpredictable, the majority of the real-time malfunctions, including intermittent faults, present serious problems; guessing what sort of information to monitor is difficult (# 2.1.2). Cases like these are very difficult to be debugged employing currently available debugging systems even though such systems may include selective monitoring of Program Status Information.

Monitoring in real-time Program Status Information (preferably selectively) is clearly desirable, but is it possible? Could either the MPU-register contents, or the program variables residing in memory, be monitored without halting or slowing down the target program execution? Could input/output device registers be monitored without affecting their contents (an inevitable fact in the case of "active" registers which are usually employed in input/output interface devices)? Could the vast amount of trace memory required for storing the captured Program Status Information be kept to a practical size? And, finally, could all these happen in a general kind of way in order to be applicable to a variety of real-time systems based on either identical or completely different microcomputers?

These are some of the "real" questions that emerge as soon as the design requirement of monitoring Program Status Information in real-time is considered.

-23-

### 2.3 Summary

Real-time debugging presents two basic problems, namely <u>Execu-</u> <u>tion Unrepeatability</u> and <u>Transparent Accessing of Program</u> <u>Status Information</u>. If efficient real-time debugging is to be achieved, it is essential that the debugging system can deal with these two problems. Only then "Program Status Information Selective Monitoring" and other techniques may be employed to achieve proper user interfacing to the Debugging tool and, consequently, to increase the debugging efficiency even further.

## CHAPTER 3

#### **3 ACTION-REPLAY DEBUGGING TECHNIQUE**

Having presented the basic problems encountered in real-time debugging (Chapter 2), an investigation is now undertaken into the possibility of providing a "transparent" solution; that is, a solution that does not involve the user in extra, time consuming activities. In particular, the possibility is investigated of transforming an "unrepeatable" real-time execution into a "repeatable" one and at the same time of transforming the real-time Program Status Information monitoring into a non-real-time process and still being able to study all the real-time activities of the program.

Obviously, the nature of the system activities which influence a real-time program execution is a key factor in the above mentioned transformations and, therefore, needs some clarification. Starting at a particular instant in time, the execution flow is influenced by :

- the internal MPU state at that instance (i.e., the current value of its registers),

- 2) any data entering the MPU during subsequent execution either via the system memory (including the DMA buffer), or via any of the input ports attached to the MPU buses (including any status information generated by these ports), or via input ports located within the MPU chip itself,

- any hardware interrupts serviced by the MPU thereafter (e.g., the NMI and IRQ of the M6800).

Any other changes occurring at the user-application side of the input ports are redundant as far as software debugging is concerned since they do not influence the program execution flow.

As soon as program execution has been abnormally terminated and assuming that the internal state of a non-deterministic microcomputer system is known at an arbitrary moment in time, it is possible to reconstruct any subsequent system state if all the external stimuli that entered the microcomputer system from that moment onwards are known together with their correspondence to the program path in question.

Having kept both the initial microcomputer internal state and the external stimuli sequence, there is no reason what so ever for not being able to repeat the simulated re-execution several times and each time to traverse the same program path; that is, execution repeatability is achieved.

The above program path reconstruction need not take place in real time. Slowing-down the execution does not alter the program behaviour as long as all external stimuli, which have been recorded via some sort of real-time monitoring mechanism (# 3.1), are synchronised with this execution. Hence, execution-speed control is achieved.

Program status information, which is an exact image of the required real-time program status information, may be obtained selectively during these non-real-time re-executions; that is, the accessing of Program Status Information is no longer a critical design requirement.

Finally, the user himself does not need to know anything about the low-level information captured during the real-time execution of the target program, or indeed anything about the reexecution mechanism itself; instead, the user's attention can be focussed upon the type and amount of Program Status Information which is required in order to understand the behaviour of the program path in question. Hence, <u>a</u> "<u>transparent</u>" <u>solu-</u> tion is achieved. In general, therefore, the above technique allows real-time debugging to take place within a non-real-time environment. For obvious reasons it is named **Action-replay Debugging Tech**nique (\*).

Problems associated with "external-stimuli monitoring", "program-path Action-replaying", "Program Status Information monitoring" and other processes relevant to the Action-replay Debugging Technique, are discussed in the following sections of this chapter.

### 3.1 External Stimuli Real-time Monitoring

The external stimuli, which are monitored during the real-time execution of the target program (# 3.0), consist of any data entering the target system via the input ports, any hardware interrupts triggered by an action initiated within the application hardware (software interrupts need not be monitored since their initiation is triggered from within the program itself) and any data entering the system memory via DMA techniques.

There are two basic problems associated with the real-time monitoring of the external stimuli. The first problem is their synchronisation with the Action-replay execution and the second problem is the risk of the trace memory overflowing. These problems are discussed in the following sections.

<sup>\*</sup> A similar technique has been previously employed in the EXDAMS Debugging System [2] which, however, requires the insertion of a large amount of diagnostic/monitoring code into the target program and, therefore, is not suitable for realtime debugging.

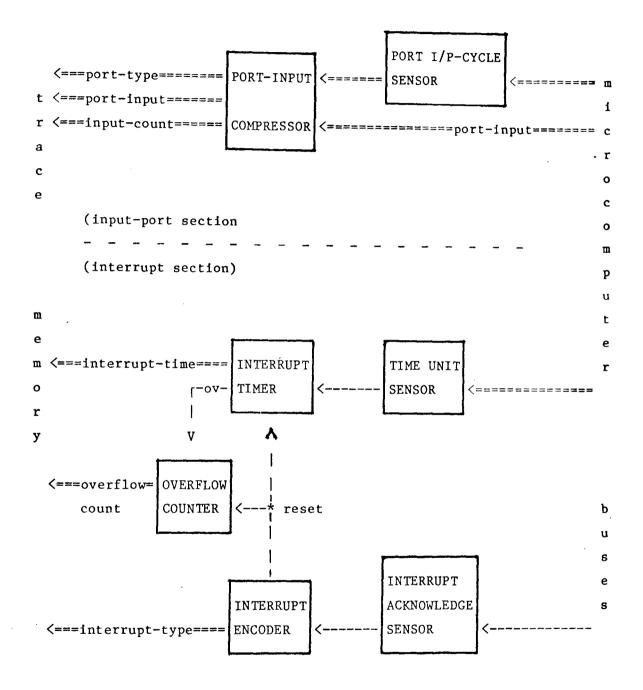

#### 3.1.1 Input Port Data Monitoring

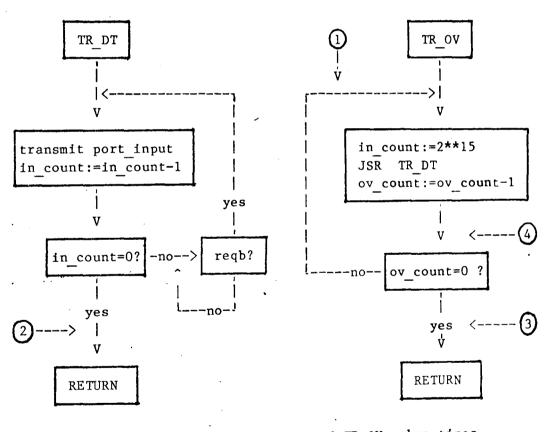

Input Port Data : The required synchronisation is not dif-Synchronisation ficult in the case of data entering the system via the input ports and under the control of the MPU itself. During the real-time execution, and in particular during input port accesses, the data bus contents are recorded and stored sequentially in the Data Trace Memory. During the Action-replay execution, this trace information is played back in a FIFO fashion; that is, the next data word to be provided during an input port cycle is the word which is located next in the trace memory.

The above procedure is independent of the number of input ports in the system.

Data Trace Memory : The basic problem when monitoring the Overflow input data sequence is that of data arriving at the input ports at a large rate and overflowing the trace memory in a very short period of time. This is especially true for the type of malfunctions for which the Action-replay debugging technique is most needed; that is, intermittent errors which by nature require long monitoring sessions. Obviously, if the trace memory overflows, an Action-replay of the program path in question can take place only until that point.

Assuming that the trace memory remains fixed to a practical size, the above problem can be dealt with in a variety of ways.

One way is to <u>omit redundant data</u>. For example, because only the data which actually enters the system influences program execution (# 3.0), monitoring at the MPU side of the input ports and not at the target application side ensures that only essential information is recorded. A similar technique may be applied when monitoring system interrupts (# 3.1.2), or data entering the system memory via DMA techniques (# 3.1.3).

Another way of delaying the overflowing of the trace memory is to compress repetitive data. For example, a repetitive data word (say, n-bit wide) may be stored in a (n+1)-bit wide trace memory only once using the extra bit to indicate that in addition to this word a (n+1)-bit wide number, generated by a counter and specifying the number of times this particular word successively entered the system, is stored in the next trace memory location. This facility can take care of a situation where the MPU is executing a "test-for-device-notbusy" loop, reading the same status word. However, if more than one input port is employed the benefit of this facility is lost unless either only one such loop exists while the rest of the ports employ interrupts, or the input port identifiers are taken into account during the data compression process and a record of multiple counts is kept (one per port identifier).

Finally, conditional breakpoints can be employed making the above trace memory suppression technique application dependent. That is, the user may introduce non-critical time slots within the program real-time execution (e.g., after the application program enters a computational process during which any communication with the real-time world is suspended). Then, the debugging system may halt the target MPU not only when an error condition has been detected, but also as soon as one of these time slots is reached (and this is sensed by the conditional breakpoint mechanism). Then, a full system state snapshot (intermediate snapshot) is taken and program execution together with a new external-stimuli trace is restarted, in which case, the Action-replay execution of the program path will take place from that moment onwards.

Clearly, no matter how sophisticated data reduction techniques and monitoring controls are employed, the trace memory overflow problem still exists if the real-time monitoring process of the input ports is performed for long periods of time. Then, the only solution is to increase the trace memory size.

## 3.1.2 Interrupt Monitoring

Interrupt: The case of interrupt synchronisation isSynchronisationrather different from that of the input<br/>port data (# 3.1.1). During the real-

time execution, a hardware interrupt is not triggered directly by an MPU activity (as with the accessing of an input port register) but by an asynchronous external event. Therefore, monitoring information about the type of the interrupt in question is not sufficient for synchronising the interrupt with the Action-replay execution.

The obvious way of accomplishing the required interrupt synchronisation is via the Time-synchronisation method. That is. to employ a counter for measuring the time elapsed between two successive interrupts and, as soon as an interrupt is sensed, to store this information in the Interrupt Trace Memory together with some data indicating the interrupt type. This time interval must not be measured in terms of real-time but either in terms of clock-cycles (for clock-synchronised bus architectures), or in terms of bus activities (for asynchronous bus architectures); only then strict synchronisation is kept between a particular interrupt and the program path execution. For example, assuming an 1MHz clock, a 32-bit counter can measure a time interval of up to 71 minutes and a (32+n)bit wide trace memory is required, where "n" is a binary number specifying the interrupt type (hence, an 1-bit number is sufficient for the two M6800 interrupt inputs while each of the eight "restart" addresses of the INTEL8080/5 may be encoded into a 3-bit number).

However, sensing the occurrence of an interrupt, while monitoring the MPU interrupt inputs, is not easy. That is, assuming that a race condition exists between two interrupts during the real-time execution, these interrupts may or may not be handled in the same order during the Action-replay. For example, in the case of the M6800 many special conditions of interrupt responses must be taken into account [37, A9], such as :

"If IRQ occurs during an SWI instruction, the pulse will be lost because SWI clears the interrupt latches", "If IRQ and NMI are active concurrently, the MPU will recognise NMI. In so doing, the interrupt latches are reset", "If an NMI occurs while a SWI is being executed, the interrupt vector will be retrieved from the IRQ location", etc.!

In addition to the above problem, an interrupt may occur very close to its recognition point (usually, it is latched in the MPU during the last cycle of an instruction). Then, the interrupt setup time (Ts) must be taken into account, making sure that this particular interrupt has or has not been latched-in (e.g., Ts = 200ns minimum for the M6800 and Ts = 120ns minimum for the INTEL 8080/5). This implies that the interrupt lines must be sampled at exactly "Ts" nanoseconds prior to the interrupt recognition point. However, sensing this point in time is not easy since the last instruction cycle must be detected first.

The above problems can be solved by monitoring the "interrupt acknowledge" MPU line instead of the corresponding interrupt line. This way, changes on interrupt lines which do not influence program execution (e.g., because the interrupt mask is disabled) are not monitored. However, some MPU makes do not provide an "interrupt acknowledge" signal.

In software terms, an interrupt is acknowledged the moment the first instruction of the corresponding routine is executed. Therefore, a more general way of sensing that an interrupt has occurred is to decode the "origin" address of the corresponding interrupt routine (assuming that interrupt routines are entered only via the MPU interrupt mechanism and never via a "jump" instruction from elsewhere in the program).

Another way of sensing that the MPU is responding to an interrupt is to decode the interrupt vector addresses as they appear onto the address bus during the MPU interrupt servicing sequence (# 5.4.1); however, in this case the user program may only write and not read from the interrupt vector location.

An alternative interrupt synchronisation may be achieved via the **Address-synchronisation method.** That is, instead of tracing the interrupt type and its arrival time, as with the time-synchronisation method, a history of the entire program path is recorded in terms of addresses; the idea being, to synchronise the interrupt in question to the address bus activity.

An interesting side effect of the Address Synchronisation Method is that the above trace information may be used for verifying the Action-replay process itself (# 3.3).

Interrupt Trace : If the time-synchronisation method is Memory Overflow employed, either the timing counter or the interrupt trace memory may overflow

resulting in the loss of the required synchronisation. In order to delay the timing counter from overflowing instruction cycles, instead of MPU clock cycles, can be used as time units. However, these cycles are not easily detected in some MPU types. Alternatively, code "fetch" cycles can be used as time units which are easily detected by finding out whether the current contents of the address bus correspond to the memory section which holds the program code and not data. Then, a 32-bit counter can measure a time interval of up to 2\*\*32/(600\*1024) = 1 hour 56 minutes (where 600kbytes/s is a typical amount of executable code for an 1MHz driven M6800 MPU (Appendix A)).

Obviously, the address synchronisation method involves the tracing of a vast amount of addresses (more than lMbyte/s in average for an M6800 driven at lMHz). As it is shown in Appendix A, this amount of traced information may be reduced considerably (less than 30kbytes/s), but only at the expense of complex hardware.

Intermediate snapshots of the target system state, taken during the non-critical time slots within the real-time execution (# 3.1.1), may also be used for solving the Interrupt Trace Memory overflow problem. However, as with the Data Trace Memory, it may be necessary to increase the memory size in order to cope with certain applications.

#### 3.1.3 DMA Input Data Monitoring

DMA Input Data: Special consideration must be applied toSynchronisationthe synchronisation of data entering the<br/>target system memory via DMA techniques.

That is, the incoming DMA data must be monitored and stored in the trace memory. However, the input port data synchronisation method (# 3.1.1) cannot be applied here, since the DMA activity is transparent to the target program after the initialisation of the DMA controller has taken place and since the operation of the DMA controller cannot be easily synchronised with the program operation.

Data entering the system memory via DMA influences indirectly the program execution; that is, only after it has been accessed by the MPU. Hence, by assuming that the address range corresponding to the block of memory which accepts the DMA data (namely the DMA buffer) is part of the "memory-mapped input/output" address space, the memory read-cycles which address this memory block long after the data entered the system can be treated as "port input cycles". Thus, data entering the MPU via the DMA section of the target system memory comply with the same rules applying to data entering through an input port as far as data-compression and Action-replay synchronisation are concerned.

In implementation terms, a programmable decoder can be employed which, having been loaded with the address limits of the DMA buffer, generates a signal indicating that the DMA buffer is currently accessed. Only then the data in question is monitored and stored in the Port Trace Memory (# 5.3.3). It should be noted, however, that any status returned to the MPU by the DMA controller during the original program execution should also be monitored so that synchronisation with the program execution can be achieved during the Action-replay.

DMA Trace Memory : Assuming that the above mentioned DMA Overflow data monitoring technique is employed, the port input data compression technique (# 3.1.1) may be applied in the DMA data monitoring process. However, due to the fact that DMA is usually associated with high data rates, the DMA trace memory is bound to overflow quickly in which case trace memory expansion should be considered.

#### 3.2 Program Path Action-replay

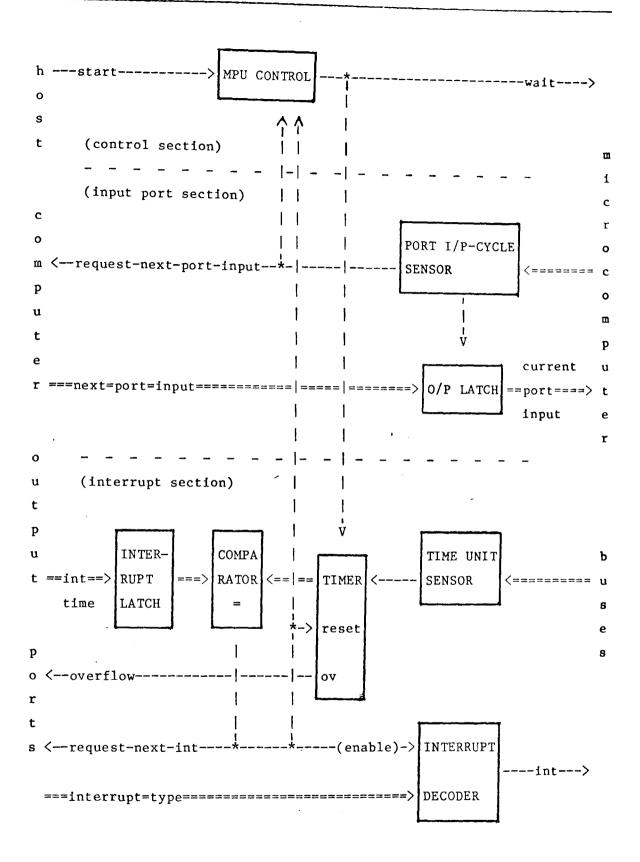

Having recorded in real-time the external-stimuli sequence which influences the target program behaviour, Action-replay debugging may now commence. As will be shown in the sections which follow program path Action-replay may be implemented in a variety of ways.

# 3.2.1 Hardware Simulator Approach

The ideal Action-replay "simulator" from a speed and reliability point of view is the MPU itself; the required re-execution may be performed at any speed up to the "real-time" one while there is no need to worry about the correctness of a software simulator.

In particular, during the Action-replay of the program path in question, the microcomputer system is isolated from the outside real-time world by disabling all input ports and interrupt lines; this is why the initial state of these ports need not be monitored prior to the real-time execution. Then, both the MPU and memory states are reset either to their initial state or to any other prerecorded intermediate state. Finally, the MPU is forced to re-execute the program path by data/status, which data bus the placing onto the MPU corresponds to the current input port cycle, and by activating the interrupt line, which corresponds to the interrupt-type (found in the interrupt trace memory), in synchronisation with the execution (# 3.1). During subsequent Action-replays any requested Program Status Information is monitored (#3.4).

During Action-replay the target computer output ports are also disabled unless it is required to debug the user application hardware; that is, in certain cases of open-loop control systems it is possible during Action-replay to initiate the original sequences of operations in the target application hardware, by allowing the control signals to influence the external hardware as normal, and to study these sequences by employing storage oscilloscopes, logic analysers, etc.

# 3.2.2 Software Simulator Approach

A software simulator of the target MPU can be employed alternatively. Then, having initialised the simulated MPU in accordance to the prerecorded initial/intermediate target MPU state, Action-replay may commence. In particular, the simulator accepts as input the target MPU source code and the external stimuli sequence (# 3.1) and provides an "Action-replay" of the program path in question, during which Program Status Information is monitored (# 3.4).

However, unless the simulator correctness has been proven without any doubt, there is no guarantee whatsoever that the same program path as that followed during the original execution can be reconstructed during Action-replay.

An additional problem is that of the target MPU to simulator speed ratio. This is a critical consideration especially since it may be necessary to initiate multiple Action-replays for additional Program Status Information monitoring (# 3.4).

Finally, the MPU Action-replaying simulator may function either within the target MPU itself (resident approach), or within a host computer (cross-approach). The latter case is considered more advantageous (# 4.2), because a host computer may provide a more comprehensive range of facilities than the target microcomputer.

# 3.3 Action-replay Verification

The correctness of the Action-replay process must be checked since there is nothing worse than a debugging tool which cannot be trusted. Therefore, a mechanism is required which detects that the program path followed during the Actionreplay execution is diverging from the original program path.

The **address-synchronisation method** (# 3.1.2), provides a simple and foolproof consistency check between the original execution and the Action-replay execution. That is, each program node generated during the Action-replay execution is compared with the corresponding program node found in the pre-recorded real-time program node record. Therefore, no other information is required for the consistency checking process than that which already has been recorded.

If however the **time-synchronisation method** has been chosen, then it is impossible to check for consistency unless some additional information is recorded. The most economical solution is to provide an **address label** (in terms of the Program Counter register contents) for each interrupt record and during Action-replay to check for consistency between this label and the current address shown on the address bus just before the interrupt service routine is entered. Correspondingly, a **time-label** (in terms of interrupt timer contents) must be provided for each input data record.

# 3.4 Program Status Information Non-real-time Monitoring

The program status information monitoring may be split into two distinct tasks, both of which are user programmable (but should also have a default state), namely the Monitoring Conditions Evaluation and the Program Status Information Formating and Displaying tasks.

# 3.4.1 Monitoring Conditions Evaluation

The Program Status Information monitoring process is controlled via a number of user defined logical conditions (that is, conditional breakpoints relating program addresses, variables, constants, as well as events), the basic purpose of which is to minimise the amount of Program Status Information down to the user current requirements.

In particular, prior to the Action-replay activation, the debugging system's **Monitoring Conditions Evaluator** finds the type of operands which are involved in the conditions themselves and activates the appropriate software hooks which are controlled by the **Condition Operands Monitor**. Then, the Action-replay process is activated and the required operands are obtained and passed to the Evaluator which, in the event of finding a condition "true", interrupts the Action-replay execution and enables the **Program Status Information Monitor**.

The above organisation may provide tracing of a particular memory location (program variable), the flow of instructions but not their results (or vice-versa), successful Branch/Jump instructions, program statistics, etc. In addition, tracing may be enabled only for an execution period specified by code address limits, real-time limits, etc.

A possible implementation of the above ideas is given in reference 9.

### 3.4.2 Program Status Information Formating and Displaying