# Efficient Architectures for Multidimensional Discrete Transforms in Image and Video Processing Applications

## By

## Saad Mohammed Saleh Al-Azawi

School of Electrical and Electronic Engineering

A thesis submitted for the degree of Doctor of Philosophy

Faculty of Science, Agriculture and Engineering

Newcastle University, June 2013

# Declaration

I declare that this thesis is my own work and it has not been previously submitted, either by me or by anyone else, for a degree or diploma at any educational institute, school or university. To the best of my knowledge, this thesis does not contain any previously published work, except where another person's work used has been cited and included in the list of references.

Saad Mohammed Saleh Al-Azawi

**Supervisor's Certificate**

This is to certify that the entitled thesis "Efficient Architectures for Multidimensional

Discrete Transforms in Image and Video Processing Applications" has been

prepared under my supervision at the school of Electrical and Electronic Engineering

/Newcastle University for the degree of PhD in Electronic Engineering.

Signature

**Supervisor: Professor Said Boussakta**

Date:

June 2013

Signature

Student: Saad Mohammed Saleh Al-Azawi

Date:

June 2013

iii

To My Beloved Family

# Acknowledgements

In the name of Allah, the Beneficent and the Merciful. Praise and Gratitude be to Allah for giving me strength and guidance, so that this thesis can be finished accordingly.

I would like to thank my supervisors: Professor Said Boussakta and Professor Alex Yakovlev. Please let me express my deep sense of gratitude and appreciation to both of you for the knowledge, guidance and unconditional support you have given me. I wish you all the best and further success and achievements in your life.

My deepest gratitude goes to my dearest parents, for their immense patience and unconditional support and encouragement throughout my life. My brothers, sisters and their daughters and sons: thank you very much for your prayers and encouragements. My friends and colleagues: thank you very much for what you have done for me. I thank you all for the companionship that has made this journey much easier. In fact, I do not need to list your names because I am sure that you know who you are.

I would like to express my sincere gratitude to Dr. Omar Nibouche for the very useful feedback on my research work. Ms. Sharon Pointer, thank you very much for your useful English language advice and comments. Also, I would like to thank all the Electrical and Electronic Engineering School and Newcastle University staff for their support during my study.

Finally, I also thank the Iraqi Ministry of Higher Education and Scientific Research, the Iraqi Cultural Attaché in London, Diyala University and the College of Engineering/Diyala University for supporting me during my study abroad.

# **Abstract**

This thesis introduces new image compression algorithms, their related architectures and data transforms architectures. The proposed architectures consider the current hardware architectures concerns, such as power consumption, hardware usage, memory requirement, computation time and output accuracy. These concerns and problems are crucial in multidimensional image and video processing applications.

This research is divided into three image and video processing related topics: low complexity non-transform-based image compression algorithms and their architectures, architectures for multidimensional Discrete Cosine Transform (DCT); and architectures for multidimensional Discrete Wavelet Transform (DWT). The proposed architectures are parameterised in terms of wordlength, pipelining and input data size. Taking such parameterisation into account, efficient non-transform based and low complexity image compression algorithms for better rate distortion performance are proposed. The proposed algorithms are based on the Adaptive Quantisation Coding (AQC) algorithm, and they achieve a controllable output bit rate and accuracy by considering the intensity variation of each image block. Their high speed, low hardware usage and low power consumption architectures are also introduced and implemented on Xilinx devices.

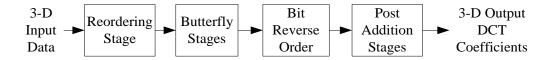

Furthermore, efficient hardware architectures for multidimensional DCT based on the 1-D DCT Radix-2 and 3-D DCT Vector Radix (3-D DCT VR) fast algorithms have been proposed. These architectures attain fast and accurate 3-D DCT computation and provide high processing speed and power consumption reduction. In addition, this research also introduces two low hardware usage 3-D DCT VR architectures. Such architectures perform the computation of butterfly and post addition stages without using block memory for data transposition, which in turn reduces the hardware usage and improves the performance of the proposed architectures.

Moreover, parallel and multiplierless lifting-based architectures for the 1-D, 2-D and 3-D Cohen-Daubechies-Feauveau 9/7 (CDF 9/7) DWT computation are also introduced. The presented architectures represent an efficient multiplierless and low memory requirement CDF 9/7 DWT computation scheme using the separable approach.

Furthermore, the proposed architectures have been implemented and tested using Xilinx FPGA devices. The evaluation results have revealed that a speed of up to 315 MHz can be achieved in the proposed AQC-based architectures. Further, a speed of up to 330 MHz and low utilisation rate of 722 to 1235 can be achieved in the proposed 3-D DCT VR architectures. In addition, in the proposed 3-D DWT architecture, the computation time of 3-D DWT for data size of 144×176×8-pixel is less than 0.33 ms. Also, a power consumption of 102 mW at 50 MHz clock frequency using 256×256-pixel frame size is achieved. The accuracy tests for all architectures have revealed that a PSNR of infinite can be attained.

# Contents

| List of Figures                                           | xii |

|-----------------------------------------------------------|-----|

| List of Tables                                            | xvi |

| Abbreviations                                             | xix |

| Chapter 1: Introduction                                   | 1   |

| 1.1 Introduction                                          | 1   |

| 1.2 Digital Image and Video Signals                       | 1   |

| 1.3 An Overview of Image and Video Compression Algorithms | 2   |

| 1.4 Research Motivation                                   | 3   |

| 1.5 Research Objectives                                   | 3   |

| 1.6 Contributions                                         | 4   |

| 1.7 Thesis Outline                                        | 5   |

| 1.8 List of Publications                                  | 6   |

| Chapter 2: Preliminary Concepts and Related Work          | 7   |

| 2.1 Introduction                                          | 7   |

| 2.2 Image and Video Compression Algorithms                | 7   |

| 2.2.1 Adaptive Quantisation Coding (AQC)                  | 8   |

| 2.2.2 Discrete Cosine Transform (DCT)                     | 9   |

| 2.2.2.1 DCT-Based Compression Systems                     | 11  |

| 2.2.2.2 3-D DCT Applications                              | 13  |

| 2.2.3 Discrete Wavelet Transform (DWT)                    | 13  |

| 2.2.3.1 DWT Decomposition Operations                      | 14  |

| 2.2.3.2 DWT Applications                                  | 18  |

| 2.3 Rate Distortion Measurements                          | 18  |

| 2.4 Related work                                          | 19  |

| 2.4.1 AQC Related Work                                    | 19  |

| 2.4.2 DCT Related Work                                    | 20  |

| 2.4.3 DWT Related Work                                    | 22  |

| 2.5 Field Programmable Gate Array (FPGA)                  | 24  |

| 2.6 Xi       | linx FPGA Devices' Main Components                    | 25 |

|--------------|-------------------------------------------------------|----|

| 2.6.1        | Configurable Logic Blocks (CLBs)                      | 26 |

| 2.6.2        | Block RAMs                                            | 27 |

| 2.6.3        | Distributed RAM (Available in SLICEM only)            | 28 |

| 2.6.4        | DSP Slices                                            | 28 |

| 2.6.5        | Specifications of FPGA Devices Used in This Thesis    | 28 |

| 2.7 Xi       | linx FPGA Design Tools                                | 29 |

| 2.7.1        | Xilinx System Generator for DSP                       | 30 |

| 2.7.2        | Vivado High Level Synthesis Design Suite (Vivado HLS) | 33 |

| 2.8 Ar       | chitectures Design Procedure                          | 33 |

| 2.9 Su       | mmary                                                 | 36 |

| Chapter 3: L | ow Complexity Block-Based Image Compression Systems   | 37 |

| 3.1 Int      | roduction                                             | 37 |

| 3.2 Ba       | ckground                                              | 38 |

| 3.2.1        | Block Truncation Coding (BTC)                         | 38 |

| 3.2.2        | Adaptive Quantisation Coding (AQC)                    | 40 |

| 3.3 Int      | ensity Based Adaptive Quantisation Coding (IBAQC)     | 41 |

| 3.3.1        | Algorithm1                                            | 42 |

| 3.3.2        | Algorithm2                                            | 44 |

| 3.4 Th       | e Proposed IBAQC Architectures                        | 46 |

| 3.4.1        | Model1                                                | 47 |

| 3.4.1        | .1 Minimum, Maximum and Mean Computation Units        | 47 |

| 3.4.1        | 2 Intensity Check Unit                                | 49 |

| 3.4.1        | .3 AQC Computation Unit                               | 50 |

| 3.4.2        | Model2                                                | 51 |

| 3.4.3        | AQC Architecture                                      | 52 |

| 3.5 Per      | rformance Evaluation                                  | 53 |

| 3.5.1        | Performance of the Proposed Algorithms                | 53 |

|      | 3.5    | 5.1.1    | Rate Distortion Performance of Algorithm1    | 53  |

|------|--------|----------|----------------------------------------------|-----|

|      | 3.5    | 5.1.2    | Rate Distortion Performance of Algorithm2    | 55  |

|      | 3.5    | 5.1.3    | Rate Distortion Performance Comparison       | 57  |

|      | 3.5.2  | Per      | formance of the Proposed Architectures       | 59  |

|      | 3.5    | 5.2.1    | Hardware Resources                           | 59  |

|      | 3.5    | 5.2.2    | Operating Frequencies and Power Consumption  | 60  |

|      | 3.5    | 5.2.3    | The Validation of the Proposed Architectures | 61  |

| 3.6  | 5      | Summa    | ary                                          | 65  |

| Chap | oter 4 | : High   | Speed Multidimensional DCT Architectures     | 66  |

| 4.   | 1      | Introdu  | action                                       | 66  |

| 4.2  | 2      | Fast Al  | Igorithms for DCT Computation                | 67  |

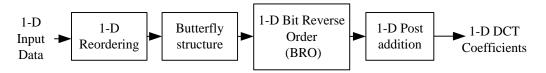

|      | 4.2.1  | The      | e 1-D DCT Radix-2 Algorithm                  | 67  |

|      | 4.2.2  | The      | e 3-D DCT VR Algorithm                       | 68  |

| 4.3  | 3      | 3-D D0   | CT RCF Architecture (RCF Architecture)       | 72  |

| 4.4  | 4      | The Pro  | oposed 3-D DCT VR Architecture               | 78  |

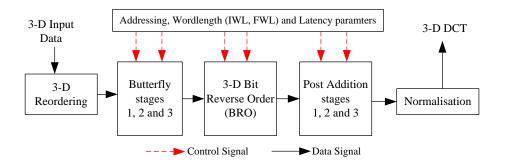

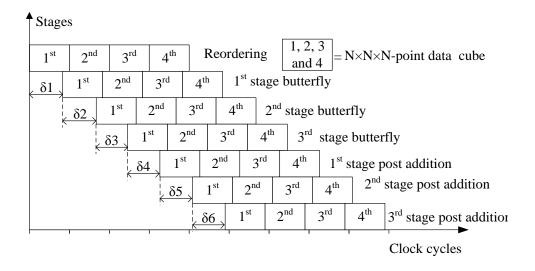

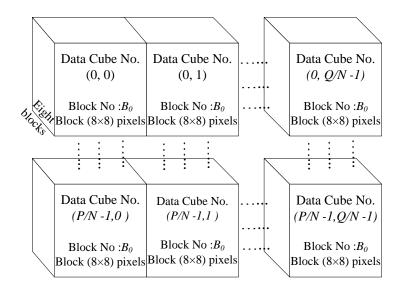

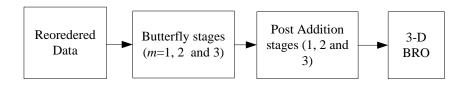

|      | 4.4.1  | The      | e 3-D Reordering Stage                       | 79  |

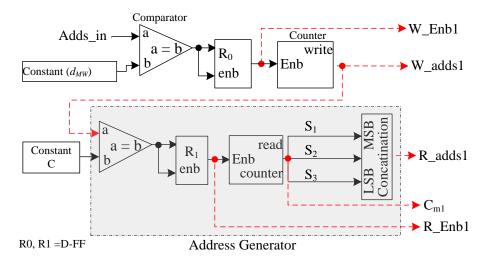

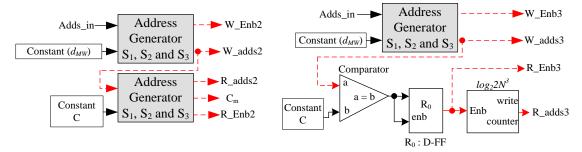

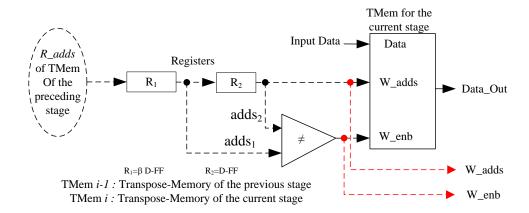

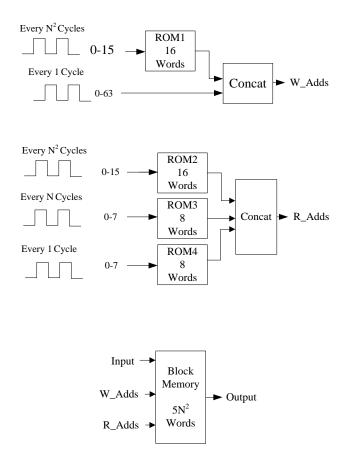

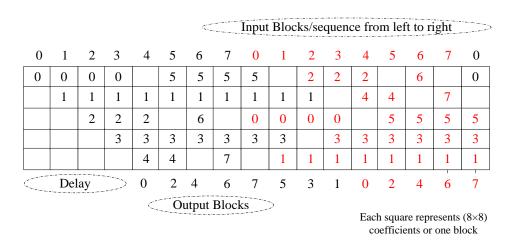

|      | 4.4    | 4.1.1    | Memory Writing Operation                     | 80  |

|      | 4.4    | 4.1.2    | Memory Reading Operation                     | 81  |

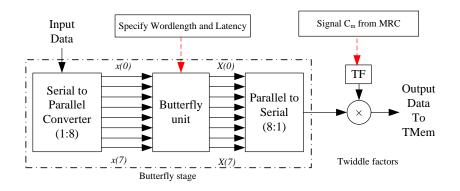

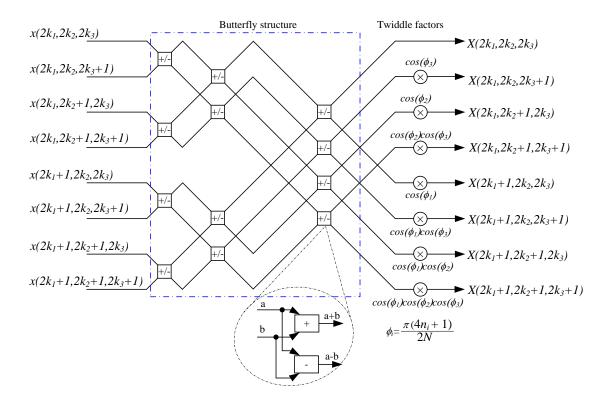

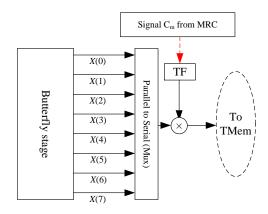

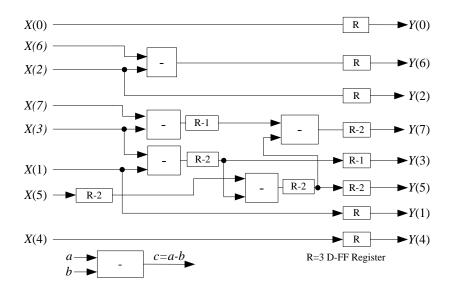

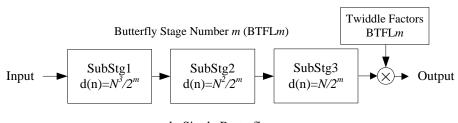

|      | 4.4.2  | But      | tterfly Stages                               | 81  |

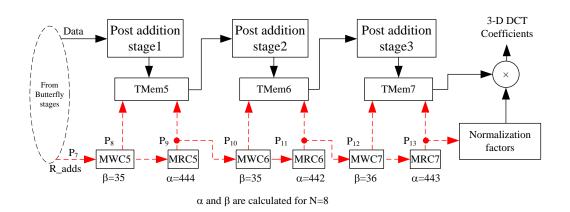

|      | 4.4.3  | Pos      | st Addition Stages                           | 85  |

| 4.5  | 5      | Results  | s and Discussion                             | 86  |

|      | 4.5.1  | Rat      | te Distortion Performance                    | 87  |

|      | 4.5.2  | Hai      | rdware Usage                                 | 89  |

|      | 4.5.3  | Spe      | eed and Power Consumption                    | 90  |

| 4.0  | 5      | Summa    | ary                                          | 92  |

| Chap | oter 5 | : Area-l | Efficient 3-D DCT Architectures              | 93  |

| 5.   | 1      | Introdu  | action                                       | 93  |

| 5 ′  | ,      | The 2 l  | D DCT VP Architectures                       | 0.4 |

| 5.2.1  | Reordering Stage                                             | 95  |

|--------|--------------------------------------------------------------|-----|

| 5.3 Si | ngle Path Data Flow 3-D DCT Architecture; Model1             | 97  |

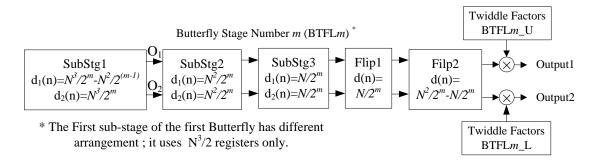

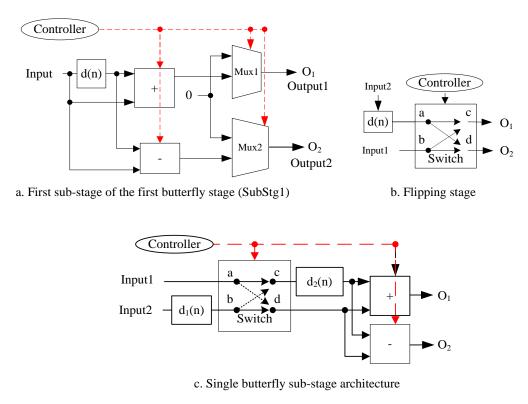

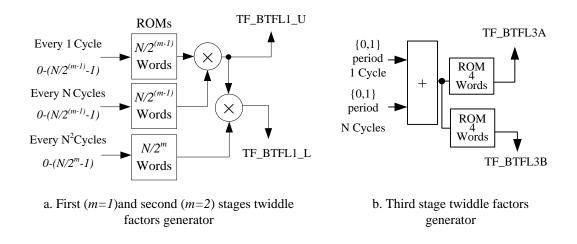

| 5.3.1  | Butterfly Stages                                             | 97  |

| 5.3.2  | Post Addition Stages                                         | 101 |

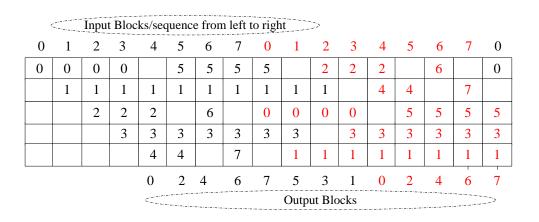

| 5.3.3  | 3-D Bit Reverse Order Stage (3-D BRO Stage)                  | 103 |

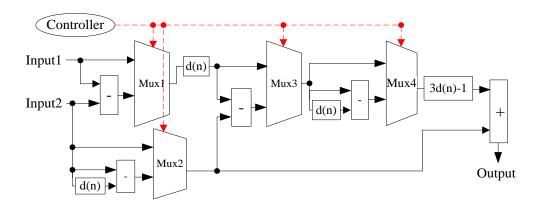

| 5.4 D  | ual Path Data Flow 3-D DCT Architecture; Model2              | 106 |

| 5.4.1  | Butterfly Stages                                             | 106 |

| 5.4.2  | Post Addition Stages                                         | 110 |

| 5.4.3  | 3-D Bit Reverse Order Stage (3-D BRO Stage)                  | 110 |

| 5.5 Pe | erformance Evaluation                                        | 111 |

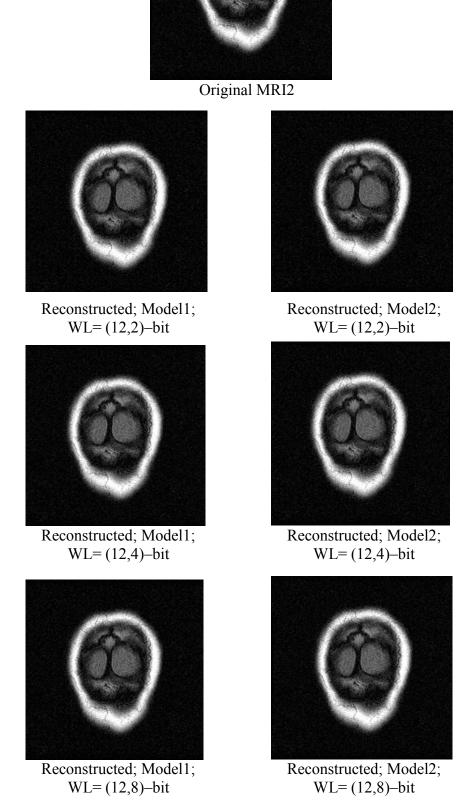

| 5.5.1  | Rate Distortion Performance                                  | 111 |

| 5.5.2  | Hardware usage                                               |     |

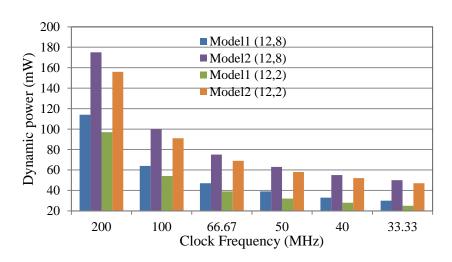

| 5.5.3  | Dynamic Power Consumption                                    |     |

| 5.5.4  | Comparing with Other Architectures                           |     |

|        | ımmary                                                       |     |

|        | Parallel and Multiplierless Multidimensional CDF 9/7 DWT Arc |     |

| _      | Faraner and Munipheness Munidimensional CDF 9/1 DWT Arc      |     |

|        | troductiontroduction                                         |     |

|        | ne CDF 9/7 1-D DWT Lifting Scheme                            |     |

| 6.3 TI | ne Proposed Lifting-based CDF 9/7 DWT Computation Scheme     | 121 |

| 6.4 TI | ne Proposed Lifting-based 1-D DWT Architecture               | 124 |

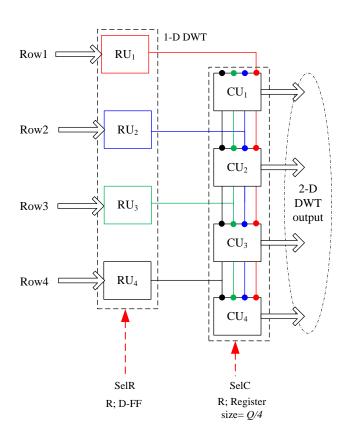

| 6.5 TI | ne Proposed Lifting-based 2-D DWT Parallel Architecture      | 127 |

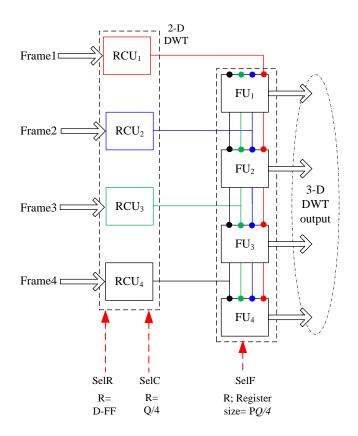

| 6.6 TI | ne Proposed Lifting-based 3-D DWT Parallel Architecture      | 130 |

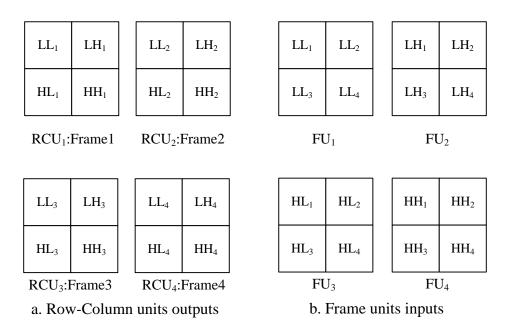

| 6.6.1  | Row-Column Units (RCUs)                                      | 131 |

| 6.6.2  | Frame Units (FUs)                                            | 131 |

| 6.7 R  | esults and Discussion                                        | 132 |

| 6.7.1  | The 2-D DWT Architecture Performance                         | 133 |

| 6.7.1  | .1 The Rate Distortion Performance                           | 133 |

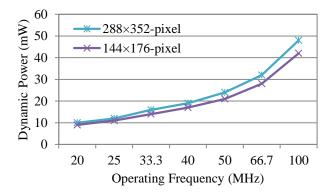

| 6.7.1  | .2 Power Consumption                                         | 134 |

| 6.7.1.3       | Hardware Usage                                                  | 134  |

|---------------|-----------------------------------------------------------------|------|

| 6.7.2         | The 3-D DWT Architecture Performance                            | 135  |

| 6.7.2.1       | Rate Distortion Performance                                     | 135  |

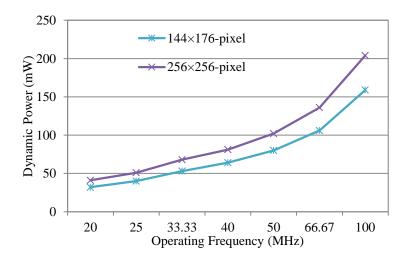

| 6.7.2.2       | Power Consumption Test                                          | 137  |

| 6.7.2.3       | B Hardware Usage                                                | 137  |

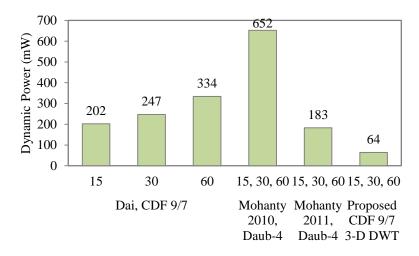

| 6.7.3         | Comparison with Other Architectures                             | 138  |

| 6.8 Sum       | nmary                                                           | 141  |

| Chapter 7: Co | nclusions and Future Work                                       | 143  |

| 7.1 Con       | iclusions                                                       | 143  |

| 7.2 Futu      | ure Work                                                        | 145  |

| Appendices    |                                                                 | 147  |

| Appendix A    | A: Brief Description of Xilinx FPGA Families                    | 147  |

| Appendix      | B : Pre-Processing Matlab Codes for IBAQC Model1 and Mod        | del2 |

| Architecture  | es                                                              | 149  |

| Appendix (    | C: Memory Writing/Reading Addresses of the proposed 3-D DCT     | VR   |

|               | Architecture                                                    | 153  |

| Appendix I    | D : Pre-Processing Matlab Codes for Chapter 4; Model1 and Mod   | del2 |

| Architecture  | es                                                              | 157  |

| Appendix 1    | E: Pre-Processing Matlab Codes for Chapter 5; Model1 and Mod    | del2 |

| Architecture  | es                                                              | 162  |

| Appendix F    | F: The 2-D and 3-D DWT Architectures Controllers                | 167  |

| Appendix C    | G: Pre-Processing Matlab Codes for Chapter 6; 2-D DWT and 3-D D | WT   |

| Architecture  | es                                                              | 171  |

| References    |                                                                 | 175  |

# List of Figures

| Figure 2.1: Basic block diagram of typical transform-based compression     | n / |

|----------------------------------------------------------------------------|-----|

| decompression system [36]                                                  | 8   |

| Figure 2.2: DCT based image compression/decompression system [36]          | 12  |

| Figure 2.3: Typical two levels 1-D DWT: a. Decomposition b. Reconstruction | 16  |

| Figure 2.4: One level 2-D and 3-D DWT decomposition.                       | 16  |

| Figure 2.5: Lifting scheme (a) decomposition (b) reconstruction            | 17  |

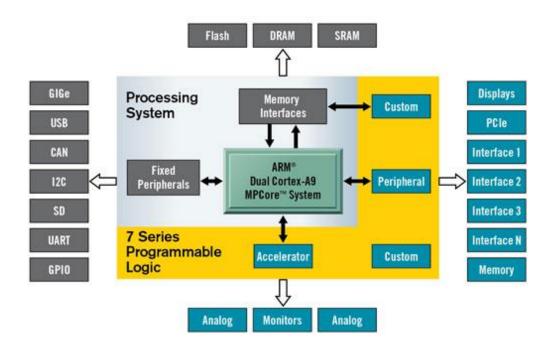

| Figure 2.6: Zynq-7000 system architecture [117]                            | 25  |

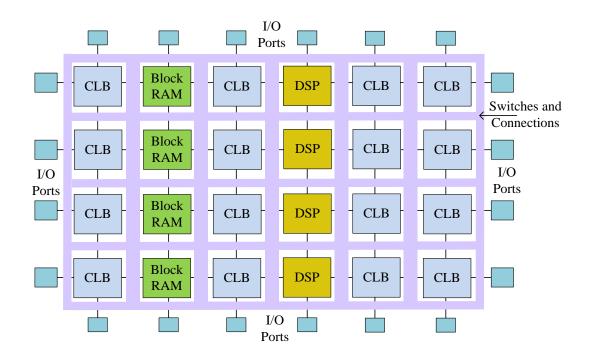

| Figure 2.7: Basic block diagram of an FPGA device architecture [126]       | 26  |

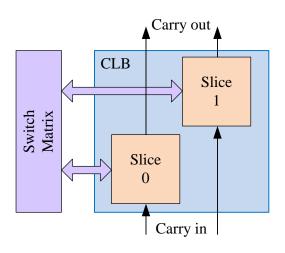

| Figure 2.8: CLB block diagram [120]                                        | 27  |

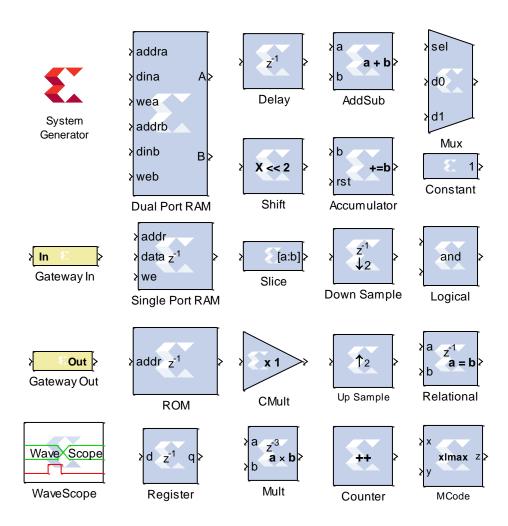

| Figure 2.9: Selected DSP blocks from system generator blockset             | 32  |

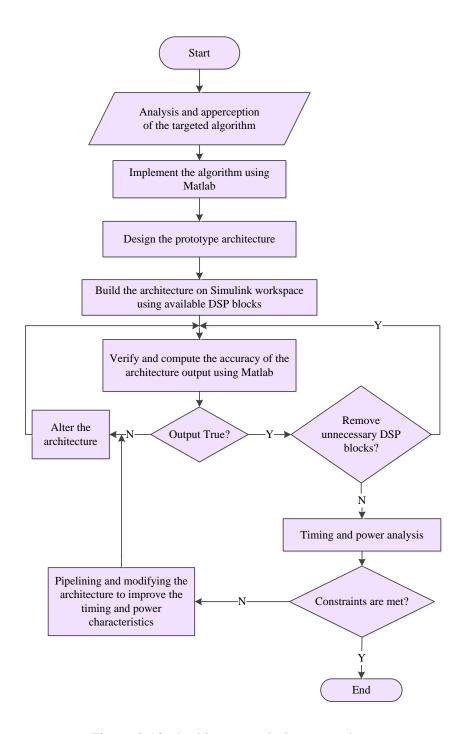

| Figure 2.10: Architectures design procedure.                               | 35  |

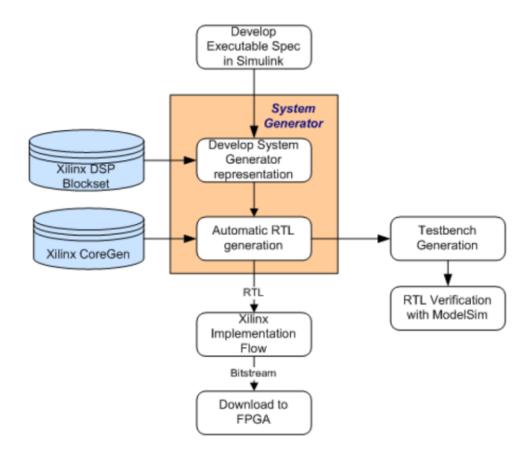

| Figure 2.11: System Generator design flow [132]                            | 36  |

| Figure 3.1: The AMBTC algorithm computation procedure.                     | 39  |

| Figure 3.2: The AQC algorithm computation procedure.                       | 40  |

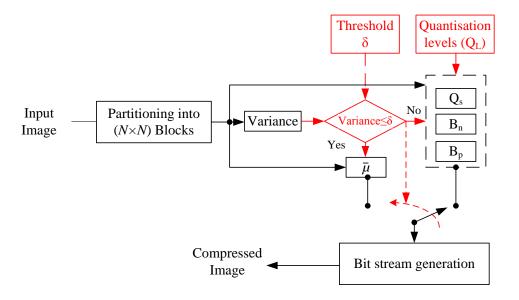

| Figure 3.3: Block diagram of Algorithm1.                                   | 42  |

| Figure 3.4: The Computation procedure of Algorithm1                        | 43  |

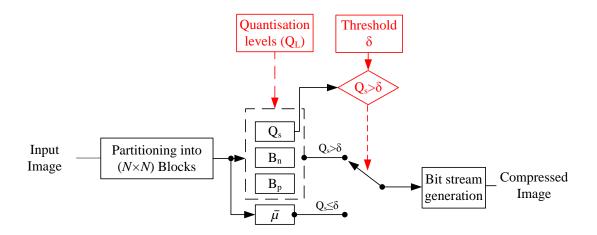

| Figure 3.5: Block diagram of Algorithm2.                                   | 45  |

| Figure 3.6: The Computation procedure of Algorithm2.                       | 46  |

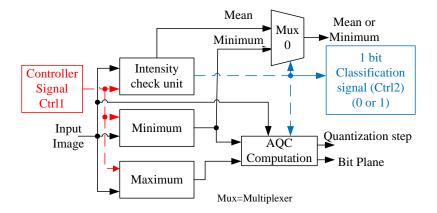

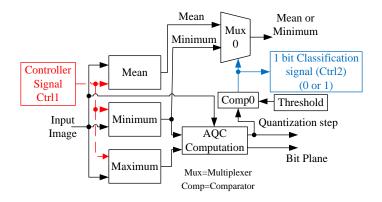

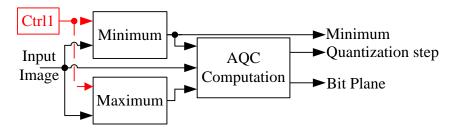

| Figure 3.7: IBAQC Model1 architecture.                                     | 47  |

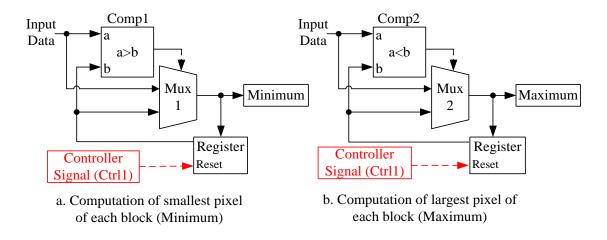

| Figure 3.8: Minimum and Maximum computation units                          | 48  |

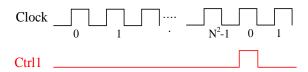

| Figure 3.9: Controller signal (Ctrl1).                                     | 48  |

| Figure 3.10: Intensity check unit of Model1                                | 49  |

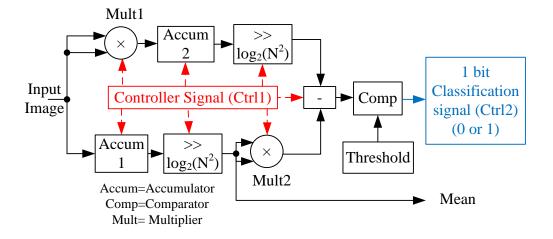

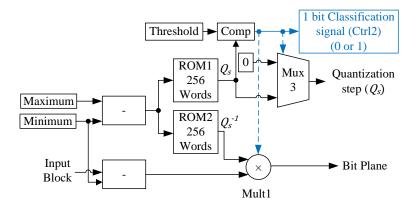

| Figure 3.11: AQC computation unit of Model1                                | 50  |

| Figure 3.12: IBAQC Model2 architecture.                                    | 51  |

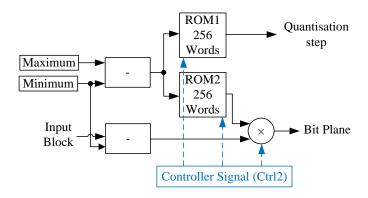

| Figure 3.13: AQC computation unit of Model2                                | 51  |

| Figure 3.14: The AQC architecture                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

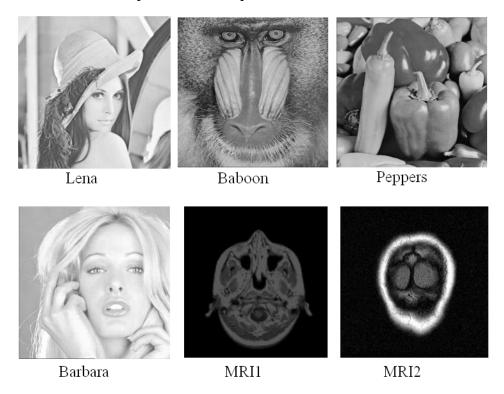

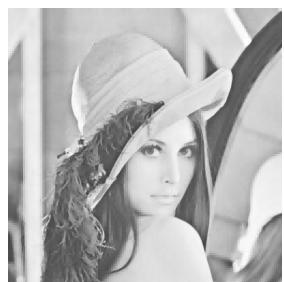

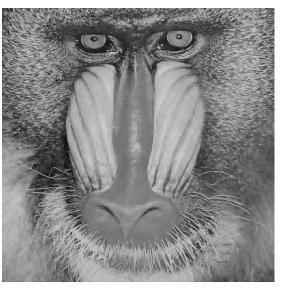

| Figure 3.15: Test images.                                                                                                                                     |

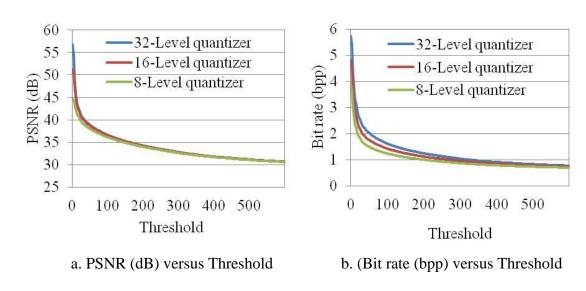

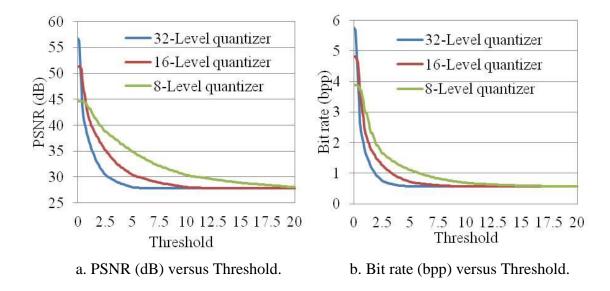

| Figure 3.16: Performance of the Lena image obtained using Algorithm1 for a block size of 4×4-pixel, different thresholds and 32, 16 and 8 quantisation levels |

| Figure 3.17: Performance of the Lena image obtained using Algorithm2 for block size of 4×4-pixel, different thresholds and 32, 16 and 8 quantisation levels   |

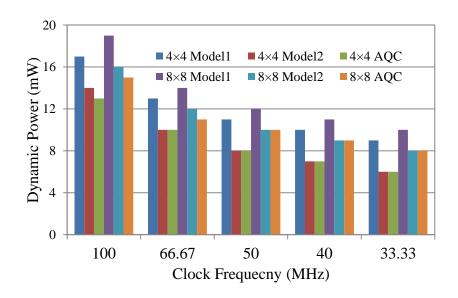

| Figure 3.18: Dynamic power consumption of the AQC and the proposed architectures using 4×4 and 8×8-pixel block sizes                                          |

| Figure 3.19: The Lena and baboon images computed using Algorithm1 and Algorithm2 architectures with a 4×4-pixel block size and 32 quantisation levels         |

| Figure 3.20: The Lena and baboon images computed using Model1 and Model2 architectures with a 4×4-pixel block size and 32 quantisation levels                 |

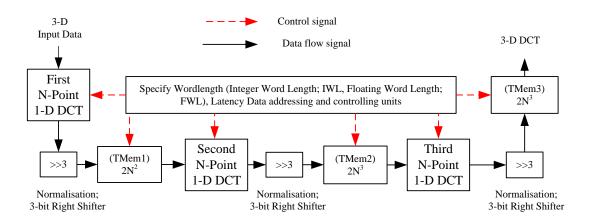

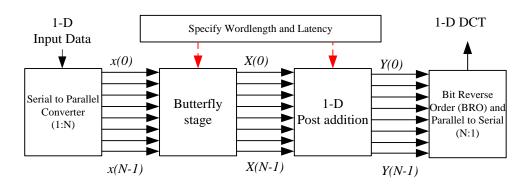

| Figure 4.1: Block diagram of 1-D DCT Radix-2 algorithm                                                                                                        |

| Figure 4.2: Block diagram of the whole RCF architecture                                                                                                       |

| Figure 4.3: Block diagram of N-point 1-D DCT architecture                                                                                                     |

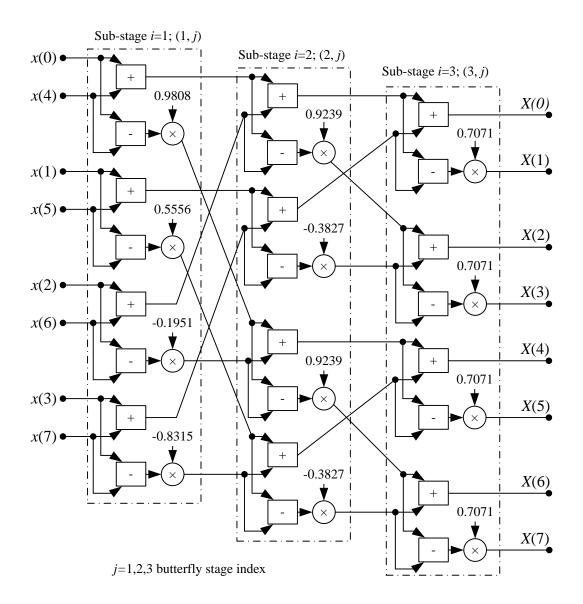

| Figure 4.4: Block diagram of 8-point butterfly stage (three sub-stages)                                                                                       |

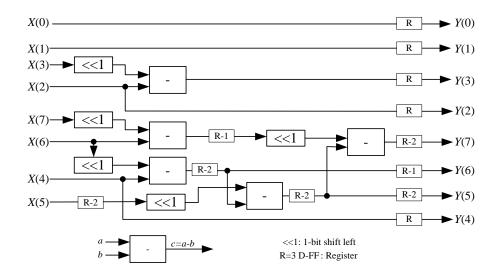

| Figure 4.5: Block diagram of 8-point post addition stage                                                                                                      |

| Figure 4.6: TMem1 writing /reading control unit of the first 1-D DCT stage75                                                                                  |

| Figure 4.7: Block diagrams of the second and third memory writing/reading control units (for TMem2 and TMem3)                                                 |

| Figure 4.8: Block diagram of 3-D DCT VR architecture                                                                                                          |

| Figure 4.9: The timing sequence of the proposed 3-D DCT VR architecture79                                                                                     |

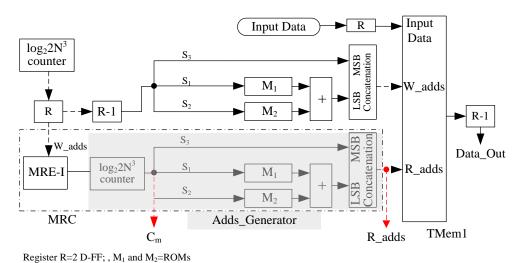

| Figure 4.10: Block diagram of the reordering unit                                                                                                             |

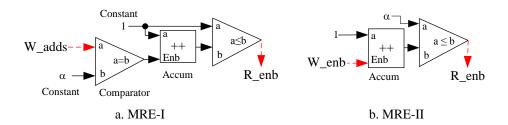

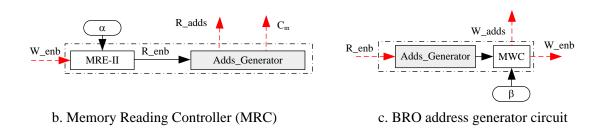

| Figure 4.11: MRE circuits                                                                                                                                     |

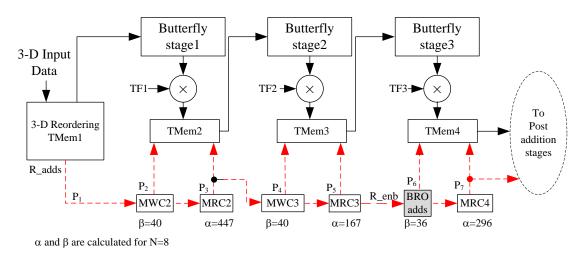

| Figure 4.12: Block diagrams of the butterfly stages and, the MRC and BRO address controllers                                                                  |

| Figure 4.13: Block diagram for single butterfly stage                                                                                                         |

| Figure 4.14: Eight-point butterfly structure.                                                                                                                 |

| Figure 4.15: The twiddle factor multiplication circuit for single butterfly stage83                                                                           |

| Figure 4.16: Memory Writing Controller (MWC) block diagram                                                       |

|------------------------------------------------------------------------------------------------------------------|

| Figure 4.17: The block diagram of the post addition stages                                                       |

| Figure 4.18: Eight points addition unit of each post addition stage                                              |

| Figure 4.19: Test MRI images and video sequences (first frame from each sequence). 86                            |

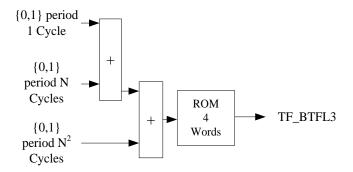

| Figure 5.1: Block diagram of the 3-D DCT VR algorithm94                                                          |

| Figure 5.2: An 8×8×8-pixel data cubes94                                                                          |

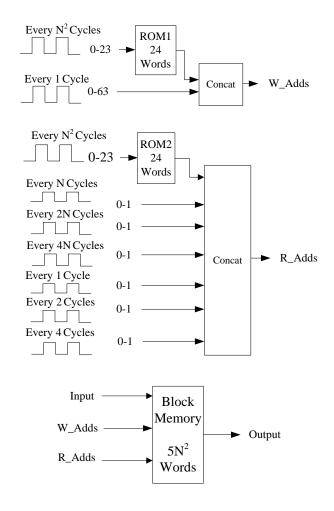

| Figure 5.3: Reordering circuit and memory content during reordering operation96                                  |

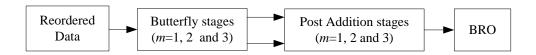

| Figure 5.4: Block diagrams of a. Model1 and b. Butterfly architectures98                                         |

| Figure 5.5: Single butterfly unit of Model198                                                                    |

| Figure 5.6: Twiddle factor generator circuit of the first butterfly stage99                                      |

| Figure 5.7: Twiddle factor generator circuit of BTFL2                                                            |

| Figure 5.8: Last sub-stage of BTFL3.                                                                             |

| Figure 5.9: Twiddle factor generator circuit of BTFL3                                                            |

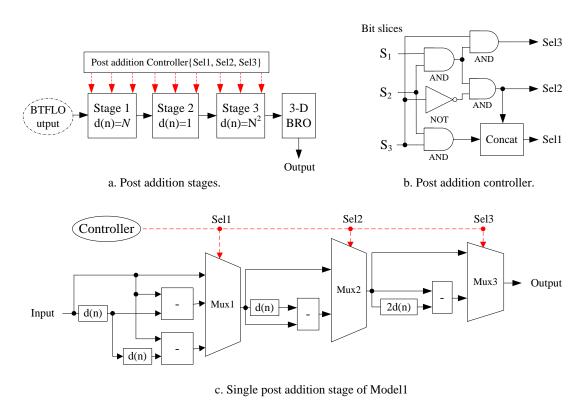

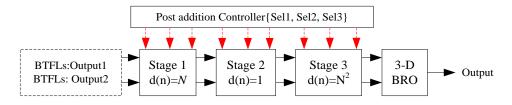

| Figure 5.10: Post addition stages and their controller                                                           |

| Figure 5.11: The 3-D BRO stage.                                                                                  |

| Figure 5.12: a. Block diagram of the proposed dual path data flow 3-D DCT architecture; Model2                   |

| Figure 5.13: The architecture of single butterfly stage of Model2                                                |

| Figure 5.14: Butterfly sub-stages and flipping stage in Model2                                                   |

| Figure 5.15: Twiddle factors generators for butterfly stages                                                     |

| Figure 5.16: Post addition stages.                                                                               |

| Figure 5.17: Third post addition stage (Stage3)                                                                  |

| Figure 5.18: The original and reconstructed MRI2 using Model1 and Model2 architectures for different wordlengths |

| Figure 5.19: Dynamic power consumption of the proposed architectures115                                          |

| Figure 6.1: The CDF 9/7 1-D DWT [28]                                                                             |

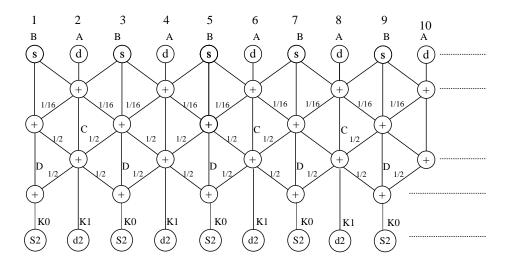

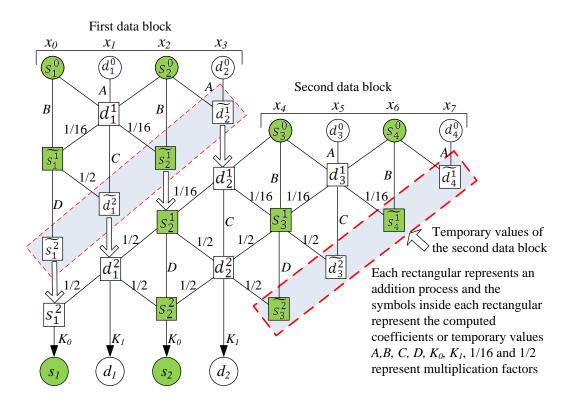

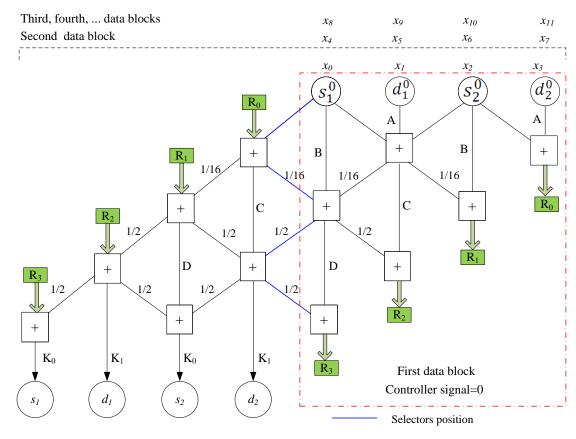

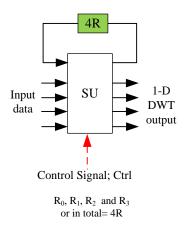

| Figure 6.2: The proposed CDF 9/7 computation scheme for the first two data blocks.122                            |

| Figure 6.3: Single unit (SU) of the CDF 9/7 1-D DWT architecture                                                 |

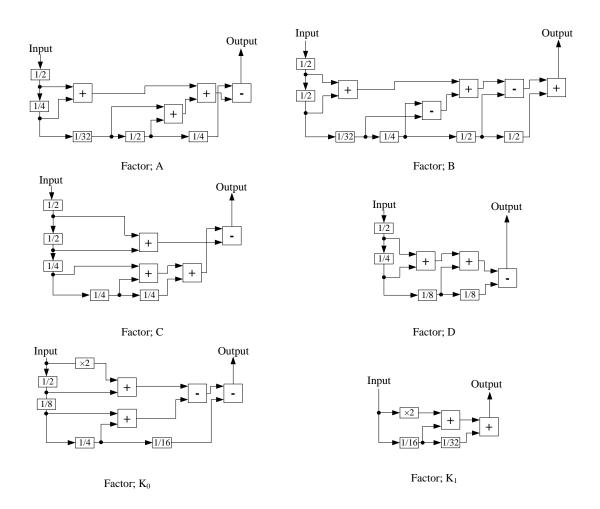

| Figure 6.4: The proposed shift-add multipliers                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.5 : The proposed 2-D DWT parallel architecture                                                                                                         |

| Figure 6.6: Four 4×4-sample data blocks                                                                                                                         |

| Figure 6.7: Block diagram of the proposed 3-D DWT lifting-based architecture 130                                                                                |

| Figure 6.8: Input bands to the frame units.                                                                                                                     |

| Figure 6.9: Power consumption for various operating frequencies using (11, 5)-bit wordlength.                                                                   |

| Figure 6.10: Dynamic power consumption (mW) for the proposed 3-D DWT architecture using various operating frequencies using (11, 5)-bit wordlength              |

| Figure 6.11: Power consumption (mW) of the proposed 3-D DWT and other architectures using 40 MHz clock frequency, (11, 5)-bit wordlength and 144×176 frame size |

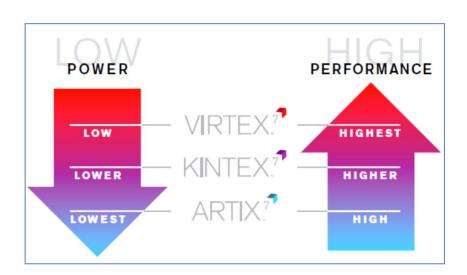

| Figure A.1: Series 7 Xilinx FPGA families performance comparison                                                                                                |

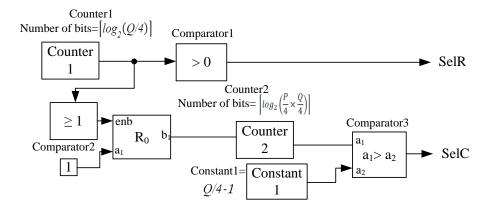

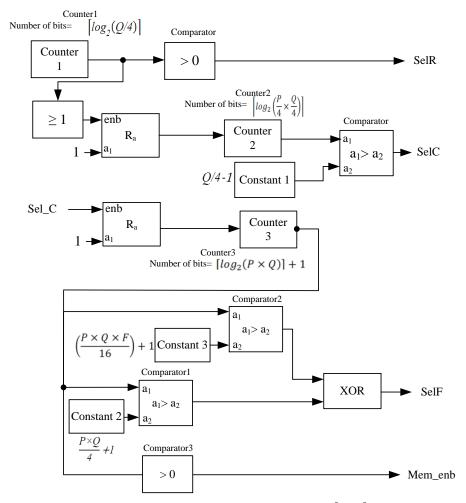

| Figure F.1: The 2-D DWT controller                                                                                                                              |

| Figure F.2: Down sampled 2-D DWT controller signals                                                                                                             |

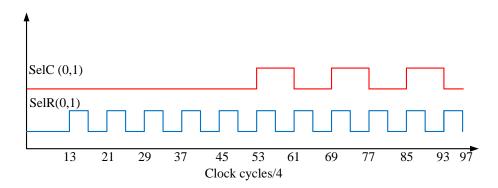

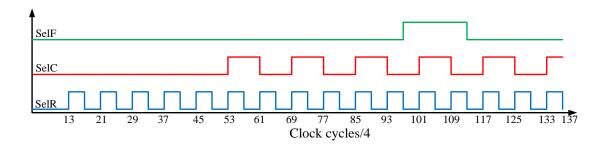

| Figure F.3: Controller block diagram of the proposed 3-D DWT architecture169                                                                                    |

| Figure F.4: The main signals of the 3-D DWT controller down sampled by 4                                                                                        |

# List of Tables

| Table 2.1: The arithmetic operations of the original RCF 3-D DCT, RCF Radix-2 and                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| VR algorithms [54, 56, 57]                                                                                                                          |

| Table 2.2: CDF 9/7 and Le Gall 5/3 analysis filters coefficients [32, 74]14                                                                         |

| Table 2.3: The arithmetic operations of the lifting-based 1-D, 2-D and 3-D CDF 9/7 wavelet filter                                                   |

| Table 2.4: Hardware resources in single CLB for Virtex 5 and Virtex 6 [120, 121]27                                                                  |

| Table 2.5: Summary of XC5VLX50T and XC6VLX760 Xilinx FPGA devices characteristics                                                                   |

| Table 3.1: Number of bits required for each block type for 4×4-pixel blocks using different number of quantisation levels                           |

| Table 3.2: Computational complexities of the AQC, Model1 and Model2 architectures.                                                                  |

| Table 3.3: PSNR and bit rate computed using Algorithm1 for different block sizes, quantisation levels and a low threshold (12)                      |

| Table 3.4: PSNR and bit rate computed using Algorithm1 for different block sizes, quantisation levels and a high threshold (400)                    |

| Table 3.5: PSNR and bit rate computed using Algorithm2 for different block sizes, quantisation levels and a low threshold (0.4)                     |

| Table 3.6: PSNR and bit rate computed using Algorithm2 for different block sizes, quantisation levels and a high threshold (2)                      |

| Table 3.7: Performance comparison between the AQC, Algorithm1 and Algorithm2 for Lena image.                                                        |

| Table 3.8: Hardware usage of the AQC and the proposed architectures                                                                                 |

| Table 3.9: Maximum operating frequencies, initial latencies and computation time for the AQC and proposed architectures using different block sizes |

| Table 3.10: The average bit rate and PSNR of the proposed algorithms and their corresponding architectures                                          |

| Table 4.1: The first eight addresses (R_adds1) for 8×8-point block76                                                                                |

| Table 4.2: Content of ROMs $M_1$ and $M_2$ for the reordering operation (TMem1 Writing                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation) (1) 80                                                                                                                                                                            |

| Table 4.3: The PSNR and RMSE between original and reconstructed input sequence                                                                                                               |

| and the maximum absolute error in 3-D DCT coefficients for the first eight input                                                                                                             |

| frames                                                                                                                                                                                       |

| Table 4.4: Comparison between hardware usages for different 3-D DCT architectures 89                                                                                                         |

| Table 4.5: Comparison between percentage utilisation rates of the proposed architectures using 21, 18 and 16-bit wordlengths                                                                 |

| Table 4.6: The power consumption and computation speed of the proposed architectures using different clock frequencies and 21, 18 and 16-bit wordlengths                                     |

| Table 4.7: Comparison of the normalised operating frequencies for different 3-D DCT architectures.                                                                                           |

| Table 5.1: The memory write/read block locations for reordering stage (block shuffling)                                                                                                      |

| Table 5.2: The memory write/read block locations for the 3-D BRO stage (shuffling between data blocks)                                                                                       |

| Table 5.3: The PSNR and RMSE between the original and reconstructed 8 frames and the maximum absolute error between the 3-D DCT coefficients computed using architectures output and Matlab. |

| Table 5.4: Percentage of hardware usages, maximum operating frequencies and computation times of both models using different wordlengths                                                     |

| Table 5.5: Maximum clock frequency of the proposed and similar architectures 116                                                                                                             |

| Table 5.6: Hardware usage comparison between the 3-D DCT architectures116                                                                                                                    |

| Table 6.1: The difference between the constant and proposed shift-add multipliers126                                                                                                         |

| Table 6.2: The PSNR and the maximum absolute error for the proposed 2-D DWT architecture using 18-bit and 16-bit WL                                                                          |

| Table 6.3: The hardware usage, maximum operating frequencies and computation time for the proposed 2-D DWT architecture using 144×176 and 288×352-pixel at (11, 5) bit wordlength.           |

| Table 6.4: The PSNR, RMSE and average of the maximum error for 3-D DWT coefficients using the proposed architectures for WL=18 (11, 7)-bit                                                   |

| Table 6.5: The PSNR, RMSE and average of the maximum error for 3-D DWT                                                |

|-----------------------------------------------------------------------------------------------------------------------|

| coefficients using the proposed architectures for WL=16 (11, 5)136                                                    |

| Table 6.6: The hardware usage, maximum operating frequencies, throughput and                                          |

| computation time for the proposed 3-D DWT architecture using 144×176 and 256×256                                      |

| image sizes at (11, 5) bit wordlength                                                                                 |

| Table 6.7: Comparison with existing 3-D DWT architectures for an input sequence                                       |

| of $F$ -frames each with $P \times P$ pixels *                                                                        |

| Table 6.8: Comparison between the proposed 3-D DWT and [27, 30, 109] architectures                                    |

| for an input frame size of $144 \times 176$ -pixel for $6VLX760FF1760-2$ Virtex $6Xilinx FPGA$                        |

| Device                                                                                                                |

| Table A.1: Brief description of Xilinx FPGA families introduced since 2003147                                         |

| Table A.2: List of Xilinx FPGA families comparison                                                                    |

| Table C.1: Content of M <sub>1</sub> and M <sub>2</sub> for memory reading addresses for TMem1 (node P <sub>1</sub> ) |

|                                                                                                                       |

| Table C.2: Content of M <sub>1</sub> and M <sub>2</sub> for memory reading addresses for TMem2 (node P <sub>3</sub> ) |

|                                                                                                                       |

| Table C.3: Content of M <sub>1</sub> and M <sub>2</sub> for memory reading addresses for TMem4 (node P <sub>6</sub> ) |

|                                                                                                                       |

# Abbreviations

Accum Accumulators

Adds\_Generator Address Generator

AMBTC Absolute Moment Block Truncation Coding

AQC Adaptive Quantisation Coding

ARM Advanced RISC Machine

ASIC Application Specific Integrated Circuits

bior biorthogonal wavelet

bpp bit per pixel

BRO Bit Reverse Order operation

BTC Block Truncation Coding

BTFL Butterfly

CDF 9/7 Cohen-Daubechies-Feauveau (9/7)

CLB Configurable Logic Block

CMOS Complementary Metal Oxide Semiconductors

CMux Column Multiplexer

Comp Comparator

$C_t$  Computation Time

CT Cosine transform

Ctrl Controller signal

CU Column unit

Daub-4 Daubechies 4-tap filter or CDF 5/3 or LeGall5/3

DCT Discrete Cosine Transform

D-FF D-Flip Flop

DFT Discrete Fourier Transform

DSP Digital Signal Processing

DWT Discrete Wavelet Transform

EBCOT Embedded Block Coding with Optimized Truncation

EDF Error Diffusion

EDK Embedded Development Kit

EZW Embedded Zerotree Wavelet

FF Flip Flop

FIFO First In First Out

FIR Finite Impulse Response

FMux Frame Multiplexer

FPGA Field programmable Gate Arrays

FT Fourier Transform

FU Frame Unit

FWL Floating Wordlength (mantissa part)

GOF Group Of Frames

HLS High Level Synthesis

HPF High Pass Filter

HVS Human Visual System

I/O Input/Output

IBAQC Intensity Based Adaptive Quantisation Coding

IDCT Inverse Discrete Cosine Transform

IHPF Inverse High Pass Filter

ILPF Inverse Low Pass Filter

IP Intellectual Property

ISE Integrated Software Environment

IWL Integer Wordlength

JPEG Joint Photographic Expert Group

Kb Kilo bits

LCD Liquid Crystal Display

LE Logic Element

LPF Low Pass Filter

LSB Least Significant Bit

LUT Look Up Table

MA Multiplier-Adder

Mem\_Enb Memory Enabling

MF Maximum operating Frequency

MHz Mega Hertz

ms millie second

mW millie Watt

MPEG Moving Picture Expert Group

MRC Memory Reading Controller

MRE Memory Reading Enable

MRI Magnetic Resonance Imaging

MSB Most Significant Bit

Multiplier Multiplier

Mux Multiplexer

MWC Memory Writing Controller

NormF Normalisation Factor

PSNR Peak Signal to Noise Ratio

R\_adds Reading address

R\_enb Reading enable

RAM Random Access Memory

RC Row Column

RCF Row Column Frame

RCU Row Column Unit

RISC Reduced Instruction Set Computing

RMSE Root Mean Square Error

ROM Read Only Memory

RTL Register Transfer Level

RU Row Unit

SDP Slice Delay product

SelC Column Selector

SelF Frame Selector

SelR Row Selector

SPECK Set Partitioned Embedded BloCk

SPIHT Set Partitioning In Hierarchical Trees

SR Shift Register

SRL Shift Register LUT

SU Single Unit

SubStg Sub Stage

TF Twiddle Factor

TMem Transpose memory

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

VLSI Very Large Scale Integration

VR Vector Radix

W\_adds Writing address

W\_enb Writing enable

WL WordLength

YC<sub>b</sub>C<sub>r</sub> Luminance-Chrominance colour space

# Chapter 1: Introduction

#### 1.1 Introduction

Transforms, such as the Fast Fourier Transform (FFT), Discrete Cosine Transform (DCT) and Discrete Wavelet Transform (DWT), represent the main part of many audio, image and video processing systems. Although these transforms improve the performance of the entire system, they represent a bottleneck in terms of their computation complexity, storage requirements and subsequent processing speed and power consumption. These issues are crucial in multidimensional applications which require a high computation load and large amount of high speed storage media. As a result of these concerns, the idea and the subject of this thesis arose. This thesis presents new and efficient hardware architectures for low complexity non-transform based image compression algorithms. Furthermore, architectures for the transforms used in transform-based image and video processing systems, such as the DCT and the DWT, are also proposed. In addition, comprehensive analyses are introduced in order to evaluate the performance of the proposed hardware architectures. The performance analysis includes the hardware usage, power consumption, processing speed and output accuracy.

In summary, this chapter introduces: in section 1.2, a general background about digital images and video signals is provided. In section 1.3, an overview of image and video compression algorithms, and their related transforms and architectures are also briefly introduced. The motivation, objectives and contributions of this research are introduced in sections 1.4, 1.5 and 1.6, respectively. The thesis outline is presented in section 1.7 and the outcome publications of this research are outlined in section 1.8.

# 1.2 Digital Image and Video Signals

The data size of any image is related to its bit rate, number of colour bands, and image size, and on the number of images or frames in the case of medical or video streams. Thus, high volume storage devices are required to handle such a large amount of data.

The data storage requirements and bit rate are important factors that affect the complexity of any image and video processing system, particularly in mobile devices. In

such devices, the main challenges are power consumption, hardware usage, storage resources and processing speed. In many image and video applications, the signal bit rate can be adjusted using lossy or lossless compression algorithms. The lossy compression algorithms sacrifice a specific amount of data accuracy to obtain high compression ratios and low bit rates, while in lossless compression algorithms; the decompressed data is exactly the same as the original, though with low compression ratios and high bit rates. For both compression algorithm classes, the computation complexity and storage of intermediate data represent an important factor that contributes to the complexity of the entire system. Thus, work has been conducted to achieve compression algorithms that produce good image quality, a low bit rate and low complexity in terms of storage requirements, high speed, low power consumption and low hardware usage.

# 1.3 An Overview of Image and Video Compression Algorithms

Numerous image and video compression algorithms have been published in the literature. This includes a class of non-transform based low complex algorithms such as Block Truncation Coding (BTC) and Adaptive Quantisation Coding (AQC) [1-5]. Further algorithms are classified as transform-based algorithms, as in the Joint Photographic Experts Group (JPEG) and JPEG2000 image compression standards [6, 7], and MPEGx and H.26x video compression standards [8]. These algorithms offer a good compromise between image quality and the output bit rate, where the bit rate and the output image quality can be adjusted by proper selection of the quality factor. Although the first class of image compression algorithms represents a low complexity and high speed compression systems, the low compression ratio represents its main drawback compared with the second class of algorithms. However, it represents a suitable choice for some applications that require low complexity and low hardware usage [9].

The second class of compression systems encompasses algorithms based on transforms such as the DCT and DWT. This increases the computation complexity, power consumption and hardware usage of such systems. To tackle these issues, many hardware architectures have been published in the literature for 1-D and 2-D DCT, and DWT [10-23], while a limited number of architectures have been suggested for 3-D DCT and DWT applications [22, 24-30]. Nevertheless, the suggested 3-D DCT and 3-D DWT in the literature have only partially met the requirements of hardware architectures such as low power consumption, high processing speed, low hardware

usage and low memory requirements. As such, it is important to produce efficient architectures for the DCT and the DWT which consider such issues for multidimensional applications.

#### 1.4 Research Motivation

The data storage, processing and transmission represent important parts of the major concerns and interest of the modern life. As an example, medical images and the related archiving systems require a high data storage capacity to handle the information of every patient. Additionally, the collected information is usually processed in different ways to prepare it for storage and transmission media to overcome their restrictions and challenge. Considering these points and other concerns, the data compression and the tools required in this field represent the backbone of these applications. However, the data processing is not a straightforward task as it has its own restrictions and challenges. Among these challenges is the computation complexity, processing time, power consumption and storage area. This thesis acts on the previous issues to provide efficient hardware architectures for the data transforms used in image and video compression systems, especially when these issues become crucial in the case of multidimensional signals, such as medical images and video streams.

# 1.5 Research Objectives

The research aims are to introduce new low complexity image compression algorithms, their corresponding architectures and efficient architectures for multidimensional data transforms used in image and video processing systems. The proposed architectures focus on achieving high computation speed, low power consumption and parameterisation for different wordlengths. The objectives of this study can be outlined as follows:

- To present parameterised architectures for low complexity image compression algorithms and multidimensional data transforms.

- To introduce new and efficient 2-D non-transform-based and low complexity image compression algorithms and their hardware architectures for low bit rate applications. The proposed algorithms should consider the intensity variation of image blocks for further bit rate reduction while preserving the output image quality within an acceptable range.

- To design and implement new high speed multidimensional DCT architectures for image and video processing applications. Such architectures can be based on the available low computational complexity fast DCT algorithms.

- To design and implement new low hardware usage architectures for 3-D DCT to achieve a compromise between the hardware usage, processing speed and power consumption for variant wordlengths. The proposed architectures should consider hardware and memory usage reduction by reducing the data transposition throughout the computation process.

- To design and implement new hardware architectures for a lifting-based 1-D, 2-D and 3-D DWT to attain high throughput and low memory requirements for different wordlengths. In such architectures, the main goals are: multiplierless, high throughput, low memory requirements and low power consumption. In such architectures, the power consumption reduction may be achieved by reduce or avoid using the high power consumption elements, such as multipliers.

#### 1.6 Contributions

The contributions of this thesis can be summarised as follows:

- 1. It introduces low complexity non-transform-based image compression algorithms for low bit rate applications. Their new high speed and low hardware usage architectures are also introduced.

- It presents new high speed multidimensional DCT architectures, based on fast DCT algorithms for image and video processing applications.

- It introduces new area efficient architectures for 3-D DCT computation using 3-D DCT VR algorithm.

- 4. It introduces parallel and multiplierless multidimensional DWT architectures to attain a good compromise between memory requirements, processing speed and power consumption.

### 1.7 Thesis Outline

The remainder of this thesis is organised as follows: Chapter 2 is an overview of image and video compression algorithms and their related data transforms, such as the DCT and DWT, which are used in 2-D image and 3-D video and, hyperspectral and medical image processing systems. It also introduces Field Programmable Gate Arrays (FPGA) devices as a medium for hardware implementation. An introduction to hardware design tools and Xilinx high level synthesis design tools is also provided.

In Chapter 3, new non-transform based and low complexity image compression algorithms for low bit rate applications are introduced. These algorithms are based on the AQC algorithm and they consider the intensity variation of each individual image block to introduce low-bit rate and high-performance compression systems. Moreover, new high speed architectures to implement these algorithms are also proposed. Furthermore, a comprehensive analysis of power consumption, speed and hardware resources is also provided.

Two high speed architectures for multidimensional DCT computation are introduced in chapter 4. These architectures are based on 1-D DCT Radix-2 and 3-D DCT VR fast algorithms. The proposed architectures are parameterised in terms of wordlength, which provides different levels of output accuracy, hardware usage and power consumption.

In chapter 5, two new low hardware usage architectures for the 3-D DCT VR algorithm are presented. The main feature of the proposed architectures are; the in place computation of the butterfly and post addition stages without using block memory for data transposition, which in turn produces efficient architectures in terms of hardware usage, processing speed and power consumption.

Multiplierless and parallel lifting-based architectures for the 1-D, 2-D and 3-D Cohen-Daubechies-Feauveau 9/7 (CDF 9/7) DWT are introduced in chapter 6. The proposed architectures represent an efficient low memory requirement, multiplierless and high precision CDF 9/7 DWT systems. In such architectures, the temporal memory for 3-D DWT has been reduced to a block memory size of four frames only. Such block memory is used as a temporary frame buffer during the computation process of the 3-D DWT. Conclusions and the outline for potential future work directions are given in chapter 7.

## 1.8 List of Publications

During the period of PhD research the following publications have been introduced:

- S. Al-Azawi, S. Boussakta, and A. Yakovlev, "Image Compression Algorithms

Using Intensity Based Adaptive Quantisation Coding," American Journal of

Engineering and Applied Sciences, vol. 4, pp. 504-512, 2011.

- S. Al-Azawi, S. Boussakta, and A. Yakovlev, "High precision and low power DCT architectures for image compression applications," in the IET Conference on Image Processing (IPR 2012), 2012, pp. 1-6.

- S. Al-Azawi, S. Boussakta, and A. Yakovlev, "Performance improvement algorithms for colour image compression using DWT and multilevel block truncation coding," in the 7th International Symposium on Communication Systems Networks and Digital Signal Processing (CSNDSP), 2010, pp. 811-815.

- S. Al-Azawi, S. Boussakta, and A. Yakovlev, "Low complexity image compression algorithm using AMBTC and bit plane squeezing," in 7th International Workshop on Systems, Signal Processing and their Applications (WOSSPA), 2011, pp. 131-134.

# Chapter 2: Preliminary Concepts and Related Work

#### 2.1 Introduction

This chapter presents explanatory materials that support the architectures presented in the remainder of the thesis. It is divided into six sections: section 2.2 is an overview of image/video compression algorithms and the associated transforms, including the DCT and DWT. The definitions of rate distortion measurements image fidelity criteria are given in section 2.3. Section 2.4 presents and overview about the related work. Section 2.5 introduces Xilinx FPGA hardware devices which are used as implementation media in the remainder of the thesis, with a particular emphasis on Virtex 5 and 6 Xilinx families given in section 2.6. Hardware design tools are presented in section 2.7. The architectures design procedure is described in 2.8 and the summary is given in section 2.9.

# 2.2 Image and Video Compression Algorithms

The revolution in data transmission and communication systems has made it of paramount importance to compress data (such as images and video) before storing or transmitting it; this is largely due to a limitation in bandwidth, bit rate and storage device size. As an example, a typical 512×512-pixel colour image requires a storage space of 786.432 Kb, if it has a typical bit rate of 8 bit per pixel per colour band (bpp). This number will increase in the case of medical or hyper-spectral images where the bit rate can be 16 or 24 bpp and, thus, in video streams the matter becomes more crucial due to the large number of images/frames and the size of each frame.

The idea of compression comes from reducing the redundancy of data which occurs from different types of correlation, such as correlation between neighbouring pixels in an image or frame, correlation between colour planes in colour images and correlation between pixels in the neighbouring frames. These three types of correlation are known as spatial redundancy, spectral redundancy and temporal redundancy, respectively [31]. These types of redundancies are classified as a statistical redundancy and psycho-visual redundancy. The later refers to the Human Visual System's (HVS) limitations [32]. Some algorithms exploit the spatial redundancy in two dimensional (2-D) image

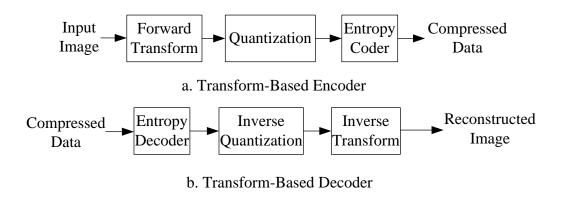

compression systems, while others algorithms exploits both spatial and temporal redundancy, which may be classified as a three dimensional (3-D) compression system. In another aspect, image compression can be classified as a lossless or lossy. The class of lossless compression algorithms ensures that the decompressed image is an exact version of the original image, this result in a low compression ratios or high bit rate. On the other hand, the lossy class of compression algorithms attains high compression ratios, which is nevertheless accompanied by a degradation of the decompressed image quality [33, 34]. JPEG and JPEG2000 image coding standards, as examples of transforms-based compression algorithms. The JPEG image compression standard is based on the DCT [6], and the JPEG2000 is a DWT-based compression system [7]. A typical transform-based compression system is shown in Figure 2.1 [7]. Even though the output performance of the transform-based compression algorithm is high, the computation complexity is their main drawback. The other class of compression algorithms is the low complex and good performance non-transform-based image compression, for which the BTC, multilevel BTC and AQC are well-known algorithms [1-3, 35]. Such algorithms are designed specifically to avoid or reduce computational complexity, memory requirement and processing time arising from applying the DCT or DWT.

Figure 2.1: Basic block diagram of typical transform-based compression / decompression system [36].

#### 2.2.1 Adaptive Quantisation Coding (AQC)

The AQC is a low complex image compression algorithm which represents an improved version of BTC algorithm [2, 35]. The BTC algorithm is used for grey-scale image compression for an output bit rate of two bit per pixel (bpp) and good image quality [1, 3]. The BTC partitions the input image into 4×4-pixel blocks and it computes a bit plane using a bi-level quantiser and two eight bit moments which represents the high and low

mean of the image block. The low compression ratio represents the main drawback of the BTC when compared with other transformed-based image compression techniques. However, it is an attractive option for mobile and low complex applications due to its simplicity and good image quality [37]. Many researchers have tried to enhance the performance and to reduce the bit rate of BTC algorithm as stated in [4, 31, 37-42]. In [37] a three level quantiser was used to classify the pixels into low, intermediate and high intensity, according to a predefined threshold. Accordingly, the AQC algorithm partitions the input image into a fixed size blocks and it encodes the input image using a multilevel quantised bit plane, the minimum intensity value of the block and the quantiser step [4, 5]. Thus, the AQC can be considered as a multi-level BTC algorithm and the coding performance of the AQC algorithm is much better than the BTC but it comes in the expenses of higher bit rate. However, the bit rate remains the same for both algorithms for low intensity variation images. Thus, the AQC algorithm produces good compromises between coding performance and computation complexity. The efficient coding performance and low implementation cost of multilevel BTC and AQC algorithms have encouraged some researchers to use them as a suitable approach for memory usage reduction in Liquid Crystal Display (LCD) overdrive [5, 43-46] and in data hiding applications [3, 47-49].

#### 2.2.2 Discrete Cosine Transform (DCT)

The DCT has gained a wide acceptance within the signal processing community since it was suggested in 1974 [50]. This is due to its energy compaction, orthogonal and performance level being close to that of Karhunen-Loeve transform with respect to the rate distortion criterion [50]. It has become an essential part of many image and video applications, including the JPEG, MPEGx and H.26x compression standards [6, 8, 51-53]. With DCT-based audio, image and video compression systems, the input signal is partitioned into N,  $N \times N$ -point data blocks or  $N \times N \times N$ -point data cubes, and then transformed into DCT domain using 1-D, 2-D and 3-D DCT transforms, respectively.

The 1-D DCT for N-point data can be computed as follows [16]:

$$X(k) = \frac{2\varepsilon}{N} \sum_{n=0}^{N-1} x(n) \times \cos\left(\frac{\pi}{2N} (2n+1)k\right)$$

(2.1)

where

$$k = 0, 1, 2, ..., N - 1$$

,  $n = 0, 1, 2, ..., N - 1$  and  $\varepsilon = \begin{cases} \frac{1}{\sqrt{2}}, & \text{for } k = 0 \\ 1, & \text{otherwise} \end{cases}$

The inverse 1-D DCT (1-D IDCT) is defined as:

$$x(n) = \sum_{k=0}^{N-1} \varepsilon \times X(k) \times \cos\left(\frac{\pi}{2N}(2n+1)k\right)$$

(2.2)

The 2-D DCT of a  $N \times N$ -point data block can be computed by computing the 1-D DCT on the rows and columns successively. Alternatively, the 2-D DCT can be computed directly as [12]:

$$X(k_1, k_2) = \frac{\varepsilon_{k_1} \varepsilon_{k_2}}{N} \sum_{n_1 = 0}^{N-1} \sum_{n_2 = 0}^{N-1} x(n_1, n_2) \times \cos\left(\frac{\pi}{2N} (2n_1 + 1)k_1\right) \times \cos\left(\frac{\pi}{2N} (2n_2 + 1)k_2\right)$$

(2.3)

and the 2-D IDCT is computed as:

$$x(n_1, n_2) = \frac{2}{N} \sum_{k_1=0}^{N-1} \sum_{k_2=0}^{N-1} \varepsilon_{k_1} \varepsilon_{k_2} X(k_1, k_2) \times \cos\left(\frac{\pi}{2N} (2n_1 + 1)k_1\right) \times \cos\left(\frac{\pi}{2N} (2n_2 + 1)k_2\right)$$

(2.4)

where

$$k_1, k_2, n_1$$

and  $n_2 = 0, 1, 2, \dots, N-1$  and  $\varepsilon_{k_1}$  and  $\varepsilon_{k_2} = \begin{cases} \frac{1}{\sqrt{2}}, & for \ k_i = 0\\ 1, & otherwise \end{cases}$

The 3-D DCT for an  $N \times N \times N$ -point data cube can be computed as follows [54]:

$$X(k_{1}, k_{2}, k_{3}) = \frac{8\varepsilon_{k_{1}}\varepsilon_{k_{2}}\varepsilon_{k_{3}}}{N^{3}} \sum_{n_{1}=0}^{N-1} \sum_{n_{2}=0}^{N-1} \sum_{n_{3}=0}^{N-1} x(n_{1}, n_{2}, n_{3})$$

$$\times \cos\left(\frac{\pi}{2N}(2n_{1}+1)k_{1}\right) \times \cos\left(\frac{\pi}{2N}(2n_{2}+1)k_{2}\right)$$

$$\times \cos\left(\frac{\pi}{2N}(2n_{3}+1)k_{3}\right)$$

(2.5)

and the 3-D IDCT is given by [54]:

$$x(n_1, n_2, n_3) = \sum_{k_1=0}^{N-1} \sum_{k_2=0}^{N-1} \sum_{k_3=0}^{N-1} \varepsilon_{k_1} \varepsilon_{k_2} \varepsilon_{k_3} X(k_1, k_2, k_3) \times \cos\left(\frac{\pi}{2N} (2n_1 + 1)k_1\right) \times \cos\left(\frac{\pi}{2N} (2n_2 + 1)k_2\right) \times \cos\left(\frac{\pi}{2N} (2n_3 + 1)k_3\right)$$

(2.6)

where

$$k_i$$

and  $n_i=0,1,2\ldots,N-1, i=1,2,3$  and  $\varepsilon_{k_i}=\begin{cases} \frac{1}{\sqrt{2}}, & for \ k_i=0\\ 1, & otherwise \end{cases}$

Further, the 3-D DCT can also be computed by applying *N*-point 1-D DCT using (2.1) on the rows then columns and the temporal or frames direction successively. This is termed the Row-Column-Frame (RCF).

It is obvious from (2.1) to (2.6) that the computation complexity of the DCT increases rapidly with the data dimensionality. As an example, the computation complexity of  $N \times N \times N$ -point data cube using an RCF approach requires  $3N^2$  1-D DCT, where each 1-D DCT requires  $N^2$  multiplication and N(N-1) addition operations. Nevertheless, the computation complexity of the 3-D DCT can be reduced using fast DCT algorithms. A number of fast DCT algorithms have been published in the literature, among them the 1-D Radix-2 algorithm [55] and 3-D DCT Vector Radix algorithm (3-D DCT VR) [54]. These fast algorithms reduce the mathematical operations involved in the computation of the DCT, thus, achieving shorter processing times. In addition they also reduce the memory space required for data transpose for both 2-D and 3-D DCT.

The arithmetic operations for the original RCF 3-D DCT, RCF 3-D DCT Radix-2 and 3-D DCT VR algorithms are shown in Table 2.1 [54, 56, 57]. It is obvious from Table 2.1 that the number of multiplications in a 3-D DCT VR algorithm is less than that required by a 3-D DCT Radix-2 algorithm by  $\frac{5}{9}N^3log_2N$ .

Table 2.1: The arithmetic operations of the original RCF 3-D DCT, RCF Radix-2 and VR algorithms [54, 56, 57].

| Operations     | Original RCF<br>3-D DCT | RCF using<br>1-D DCT Radix-2         | 3-D DCT VR                           |

|----------------|-------------------------|--------------------------------------|--------------------------------------|

| Multiplication | $3N^4$                  | $\frac{3}{2}N^3log_2N$               | $\frac{7}{8}N^3log_2N$               |

| Addition       | $3N^3(N-1)$             | $\frac{9}{2}N^3log_2N - 3N^3 + 3N^2$ | $\frac{9}{2}N^3log_2N - 3N^3 + 3N^2$ |

#### 2.2.2.1 DCT-Based Compression Systems

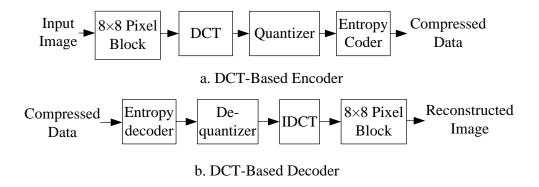

A conventional DCT-based image compression system encompasses of: DCT, quantisation and encoding, as shown in Figure 2.2 [6].

Figure 2.2: DCT based image compression/decompression system [36].

As shown in Figure 2.2, each 2-D input image is partitioned into fixed block sizes (typically 8×8-pixel), and then the DCT is applied to tackle the spatial correlation in the block. Furthermore, the quantisation and entropy coding are used to reduce the bit rate further.

In 3-D signals, such as videos and 3-D medical images, the spatial correlation between pixels can be reduced using the 2-D DCT, while the motion compensation process used to tackle the correlation between frames (temporal correlation). This makes the 3-D video compression systems, such as in MPEGx and H.26x standards, consist of 2-D compression system with a motion compensation unit. However, the high computation complexity of motion compensation makes it is difficult to get a real time 3-D compression system without using efficient hardware accelerators. Further, the motion estimation is computed with respect to a reference frame within a group of frames; this dependency can cause accumulated and propagated error throughout each group of frames [58, 59]. The computation complexity of the conventional 3-D images and videos has increased the need for new low complex compression system, particularly in mobile and wireless communication systems [58]. New approaches have been proposed in the literature that considers video data as a 3-D data volume. The correlation at the temporal direction is tackled by applying 1-D DCT along the third dimension while spatial data redundancy is considered using the 2-D DCT; this has led to new video and 3-D image compression systems using the 3-D DCT [24, 54, 59-63]. Such a transform is particularly suited for embedded systems requiring low complexity implementation of both video encoder and decoder, such as the case of mobile terminals with videocommunication capabilities [24].

#### 2.2.2.2 3-D DCT Applications

The 3-D DCT is used for different applications, such as 3-D video compression, hyper spectral image compression and watermarking [64-68]. In [64], an approach based on a JPEG lossy image compression system and a 3-D DCT for still image compression was introduced. The proposed system constructs an 8×8×8-pixel 3-D data cubes from the original 2-D image data using a spiral scanning. Such technique utilises a new quantisation table to improve the coding performance. It has been found that the performance of the proposed technique outperformed the conventional JPEG compression, especially at low and high bit rates in particular [64]. Furthermore, the 3-D DCT has been used to exploit the spatio-temporal redundancy in video watermarking [65-67] and hyper spectral image compression [68]. Other applications of 3-D DCT algorithms include object tracking [69], stereoscopic video quality assessment [70], 3-D video de-noising [71] and lip reading [72].

#### 2.2.3 Discrete Wavelet Transform (DWT)

The DWT [73] is used in different image and video applications, such as compression, watermarking and denoising. Similar to the DCT, the DWT exhibits a high rate of energy compaction, thus making it a good choice in compression standards. Moreover, the DWT in image compression algorithms has the property to overcome the blocking artifact that characterise the DCT-based or block-based image compression techniques. Nevertheless, the DWT affected by its high computation complexity and memory requirements compared to the DCT or other block-based algorithms. Such requirements are dependent on the wavelet filter length and the size of input data.

Various low and high pass wavelet filters are used in DWT applications. The simplest wavelet filter is the Haar wavelet filter, which has the following coefficients for decomposition and reconstruction operations, respectively.

LPF=

$$[0.707 \ 0.707]$$

and HPF= $[-0.707 \ 0.707]$  (2.7)

where LPF and HPF are the Low and High Pass Filter, respectively. The coefficients of Haar reconstruction filter are shown below:

ILPF=

$$[0.707 \ 0.707]$$

and IHPF= $[0.707 \ -0.707]$  (2.8)

where ILPF and IHPF are the Inverse Low and High Pass Filter, respectively.

Further, more sophisticated wavelets filters are available, which they are different in terms of output performance, filter order and computation complexity. As an example of these filters are Cohen-Daubechies-Feauveau 9/7 (CDF 9/7) and Le Gall 5/3 which are used in JPEG2000 lossy and lossless compression standards, respectively. The coefficients of both filters are shown in Table 2.2 [32, 74]. Moreover, there are infinite number of possible wavelet filters, such as Daubechies and Coiflets families, and the selection of the best wavelet filter depends on the required application [75, 76].

Table 2.2: CDF 9/7 and Le Gall 5/3 analysis filters coefficients [32, 74].

|    | CDF 9/7   |           | Le Gall 5/3 |          |  |

|----|-----------|-----------|-------------|----------|--|

|    | LPF       | HPF       | LPF         | HPF      |  |

| 0  | 0.852699  | 0.788486  | 1.060660    | 0.707107 |  |

| ±1 | 0.377402  | 0.418092  | 0.353553    | 0.353553 |  |

| ±2 | -0.110624 | -0.040689 | -0.176777   |          |  |

| ±3 | -0.023849 | -0.064539 |             |          |  |

| ±4 | 0.037828  |           |             |          |  |

#### 2.2.3.1 DWT Decomposition Operations

The DWT decomposition operation consists of two steps namely; filtering and decimation (down sampling by 2). This operation is reversed at the decoder side in the reconstruction operations. It acts to reverse the decomposition operations using inverse wavelet filters and up sampling by 2. The filtering operation is accomplished by applying a sequence of low and high pass filters. The DWT decomposition and down sampling operation for a 1-D input signal can be expressed by the following two equations [77]:

$$Y_{Low}(n) = \sum_{k=-\infty}^{\infty} g(k-2n) x(k)$$

$$Y_{High}(n) = \sum_{k=-\infty}^{\infty} h(k-2n) x(k)$$

(2.9)

Where x(k) represents the input signal and  $Y_{Low}(n)$  and  $Y_{High}(n)$  are the low and high output bands, and g and h represent the impulse response of DWT low and high pass

filters, respectively. Further, the reconstruction operations can be carried out as follows [77]:

$$x(k) = \sum_{n=-\infty}^{\infty} g'(k-2n) Y_{Low}(n) + \sum_{n=-\infty}^{\infty} h'(k-2n) Y_{High}(n)$$

(2.10)

where g' and h' represent the impulse response of the inverse DWT (IDWT) low and high pass filters, respectively.

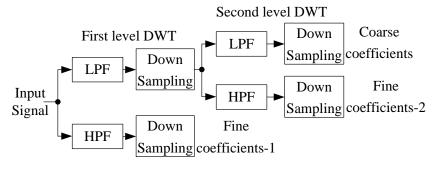

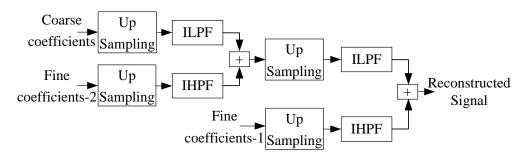

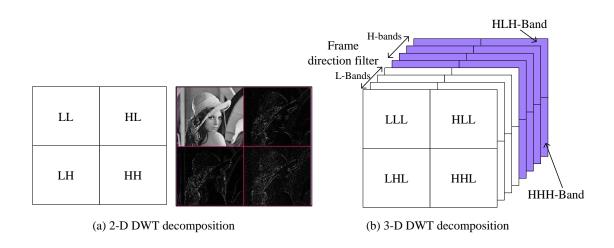

The decomposition and reconstruction proposes can be repeated L times, where  $L = log_2 P$ , P is the input data length and L is the number of decomposition levels, which leads to a multilevel 1-D DWT decomposition and reconstruction as shown in Figure 2.3. This figure shows that both directions (decomposition and reconstruction) consist of a set of low and high pass filters with down sampling step in the decomposition and an up sampling step for reconstruction. Furthermore, in Figure 2.3 the upper output represents the coarse components while the fine components of the original signal are represented in the lower part. The coarse part contains the shape of the signal or image decimated by the number of wavelet levels. It results from applying a sequence of low pass filters only. The fine parts are the output that results from a combination of high and low pass filters or high pass filters only. Furthermore, in multidimensional signals such as 2-D images and video sequences, the DWT can be computed using separable technique by applying 1-D DWT on each dimension, successively. Thus, the 2-D DWT can be computed by applying (2.9) on the rows and columns and on frames in the case of 3-D DWT. Further, 2-D and 3-D DWT can be computed using non-separable technique by applying 2-D and 3-D wavelet filters on the input data. Therefore, for the 2-D DWT, four output bands are computed for each decomposition level, namely: LL, HL, LH and HH bands, where: L and H stand for 1-D Low and High pass filters, respectively. Similarly, the output arising from 3-D DWT is 8-band signal. These bands are: LLL, HLL, LHL, HHL, LLH, HLH, LHH and HHH. As a result of the filtering operations, H bands contain the fine components and the L band contains the coarse components in 2-D and 3-D DWT. The output bands for one level 2-D and 3-D DWT decomposition are shown in Figure 2.4.

a. Two levels forward 1-D DWT

b. Two levels inverse 1-D DWT

Figure 2.3: Typical two levels 1-D DWT: a. Decomposition b. Reconstruction

Figure 2.4: One level 2-D and 3-D DWT decomposition.

The convention-based 1-D DWT computation of any 1-D signal can be obtained by two convolution steps using low and high pass filters and down sampling by 2. The convolution operation produces two sub-bands, low and high frequency; each one contains half the number of the original input samples [78]. Thus, the DWT

decomposition and down sampling operation for a 1-D input signal is computed using (2.9) and the reconstruction operations can be performed using (2.10) [77, 79].

The preceding computation procedure produces wavelet coefficients for 1-D signals, and moreover, the wavelet coefficients of 2-D and 3-D signals can be computed by applying 1-D DWT along each signal dimension, separable approach [78]. Additionally, as the convolution-based DWT computation approaches require high computation loads, a new algorithm was introduced in [80], which has been named the lifting scheme or lifting-based DWT computation method. The lifting scheme has been considered as an efficient approach for DWT computation. The computation load of the convolution-based DWT has been reduced by up to 50% using the lifting-based DWT scheme [81].

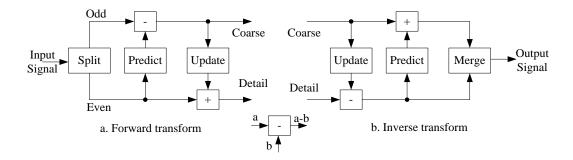

The lifting scheme partitions the wavelet filter into a sequence of triangular matrices. Such an approach is called lifting-based DWT. The lifting scheme is composed of a sequence of prediction and updating steps as shown in Figure 2.5. The most important features of this scheme can be summarised as follows [81]:

- 1. Faster than the ordinary convolution-DWT approaches.

- 2. Low memory requirement.

- 3. The computation of each lifting step can be implemented in parallel.

Figure 2.5: Lifting scheme (a) decomposition (b) reconstruction.

Further, the computational complexity of lifting-based CDF 9/7 DWT is shown in Table 2.3. The number of operations is computed according to the original structure of the CDF 9/7 1-D DWT lifting scheme. In this table, 3N multiplication and 4N-4 addition operations are required to compute the 1-D CDF 9/7 wavelet filter for N-sample using lifting scheme. In addition, 2N 1-D DWT is required to compute the 2-D

DWT for  $N \times N$ -point data block using the RC approach while,  $3N^2$  1-D DWT is required in the case of the RCF 3-D DWT.

Table 2.3: The arithmetic operations of the lifting-based 1-D, 2-D and 3-D CDF 9/7 wavelet filter.

| Operations     | 1-D        | 2-D      | 3-D                     |  |

|----------------|------------|----------|-------------------------|--|

| Multiplication | 3 <i>N</i> | $6N^2$   | 9 <i>N</i> <sup>3</sup> |  |

| Addition       | 4N - 4     | 2N(4N-4) | $3N^2(4N-4)$            |  |

### 2.2.3.2 DWT Applications

The JPEG2000 image compression standard is one of the most important applications of 2-D DWT [7, 82]. Further, the multidimensional DWT is used in hyperspectral image compression [32], 3-D integral images compression [83], medical image compression [26, 84-86] and image watermarking [87]. The 3-D DWT is used in video, medical and remote sensing imaging (multispectral images) compression systems, and such an example is the 3-D SPECK [32]. Furthermore, various other wavelet-based image compression algorithms have been published in the literature. Among them the Embedded Zerotree Wavelet (EZW), Set Partitioning In Hierarchical Trees (SPIHT), Set Partitioned Embedded BloCK coder (SPECK), Embedded Block Coding with Optimized Truncation (EBCOT)[32].

### 2.3 Rate Distortion Measurements

Image and video quality is an important factor in different applications. Thus, the output accuracy through this thesis is computed and considered carefully using the well-known rate distortion measurement criteria. The Root Mean Square Error (RMSE) and Peak Signal to Noise Ratio (PSNR) have been used as objective fidelity criteria. The RMSE and PSNR (dB) between the original and the reconstructed images or frames can be computed as follows:

$$RMSE = \sqrt{\frac{1}{PQ} \sum_{i=1}^{Q} \sum_{j=1}^{P} (I_{in}(i,j) - I_{out}(i,j))^{2}}$$

(2.11)

$$RMSE = \sqrt{\frac{1}{PQF} \sum_{i=1}^{Q} \sum_{j=1}^{P} \sum_{k=1}^{F} (I_{in}(i,j,k) - I_{out}(i,j,k))^{2}}$$

(2.12)

$$PSNR = 10log_{10} \left( \frac{\left( max(I_{in}) \right)^2}{(RMSE)^2} \right)$$

(2.13)

where, P and Q are the image/frame dimensions, F is the number of images or frames,  $I_{in}(i,j)$  and  $I_{out}(i,j)$  is the original and reconstructed images, respectively.  $Max(I_{in})$  is typically equal to 255.

### 2.4 Related work

The related work section has been divided into three sub-sections to summarise the previous work about the AQC, DCT and DWT algorithms and architectures.

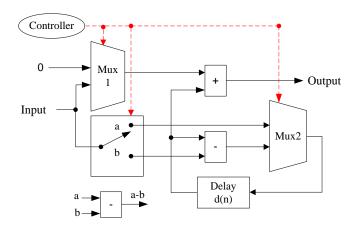

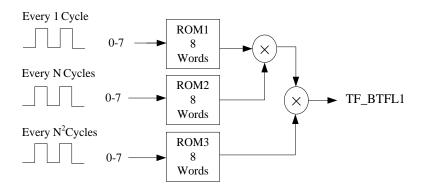

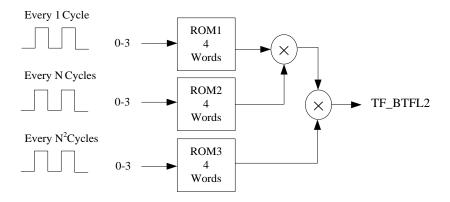

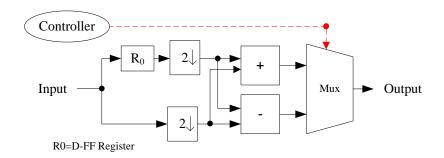

### 2.4.1 AQC Related Work