## High Gain Non-isolated DC-DC Converter Topologies for Energy Conversion Systems

Musbahu Muhammad B.Eng., M. Eng.

A thesis submitted for the degree of Doctor of Philosophy

February, 2017

School of Electrical Electronic Engineering

Newcastle University

United Kingdom

### **Abstract**

Emerging applications driven by low voltage level power sources, such as photovoltaics, batteries and fuel cells require static power converters for appropriate energy conversion and conditioning to supply the requirements of the load system. Increasingly, for applications such as grid connected inverters, uninterruptible power supplies (UPS), and electric vehicles (EV), the performance of a high efficiency high static gain power converter is of critical importance to the overall system. Theoretically, the conventional boost and buck-boost converters are the simplest non-isolated topologies for voltage step-up. However, these converters typically operate under extreme duty ratio, and severe output diode reverse recovery related losses to achieve high voltage gain. This thesis presents derivation, analysis and design issues of advanced high step-up topologies with coupled inductor and voltage gain extension cell. The proposed innovative solution can achieve significant performance improvement compared to the recently proposed state of the art topologies.

Two unique topologies employing coupled inductor and voltage gain extension cell are proposed. Power converters utilising coupled inductors traditionally require a clamp circuit to limit the switch voltage excursion. Firstly, a simple low-cost, high step-up converters employing active and passive clamp scheme is proposed. Performance comparison of the clamps circuits shows that the active clamp solution can achieve higher efficiency over the passive solution. Secondly, the primary detriment of increasing the power level of a coupled inductor based converters is high current ripple due to coupled inductor operation. It is normal to interleaved DC-DC converters to share the input current, minimize the current ripple and increase the power density. This thesis presents an input parallel output series converter integrating coupled inductors and switched capacitor demonstrating high static gain. Steady state analysis of the converter is presented to determine the power flow equations. Dynamic analysis is performed to design a closed loop controller to regulate the output voltage of the interleaved converter. The design procedure of the high step-up converters is explained, simulation and experimental results of the laboratory prototypes are presented. The experimental results obtained via a 250 W single phase converter and that of a 500 W interleaved converter prototypes; validate both the theory and operational characteristics of each power converter.

i

## **Acknowledgements**

First and foremost, all praise is due to Allah (God), who gives me the wisdom, health and patience to complete this work.

It is a pleasure always to thank the many people who have made this research work and thesis possible. The author would like to thank the Petroleum Technology Development Fund (PTDF) Nigeria; this work would not have been carried out without their funding. I would like to thank them for their financial support and the invaluable PhD Scholarship award.

I acknowledge wholeheartedly with deepest appreciation the outstanding guidance, intellectual support and encouragement provided by my supervisors, Dr Matthew Armstrong and Dr Mohammed Ali Elgendy. The successful completion of this work would not have been possible without their indefatigable patience and persistence in keeping us on schedule. I am extremely grateful for having the privilege to work with Dr Matthew Armstrong and learn from his expertise. What I learned from him is beyond just solving the research problems. He has always been and would be an inspiration to me.

Many thanks are also due to the academic and technical support staff within the school; Jack, Allan and Chris in helping with the construction of the equipment for performing the experimental work. I would like to acknowledge the support of Darren Mackie throughout the project and printed circuit board (PCB) design. Special thanks go to James Richardson and Gordon for their valuable help and guidance. Thanks to the Postgraduate Research Coordinator Gillian Webber and the remaining administrative staff for their assistance.

I am also indebted to my colleagues in the UG lab (Electrical Power Group). It has been an exciting and great pleasure to work with creative, dedicated and talented colleagues. We had many interesting discussions during the past years, and I will always remember the time we spent together and the friendship.

My heartfelt appreciation goes to my mum for her moral support and encouragement throughout my life and further education. I would like to thank my family members and relatives who have inspired and continued to motivate me. Finally, I would like to appreciate the endless support I received from my family, especially my wife for her encouragement, prayer and understanding in this research work and future endeavour.

Finally, I am grateful to my children, Fatima, Khadija and Muhammad. They have been behind me throughout this research work. I would like to thank them for their patience during the moments when they needed me most and the research work keeps me away from them.

## **Contents**

| Abstract                                       | i   |

|------------------------------------------------|-----|

| Acknowledgements                               | ii  |

| Contents                                       | iv  |

| Figures                                        | xi  |

| Tables                                         | xv  |

| Symbols                                        | xvi |

| Chapter 1 Introduction                         | 1   |

| 1.1 Background                                 | 1   |

| 1.2 High Step-up DC-DC Converters Applications | 3   |

| 1.2.1 Grid Connected Photovoltaic Inverter     | 3   |

| 1.2.2 High Intensity Discharge (HID) Lamp      | 5   |

| 1.2.3 Electric Vehicle                         | 5   |

| 1.2.4 Uninterruptible Power Supply UPS         | 6   |

| 1.2.5 Telecommunication Power System           | 7   |

| 1.2.6 Distributed Power system                 | 7   |

| 1.3 Characteristics of High Step-up Converters | 8   |

| 1.3.1 High Conversion Ratio                    | 8   |

| 1.3.2 High-Efficiency                          | 9   |

| 1.3.3 Low Voltage/Current Ripple               | 9   |

| 1.3.4 Fast Response                            | 9   |

| 1.4 Motivation                                 | 9   |

| 1.5 Aim and Objectives                         | 10  |

| 1.6 Thesis layout                              | 11  |

| 1.7 Research Impact                            | 13  |

|   | 1.8 Publications Arising from this Research                               | 13 |

|---|---------------------------------------------------------------------------|----|

|   | 1.9 Summary                                                               | 14 |

| C | Chapter 2 High Step-up DC-DC Conversion Techniques -A Literature Review   | 15 |

|   | 2.1 Introduction                                                          | 15 |

|   | 2.2 DC-DC Boost Converter                                                 | 16 |

|   | 2.2.1 General Structure of DC-DC Boost Converters                         | 16 |

|   | 2.2.2 Isolated DC-DC Boost Converters                                     | 17 |

|   | 2.2.3 Non-isolated DC- DC Boost Converter                                 | 18 |

|   | 2.2.4 Conventional Non-isolated DC-DC Boost Converter                     | 18 |

|   | 2.2.5 Limitations of Conventional Converters in High step-up Applications | 19 |

|   | 2.3 Topology Evaluation for High step-up DC-DC Boost Converter            | 20 |

|   | 2.3.1 Cascade Converter                                                   | 20 |

|   | 2.3.2 Quadratic Boost Converter                                           | 21 |

|   | 2.3.3 Three Level Boost Converter                                         | 21 |

|   | 2.3.4 Voltage Multiplier Cell                                             | 22 |

|   | 2.3.5 Switched Capacitor/Switched Inductor Techniques                     | 23 |

|   | 2.3.6 Voltage Lift Circuit                                                | 25 |

|   | 2.3.7 Active Network                                                      | 26 |

|   | 2.3.8 Transformer Based DC-DC Converters                                  | 27 |

|   | 2.3.9 Stacked DC-DC Converters                                            | 28 |

|   | 2.3.10 Integrated Converters                                              | 29 |

|   | 2.4 High Step-up DC-DC Converters Platforms                               | 31 |

|   | 2.5 Classification of Non-isolated DC-DC Boost Converters                 | 32 |

|   | 2.5.1 Step-up Converters without Wide Voltage gain                        | 32 |

|   | 2.5.2 Step-up Converters with Wide Voltage gain                           | 33 |

|   | 2.6 High Switching Frequency Operation                                    | 33 |

|   | 2.7 Soft Switching Performance in High Sten-up Converters                 | 35 |

|   | 2.7.1 Zero Voltage Switching (ZVS) Technique                     | 36 |

|---|------------------------------------------------------------------|----|

|   | 2.7.2 Zero Current Switching (ZCS) Technique                     | 36 |

|   | 2.7.3 Voltage Clamping                                           | 37 |

|   | 2.8 Reverse Recovery Characteristic of Output Diode              | 37 |

|   | 2.9 Summary                                                      | 38 |

| C | hapter 3 Single phase Converter Steady State Analysis and Design | 40 |

|   | 3.1 Introduction                                                 | 40 |

|   | 3.2 Proposed Converter and Operational Principle                 | 41 |

|   | 3.2.1 Circuit Configuration and Description                      | 41 |

|   | 3.2.2 Converter Principle of Operation                           | 42 |

|   | 3.3 Steady State Performance Analysis                            | 46 |

|   | 3.3.1 Voltage Gain                                               | 46 |

|   | 3.3.2 Voltage Stress Analysis                                    | 49 |

|   | 3.3.3 Current Stress Analysis                                    | 50 |

|   | 3.3.4 (ZVS) Soft Switching Performance                           | 52 |

|   | 3.4 Performance Comparison                                       | 54 |

|   | 3.5 Design Consideration                                         | 56 |

|   | 3.5.1 Coupled Inductor Turns Ratio Design                        | 56 |

|   | 3.5.2 Leakage Inductance Design                                  | 56 |

|   | 3.5.3 Magnetizing Inductor Design.                               | 56 |

|   | 3.5.4 Magnetic Core Selection                                    | 57 |

|   | 3.5.5 Clamp Capacitor Design                                     | 57 |

|   | 3.5.6 Switched Capacitor Design                                  | 58 |

|   | 3.5.7 Output Capacitor Design                                    | 59 |

|   | 3.5.8 Power Device Selection                                     | 59 |

|   | 3.5.9 Time Sequence Design                                       | 59 |

|   | 3.6 Simulation Results                                           | 60 |

| 3.7 Experimental Verification                                            | 62 |

|--------------------------------------------------------------------------|----|

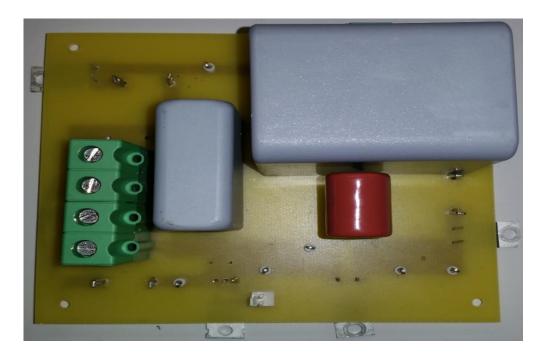

| 3.7.1 High Step-up Active Clamp Boost Converter Prototype                | 62 |

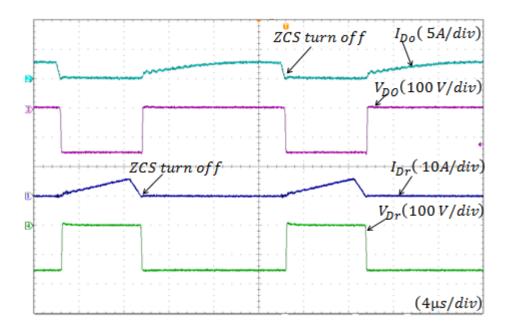

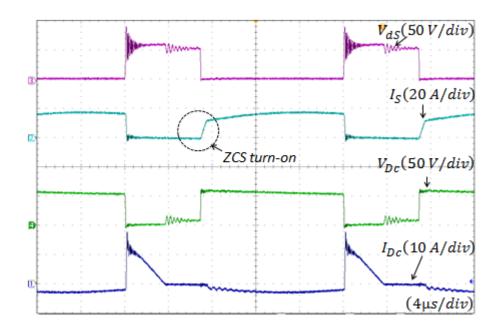

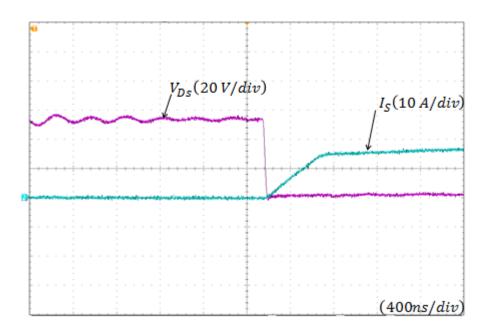

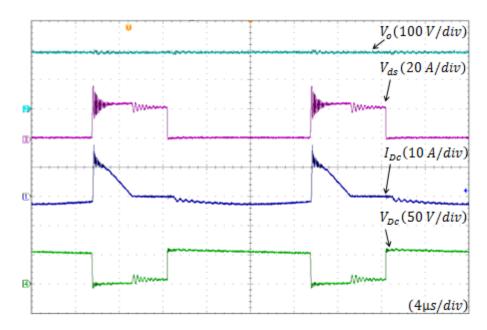

| 3.7.2 Measured Experimental Waveforms                                    | 63 |

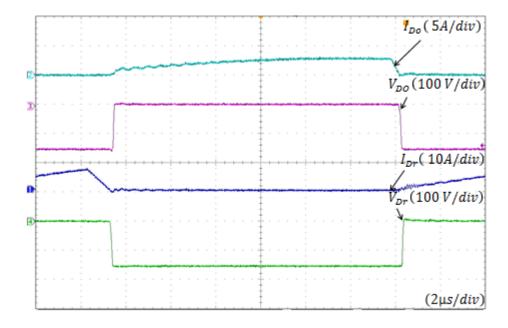

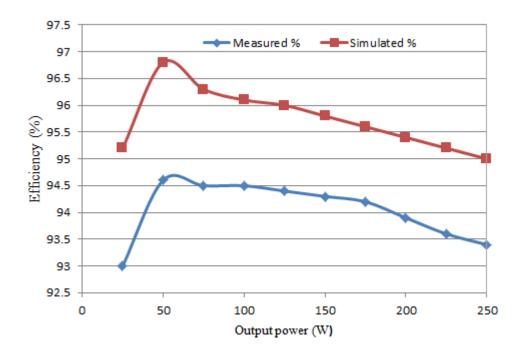

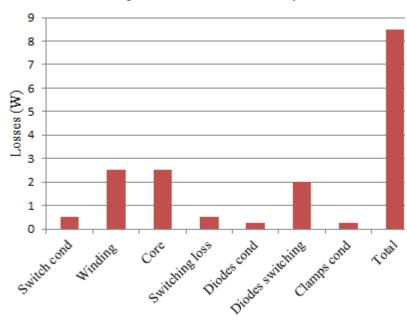

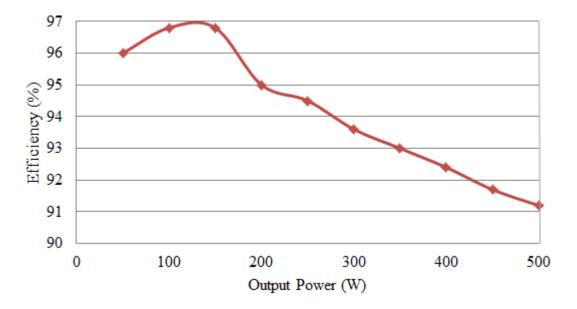

| 3.8 Efficiency Measurement and Power Loss Analysis                       | 69 |

| 3.9 Summary                                                              | 70 |

| Chapter 4 Utilization of Passive Clamp Circuit in High Step-up Converter | 71 |

| 4.1 Introduction                                                         | 71 |

| 4.2 Converter Operational Analysis                                       | 72 |

| 4.2.1 Circuit Description                                                | 72 |

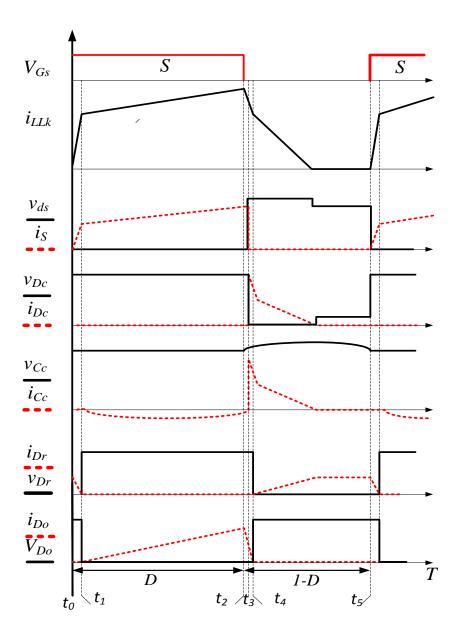

| 4.2.2 Modes of Operation                                                 | 73 |

| 4.3 Steady State Converter Analysis                                      | 77 |

| 4.3.1 Voltage Conversion Ratio                                           | 77 |

| 4.3.2 Power Devices Voltage Stress                                       | 79 |

| 4.3.3 Current Stress                                                     | 80 |

| 4.3.4 Diodes Reverse Recovery Alleviation                                | 80 |

| 4.4 Circuit Design                                                       | 81 |

| 4.5 Simulation Verification                                              | 81 |

| 4.6 Experimental Validation                                              | 83 |

| 4.6.1 High Step-up Passive Clamp Boost Converter Prototype               | 83 |

| 4.6.2 Experimental Results                                               | 84 |

| 4.7 Performance Comparison                                               | 88 |

| 4.8 Topologies Comparison                                                | 89 |

| 4.8.1 Power Devices Voltage Stress                                       | 89 |

| 4.8.2 Current Stress                                                     | 90 |

| 4.8.3 Clamp Circuits Performance                                         | 91 |

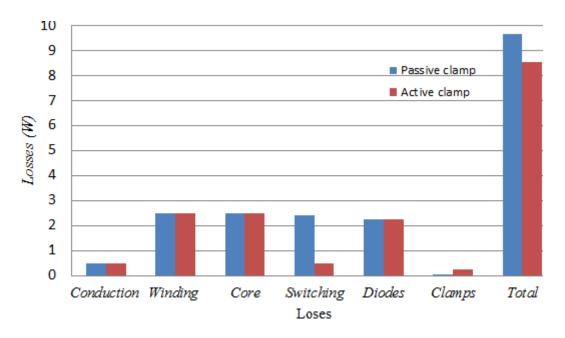

| 4.8.4 Loss Break down Comparison                                         | 93 |

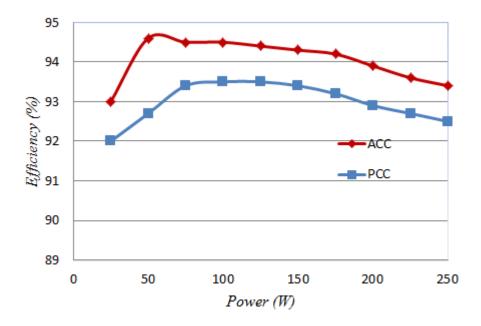

| 4.8.5 Efficiency                                                         | 93 |

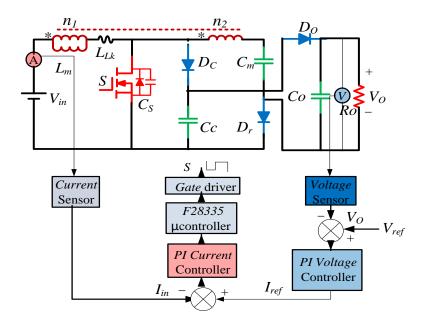

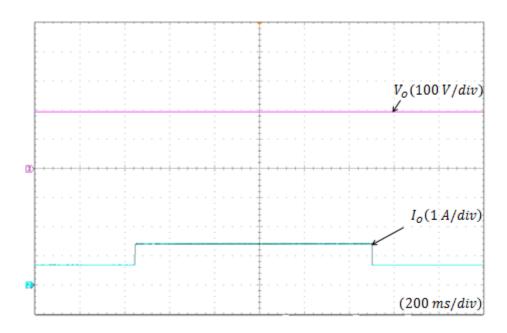

|   | 4.9 Closed Loop Response                                         | 94    |

|---|------------------------------------------------------------------|-------|

|   | 4.10 Summary                                                     | 96    |

| C | Chapter 5 Interleaved High Step-up Converter Analysis and Design | 98    |

|   | 5.1 Introduction                                                 | 98    |

|   | 5.2 Interleaved High Step-up Converter Overview                  | 99    |

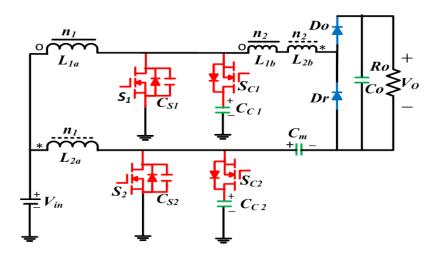

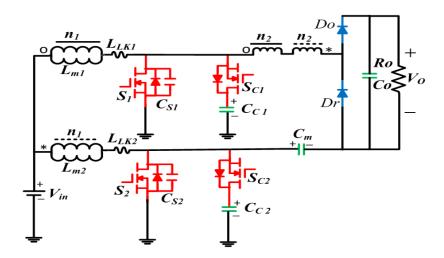

|   | 5.2.1 Circuit Topology Description                               | 99    |

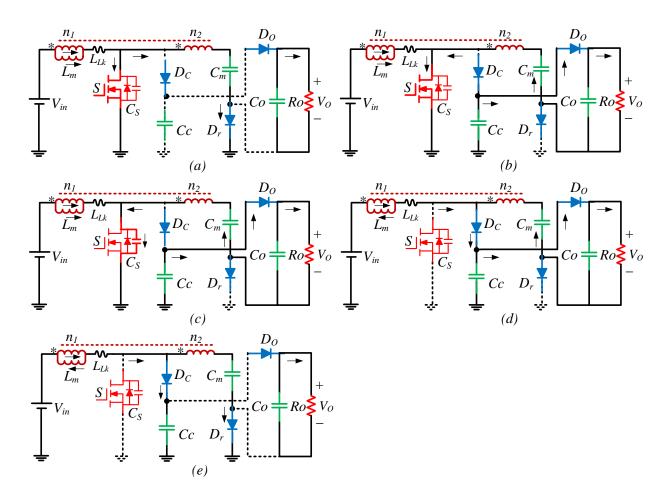

|   | 5.2.2 Circuit Operational Principle                              | . 100 |

|   | 5.3 Interleaved Converter Steady State Analysis                  | . 106 |

|   | 5.3.1 Static Gain                                                | . 106 |

|   | 5.3.2 Power Semiconductors Voltage Stress                        | . 109 |

|   | 5.3.3 Current Stress Analysis                                    | . 109 |

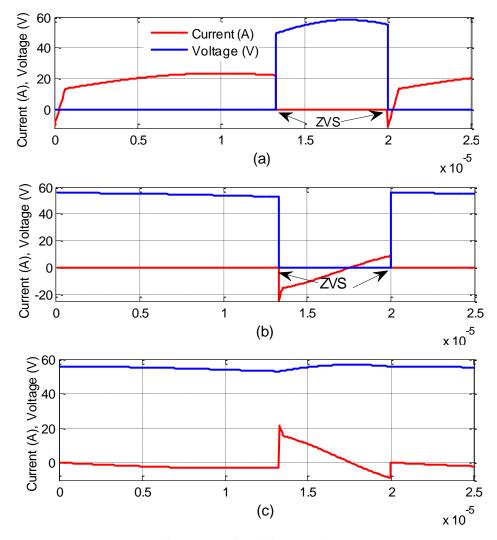

|   | 5.3.4 (ZVS) Soft Switching performance                           | . 110 |

|   | 5.4 Design Procedure                                             | . 111 |

|   | 5.4.1 Coupled Inductor Turns Ratio Design                        | . 111 |

|   | 5.4.2 Leakage Inductance Design                                  | . 111 |

|   | 5.4.3 Magnetizing Inductor Design                                | . 112 |

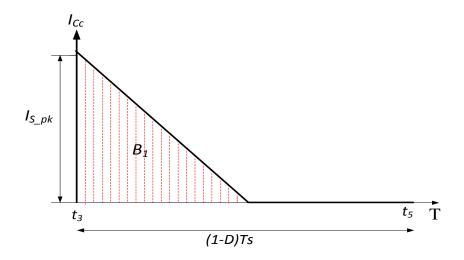

|   | 5.4.4 Clamp Capacitor Design                                     | . 112 |

|   | 5.4.5 Switched Capacitor Design                                  | . 113 |

|   | 5.4.6 Output Capacitor Design                                    | . 114 |

|   | 5.4.7 Dead Time design                                           | . 114 |

|   | 5.5 Simulation                                                   | . 115 |

|   | 5.6 Experimental Validation                                      | . 118 |

|   | 5.6.1 High Step-up Interleaved Boost Converter Prototype         | . 118 |

|   | 5.6.2 Measured Experimental Waveforms                            | . 119 |

|   | 5.7 Measured Efficiency                                          | . 123 |

|   | 5.8 Summary                                                      | . 124 |

|   | Chapter 6 Small Signal Modelling and Stability Analysis          | . 126 |

| 6.1 Introduction                                                  | 126 |

|-------------------------------------------------------------------|-----|

| 6.2 Modelling Assumptions                                         | 127 |

| 6.3 Small Signal Analysis Using State space Averaging             | 128 |

| 6.3.1 Interleaved Converter Model                                 | 128 |

| 6.3.2 Averaging                                                   | 128 |

| 6.3.3 Steady State                                                | 129 |

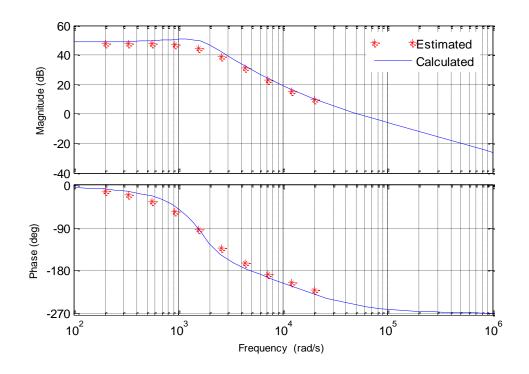

| 6.3.4 Model Transfer Function                                     | 130 |

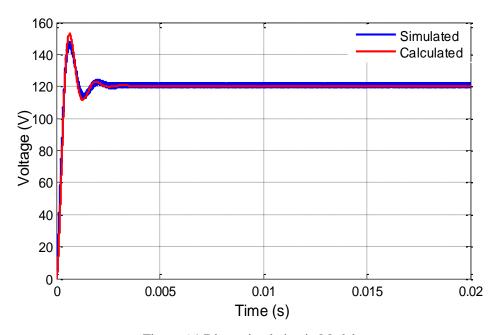

| 6.3.5 Model Validation with Simulink                              | 131 |

| 6.3.6 Perturbation                                                | 132 |

| 6.3.7 Linearization                                               | 132 |

| 6.3.8 Transfer function                                           | 133 |

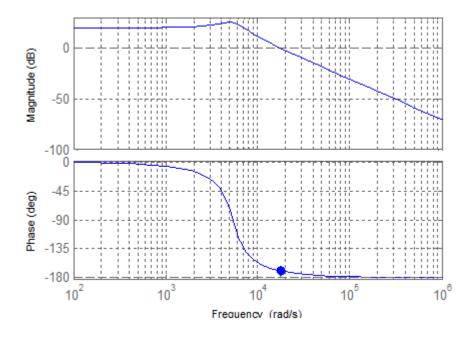

| 6.3.9 Duty Ratio Control                                          | 134 |

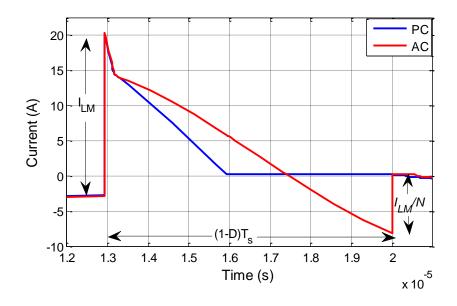

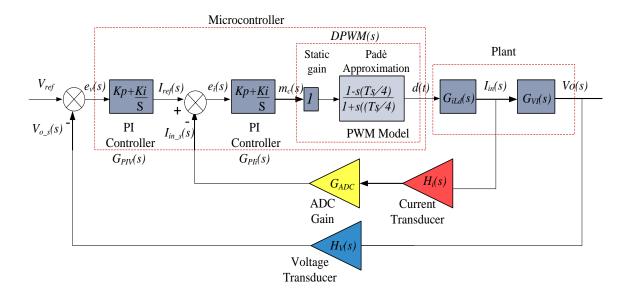

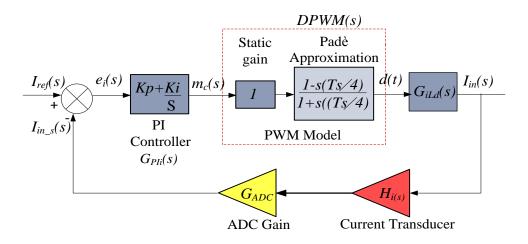

| 6.4 Current Mode Control                                          | 137 |

| 6.4.1 Inner Current Control Loop                                  | 138 |

| 6.4.2 Outer Voltage Control Loop                                  | 142 |

| 6.1 Simulation and Experimental Results                           | 144 |

| 6.2 Manual Tuning of Discrete PI Controller                       | 146 |

| 6.3 Summary                                                       | 148 |

| Chapter 7 Conclusion and Further Work                             | 149 |

| 7.1 Introduction                                                  | 149 |

| 7.2 Single Phase High Step-up Converter                           | 151 |

| 7.3 Interleaved High Step-up Converter                            | 152 |

| 7.4 Further Work                                                  | 153 |

| Appendix A Simulink Model of the Proposed High Step-up Converters | 155 |

| A.1 Introduction                                                  | 155 |

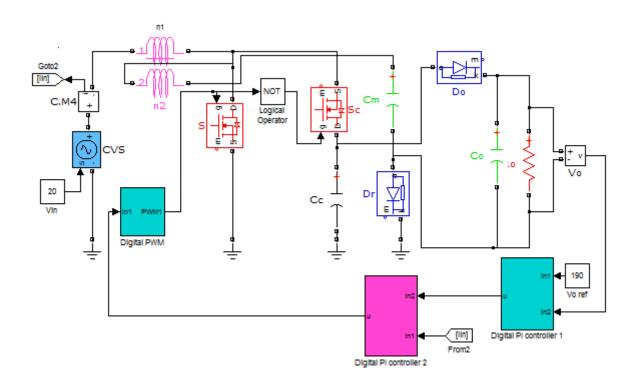

| A.2 Single Phase Active Clamp Converter Simulink Model            | 155 |

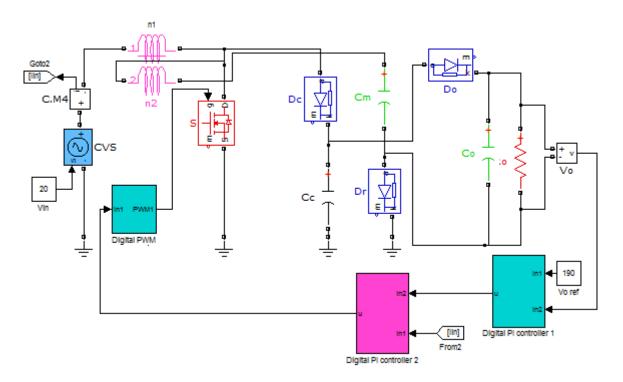

| A.3 Single Phase Passive Clamp Converter Simulink Model           | 156 |

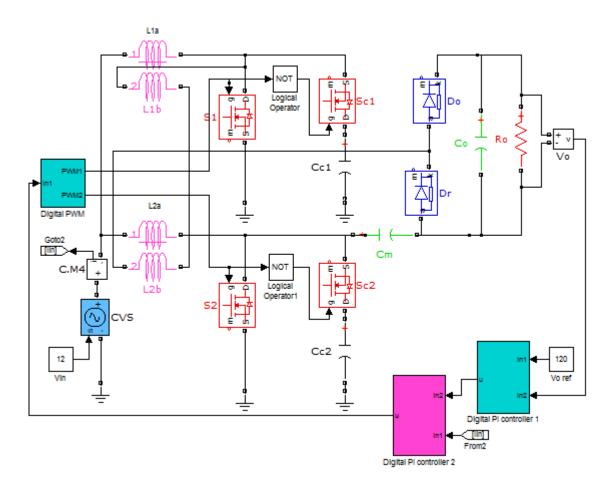

| A.4        | Interleaved Active Clamp Converter Simulink Model         | 156 |

|------------|-----------------------------------------------------------|-----|

| Appen      | dix B High Step-up Converters Hardware                    | 158 |

| B.1        | Introduction                                              | 158 |

| B.2        | Single Phase Active Clamp High Step-up Converter Circuit  | 158 |

| B.3        | Single Phase Passive Clamp High Step-up Converter Circuit | 159 |

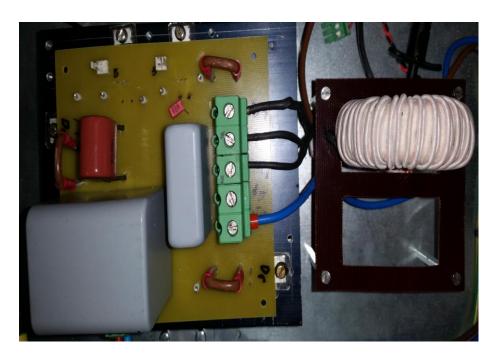

| B.4        | Interleaved Converter                                     | 159 |

| Appen      | dix C Controller Overview                                 | 161 |

| C.1        | Introduction                                              | 161 |

| C.2        | Digital Signal Processor (DSP) Board                      | 161 |

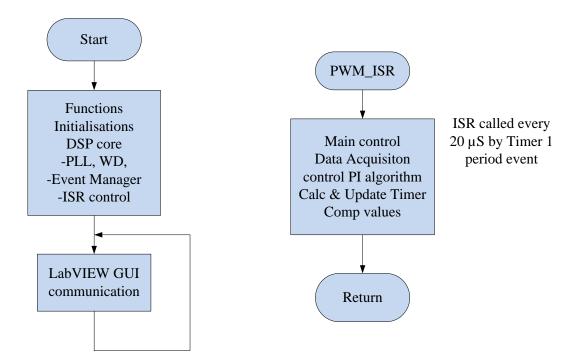

| C.3        | Software Implementation                                   | 162 |

| Appen      | dix D Gate Drives and Sensors Interface Board             | 164 |

| D.1        | Introduction                                              | 164 |

| D.2        | Gate Drive Interface                                      | 164 |

| D.3        | Sensor Interface                                          | 165 |

| Appen      | dix E Power Loss Analysis and Efficiency                  | 166 |

| E.1        | Introduction                                              | 166 |

| E.2        | Switch Conduction Loss                                    | 166 |

| E.3        | Switching Loss                                            | 166 |

| E.4        | Diode Conduction and Switching Losses                     | 167 |

| E.5        | Coupled Inductor Copper and Core Loss                     | 167 |

| E.6        | Theoretical Efficiency                                    | 168 |

| References |                                                           | 169 |

## **Figures**

| Figure 1.1 Single phase grid connected renewable energy system                 | 4  |

|--------------------------------------------------------------------------------|----|

| Figure 1.2 High Intensity discharge lamp ballast block diagram                 | 5  |

| Figure 1.3 Electric vehicle drive train                                        | 6  |

| Figure 1.4 Dual front end telecom power system                                 | 7  |

| Figure 1.5 Distributed power system                                            | 8  |

| Figure 2.1 Boost converter unidirectional power flow                           | 16 |

| Figure 2.2 Flyback converter                                                   | 18 |

| Figure 2.3 Conventional boost Converter                                        | 19 |

| Figure 2.4 Cascade boost converter                                             | 20 |

| Figure 2.5 Quadratic boost converter                                           | 21 |

| Figure 2.6 Three level boost converter                                         | 22 |

| Figure 2.7 Boost converter with voltage multiplier cell                        | 23 |

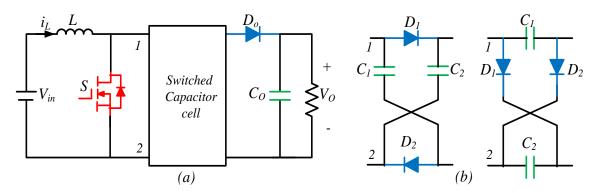

| Figure 2.8 Switched capacitor structure                                        | 24 |

| Figure 2.9 Switched inductor structure                                         | 25 |

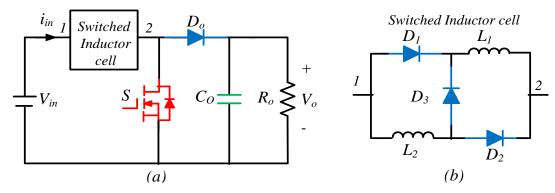

| Figure 2.10 Voltage lift converter                                             | 25 |

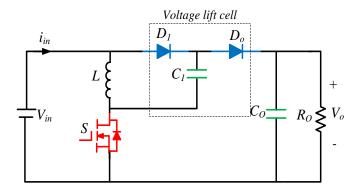

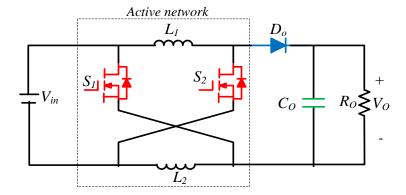

| Figure 2.11 Active network converter                                           | 26 |

| Figure 2.12 Non-isolated stacked converter structure [82]                      | 28 |

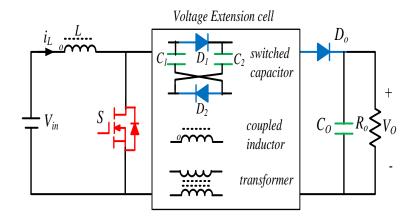

| Figure 2.13 Typical circuit for high step-up dc-dc conversion                  | 32 |

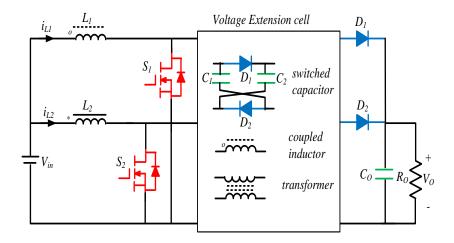

| Figure 2.14 Typical circuit for interleaved high step-up dc-dc conversion      | 32 |

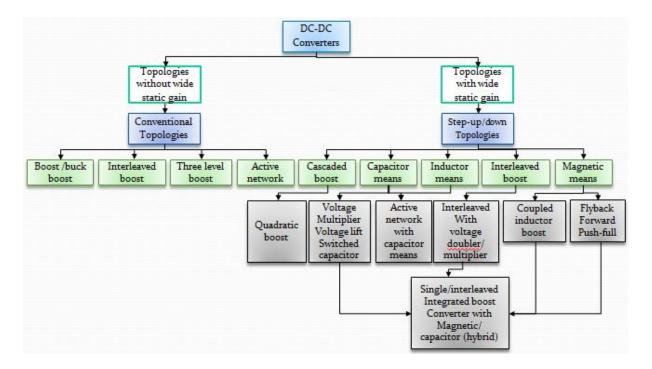

| Figure 2.15 Classification of step-up converters                               | 33 |

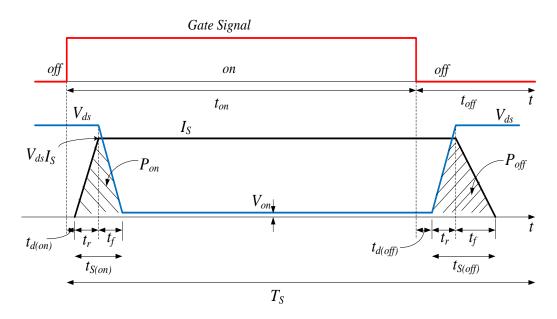

| Figure 2.16 Typical linearized switching trajectory of power device            | 34 |

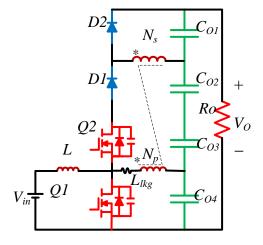

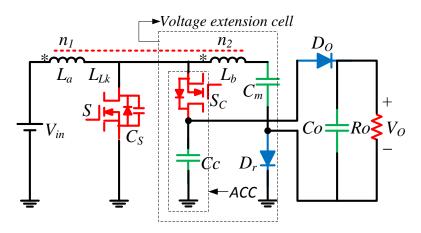

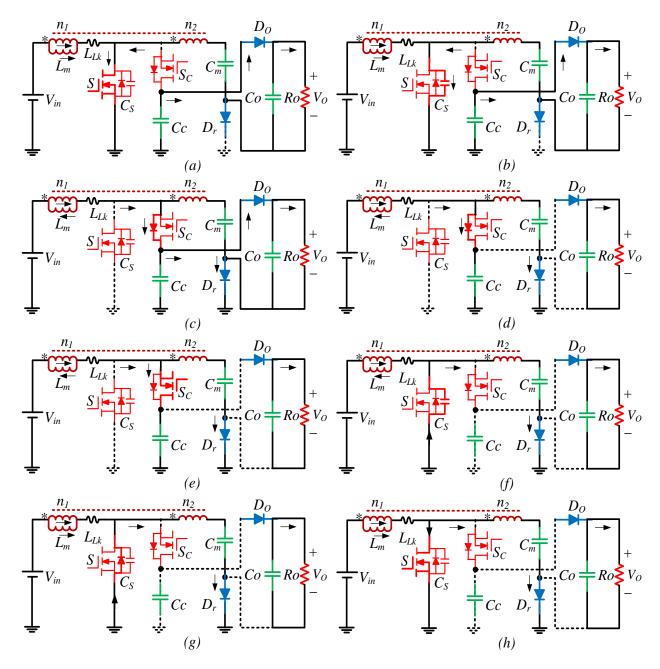

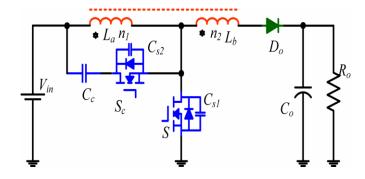

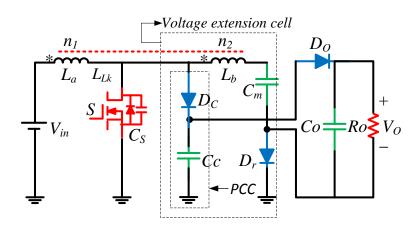

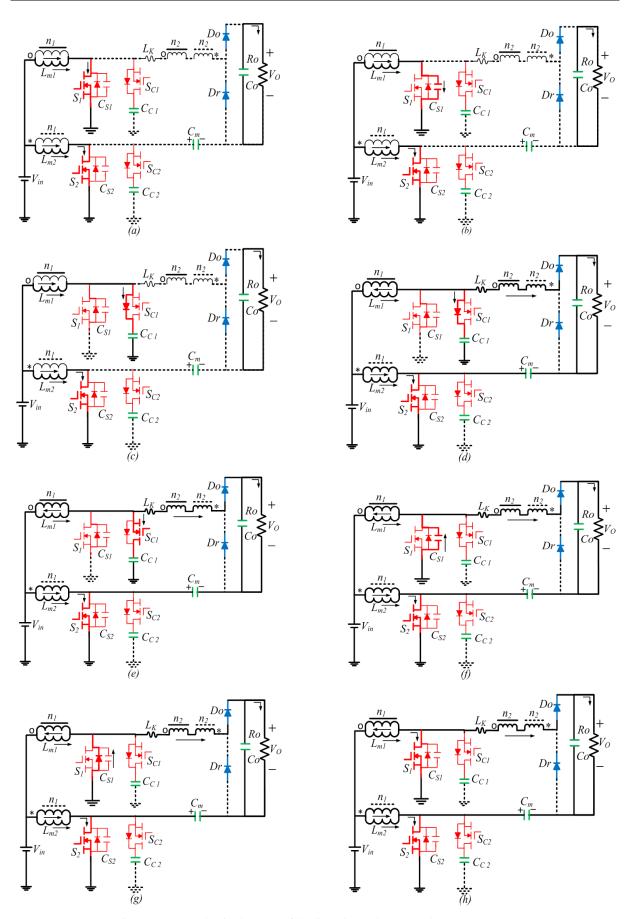

| Figure 3.1 Circuit configuration of the proposed converter                     | 41 |

| Figure 3.2 Equivalent circuit of the high step-up boost converter              | 42 |

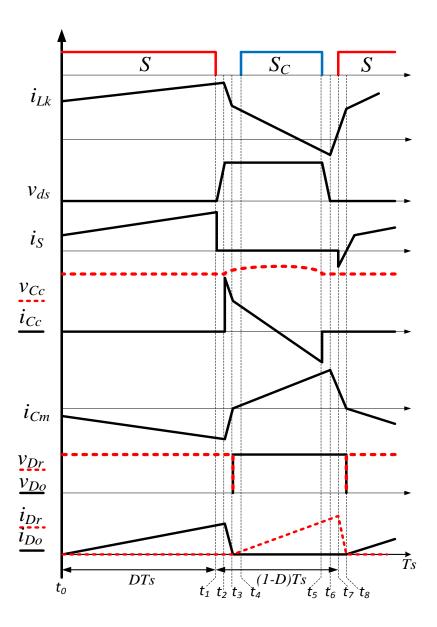

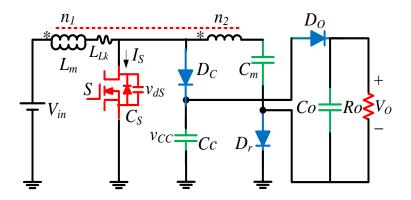

| Figure 3.3 Steady state theoretical waveforms                                  | 43 |

| Figure 3.4 Operational stages equivalent circuits                              | 44 |

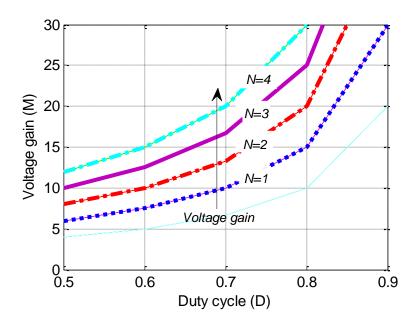

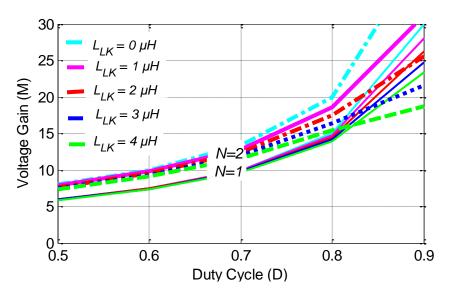

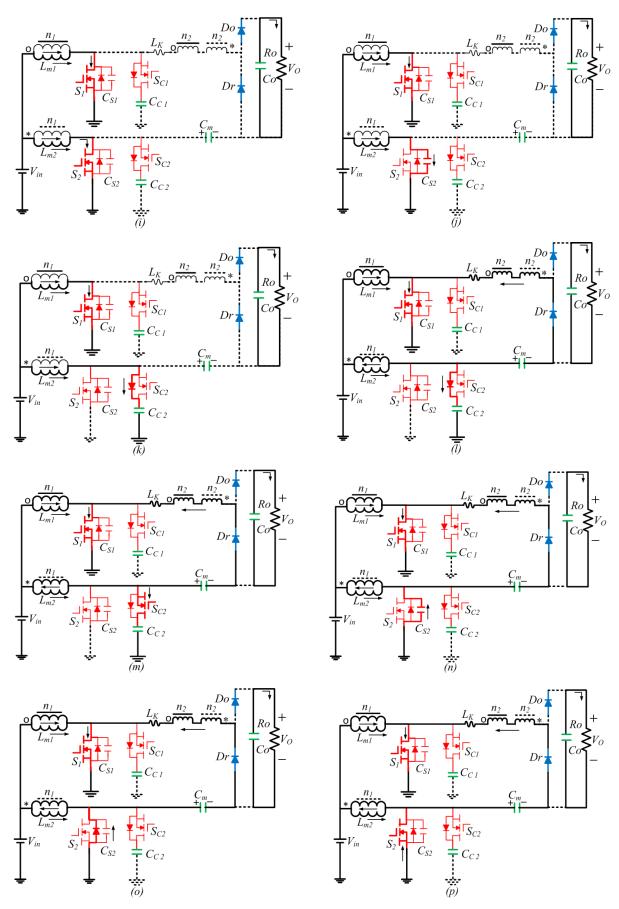

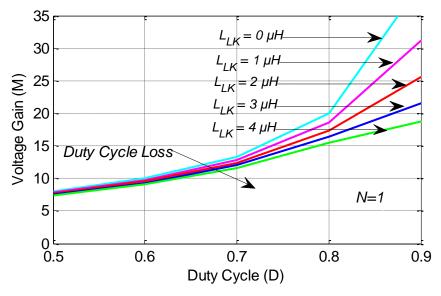

| Figure 3.5 Ideal voltage gain characteristic for various D and N values        | 47 |

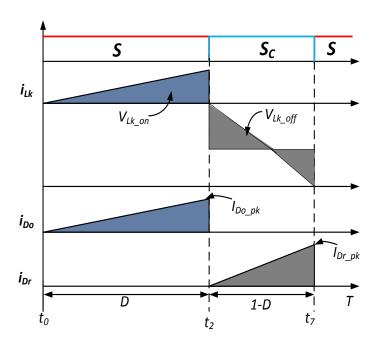

| Figure 3.6 Simplified waveform for voltage gain derivation                     | 48 |

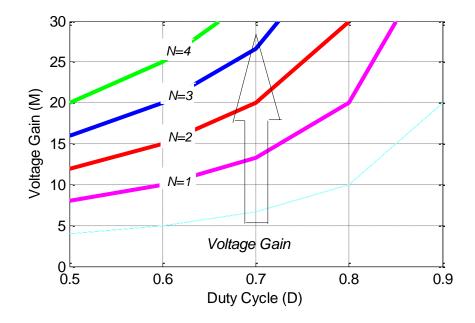

| Figure 3.7 Voltage gain characteristic of the converter for various $Q$ values | 49 |

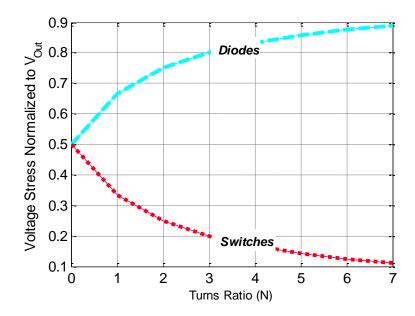

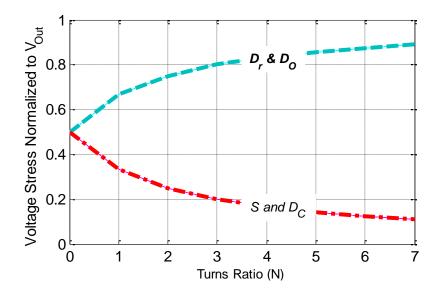

| Figure 3.8 Normalized semiconductors voltage stress as function of turns ratio | 50 |

| Figure 3.9 Simplified converter waveforms for current stress analysis          | 51 |

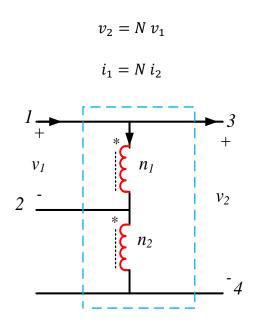

| Figure 3.10 Current and voltage relationship of a non-isolated transformer [92]         | 53     |

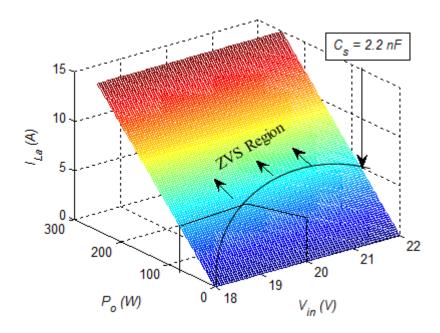

|-----------------------------------------------------------------------------------------|--------|

| Figure 3.11 ZVS boundary of main switch as a function of input voltage and output power | er. 54 |

| Figure 3.12 Buck-boost active clamp converter [73]Error! Bookmark not def               | ined.  |

| Figure 3.13 Active clamp coupled inductor boost converter [48]                          | 55     |

| Figure 3.14 Voltage and current waveform of switched capacitor                          | 58     |

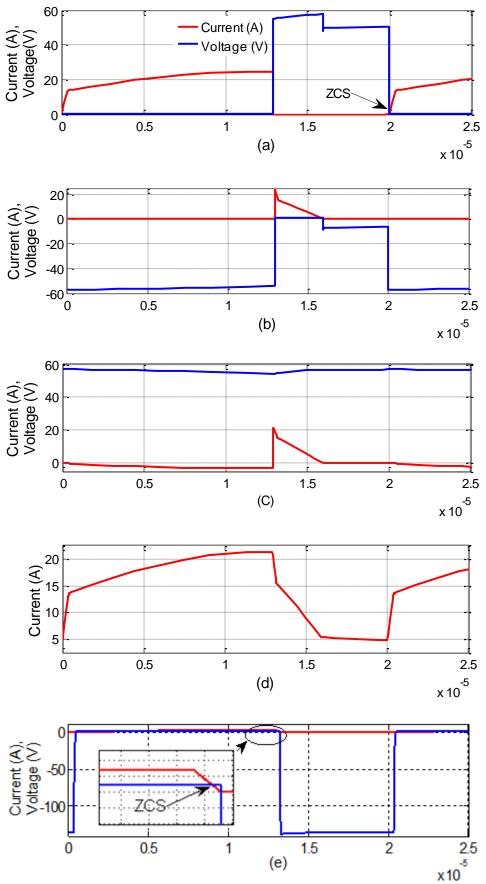

| Figure 3.15 (Continuation) Simulation results                                           | 62     |

| Figure 3.16 Photograph of the experimental prototype                                    | 63     |

| Figure 3.17 Complimentary gate signals of the main switch and clamp switch              | 64     |

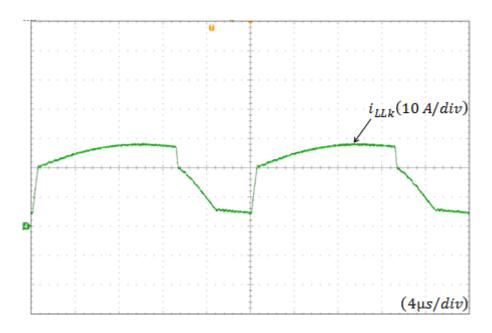

| Figure 3.18 Leakage inductor current waveform                                           | 64     |

| Figure 3.19 Main and clamp switch current and voltage waveforms                         | 65     |

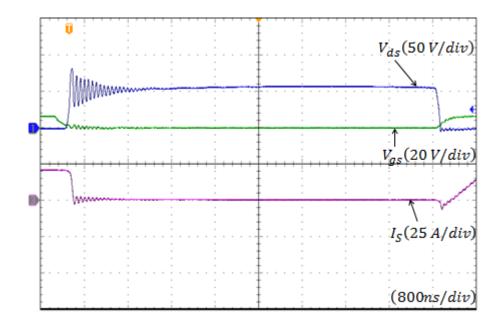

| Figure 3.20 (ZVS) details of main switch                                                | 66     |

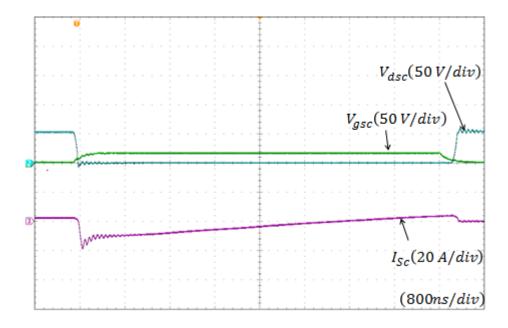

| Figure 3.21 (ZVS) details of clamp switch                                               | 66     |

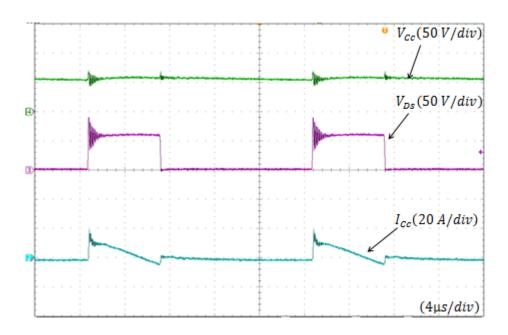

| Figure 3.22 Clamp circuit performance                                                   | 67     |

| Figure 3.23 Diodes voltage and current waveforms                                        | 68     |

| Figure 3.24 Close up of diodes (ZCS) turn off and reverse recovery alleviation          | 68     |

| Figure 3.25 Measured Efficiency                                                         | 69     |

| Figure 3.26 Converter loss distribution                                                 | 69     |

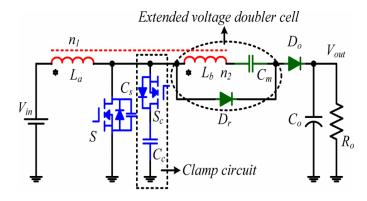

| Figure 4.1 Single phase non-isolated DC-DC boost converter with passive clamp           | 72     |

| Figure 4.2 Equivalent circuit of the high step-up boost converter                       | 73     |

| Figure 4.3 Some typical steady state waveforms in CCM operation                         | 74     |

| Figure 4.4 Operational modes equivalent circuits showing current flow path              | 75     |

| Figure 4.5 Voltage conversion ratio as a function of <i>D</i> and <i>N</i> values       | 78     |

| Figure 4.6 Semiconductors devices voltage stress reduction effect                       | 79     |

| Figure 4.7 (Continued) Simulation results                                               | 83     |

| Figure 4.8 Photograph of the experimental prototype                                     | 83     |

| Figure 4.9 Main switch and clamp diode current and voltage waveforms                    | 84     |

| Figure 4.10 (ZCS) turn on detail of the main switch                                     | 85     |

| Figure 4.11 Passive clamp circuit performance                                           | 85     |

| Figure 4.12 Clamp Capacitor current and voltage waveforms                               | 86     |

| Figure 4.13 Capacitors voltage stress                                                   | 86     |

| Figure 4.14 Diodes measured current and voltage waveforms                               | 87     |

| Figure 4.15 Diodes (ZCS) turn off and reverse recovery alleviation                      | 87     |

| Figure 4.16 leakage inductor current waveform                                           | 88     |

| Figure 4.17 Typical active clamp circuit current waveform                               | 91     |

| Figure 4.18 Passive clamp circuit current waveform                                     | 92      |

|----------------------------------------------------------------------------------------|---------|

| Figure 4.19 Simulated clamp circuits behaviour                                         | 92      |

| Figure 4.20 Loss breakdown comparison                                                  | 93      |

| Figure 4.21 Efficiency curves                                                          | 94      |

| Figure 4.22 Control architecture                                                       | 95      |

| Figure 4.23 Step change in load from half load to full load and vice versa             | 95      |

| Figure 4.24 Load change from full load to no load and back to full load                | 96      |

| Figure 5.1 Circuit diagram of the interleaved non-isolated DC-DC boost converter       | 99      |

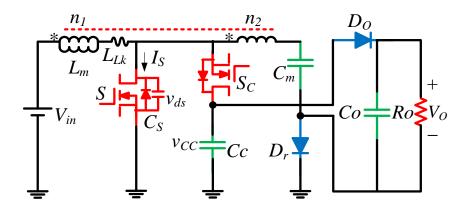

| Figure 5.2 Equivalent circuit of the interleaved DC-DC boost converter                 | 100     |

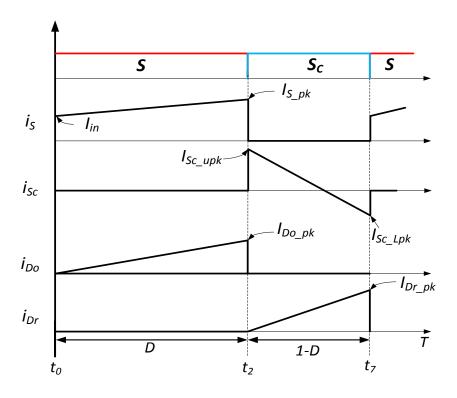

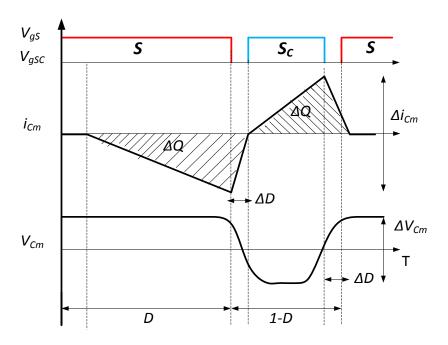

| Figure 5.3 key steady state waveforms                                                  | 101     |

| Figure 5.4 (Continued) Topological states of the interleaved DC-DC boost converter     | 103     |

| Figure 5.5 Voltage gain characteristic of the converter for various $D$ and $N$ values | 107     |

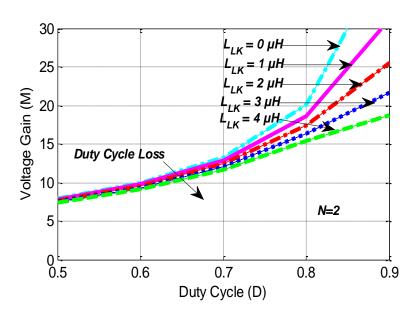

| Figure 5.6 Voltage gain characteristic of the converter                                | 109     |

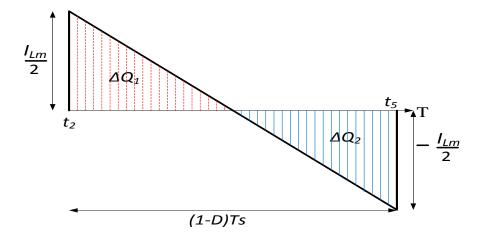

| Figure 5.7 Clamp capacitor current waveform                                            | 112     |

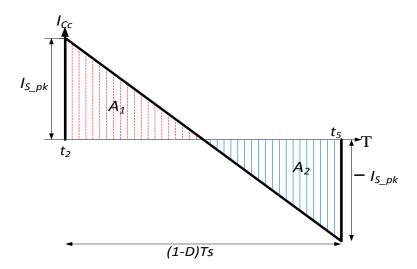

| Figure 5.8 Simplified voltage and current waveform of switched capacitor               | 113     |

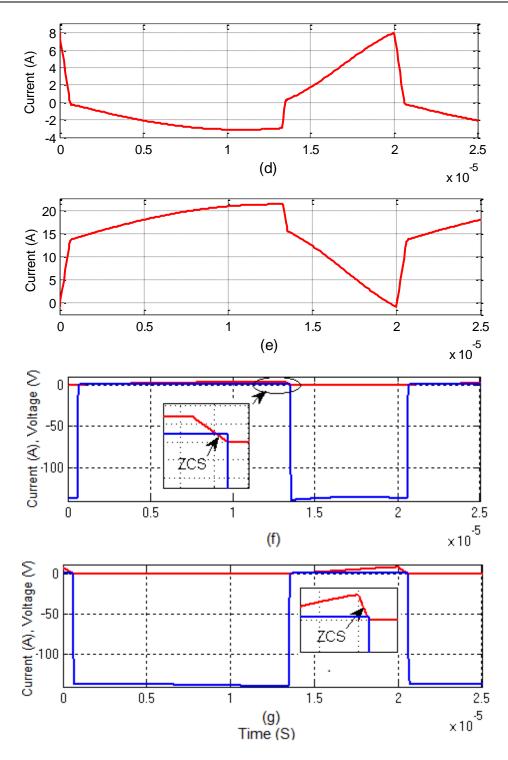

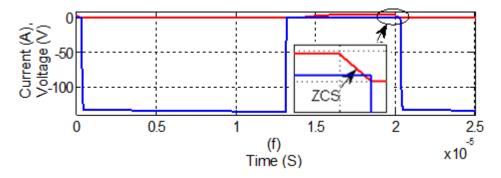

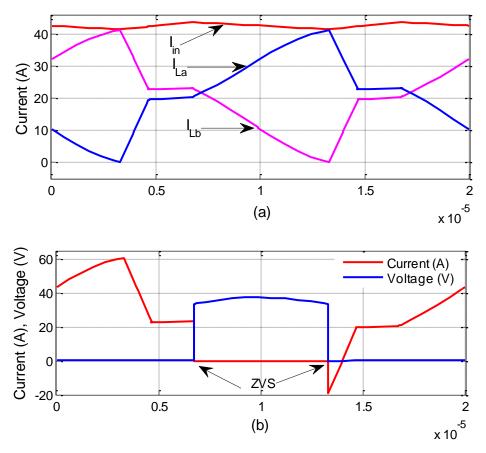

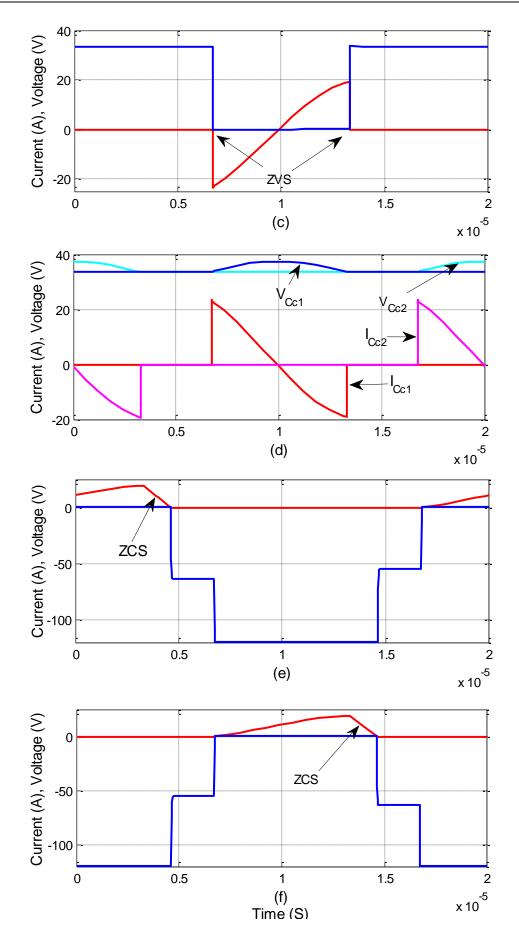

| Figure 5.9 (Continued) Simulation results                                              | 117     |

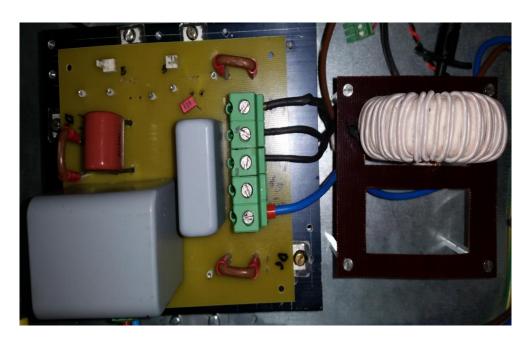

| Figure 5.10 Photograph of the experimental prototype                                   | 118     |

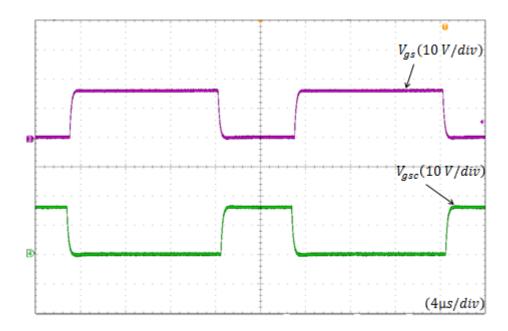

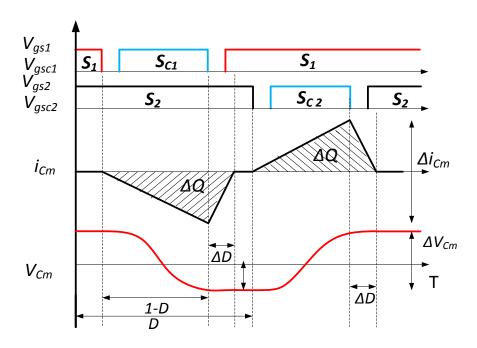

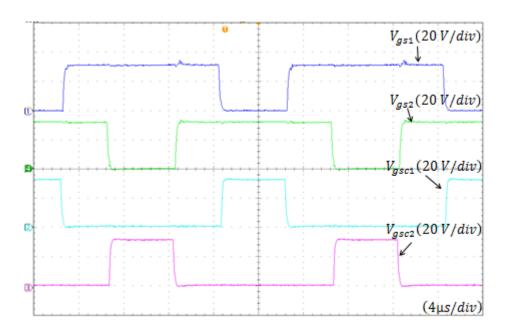

| Figure 5.11 Gate signals of the main and clamp switches                                | 119     |

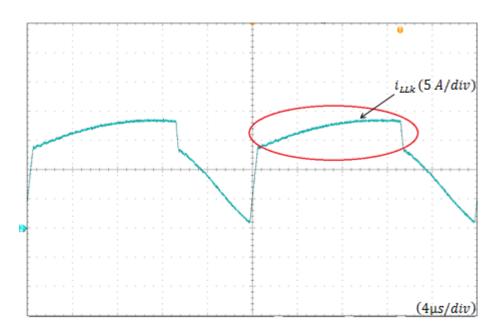

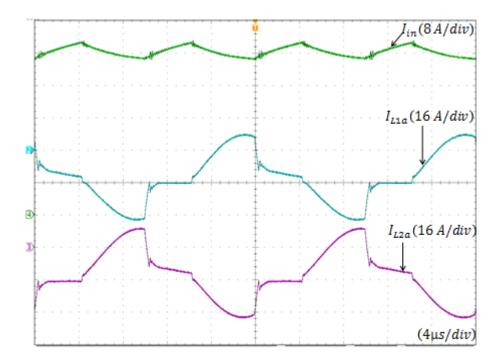

| Figure 5.12 Input current and coupled inductor primary current waveforms               | 120     |

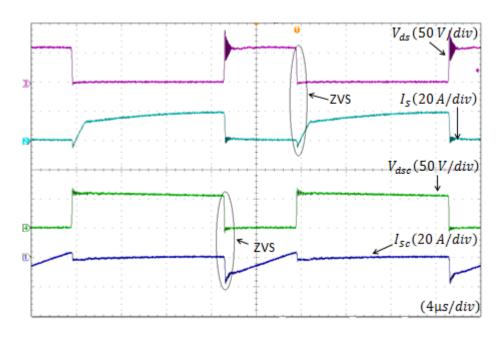

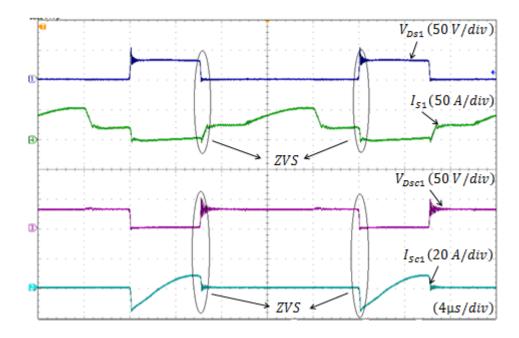

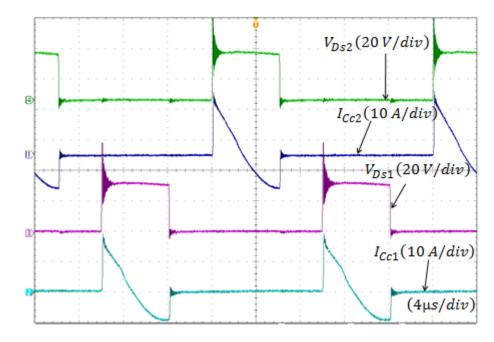

| Figure 5.13 Main switch S1 and clamp switch SC1 waveforms                              | 120     |

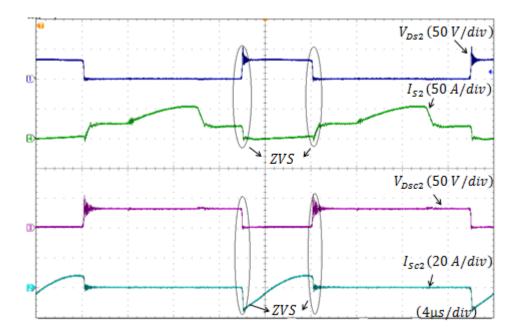

| Figure 5.14 Main switch S2 and clamp switch SC2 waveforms                              | 121     |

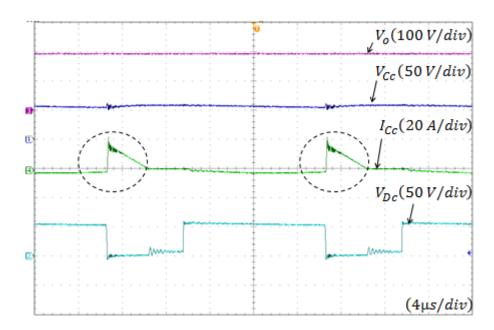

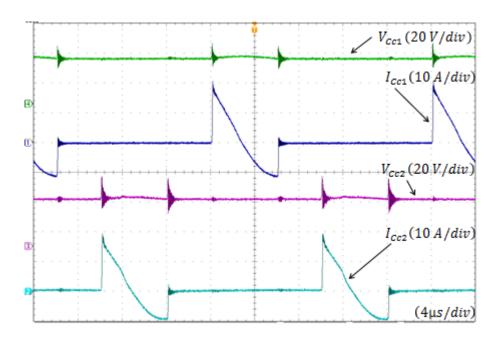

| Figure 5.15 Clamp circuit waveforms                                                    | 121     |

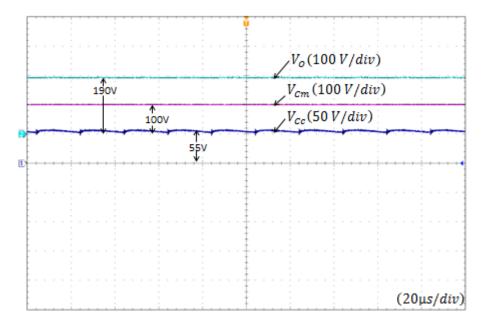

| Figure 5.16 Clamp capacitors CC1 and CC2 waveforms                                     | 122     |

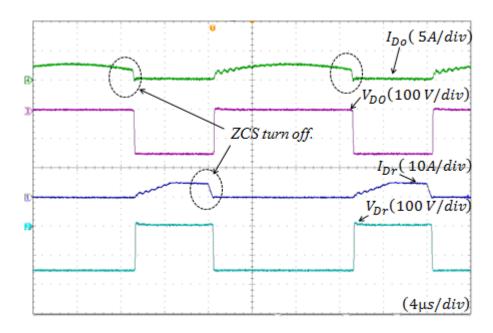

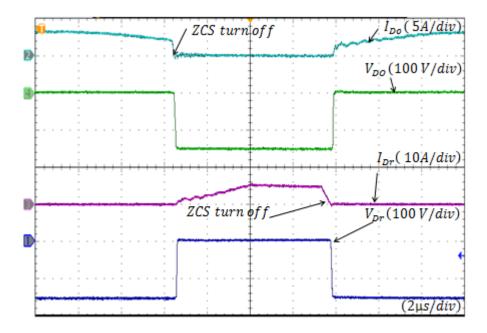

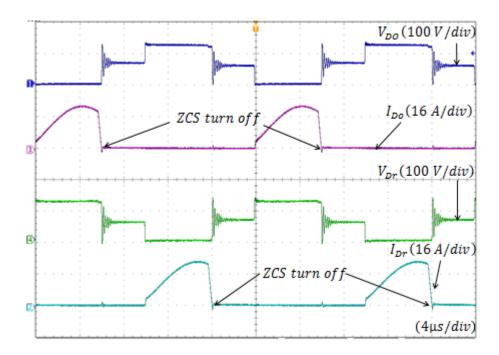

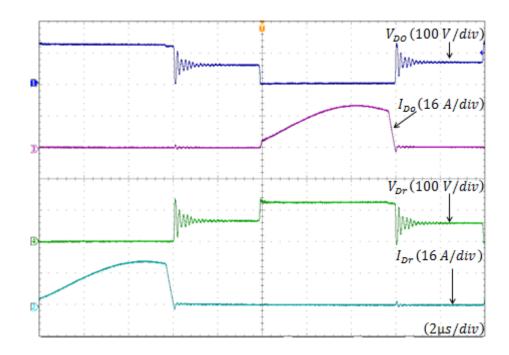

| Figure 5.17 Voltage and current stress of the diodes                                   | 123     |

| Figure 5.18 (ZCS) turn off of diodes and reverse recovery problem alleviation          | 123     |

| Figure 5.19 Measured Efficiency of the converter                                       | 124     |

| Figure 6.1 Direct simulation in Matlab                                                 | 131     |

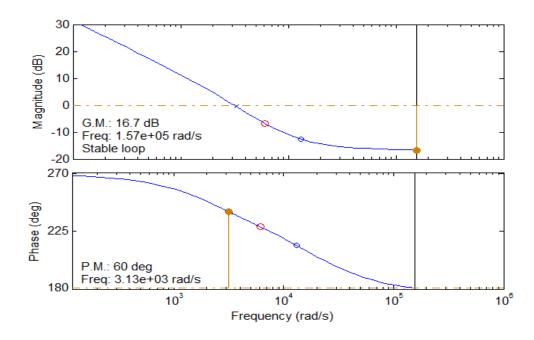

| Figure 6.2 Bode diagram of transfer function                                           | 131     |

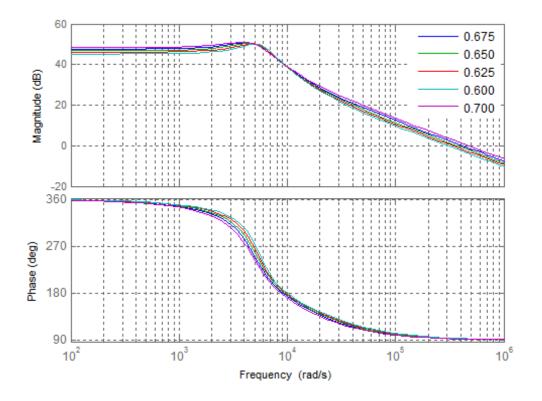

| Figure 6.3 Calculated and estimated control to output transfer function                | 135     |

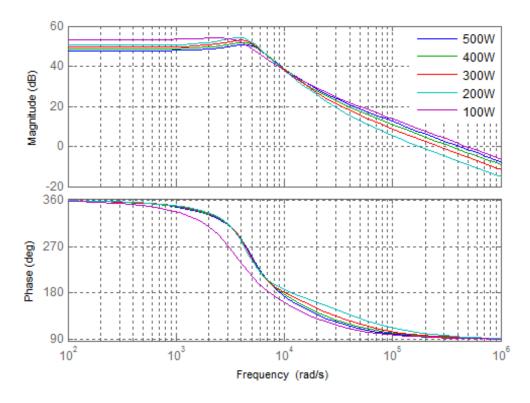

| Figure 6.4 Variation in DC gain with duty ratio                                        | 136     |

| Figure 6.5 Load change effect                                                          | 136     |

| Figure 6.6 Block diagram of dual loop feedback control diagram of high step-up inte    | rleaved |

| hoost converter in continuous domain                                                   | 137     |

| Figure 6.7 Block diagram of current control loop in continuous domain             | 138         |

|-----------------------------------------------------------------------------------|-------------|

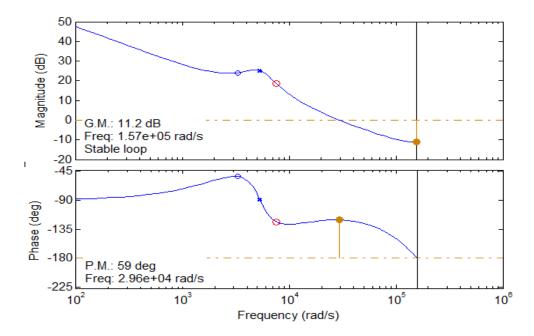

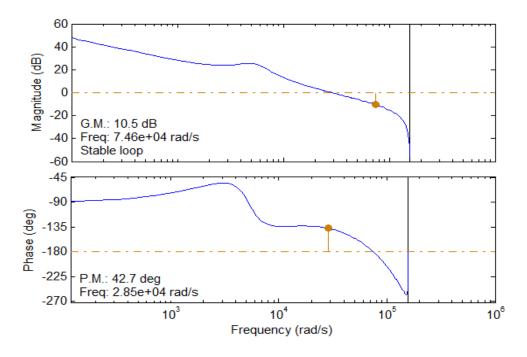

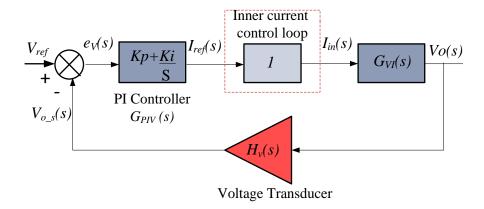

| Figure 6.8 Bode Diagram of current control loop with discrete PI controller       | 140         |

| Figure 6.9 Digital PWM delay effect                                               | 141         |

| Figure 6.10 Block diagram of voltage control loop in continuous domain            | 142         |

| Figure 6.11 Bode plot of the voltage control loop with discrete PI controller     | 143         |

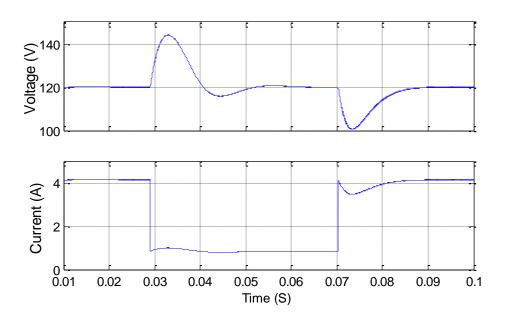

| Figure 6.12 Simulated response to load changes from 500W to 100 W                 | 144         |

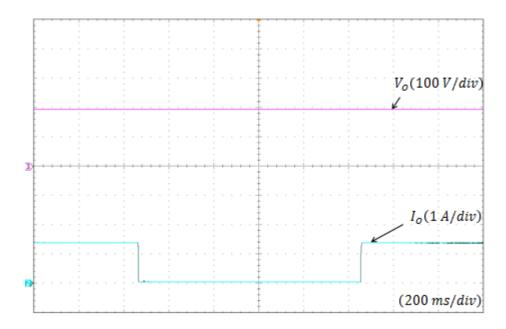

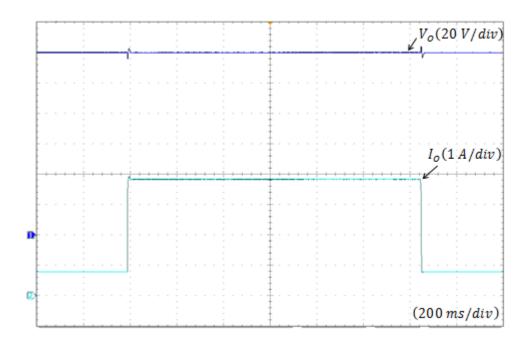

| Figure 6.13 Experimental response to step change from light load $PO = 100 W$ and | d full load |

|                                                                                   | 145         |

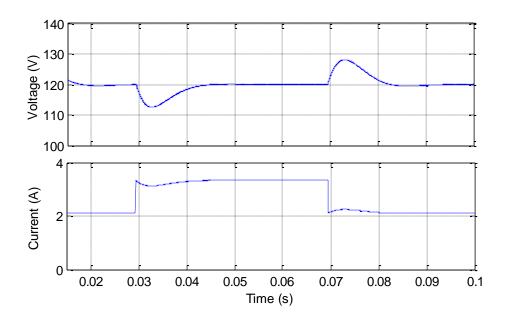

| Figure 6.14 Simulated response to load changes from 250W to 400 W                 | 146         |

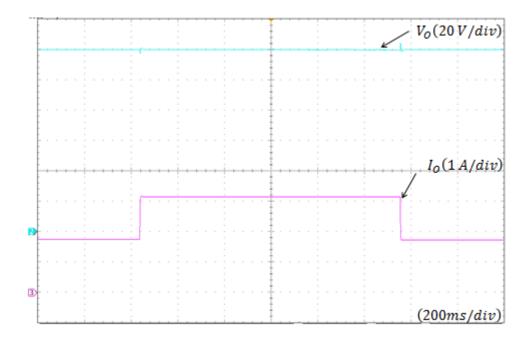

| Figure 6.15 Experimental response of load variation between $PO = 250 W$ and $PO$ | = 400 W     |

|                                                                                   | 146         |

| Figure A.1 Simulink model of the single phase active clamp converter              | 155         |

| Figure A.2 Simulink model of the single phase passive clamp converter             | 156         |

| Figure A.3 Simulink model of the proposed high step-up interleaved converter      | 157         |

| Figure B.1 High step-up converter with active clamp circuit                       | 158         |

| Figure B.2 High step-up converter with passive clamp circuit                      | 159         |

| Figure B.3 Interleaved converter photograph                                       | 160         |

| Figure B.4 Complete interleaved converter prototype                               | 160         |

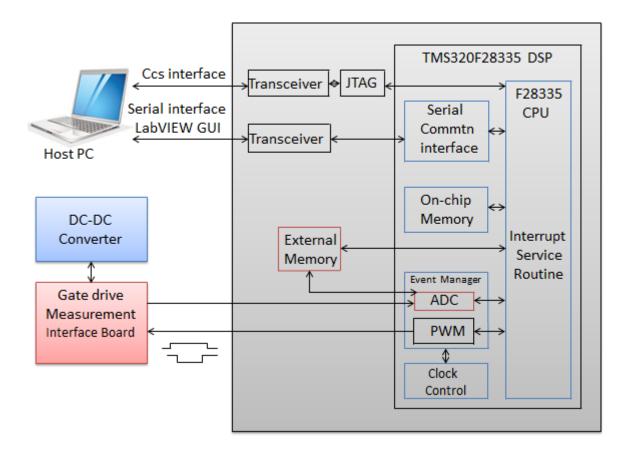

| Figure C.1 Texas instrument TMS320F28335 DSP Board                                | 161         |

| Figure C.2 Control overview                                                       | 162         |

| Figure C.3 Program flow chart                                                     | 163         |

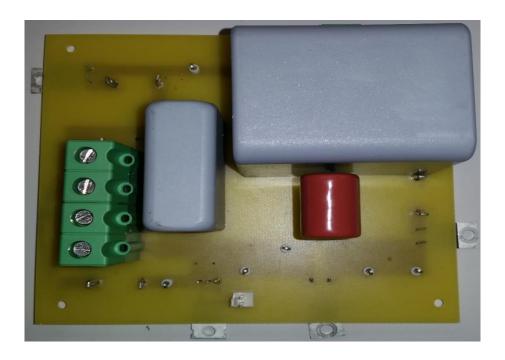

| Figure D.1 Interface board                                                        | 165         |

## **Tables**

| Table 3.1 Performance comparison between (BBAC), (ACCIB) Converters and Proposed              |

|-----------------------------------------------------------------------------------------------|

| Converter                                                                                     |

| Table 3.2 Converter Simulation Parameters                                                     |

| Table 4.1 Comparison between the simulated, measured and calculated results of PCC $\dots$ 89 |

| Table 4.2: Devices voltage stress comparison between passive and active clamp converters.90   |

| Table 4.3: Semiconductors current stress comparison between passive and active clamp          |

| converters90                                                                                  |

| Table 5.1 Converter Parameters                                                                |

| Table 6.1 Manual Tuning of PI controller based on Zeigler-Nichols method                      |

## **Symbols**

AC Alternating Current

ADC Analogue to Digital Converter CCM Continuous Conduction Mode

DC Direct current

DCM Discontinuous Conduction Mode

DPG Distributed Power Generation

DSP Digital Signal Processor

EMI Electro-Magnetic Interference

ESS Energy Storage System

EV Electric Vehicle

HID High Intensity Discharge HEV Hybrid Electric Vehicle

IGBT Insulated Gate Bipolar Transistor

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

LTI Linear Time Invariant

MOSFET Metal Oxide Field Effect Transistor

MPPT Maximum Power Point Tracking

PFC Power Factor Correction

PHEV Plug-in Hybrid Electric Vehicle

PI Proportional-Integral

PV Photovoltaic

PWM Pulse Width Modulation

RCD Resistor-Capacitor-Diode

RES Renewable Energy Sources

RMS Root-Mean-Square

UPS Uninterruptible Power Supply

(ZCS) Zero Current Switching

ZCT Zero Current Transition

(ZVS) Zero Voltage Switching

ZVT Zero Voltage Transition

## Chapter 1

## Introduction

#### 1.1 Background

The growing use of renewable energy sources (RESs) and Energy storage systems (ESS), due to global environmental concern, brings new challenges to the energy conversion technology. Because some devices that store or produce electrical energy (e.g., batteries, ultra-capacitors, fuel cells and solar photovoltaic) is often realized using multiple low voltage cells, which are usually connected in series to produce sufficient voltages for the intended application. Unfortunately, series connection of cells degrades the system performance, adds complexity to the system, and possible temperature rise due to fabrication variation and different operating conditions between cells. In batteries, this may be related to the state of charge of a cell. In solar arrays, it may be due to a change in solar irradiance or partial shading of the array.

Many green power supply system calls for a high efficiency, high step-up DC-DC converter in the power conversion stage. Typical applications include grid-connected inverters [1-4], drive [5], uninterruptible (UPS) [6, 7], motor power supply system telecommunication/network server power systems [8], electric vehicle (EV) [9], high intensity discharge (HID) lamps [10, 11] and distributed power generation (DPG) system [12]. Furthermore, high voltage step-up gains usually ten times or higher are increasingly required when the system is powered by low voltage energy sources such as Li-ion batteries, solar arrays and fuel cells. It is necessary or customary to use a relatively high and stable DC voltage in these applications. Besides, considering that the overall cost of a renewable energy system is high, the use of high-efficiency power electronic converter is necessary.

The boost and buck-boost converters are the simplest non-isolation topologies that produce an output voltage that is greater in magnitude than the source voltage [13, 14]. However, the conventional boost and buck-boost converters must operate at extreme duty ratio to achieve high voltage gain (in particular ten times). This is an undesirable operating point since the

1

output diode sustains short pulse, high amplitude, current pulses which result in severe reverse recovery losses. Besides, as the output voltage increases so must the voltage rating of the semiconductor switching devices and at high duty ratio the conduction losses of the semiconductor device can make a more significant impact to the performance of the system. Furthermore, as the duty ratio approaches unity, the output voltage approaches zero, and the efficiency decreases to zero [14]. Consequently, the converter may suffer poor dynamic response to system parameter changes and potential load variations. This behaviour is typical of converters having boost or buck-boost characteristics. The challenge for any high step-up DC-DC converter is to avoid extreme duty ratio operation.

Rather than a conventional single stage boost converter, a cascade boost converter is an attractive solution to enlarge the voltage gain without extreme duty ratio operation. However, the controllers must be synchronized, and the stability of the converter is another concern [15]. Moreover, the second stage may experience severe reverse recovery related losses in high power applications. Furthermore, the energy has to be converted twice, which obviously has an impact on overall efficiency.

Classical converters with magnetic coupling such as flyback or push-pull converters can easily achieve higher conversion ratio, by proper choice of the transformer turns ratio. One of the most commonly understood transformer based topologies is the flyback converter. The main drawback of the transformer based topologies is high turn off voltage spike seen by the primary switch, due to the transformer leakage inductance interaction with parasitic capacitor of the switch. To go some way to mitigating these effects, energy recycling techniques must be adopted to recycle the leakage energy [16]. Moreover, the transformer volume and weight is another problem that inhibits developing a compact, high power density converter. Thus, whilst functional, these types of converters do not offer an optimal solution in cost sensitive power supply applications.

This thesis is concerned specifically with research into high step-up DC-DC boost converter topologies. There is increasing interest in the use of high step-up DC-DC boost converters for harvesting all available energy, typical applications call for high-efficiency high step-up converters. These two features are the focus of this research. Basic boost and buck boost converters operate with extreme pulse width modulation (PWM) duty ratio to achieve higher conversion ratio of (ten times or higher). Appropriate duty ratio is desirable since extreme duty ratio operation have long been recognised as causing some operational drawbacks to the high step-up converters.

Some of the major shortcomings of extreme duty ratio operation include reverse recovery loss of the output diode as a result of short pulse current with large amplitude. Furthermore, the output diode reverse recovery problem can lead to higher turn-on switching loss for the power switch. For this reason, there is considerable motivation to improve the performance of high step-up boost converters by alleviating the diode reverse recovery loss so that switching loss can be significantly reduced. Literature has revealed that the power device voltage rating in conventional boost converter is the same as the converter output voltage. Another concern related to the efficiency of high step-up converters is power device rating. A high voltage rated device is not a good choice for the steady state operation because of the high input current (as the power MOSFET rating increases, so does the on-state resistance  $R_{ds\_on}$  resulting in conduction losses which also degrade the efficiency). The challenge for a high step-up converter is to dramatically reduce the conduction losses. Appropriate duty ratio operation, conduction losses reduction and alleviation of diode reverse recovery problem can greatly improve the efficiency of power conversion. It is the aim of this thesis to investigate methods of improving the performance of high step-up converters.

#### 1.2 High Step-up DC-DC Converters Applications

Many applications powered by RESs call for a high-efficiency high step-up DC-DC converter in the power conversion stage. Typical examples include grid connected inverters [1-4], high-intensity discharge lamp (HID) [10], electric drives [17] and uninterruptible power supply system (UPS) [6, 7]. Some emerging applications that require high step-up DC-DC power converters are briefly described in the following section.

#### 1.2.1 Grid Connected Photovoltaic Inverter

One of the most important applications of solar photovoltaic (PV) is electricity generation, particularly in countries having a considerable amount of solar radiation. The application could be a stand-alone or grid-connected system. The PV grid-connected power system is a fast growing segment in Europe, with record addition of 1.9 gigawatts in Germany, 2.4 gigawatts for the United Kingdom, 0.9 and 0.4 GW for France and Italy respectively in 2014 [18]. Countries like Japan, China and the U.S have added 9.7, 10.6 and 6.2 GW respectively for the same year under review. This addition brings the total global installed capacity to 177 GW [18].

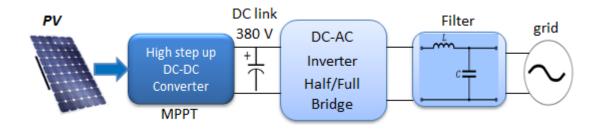

Figure 1.1 shows the block diagram of a typical grid connected PV power system. PV panels

Figure 1.1 Single phase grid connected renewable energy system

are often connected in series to obtain the DC link voltage along with the power converter to track the maximum power point (MPP) range of the PV. However, when partial shading occurs or mismatch, the MPP losses increase significantly. Another configuration is to use a modular approach to reduce the cost and improve the system MPPT efficiency; in this case, an independent module integrated DC-DC converter is used for each PV panel. Thus, decoupling every panel from others to make the system configuration flexible and maximizes the output power. Nevertheless, the topology normally has two power electronic converters. The first converter is the high step-up boost converter that is required to raise the relatively low solar panel DC voltage to a certain level suitable for synthesizing the alternating current AC line voltage, which is typically 380 - 400 V DC. The second converter is the DC-AC inverter that injects sinusoidal current into the grid. The high step-up DC-DC converter along with maximum power point tracking (MPPT) algorithm stabilise the DC bus voltage level and make full utilization of the PV array. The performance of the high step-up DC-DC converter is crucial to the performance of the whole PV system because the DC-DC converter is the core element that interfaces the solar photovoltaic with the DC-AC inverter and manages the power flow.

The main shortcoming of a grid-connected power system is power contributed by the system to the grid is available only during part of each day since solar energy is available only during the daylight hours. To overcome this problem an energy storage system ESS such as battery is usually employed in the photovoltaic inverter systems to improve the system performance and supply availability [19]. The objective of utilising the ESS is to provide a back-up function, transferring the solar energy to the ESS during the sunny time, whilst delivering energy to the DC bus when the solar energy is not available. As a result, stable and fast response AC power can be provided to the grid. Integrating the grid connected PV system with ESS is achievable with the aid of bidirectional DC-DC converter that has power flow in both forward and reversed directions (boost and buck).

#### 1.2.2 High Intensity Discharge (HID) Lamp

High-intensity discharge (HID) lamp are preferable, instead of conventional halogen lamps for use as automobiles headlamps due to its superior performance and numerous advantages, such as higher efficiency, longer life, good light beam focus and superior colour rendering capability. Although the HID lamp has significant advantages, its operation is similar to the other discharge lamps and requires a ballast to control the lamp power during steady state operation.

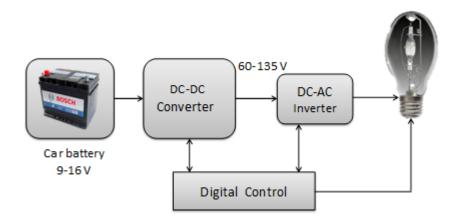

Figure 1.2 shows typical ballast circuit for powering and igniting the lamp. The ballast consists of high step-up DC-DC converter, an inverter and an igniter. The HID are powered using the automobile 12 V battery, which provide an input voltage much lower than the operational voltage of the ballast. For this reason, a high step-up DC-DC converter is required in the ballast to step-up the battery voltage to (380 V - 400 V) during start up and in the (60-135 V) range during steady state operation [10, 11]. Therefore, a high step-up DC-DC converter with about tenfold voltage gain is critical for the operation of the lamp.

Figure 1.2 High Intensity discharge lamp ballast block diagram

#### 1.2.3 Electric Vehicle

The automotive companies are focused on electric vehicles (EV), hybrid electric vehicles (HEV), plug-in hybrid electric vehicles (PHEV) and fuel cells vehicles to meet the demand for emission-free vehicles with improved fuel economy, comfort and safety. However, the key challenge lies in the efficiency, cost, size of power electronic converter and machine. In particular, the high step-up DC-DC converter to interface the fuel cell voltage with the battery packs.

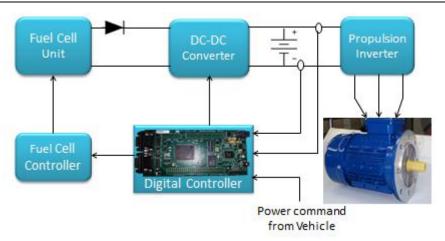

Figure 1.3 Electric vehicle drive train

Figure 1.3 illustrates a typical fuel cell vehicle propulsion system. A high step-up DC-DC boost converter is usually employed to step-up the relatively low DC voltage of the fuel cell to a typical DC link voltage of 400V which is also compatible with the battery. An inverter is then used to drive the propulsion motor. ESS such as: Li-ion batteries are often used to provide supplementary power during vehicle starting, acceleration and hill climbing. Different configurations and classifications of electric vehicle propulsion system can be found in [9]. The use of bidirectional DC-DC converter along with ESS in electric vehicle to achieve power transfer in either direction is demonstrated in [20] The regenerative energy fed back by the electric machine during breaking is absorbed by the battery. Whilst the capacitive energy source is step-up by the converter to compliment vehicle starting and acceleration.

#### 1.2.4 Uninterruptible Power Supply UPS

The growing use of Uninterruptible power supply (UPS) to supply power to the sensitive loads and protect them during mains outages under normal or abnormal utility power conditions is well documented [6, 7]. UPS has been widely used to supply seamless power to critical loads, such as medical equipment, communication systems computers and servers. All UPS uses specific DC-DC power electronics converters to interface different sources and load. For example, the UPS topology consists of power factor correction (PFC) circuit, which is typically an AC-DC front-end converter that convert the ac-line voltage (90 – 265  $V_{rms}$ ) and provides a regulated DC link voltage of (380 - 400 V) required by the inverter. During the mains or utility outage, the UPS enters the backup mode, and the UPS generate AC voltage from the 48 V back-up batteries to supply the load. A high step-up converter is necessary to raise the battery bank voltage to that required by the DC bus.

#### 1.2.5 Telecommunication Power System

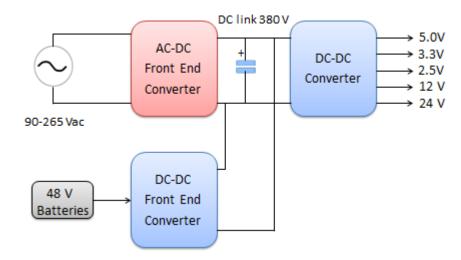

Figure 1.4 Dual front end telecom power system

Typically, UPS provide up to 30 minutes of reserve time; this is far shorter than the reserved time needed by telecommunication power systems. Consequently, using 48 V DC telecom bus has become a natural choice of powering data processing equipment installed in the telecom environment [10]. Figure 1.4 shows a typical Power supply system of telecommunication equipment. The power supply is characterised by high power density, efficiency and has several stages [8]. Traditionally the first stage is AC-DC system powered from AC-line voltage  $(90 - 265 \, V_{rms})$  and provides a high step-up DC bus voltage of up to  $(400 \, \text{V})$ . The AC-DC converter serves as a power factor correction circuit for suppressing the harmonic level. The nominal 380 V bus voltage is converted to a tightly regulated lower voltage of 5, 3.3, 12 and 24 V respectively for the logic circuits. However, during the mains outage the telecommunication industries uses 48V DC battery bank as a conventional choice to provide back-up. In this case, a DC-DC high step-up back-up converter is required to provide a simple and efficient solution of raising the 48V DC battery bank voltage to the 400 V DC link voltage. A high step-up DC-DC converter that generates 400 V DC from 48 V DC batteries is necessary in the telecommunication server power supply system.

#### 1.2.6 Distributed Power system

Distributed power generation (DPG) systems are considered to be the key components of future power grids due to its ability to produce and distribute energy to various loads. For the purpose of robust control, monitoring, power quality improvement, fault detection/isolation and stabilization, DPG uses Microgrids in combination with renewable energy sources such as batteries, photovoltaic panels, fuel cells and loads [12]. Microgrids can operate

autonomously or grid connected depending on the configurations, and there is no doubt that DPG is the building blocks of a smart grid.

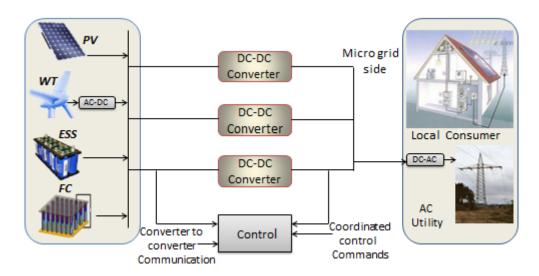

Figure 1.5 shows the DPG block diagram. The system requires specific power electronics converters to convert and regulate the generated power before interconnection with the utility grid and/ or onward supply to consumer loads [21, 22]. It is necessary to employ DC-DC converters with various power levels to exploit the locally produced power to meet the requirement of various local loads. In a nutshell, the quality and efficiency of the overall system depend on the performance of these power electronic converters.

Figure 1.5 Distributed power system

#### 1.3 Characteristics of High Step-up Converters

In general, the performance of high step-up DC-DC converters exhibits high output voltage and large input current. The large input current emanates from low input voltage. Therefore, some of the desirable characteristics of high step-up converters are briefly described in the subsequent sections.

#### 1.3.1 High Conversion Ratio

Many applications powered by RESs or ESS call for high step-up DC-DC converters. For example, the output voltage level of the PV array in the grid-connected inverter is typically low 16-43 V and the DC bus voltage suitable for synthesizing the AC line voltage is 380 - 400 V DC. About ten times (10X) or higher voltage gain is required to raise the array voltage to DC link voltage for steady state operation.

#### 1.3.2 High-Efficiency

The large input current is a major concern related to the efficiency of the high step-up DC-DC converters. Low input voltage results in large input current. Therefore, higher peak and root-mean-square (RMS) current stress suffered by the switching components is a primary detriment to increasing the efficiency. To enhance the efficiency of DC-DC converters low rated devices with low on-state resistance are desirable to reduce the conduction loss. In high voltage applications, the reverse recovery problem of the output diode is another concern. Lower rated diodes typically recover faster.

#### 1.3.3 Low Voltage/Current Ripple

Power electronic converters have an inherent switching characteristic, which causes the current and voltage to fluctuate. For example, in DC-DC boost converter, the switching action of the power MOSFET or IGBT causes the inductor current to have a triangular waveform with a DC offset. The DC component of this inductor current flows through the load and AC components via the output capacitor. A capacitor ripple voltage is produced due to time-varying current through the capacitor. The input current or the output voltage contains some ripple on top of the steady state value. Power electronic converter designers consider the ripple magnitude to be a key parameter in designing such systems. Minimization of the current/ voltage ripple (AC component in the system) which decreases the efficiency lifetime of the converter is essential. In an ideal situation, only DC components should be present at the output.

#### 1.3.4 Fast Response

In a DC-DC converter operating under closed loop control, the duty ratio is determined by the converter nominal operating point based on converter dynamics. Likewise the load resistance, which is also based on DC loads requirement. The load resistance and duty ratio are exogenous quantities that require compensation scheme due to pole-zero variation. The converter should exhibit a fast response in the presence of load/source changes, other external disturbances and must be able to operate in adverse environmental conditions.

#### 1.4 Motivation

Theoretically, conventional boost and buck-boost converters are the simplest PWM controlled topologies for voltage step-up. However, these converters must operate under extreme duty

ratio to achieve high voltage gain which severely penalizes the efficiency. In addition, the high output voltage requires higher rated device with large on-state resistance. As the power device rating increases so does the conduction loss which further degrade the efficiency. Furthermore, the output diode sustains a short pulse current with the high amplitude that result in reverse recovery related losses. One of the main challenges of high step-up DC-DC converters is to avoid extreme duty ratio operation so that both switching and conduction losses can be substantially reduced. Finding a way to avoid extreme duty ratio operation in high step-up converters is one of the motivations of this thesis.

One of the simplest solutions for avoiding extreme duty ratio operation is by using cascade structure. In cascade structure, both stages can achieve step-up function and switch conduction loss is low in the first stage. However, the high output voltage still affects the efficiency of the second stage. Transformers or coupled inductor based converters such as flyback and forward converters can provide higher conversion ratio without extreme duty ratio operation by utilising the transformer turns ratio. A drawback to the use of a transformer is high voltage stress seen by the power device, due to the interaction between the leakage inductance and switch capacitance conventionally requires a snubber. A resistor-capacitor-diode (RCD) snubber can suppress the device voltage stress, but the leakage energy dissipates within the snubber contributing to the losses. A passive lossless or active clamp circuit can recycle the leakage energy and reduce the device voltage stress. Evaluating the performance of leakage energy recycling schemes on the same power converter is another motivation.

#### 1.5 Aim and Objectives

Power electronics converters are key components for interfacing and conditioning the power level of source and load in many applications. Direct connection to various voltage levels requires utilizing advanced topologies combined with low-rated high- performance power semiconductor devices.

The aim of this research is to develop a high step-up DC-DC power conversion system to meet the requirement of emerging power supply system in energy delivery and management.

The main objectives and research contributions are:

• To propose a new single phase non-isolated DC-DC boost converter based on coupled inductor and capacitor charge transference with high conversion ratio.

- To propose a new high step-up high-efficiency interleaved non-isolated coupled inductor DC-DC boost Converter with ten times (10X) static gain or higher.

- Application of capacitor charge transference and a coupled inductor turns ratio in high step-up converters to avoid extreme PWM duty ratio operation.

- To develop models of the interleaved high step-up converter suitable for control design implementation.

- Experimental assessment of the performance of the proposed single phase and interleaved high step-up converters using a digital signal processor (DSP) platform.

In order to achieve the above goals the thesis proposes the following approach:

- a. Application of active clamp circuit to depress the coupled inductor leakage energy and realize zero voltage switching (ZVS) technique so as to minimize the switching losses under high-frequency operation.

- b. Assess the performance of active and passive clamping schemes in recycling the leakage inductor energy with regards to single phase high step-up converter.

- c. Utilize an interleaved technique to increase the power density and improve the efficiency of high step-up converter.

- d. Utilizing the inherent leakage inductance of the coupled inductor to alleviate the reverse recovery related losses of the diodes.

- e. Present a comprehensive steady-state operational analysis and design guidelines of the converters.

#### 1.6 Thesis layout

The thesis is structured as follows:

Chapter 2: Literature Review- A background description and review of the methods of developing the state of the art high step-up boost converters is presented to define firstly the work and its novelty. The main challenges related to the current state of the art non-isolated high step-up DC-DC boost converters are identified. The improved system platform is then proposed with the advantages of higher efficiency, simple circuit and low cost.

**Chapter 3:** This chapter proposes a new single phase high step boost converter employing coupled inductor and voltage gain extension cell. A description is also given on how the topology is developed based on the concept of two capacitors charged in parallel and discharged in series. The capacitors are integrated into coupled inductor boost converter to

configure the voltage gain extension cell. The state of the art solution of alleviating the reverse recovery problem of the output diode is to control the current falling rate with the aid of an auxiliary circuit. In this approach the diodes are always in series with the coupled winding when the diodes turn off. This makes the leakage inductance available to control the current falling rate of the diodes. Thus, the diode reverse recovery problem is alleviated. The power stage model is fully investigated and developed. Experimental test results of a 250 W implemented prototype are given to verify the operational principles.

Chapter 4: The performance evaluation of clamp circuits has been carried out in this chapter by replacing the active clamp solution in chapter 3 with passive clamp scheme. On one hand, the passive clamp approach achieves similar function of active clamp circuit in depressing the leakage inductance energy with low level of circulating current in the clamp circuit, cost reduction and higher reliability. On the other hand, the passive clamp converter has the advantage of achieving zero current switching (ZCS) of the primary switch. Experimental results revealed that the active clamp converter achieves higher efficiency than the passive clamp converter.

Chapter 5: The main drawback of the coupled inductor in a high step-up application is a large current ripple. This issue is addressed by proposing an interleaved high step-up boost converter with high voltage gain. The topology demonstrates how the high input current is shared between the interleaved phases and minimizes the current ripple. It further illustrates that by appropriate current sharing the passive components size is reduced, which improves the thermal distribution and the transient response. Detailed steady state analysis including design consideration is presented. A 500 W laboratory prototype have been developed, and the experimental results are given to validate the theoretical analysis.

**Chapter 6:** In this section, the modelling of the proposed interleaved high step-up boost converter is demonstrated. It also highlights the steps in obtaining the full and reduced order models of the converter based on state space averaging. The reduced order model is linearized and various linear time invariant (LTI) transfer functions are derived. Furthermore, a block diagram model is developed suitable for dual loop average current mode control. The dual loop controller is implemented with Texas Instrument TMS320F28335 digital signal processor (DSP). The controller provides smooth power flow control.

**Chapter 7:** Conclusion- deals with the summary of the whole work and the extent to which the research aim and objectives have been met. Conclusions are drawn from the study and potential areas of further investigation are equally suggested.

#### 1.7 Research Impact

The Proposed Interleaved high step-up boost converter developed in this thesis has attracted Industrial Consortium under the project known as HICO. The 500 W converter prototype have been installed and currently running in a car as a technology demonstration on electric vehicle EV battery charging application. The interleaved high step-up converter is used as an interface for charging the automotive traction batteries (Li-ion batteries) from a low voltage source (12 V car battery). In this application, the maximum voltage required is 100.1 V. Therefore, the duty ratio is adjusted to obtain the desired voltage level. In addition, there is future plan to develop a 2 KW converter for use in the same application.

#### 1.8 Publications Arising from this Research

The research work carried out in this thesis has resulted in publication in IEEE journal of emerging and selected topics in power electronics (JESTPE):

- Muhammad M., M. Armstrong, and M. A. Elgendy, "A Non-isolated Interleaved Boost Converter for High voltage Gain Applications." IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016. 4(2): pp. 352-362,

- Muhammad M., M. Armstrong, and M. A. Elgendy, "Analysis and Implementation of a High Gain Non-isolated DC-DC Boost Converter" Submitted for peer review in: IET Power Electronics.

In addition, the following conference papers stemmed from the research

- (1) Muhammad, M., M. Armstrong, and M. Elgendy. "Non-isolated DC-DC converter for high-step-up Ratio Applications", in Power Electronics and Applications (EPE'15 ECCE-Europe), 2015, 17<sup>th</sup> European Conference on. 2015

- (2) Muhammad, M., M. Armstrong, and M. Elgendy. "Non-isolated, high gain, boost converter for power electronic applications." in 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016). 2016.

- (3) Muhammad, M., M. Armstrong, and M. A. Elgendy, "Modelling and Control of Non-isolated High Voltage Gain Boost Converter Employing Coupled Inductor and Switched Capacitor." in 2016 International Conference for Students on Applied Engineering (ICSAE). 2016.

#### 1.9 Summary

This section provides a general background of the high step-up DC-DC conversion and their typical applications, in particular, it demonstrate the rapid increase in the use of DC-DC converters and their roles as an interface for connecting various voltages levels and managing the power flow. Following this, the motivation of the whole work is presented. The aim of the research is then defined; to develop a high efficient, high step-up DC-DC power converter system based on current commercially available power semiconductors to meet the requirement of emerging applications in providing future energy delivery and management.

## Chapter 2

# **High Step-up DC-DC Conversion Techniques -A Literature Review**

#### 2.1 Introduction

High step-up DC-DC boost converters are widely used as an interface to transfer power between the low voltage sources to a higher DC bus. In many modern applications, such as HID lamp [10], EV [9] and grid-connected PV systems [2] powered by RESs; it is necessary to utilise converters with high static gain, usually ten times or higher. Since most of these RESs provide a low output voltage, a conventional boost or buck-boost converter can be employed to step-up the source voltage to the voltage level required by the load. However, the conventional boost and buck-boost converters suffer extreme PWM duty ratios to achieve high voltage gains. The output diode sustains short pulse current with high amplitude, which results in severe reverse recovery losses. In addition, as the output voltage increases so must the voltage rating of the semiconductor switching device and because of the high input current that results from the low input voltage, the conduction losses of the semiconductor device can make a more significant impact on the performance of the system. Furthermore, as the duty ratio approaches unity, the converter may suffer poor dynamic response to system parameter changes and potential load variations [23, 24].

Various techniques for high step-up conversion have been reported in the literature [10, 23, 25-46]. Depending on the application, they are either isolated [25-35, 47] or non-isolated [10, 23, 36, 37, 39, 41, 43, 44, 46, 48-50] topologies. Transformer based converters can easily achieve high voltage gain by adjusting the turns ratio and utilises low rated devices to reduce the conduction losses. However, the leakage inductor induces high voltage stress to the power device and traditionally requires a snubber. Either RCD snubber circuit or a clamp circuit must be used to handle the leakage energy. To address the demand for high step-up high power density in DC-DC converters, the power electronics community and industries have

been reacting in two different ways; developing semiconductor technology and or developing new converter topologies. This work addresses the later by proposing new converter topologies.

The high-frequency operation has been explored in the literature due to significant advantage of reducing the volume and weight of the converter. Miniaturization of power converter circuits is possible if they operate at a higher switching frequency. However, the switching losses are proportional to switching frequency. To design a compact converter, a way to minimise or eliminate the switching losses must be conceived. Resonant and soft switching techniques are applied to high step-up converters to mitigate the switching losses.

This chapter presents an overview of techniques of developing high step-up non-isolated DC-DC boost converters. The first section of this chapter describes the characteristics of conventional boost converter being the most popular topology and its major limitations in high step-up application. The subsequent section evaluates different techniques aimed at overcoming the limitations of the boost converter and improving the conversion ratio. The main advantages and drawback regarding each technique is highlighted, and the rationale for choosing the magnetically coupled converters and voltage gain extension cell in this work is explained clearly. Furthermore, some soft switching techniques and methods of alleviating the diode reverse recovery related losses are also reviewed.

#### 2.2 DC-DC Boost Converter

#### 2.2.1 General Structure of DC-DC Boost Converters

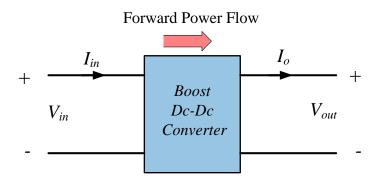

Figure 2.1 Boost converter unidirectional power flow

Figure 2.1 illustrate the generic structure of the DC-DC boost converter. Depending on the configuration, the input side can be current fed or voltage fed. The input voltage can be a battery, fuel cell or solar photovoltaic. The load is placed on the output side; this could be an

inverter in stand-alone or grid-connected power system. The converter has a unidirectional power flow. The active switch is typically implemented with semiconductor devices such as MOSFET or IGBT. The term step-up and boost are used interchangeably to imply a converter whose output voltage is always higher in magnitude than the input voltage [14, 51]. In most cases, boost refers to converters without wide conversion ratio, whilst high step-up usually refers to converter with wide voltage gain. DC-DC converters are further classified as isolated or non-isolated

#### 2.2.2 Isolated DC-DC Boost Converters

The high-frequency transformer based system is an attractive solution for providing galvanic isolation and impedance matching between the source and load. As an example, isolation is usually required by regulatory agencies in off-line power supply applications. Classical converters with galvanic isolation such as flyback, current-fed push-pull converters can easily achieve high voltage gain by adjusting the turns ratio. However from an efficiency standpoint, the high-frequency transformer implies additional cost, losses and inhibits developing a compact converter. Thus, the volume weight and losses are the main limitations of isolated converters in embedded applications. Isolated boost converters are either current-fed [26-28] or voltage-fed [34, 52]. Some typical examples of isolated DC-DC converters topologies include flyback [16, 53], forward [54], full bridge [26, 27], half bridge [28-30, 55], push-pull converters [31-33] or their variations.

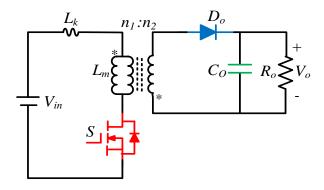

A flyback converter is the most widely understood topology due to its relative simplicity. Theoretically, the transformer reduces the magnetic components count by providing energy storage and galvanic isolation. However, the semiconductor devices incur current and voltage stress which limit its use to low power applications. The interaction between the parasitic capacitor of the switch and transformer leakage inductance induces high voltage spike during turn off which necessitates the use of clamp circuit. The simplified circuit of flyback converter is shown in Figure 2.2. Note that a red colour is chosen for the power switch, load resistor, blue for the power diode and green for the capacitor. The colour convention is adopted throughout this thesis for easy recognition of one passive component from the other.

The full bridge DC-DC converter is considered one of the famous isolated topologies, with more component counts when compared with the half bridge converter. The operation of the circuits involves utilisation of the transformer leakage inductance for transferring energy from source to the load. Prominent advantages of full bridge converter include immunity from

Figure 2.2 Flyback converter

transformer flux imbalance and absence of output inductor. A fundamental shortcoming of the voltage fed full bridge converter is the voltage spike across the output diode, due to the leakage inductance of the transformer. The voltage spikes are exacerbated by increasing the switching frequency [52]. Other problems include duty cycle loss and pulse current at the input which increases the filter size.

#### 2.2.3 Non-isolated DC- DC Boost Converter

Rather than the isolated converters, non-isolated DC-DC converters can be used to improve the efficiency. Consequently, the volume, weight and losses associated with the high-frequency transformer are reduced. Furthermore, in the high power application where weight size is the main concern, the transformer-less structure is the most attractive [23]. It is becoming a more suitable solution to employ non-isolated converters to reduce the system cost and improve the efficiency. Since the passive components size and weight of non-isolated converters vary inversely with frequency, the components then operate at converter switching frequency in tens of kilohertz (KHz) range or higher. This high frequency leads to dramatic reduction in converter size and weight. In summary, for applications that require isolation between source and load based on safety measures, the isolated topologies are the right choices. However, in high power applications where volume weight is the main concern, the non-isolated topologies are the best option. The basic non-isolated DC-DC step-up topologies that produce an output voltage higher in magnitude than the input voltage are the boost and buck-boost converters.

#### 2.2.4 Conventional Non-isolated DC-DC Boost Converter

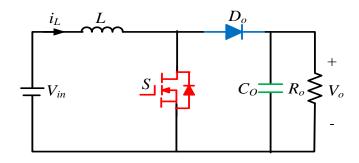

The conventional non-isolated DC-DC boost converter is shown in Figure 2.3. As the name implies the output voltage  $V_0$  is always higher in magnitude than the input voltage  $V_{in}$ . Higher

output voltage can be accomplished by controlling the operation of the switch using the PWM signal. Accordingly, the states of the switch (ON/OFF) are changed periodically with the period equal to  $T_{sw}$  (switching period) and duty ratio equal to D. The level of the converted voltage depends on the magnitude of the applied input voltage and the duty ratio.

Figure 2.3 Conventional boost Converter

During the switch turn on instant, the diode  $D_O$  is reversed biased, and the input source charges the inductor L. When the switch turns off, the load receives energy from the input as well as the inductor. The capacitor  $C_O$  removes the switching harmonics from the applied input signal. Noticeably, the energy transfer in a step-up (boost) converter is between a voltage and current source. Since in a steady state, the capacitor or inductor can be represented by their instantaneous voltage or currents as an equivalent voltage and current sources respectively.

The steady state operation described is known as continuous conduction mode (CCM), since the inductor passes a current continuously without a break. However, if the inductor current became zero for part of the cycle as duty ratio *D* comes out of conduction, then this operation is called discontinuous conduction mode (DCM).

#### 2.2.5 Limitations of Conventional Converters in High step-up Applications

The boost and buck-boost converters are the simplest PWM controlled topologies for voltage step-up. However, these converters typically operate under extreme duty ratio to achieve high voltage gain. As a consequence, significant voltage and current stresses are incurred by the power converter devices and poor dynamic characteristics can result in the controlled output response. Besides, the power device rating is proportional to the output voltage and a high rated power device potentially increases the conduction losses which also degrade the efficiency. Furthermore, the output diodes often sustain short, but high amplitude, current pulses due to the narrow turn off time; which induces reverse recovery losses.

# 2.3 Topology Evaluation for High step-up DC-DC Boost Converter

The major obstacle of improving the efficiency of the basic DC-DC converters such as boost and buck-boost in a high step-up application is extreme PWM duty ratio, conduction losses emanating from high rated power devices and reverse recovery related loss of the output diode. In view of these limitations, several work have been carried out to explore numerous topologies with potentials of improving the limitations of basic topologies such as static gain, power devices voltage stress, power density and efficiency. The next section focuses on evaluating these topologies and stating their advantages or disadvantages.

#### 2.3.1 Cascade Converter

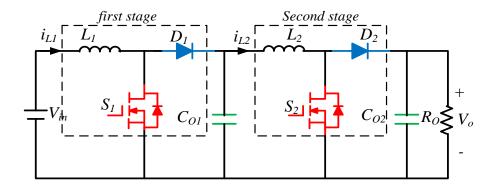

Figure 2.4 Cascade boost converter

The use of two DC-DC boost converters in cascade is an effective method of improving the static voltage gain [56]. It mainly involves connecting the output stage of a boost converter to the input of another boost converter, such that an intermediate bus voltage is developed around capacitor  $C_{O1}$  as illustrated in Figure 2.4. Effectively the cascade structure produces an output voltage which is a product of individual boost stages resulting in a higher static gain. By utilising the cascade structure each stage can achieve step-up function without extreme duty ratio operation, thus the conduction and switching losses are substantially reduced. The conduction loss of the first stage can be low, even though the input current is high. For the second stage, the input current is low due to the boost in voltage received from the intermediate bus voltage. However, the device voltage stress in the second stage is the same as the output voltage, and the reverse recovery loss of the output diode can be severe in high power applications. Another major drawback from the efficiency point of view is the energy is converted twice, which obviously has an impact on overall efficiency. Moreover, the interaction between the individually designed boost converters may cause instability in the

cascade converter from a small signal point of view [15].

Application of passive or active snubber cell to the cascade converter to implement (ZVS) for active switches as demonstrated in [36, 57], does not in any way improve the static gain of the original structure. The devices voltage stress usually remains the same with the original cascade structure despite (ZVS) soft switching performance.

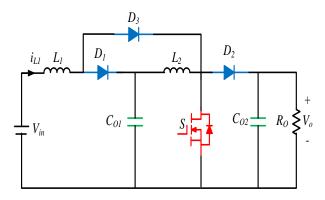

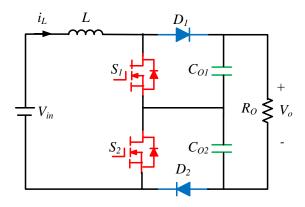

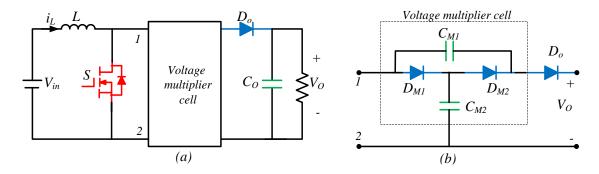

#### 2.3.2 Quadratic Boost Converter