# High Power Density AC to DC Conversion with Reduced Input Current Harmonics

# David Edward Grant

A thesis submitted for the degree of Doctor of Philosophy

School of Electrical and Electronic Engineering Newcastle University

March 2015

## Abstract

This thesis investigates the benefits and challenges arising from the use of minimal capacitance in AC to DC converters. The purpose of the research is to ultimately improve the power density and power factor of electrical systems connected to the grid. This is carried out in the context of a low cost brushless DC drive system operating from an offline power supply.

The work begins with a review of existing applications where it is practical to use a limited amount of DC link capacitance. The vast majority of these have a load which is insensitive to supply power variations at twice the line frequency. Low performance motor drives are found to be the most prevalent, with the inertia of the rotor mitigating the effect of torque ripple. Further research is carried out on active power factor correction techniques suitable for this application, leading to the conclusion that no appropriate systems exist.

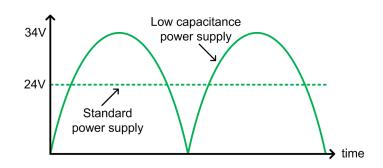

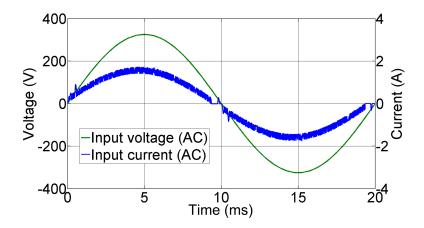

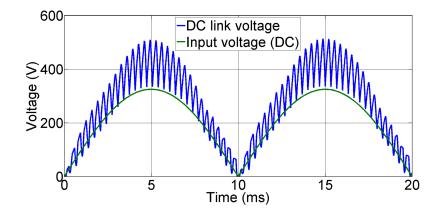

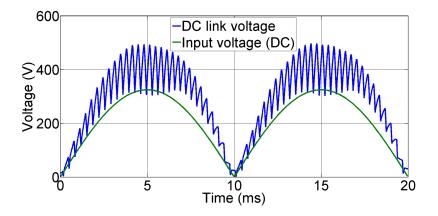

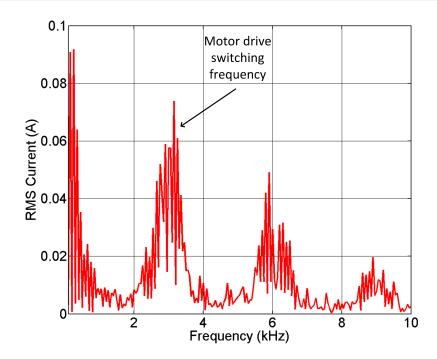

A power supply is developed to enable a 24V, 200W brushless motor drive to operate from the mains. The system runs successfully using only 1 $\mu$ F of DC link capacitance, which causes the motor supply voltage to have 100% ripple. It is noted that whilst this drastically reduces the low frequency input current harmonics, those occurring at the load switching frequency are greatly increased.

To combat this, a novel active power factor correction system is proposed using a notch filter to detect the input current error. The common problem of voltage feedback ripple is avoided by eliminating the voltage control loop altogether. The main limitations are identified as a high sensitivity to load step changes and variations in line frequency. Despite this, a high power factor is maintained in all operating conditions, as well as compliance with the relevant harmonic standards.

## Acknowledgements

My sincere thanks go to Dyson Technology Ltd and Newcastle University for the support and funding which made this research possible. I am particularly grateful for the contribution from my industrial supervisor, Steve Greetham, whose technical guidance and inspiration were critical to the success of this work. I am equally indebted to Chris Bateman for the significant input to the practical side of the project, as well as helping to make our office an enjoyable place to work. At Dyson I would also like to thank Tuncay Celik, Andy Clothier and everyone else who has helped me over the last four years.

Thanks to Barrie Mecrow for simultaneously fulfilling the roles of supervisor, mentor and mickey-taker. There is no doubt I am more receptive to sound academic advice when delivered with a good sense of humour. I'm especially thankful for the direction I received at the times when I was a little lost. I am also very grateful to Dave Atkinson for the support with the technical aspects of the research and for proofreading this thesis. Thanks as well for regularly waiting an inordinate amount of time for me to stop talking, before adding some valuable input to the discussion.

I'd like to thank everyone who has politely endured the insufferable tedium of my academic ramblings, whilst paying no regard as to their interest in the topic. In particular, to Clare who has heard the 'T' word more times than an emeritus professor and will be as glad as me on the hand in day.

Finally I would like to thank my parents, two people who had no direct involvement with the work, but could not have been more important in making it happen. Everything I have achieved has come through a lifetime of their support and encouragement; for this I will always be grateful.

# Contents

| 1        | Introduction |                                                                 |    |

|----------|--------------|-----------------------------------------------------------------|----|

|          | 1.1          | AC to DC Converters                                             | 1  |

|          | 1.2          | Reduced DC Link Capacitance                                     | 5  |

|          | 1.3          | Thesis Overview                                                 | 5  |

|          | 1.4          | Novel Aspects                                                   | 6  |

| <b>2</b> | A L          | iterature Review of Reduced Capacitance Power Systems           | 8  |

|          | 2.1          | Existing Applications for Reduced DC Link Capacitance           | 8  |

|          |              | 2.1.1 Three-Phase Motor Drives                                  | 8  |

|          |              | 2.1.2 Single-Phase Motor Drives                                 | 10 |

|          |              | 2.1.3 Battery Charging                                          | 13 |

|          |              | 2.1.4 LED lighting                                              | 16 |

|          |              | 2.1.5 Auxiliary Ripple Energy Storage                           | 21 |

|          | 2.2          | Capacitor Technology                                            | 23 |

|          | 2.3          | Power Factor Correction                                         | 25 |

|          |              | 2.3.1 Passive PFC                                               | 25 |

|          |              | 2.3.2 Active PFC                                                | 26 |

|          | 2.4          | Conclusion                                                      | 38 |

| 3        | The          | $\sim$ Reduced DC Link Capacitance Power Supply and Motor Drive | 40 |

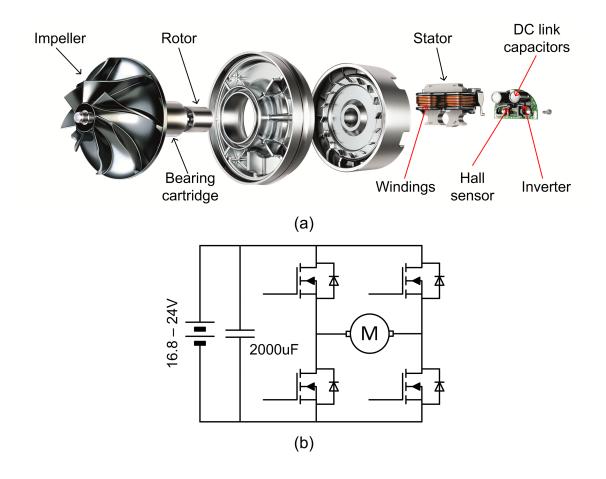

|          | 3.1          | The 200W 100,000RPM BLDC Motor Drive                            | 41 |

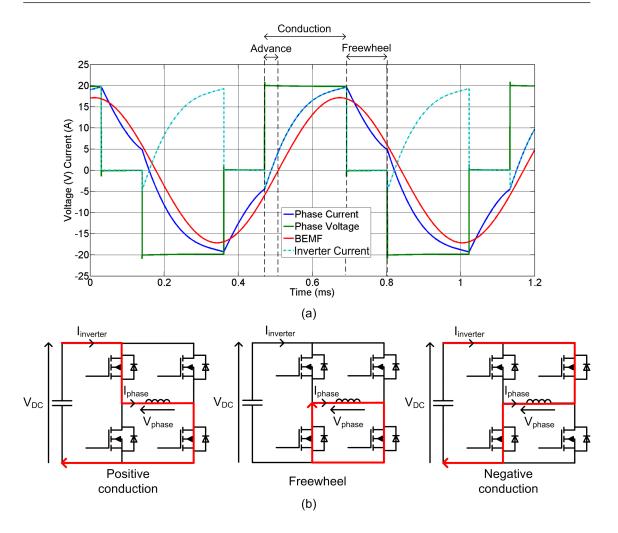

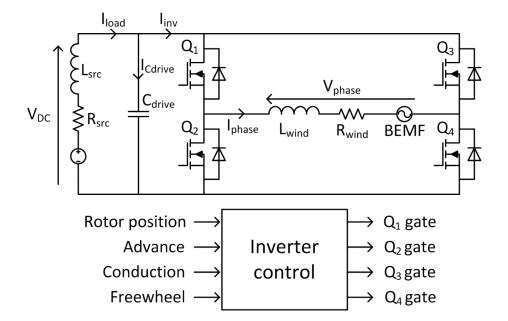

|          | 3.2          | 200W BLDC Motor Drive Simulation                                | 44 |

|          | 3.3          | Power Converter Design                                          | 50 |

|          |              | 3.3.1 Transformer Isolation                                     | 50 |

|          |              | 3.3.2 Transformer Design and Topology Selection                 | 54 |

|          | 3.4          | Power Supply Simulation                                         | 59 |

|          | 3.5          | Prototype Hardware                                              | 64 |

| 4        | Tes          | t Results and Validation of the Power System Simulation         | 67 |

|          | 4.1          | Power Supply Testing with a Resistive-Inductive Load            | 67 |

### CONTENTS

|          | 4.2   | Power Supply Testing with a BLDC Motor Drive                       | 71   |

|----------|-------|--------------------------------------------------------------------|------|

|          | 4.3   | Power Supply Testing with a Zero Capacitance BLDC Motor Drive .    | 78   |

|          |       | 4.3.1 Motor Drive Conduction Angle Modulation                      | 85   |

|          | 4.4   | Power Supply Simulation with a Conventional Smooth DC Link Voltage | e 90 |

|          | 4.5   | Power Supply Switching Loss Analysis                               | 97   |

|          | 4.6   | Conclusion                                                         | 102  |

| <b>5</b> | AP    | FC Control System Design                                           | 104  |

|          | 5.1   | Filter Energy Storage                                              | 104  |

|          | 5.2   | Active Filter Hardware Design                                      | 108  |

|          | 5.3   | Active Filter Control System Design                                | 110  |

|          |       | 5.3.1 Fixed Reference APFC                                         | 111  |

|          |       | 5.3.2 Filter-Based APFC                                            | 126  |

|          | 5.4   | Conclusion                                                         | 138  |

| 6        | AP    | FC Hardware Design                                                 | 140  |

|          | 6.1   | Current Sensor Design                                              | 140  |

|          | 6.2   | Analogue vs. Digital Implementation                                | 141  |

|          | 6.3   | Analogue Control System Design                                     | 142  |

|          |       | 6.3.1 Mains Polarity Detector                                      | 142  |

|          |       | 6.3.2 DC to AC Current Sense Modulator                             | 144  |

|          |       | 6.3.3 Shunt Differential Amplifier                                 | 145  |

|          |       | 6.3.4 Notch Filter                                                 | 147  |

|          |       | 6.3.5 Hysteresis Controller                                        | 150  |

| 7        | AP    | FC Hardware Test Results                                           | 153  |

|          | 7.1   | Control System Bandwidth                                           | 153  |

|          | 7.2   | Low Attenuation APFC Results                                       | 156  |

|          | 7.3   | High Attenuation APFC Results                                      | 161  |

|          | 7.4   | Line Frequency Variation                                           | 165  |

|          | 7.5   | Load Shutdown                                                      | 169  |

| 8        | Cor   | nclusions                                                          | 174  |

|          | 8.1   | New Knowledge                                                      | 176  |

|          | 8.2   | Further Work                                                       | 179  |

|          | 8.3   | Closing Remarks                                                    | 180  |

| R        | efere | nces                                                               | 190  |

## List of Symbols and Abbreviations

| $I_{load}$   | Load current                   |

|--------------|--------------------------------|

| $N_{phase}$  | Phase number                   |

| $f_{supply}$ | Supply frequency               |

| $C_{DC}$     | DC link capacitance            |

| $V_{DC}$     | DC link voltage                |

| $V_{ripple}$ | DC link voltage ripple         |

| $V_{AC}$     | AC supply voltage              |

| $I_{AC}$     | AC supply current              |

| $P_{in}$     | Input power                    |

| $I_{DC}$     | DC input current               |

| $\hat{V}$    | Supply voltage amplitude       |

| $\hat{I}$    | Supply current amplitude       |

| $L_{out}$    | Output filter inductor         |

| $V_{batt}$   | Battery voltage                |

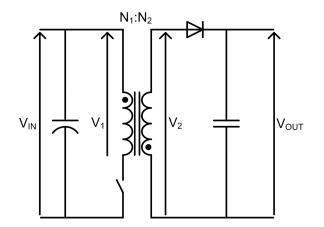

| $V_{in}$     | DC input voltage               |

| $E_C$        | DC link capacitor energy       |

| $P_{in}$     | Input power                    |

| $P_{out}$    | Output power                   |

| $I_{ref}$    | Reference current              |

| $V_{ff}$     | Voltage feedforward            |

| $V_{ea}$     | Voltage error amplifier output |

| $V_{ref}$    | Voltage reference              |

| $I_{in}$     | DC input current               |

| $V_{out}$    | Output voltage                 |

| i            | Current                        |

| t            | Time                           |

| $I_{comp}$   | Compensation current           |

| $I_{load}$   | Load current                   |

| T            | Torque                                     |

|--------------|--------------------------------------------|

| E            | Voltage                                    |

| R            | Resistance                                 |

| $\theta$     | Angle                                      |

| L            | Inductance                                 |

| $V_{phase}$  | Phase voltage                              |

| $R_{src}$    | Source resistance                          |

| $L_{src}$    | Source inductance                          |

| $I_{phase}$  | Phase current                              |

| $L_{wind}$   | Winding inductance                         |

| $R_{wind}$   | Winding resistance                         |

| $C_{drive}$  | Motor drive capacitance                    |

| $I_{inv}$    | Inverter current                           |

| N            | Number of turns                            |

| f            | Frequency                                  |

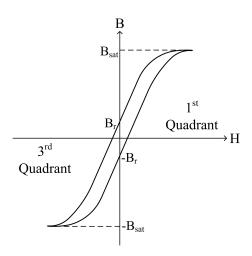

| $B_{sat}$    | Saturation flux density                    |

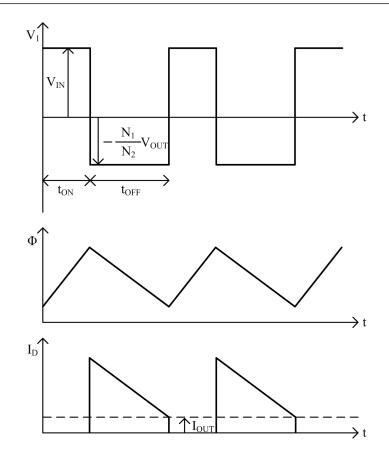

| D            | Duty cycle                                 |

| $R_{DS(on)}$ | Conducting drain-source channel resistance |

| В            | Flux density                               |

| H            | Magnetic Field Strength                    |

| $f_{sw}$     | Switching frequency                        |

| $\hat{B}$    | Peak flux density                          |

| $B_r$        | Remanent flux density                      |

| $C_{src}$    | Source capacitance                         |

| $C_{out}$    | Output capacitance                         |

| $L_{out}$    | Output inductance                          |

| $L_{leak}$   | Leakage inductance                         |

| $V_{GS}$     | Gate-Source voltage                        |

| $V_{pri}$    | Primary winding voltage                    |

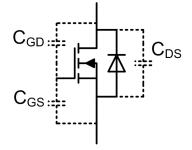

| $C_{GD}$     | Gate-drain capacitance                     |

| $C_{GS}$     | Gate-source capacitance                    |

| $C_{DS}$     | Drain-source capacitance                   |

| $C_{ISS}$    | MOSFET input capacitance                   |

| $C_{OSS}$      | MOSFET output capacitance            |  |

|----------------|--------------------------------------|--|

| $C_{pri}$      | primary winding capacitance          |  |

| $P_{sw}$       | Switching loss                       |  |

| $P_{COSS}$     | Parasitic capacitance switching loss |  |

| $I_{DS}$       | Drain-source current                 |  |

| $V_{DS}$       | Drain-source voltage                 |  |

| $t_{on}$       | Turn-on transition time              |  |

| $t_{off}$      | Turn-off transition time             |  |

| $P_{CPRI}$     | Primary winding capacitance loss     |  |

| $P_{cond}$     | Conduction loss                      |  |

| $P_{RR}$       | Reverse recovery loss                |  |

| $E_{filter}$   | Filter energy storage                |  |

| $P_{harmonic}$ | Harmonic power                       |  |

| $L_{boost}$    | Boost inductance                     |  |

| $\hat{V_{in}}$ | Peak input voltage                   |  |

| $I_{ripple}$   | Ripple current                       |  |

| $PF_D$         | Displacement power factor            |  |

| $f_{notch}$    | Notch filter tuned frequency         |  |

| AC     | Alternating Current                               |  |  |

|--------|---------------------------------------------------|--|--|

| DC     | Direct Current                                    |  |  |

| VSD    | Variable Speed Drive                              |  |  |

| ESR    | Equivalent Series Resistance                      |  |  |

| ESL    | Equivalent Series Inductance                      |  |  |

| LED    | Light Emitting Diode                              |  |  |

| RMS    | Root Mean Square                                  |  |  |

| EMI    | Electro-Magnetic Interference                     |  |  |

| IEC    | International Electrotechnical Commission         |  |  |

| PFC    | Power Factor Correction                           |  |  |

| IGBT   | Insulated Gate Bipolar Transistor                 |  |  |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |  |  |

| HVAC   | Heating Ventilation and Air Conditioning          |  |  |

| PWM  | Pulse Width Modulation            |

|------|-----------------------------------|

| DTC  | Direct Torque Control             |

| SVM  | Space Vector Modulation           |

| FOC  | Field Oriented Control            |

| CCCV | Constant Current Constant Voltage |

| SRC  | Sinusoidal Ripple Current         |

| DAB  | Dual Active Bridge                |

| APFC | Active Power Factor Correction    |

| ARES | Active Ripple Energy Storage      |

| PV   | Photo-Voltaic                     |

| MTBF | Mean Time Between Failures        |

| EMC  | Electro-Magnetic Compatibility    |

| CCM  | Continuous Conduction Mode        |

| DCM  | Discontinuous Conduction Mode     |

| FET  | Field Effect Transistor           |

| THD  | Total Harmonic Distortion         |

| APF  | Active Power Filter               |

| BLDC | BrushLess Direct Current          |

| RPM  | Revolutions Per Minute            |

| BEMF | Back ElectroMotive Force          |

| PCB  | Printed Circuit Board             |

| ADC  | Analogue to Digital Converter     |

| FFT  | Fast Fourier Transform            |

| PI   | Proportional-Integral             |

| GBP  | Gain Bandwidth Product            |

# Chapter 1

## Introduction

### **1.1** AC to DC Converters

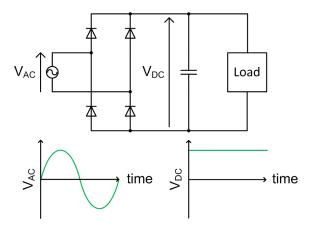

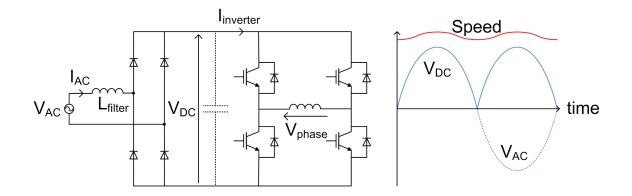

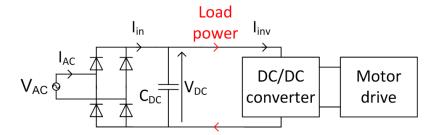

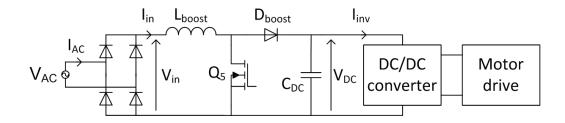

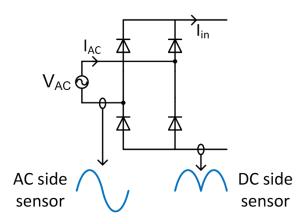

Many electrical systems which are connected to the mains cannot derive their power directly from an AC source. It is first necessary to convert this to a DC source, most commonly with a diode bridge rectifier and DC link capacitor as shown in Figure 1.1. These components can be found on the front end of consumer electronic products, Variable Speed Drives (VSDs) and computer power supplies among numerous other applications. Over time, the constant demand for new technology has vastly increased the number of these systems connected to the grid.

Figure 1.1: A single-phase AC to DC converter constructed from a diode bridge rectifier and smoothing capacitor

For a single-phase supply, AC to DC conversion entails the transformation of timevarying power to constant power. This process inherently requires energy storage to account for the short term imbalance between the input and output power of the system. When the magnitude of the AC voltage exceeds the DC voltage, the rectifier diodes are forward biased, allowing charge to flow into the capacitor and hence energy is stored. When the DC voltage exceeds the AC voltage, the rectifier diodes are reverse biased and the capacitor discharges, providing the sole source of energy for the load. This process of charging and discharging causes a ripple in the DC link voltage which is determined by four factors; the load current  $I_{load}$ , number of phases  $N_{phase}$ , supply frequency  $f_{supply}$  and DC link capacitance  $C_{DC}$ .

$$V_{ripple} = \frac{I_{load}}{2N_{phase} \cdot f_{supply} \cdot C_{DC}}$$

(1.1)

As the number of phases, supply frequency and average load current will be fixed for a given application, it is therefore necessary to have a large DC link capacitance in order to achieve a small ripple voltage. Whilst this is beneficial to the performance of the load, it has a negative impact on the volume and cost of the system. The intrinsic link between operating frequency and size has lead to DC link capacitance being the key limiting factor in AC to DC converter power density [1]. DC to DC converters are far superior in this respect as the operating frequency is chosen as part of the system design, constrained only by the limits of the components and control system. For mains connected loads requiring a constant supply voltage, improvements in capacitor technology offer the only significant method of reducing the size and cost of the AC to DC stage.

Electrolytic capacitors are the favoured devices for this purpose as they have a far greater energy storage density than electrostatic variants [2]. It is for this reason alone that they remain the popular choice for line frequency filtering applications. However, in almost every other respect they are inferior, suffering from high Equivalent Series Resistance (ESR) and Equivalent Series Inductance (ESL) coupled with a poor tolerance to temperature. Additionally, the liquid electrolyte used in their construction degrades over time, leading to failure rates almost two orders of magnitude higher than 'dry' capacitor variants [3]. This poses significant issues for power converters in long-term installations such as solar generators or LED lighting systems.

The combination of a large capacitor and a bridge rectifier leads to a further problem in the form of highly distorted input current. Due to the non-linear behaviour of the diodes, current can only be drawn from the supply when they are forward biased. As can be seen in Figure 1.2, a small DC link voltage ripple leads to a very short diode conduction period and subsequently a short spike of input current near the peak of the mains voltage. The non-sinusoidal current contains harmonics which do not contribute to the active power flow in the system, leading to a poor power factor, typically less than 0.7 [4].

Figure 1.2: Input current distortion caused by high DC link capacitance

Poor power factor and high current distortion have a number of side effects detrimental to the performance of the power network and the systems connected to it:

- 1. Voltage distortion resulting from the harmonic currents flowing through the impedance of the supply system.

- 2. Higher RMS current for a given real power, requiring over-rating of transformers, switchgear and cables making them larger and more costly; this is becoming a significant issue as the price of copper rises [5].

- 3. High frequency current pulses causing additional transformer heating, false tripping of breakers and skin effect in conductors.

- 4. Interference with sensitive equipment due to increased  $\frac{di}{dt}$  and therefore greater conducted/radiated Electro-Magnetic Interference (EMI).

- 5. Resonance and reactive power injection by harmonic filters [6].

In an effort to control these issues, IEC 1000-3-2, which sets limits on harmonic current emissions in equipment up to 16A per phase, was adopted as a European

Standard in 2001 (as EN 61000-3-2). This requires virtually all consumer and light industrial electrical equipment to be designed with consideration for its effect on supply current distortion [7]. The standard sets limits for individual harmonic magnitudes for the input current to a device, with the requirements varying depending on its classification.

The most significant of these requirements are the Class A limits as they cover the widest range of applications. These are shown in Table 1.1 along with the Class D limits applicable to devices "shown to have a pronounced effect on the public electricity system". The key difference between the Class A and Class D limits is that the former are given in absolute terms, whereas the latter are scaled by the active load power.

|                  | Class A                 | Class I                | )                       |

|------------------|-------------------------|------------------------|-------------------------|

| Harmonic order n | Current limit (A)       | Current limit $(mA/W)$ | Max current (A)         |

| 3                | 2.3                     | 3.4                    | 2.3                     |

| 5                | 1.14                    | 1.9                    | 1.14                    |

| 7                | 0.77                    | 1.0                    | 0.77                    |

| 9                | 0.4                     | 0.5                    | 0.4                     |

| 11               | 0.33                    | 0.35                   | 0.33                    |

| 13               | 0.21                    | 0.30                   | 0.21                    |

| 15 - 39 odd      | $0.15 \ge \frac{15}{n}$ | $\frac{3.85}{n}$       | $0.15 \ge \frac{15}{n}$ |

| 2                | 1.08                    | -                      | -                       |

| 4                | 0.43                    | -                      | -                       |

| 6                | 0.3                     | -                      | -                       |

| 8 - 40 even      | $0.23 \ge \frac{8}{n}$  | -                      | -                       |

Table 1.1: BS EN 61000-3-2 harmonic current limits

In order to meet these requirements, the conventional approach is to add a Power Factor Correction (PFC) circuit, using either passive or active filtering techniques. This allows for a reduction in input current harmonics whilst maintaining a constant DC output voltage; the penalty for this is a further increase in size and cost.

### 1.2 Reduced DC Link Capacitance

In response to the problems discussed previously, there has been growing academic and industrial interest in the design of power converters with reduced DC link capacitance. For certain applications, an acceptable performance can still be achieved when the DC link voltage, and subsequently the output power, has a very large ripple at twice the line frequency. This is always the case in single-phase AC systems such as heaters, incandescent lighting or induction motors, where the load responds to the average, rather than instantaneous value of the supplied power. For example, the 100Hz (or 120Hz) variation in input power to a heating element is not seen in its output as the thermal time constant prevents a significant change in temperature at this frequency. Similarly, the inertia of a universal or induction motor means that its speed will be relatively constant over one half-cycle of the mains, despite the large variation in torque. In these applications there is still energy storage present, but instead of a dedicated component such as a capacitor, it is the load itself which provides this function.

As discussed extensively in the next chapter, this same principle can be applied to DC loads which do not require constant power. By limiting the imbalance between the input and output power of an AC to DC converter, the energy storage requirement is reduced, leading to a potentially more compact and lower cost system. The increased DC link voltage ripple results in a longer conduction period for the rectifier diodes and subsequently a smoother input current with less harmonic content.

Whilst this concept and its benefits are clear, the new challenges it creates are not inconsiderable. By removing the decoupling between the supply and load, the subsystems become far more interdependent, with a change in one reflected immediately in the other. A holistic approach is required for the system design in order for it to function properly, with a greater consideration for the dynamic behaviour of the load and varying supply conditions. It is the study of this problem and its potential solutions which ultimately forms the key focus of this work.

### 1.3 Thesis Overview

This thesis begins with research into existing applications where the DC link capacitance is purposefully small. Compared to a conventional design, the DC link capacitance can be reduced by more than 99% in some cases, whereas in others it may be as little as 30%. However, in each case this is done for the purposes of improving size, cost, lifetime or harmonic performance. Particular attention is paid to the detrimental effects this has on load behaviour, along with the techniques used to mitigate them. A review of power factor correction techniques is included, which fundamentally concludes that no existing systems are suited for use with reduced DC link capacitance.

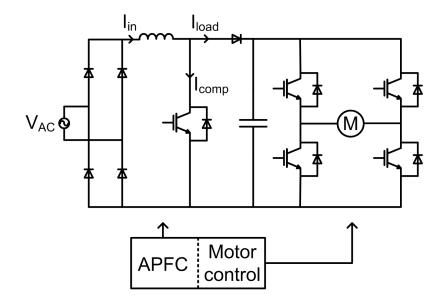

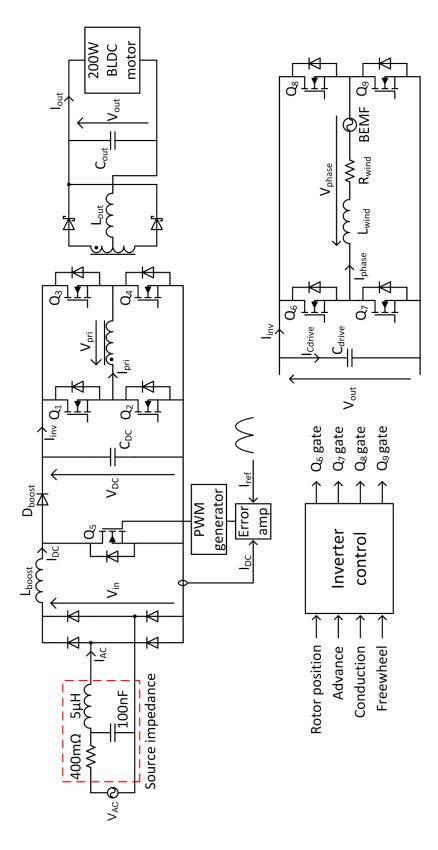

Low performance motor drives are found to be the main application for this concept, with considerable existing work by academics and the industrial sponsor for this research. A 200W 24V brushless DC motor drive is selected as the test load, requiring a DC to DC converter to provide the correct supply voltage. This provides another platform on which to analyse the effects of reduced DC link capacitance, particularly the loss of efficiency with an increasingly dynamic load.

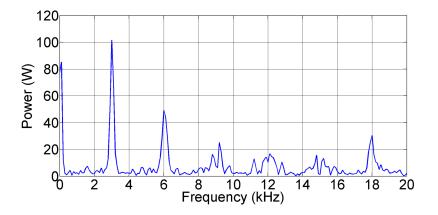

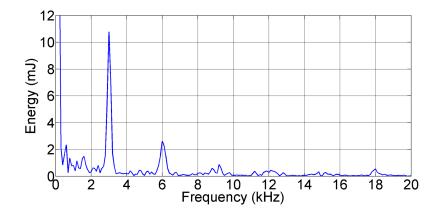

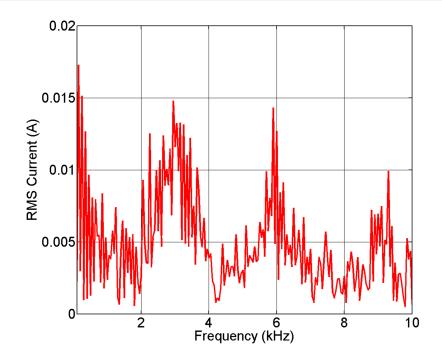

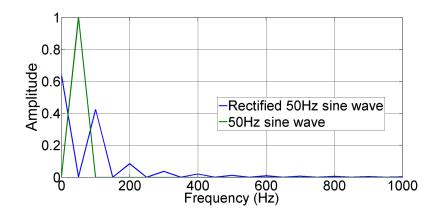

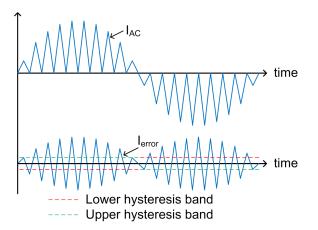

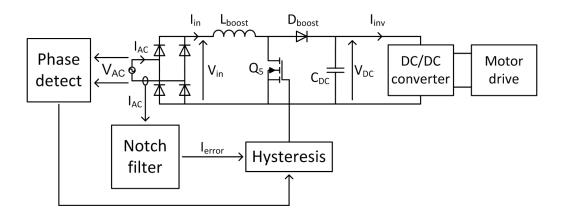

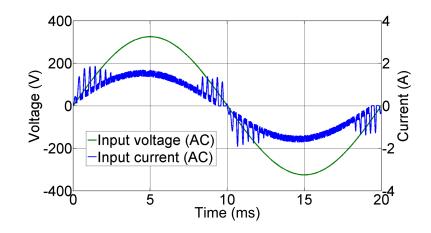

Load harmonics in the input current are identified as the key challenge of this application, leading to the development of a novel control system designed to attenuate them using the minimum amount of energy storage. Fundamental analysis of harmonic filtering is followed by the simulation of two different control methods for a boost converter front-end. The more successful technique based on notch filtering is implemented in hardware, with Chapter 6 covering the design process in detail.

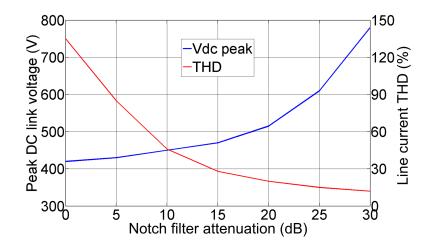

Finally, the system is tested over a range of operating conditions in order to thoroughly analyse its behaviour. The main performance limitations are shown to be an increased sensitivity to rapid load reductions and variations in supply frequency. Furthermore, an important compromise is noted between the level of harmonic attenuation achieved and the peak DC link voltage. Despite this, the controller is shown to maintain a power factor exceeding 0.9 even in worst case conditions, as well as meeting the more challenging scaled EN 61000-3-2 harmonic limits.

### 1.4 Novel Aspects

All of the research contained within this thesis stems from the idea that in certain power converter applications, an improvement in size, cost and power factor can be realised through a reduction in DC link capacitance. The challenge is in solving the new problems that occur when there is virtually zero decoupling between the different subsystems. The most significant contributions to knowledge are:

- 1. An active power factor correction system which does not require a reference current or voltage control loop, thus allowing it to work with 100% DC link voltage ripple. The input current error is extracted by a notch filter tuned to the supply frequency rather than by the subtraction of an ideal reference. A patent application covering this concept is currently being compiled by Dyson Technology Ltd.

- 2. An active power factor correction system which only attenuates the high frequency harmonic content of the line current, removing the need for a large DC link capacitor. This works in conjunction with an existing motor drive control strategy designed to produce minimal low frequency harmonics.

- 3. New research into the practical limits of minimising energy storage in low cost power supplies such as those found in domestic appliances or other applications with reduced performance requirements.

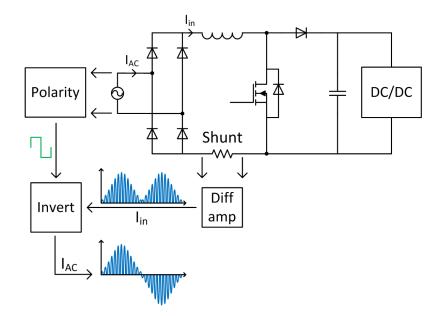

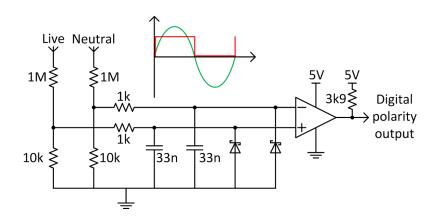

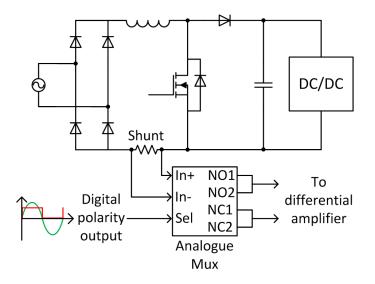

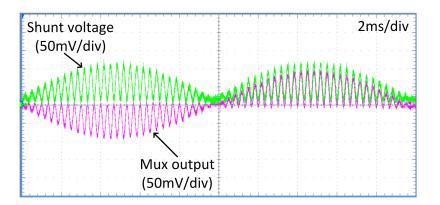

- 4. A novel current sensing system which provides a measure of the line input current by multiplying the DC link input current with the polarity of the input voltage. This provides the essential AC current signal necessary for extraction of the harmonic content without the additional distortion caused by the rectification process. By placing the current sensor after the bridge rectifier, a simple non-isolated shunt arrangement can be used, providing a very compact, low cost solution which can measure from DC into the MHz range. A patent application covering this circuit design is currently being compiled by Dyson Technology Ltd.

# Chapter 2

# A Literature Review of Reduced Capacitance Power Systems

This chapter reviews prior art in two key areas relevant to the work in this thesis. The first analyses existing power converter applications which make use of reduced DC link capacitance. This provides valuable insight into the challenges faced when designing such systems, one of which is load frequency distortion of the supply current. Subsequently this leads on to the second research area; power factor correction.

## 2.1 Existing Applications for Reduced DC Link Capacitance

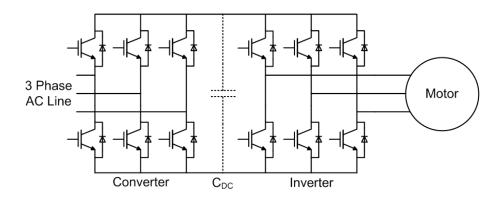

#### 2.1.1 Three-Phase Motor Drives

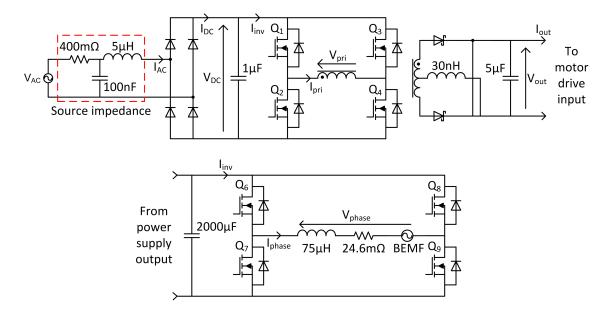

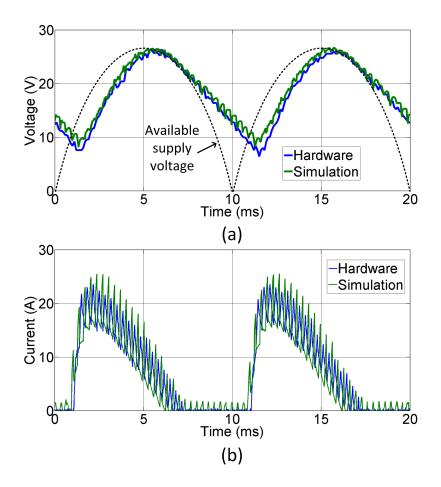

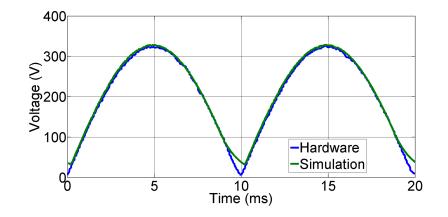

Research in this field has shown that the problems discussed in the previous chapter can be mitigated somewhat through the use of reduced DC link capacitance. Its main application is in three-phase converter/inverter drives (see Figure 2.1), where the problems caused by limited decoupling can be overcome [8–13]. These systems work on the principle that if the instantaneous input and output currents can be forced to the same value, no DC link energy storage is required. The dynamics of the control system determine the extent to which this can be achieved; a fast and accurate scheme will require minimal capacitance to cater for the imbalance between input and output currents [10]. It has been proposed by Kim and Sul [11] that the power device junction capacitance alone could be adequate, allowing one-chip AC-DC-AC power conversion. However, this is likely to be impractical as a sufficiently high speed voltage control loop would rapidly modulate the input current amplitude, causing distortion and subsequently a poor power factor. A clear parallel can be drawn between this system and a matrix converter, and would likely suffer from many of the same drawbacks.

Figure 2.1: three-phase converter/inverter with minimal DC link capacitance

Due to the nature of three-phase systems, it is possible to obtain an approximately constant power transfer if the load appears linear, unlike in single-phase systems where the power is inherently time varying. This is ideal in the case of a motor drive system where the load typically demands constant power.

A number of different converter control strategies have been developed with the aim of maintaining a constant DC link voltage whilst keeping the input power factor high. Kim and Sul [11] use a power estimator technique based on the load and system losses to predict the active power required from the input. A space-vector based current controller is used for rapid control of the source and load side currents. Malesani *et al.* [10] use actual DC link current measurements to generate a feedforward compensation term to speed up the system response. There are however a number of problems associated with DC link current measurement, most significantly the additional stray inductance caused by the sensor itself [9] and the need for a low pass filter due to the switching noise on the link. A low pass filter will introduce delay into the system, limiting the speed of the current regulation. Due to the importance of current control bandwidth, other techniques have been employed such as deadbeat control [14], direct capacitor current control [8] and feedback linearisation [9].

Whilst exhibiting good performance in terms of both input and output current quality, such converter/inverter systems suffer from high cost and complexity. An alternative solution is to use an uncontrolled rectifier for AC/DC conversion, using

diodes rather than active devices such as IGBTs or MOSFETs. Andersen et al. [15] present a reduced capacitance AC drive intended for HVAC (Heating Ventilation and Air Conditioning) applications. The application is critical to the feasibility of the reduced capacitance drive system, as HVAC involves fan-type loads which can tolerate a certain degree of torque ripple. The performance requirements in terms of efficiency, acoustic noise and harmonic distortion however are high. For a full wave rectified three-phase voltage, the maximum theoretical DC link ripple is  $1 - \frac{\sqrt{3}}{2} \approx 13\%$ , which will be seen if no DC link capacitance is used. As discussed previously, there is essentially no voltage hold-up in a reduced capacitance converter and so the full ripple voltage will be seen by the inverter. The output current will subsequently contain a 300Hz component (6 times the line frequency) which will produce a corresponding torque ripple. In the work carried out by Andersen et al. [15] a 12% torque ripple is seen due to this effect. For a fan load, this is not a problem unless the 300Hz modulation is audible. If smoother torque is required, the voltage ripple can be compensated for by modulating the PWM in anti-phase with the voltage. Upon implementing this technique, a 50% reduction in torque ripple was seen.

Similar work has been carried out by Kretschmar and Nee [16], but without torque ripple compensation. The inverter produced an almost pure sinusoidal current wave-form despite the use of an open loop control system; this is most likely due to the higher motor frequency and simulated line inductance used during the tests. It is worth noting that line impedance is an often overlooked factor when considering the harmonic performance of a device, yet its effects can be significant. A highly inductive supply line is equivalent to adding a dedicated AC choke, and will therefore attenuate harmonics considerably.

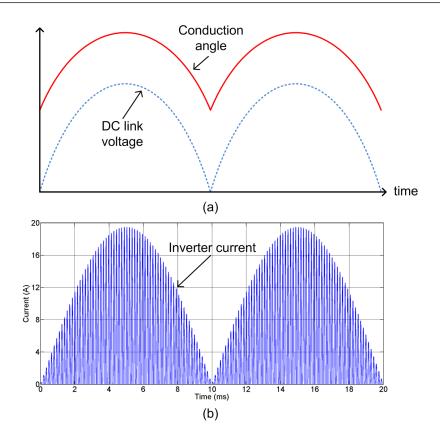

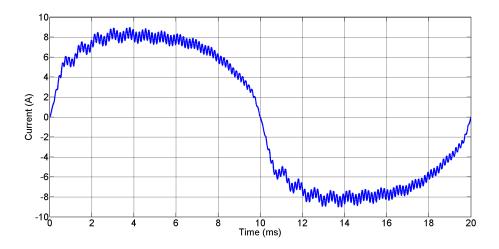

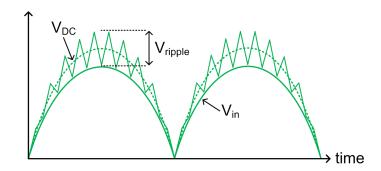

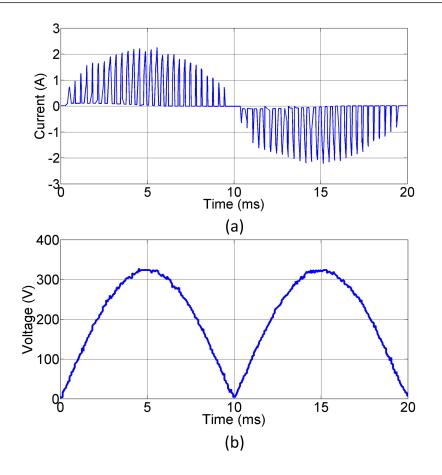

### 2.1.2 Single-Phase Motor Drives

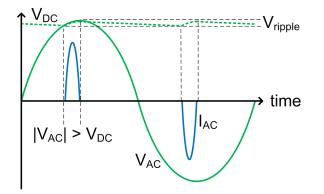

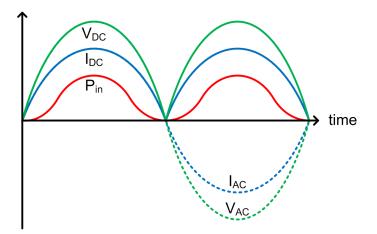

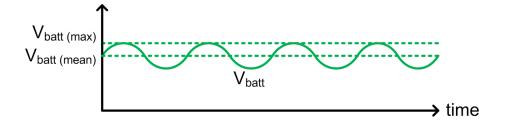

For single-phase systems the performance limitations resulting from a low capacitance DC link are much more severe, and therefore the intended applications must be carefully considered. This is due to the 100% ripple voltage observed when there is no DC link energy storage present. As with three-phase systems, the main application is in motor drives, where the inertia of the load mitigates the effect of torque ripple [17–23]. As shown in Figure. 2.2, a single-phase linear load will draw power in a time varying fashion. Assuming the load is linear, the input power varies as a function of  $sin^2$ , as shown in Equation. 2.1.

Figure 2.2: Ideal DC link voltage, current and input power waveforms for a singlephase load

$$P_{input} = \hat{V}\hat{I}sin^2(\omega(t)) \tag{2.1}$$

Given that there is no decoupling available, the output power must therefore vary in the same manner, at the same time. Such oscillations in output power have long been accepted in domestic appliances through the use of universal motors, which can be found in products such as drills, vacuum cleaners and food processors. When combined with new brushless motor technology, this property can be capitalised on for improvements in power density, harmonics, efficiency and product lifetime.

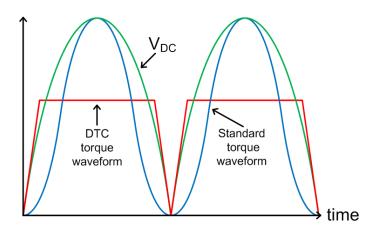

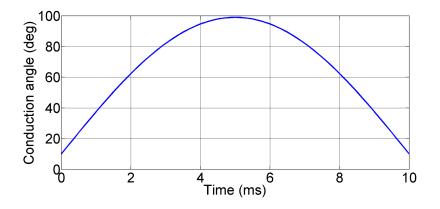

Whilst it is possible to run a low capacitance drive using basic PWM control, its performance can be improved through the use of more advanced modulation techniques, as in a conventional drive system. As outlined in [22] and [17] Direct Torque Control (DTC) can be effective where a heavily fluctuating inverter supply exists. DTC allows the motor variables of flux and torque to be controlled directly by making calculations based on the measured motor voltage and current. The estimated flux and torque values are compared with a reference, and an error compensation is made by the inverter if they lie outside a set tolerance band. This works well with

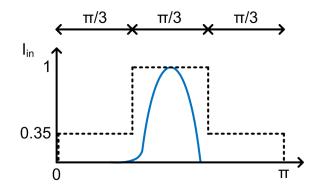

a fluctuating DC link voltage, as the controller simply increases the power device conduction times as the voltage drops. For the majority of the mains cycle, full motor torque can be maintained by compensating for the voltage ripple, resulting in a trapezoidal torque profile as shown in Figure 2.3. Once the voltage falls below a certain point, the stator flux linkage cannot be maintained and the torque drops off. This is not a problem however, as excessive DC link voltage compensation will result in high distortion of the input current, causing the system to become self-defeating.

Figure 2.3: Trapezoidal torque profile resulting from DC link voltage compensation

DTC is a form of hysteresis control, and subsequently has a variable switching frequency. This complicates harmonic filtering and can induce resonances between the small DC link capacitor and line inductance. If this poses a particular problem, fixed-frequency techniques such as Space Vector Modulation (SVM) can be used instead, with the operating frequency set above the resonance [22]. The rapid integration and vector multiplication make DTC computationally intense, but given the speed of modern microcontrollers this is no longer an issue except in extremely cost sensitive applications.

Haga *et al.* [17] make use of the dither effect combined with DTC to simultaneously control the input current waveform and motor torque. Dither is a technique used to linearise non-linear systems by intentionally adding noise to a signal, in this case the converter input current. The inverter switching signals have a high frequency (dither) component superimposed on the motor control signals. The dither component is controlled such that it causes a sinusoidal input current to be drawn when passed through a low pass filter. Due to the frequency of the signal, the presence of

the small DC link capacitor is sufficient, removing the need for an AC input filter. The system behaves somewhat like a combined converter/inverter, but achieves input and output current control using a single power stage. Due to its linearisation properties, the dither effect can be applied to systems with a conventional DC link as demonstrated by Cacciato *et al.* [4].

As an alternative to DTC, Lamsahel and Mutschler [23] propose the use of Field Oriented Control (FOC) in low capacitance drives for domestic appliances. FOC is simpler to implement and has a fixed switching frequency, allowing the use of basic microcontrollers which results in lower cost products. A basic FOC system can successfully control a low capacitance drive, but the resulting motor torque has a high harmonic content. An improvement is seen when the D and Q axis current reference values are modulated by the DC link voltage. Although the input current is significantly more distorted than in [17], full compliance with BS EN 61000-3-2 is still achieved. This example reiterates the key challenge with reduced capacitance drive systems, in that torque ripple and input current distortion are in constant contention; a reduction in one results in an increase in the other.

### 2.1.3 Battery Charging

Another potential application for low DC link capacitance is battery charging, inviting the possibility of a combined power supply/fast charger sharing the same hardware. The key to making this work is sinusoidal modulation of the load (charging) power, in much the same way as it is with a motor drive. A similar challenge is presented, as conventional charging techniques often use a Constant Current Constant Voltage (CCCV) approach, producing a constant power load [24].

Due to their high energy density, lithium-ion cells form the basis for batteries in a vast range of products, from electric vehicles to mobile phones. This has naturally lead to research into understanding and improving the charging process [24–26], with a particularly relevant conclusion for this application; Sinusoidal Ripple Current (SRC) charging above 10Hz does not degrade the performance or lifetime of the cells. Furthermore, Chen *et al.* [24] demonstrated that by charging at the minimum AC impedance frequency, the cell temperature, lifetime and charging efficiency were notably improved over CCCV methods.

An important difference between a battery charger and a motor load is that whilst they can both tolerate large ripple currents, lithium ion cells require a tightly controlled charging voltage. This is a difficult problem to overcome in a system with minimal DC link capacitance and a high input power factor requirement. The expected 100% DC link voltage ripple seen in Figure 2.2 would be damaging if it was passed through to the cells, so a more elaborate power control method is necessary.

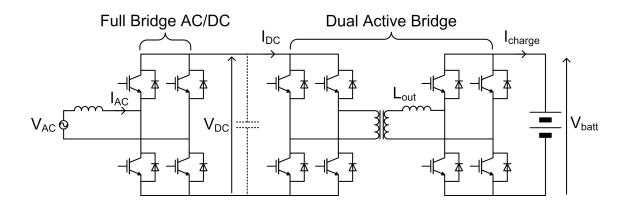

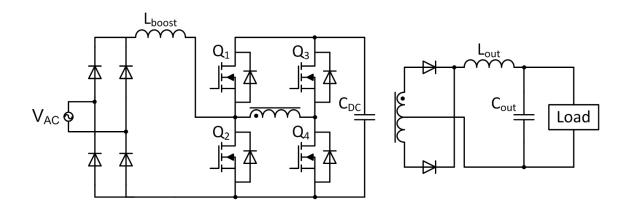

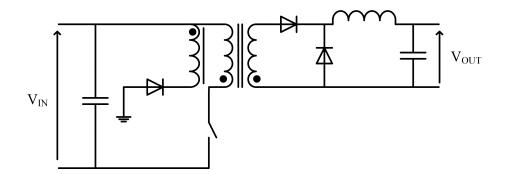

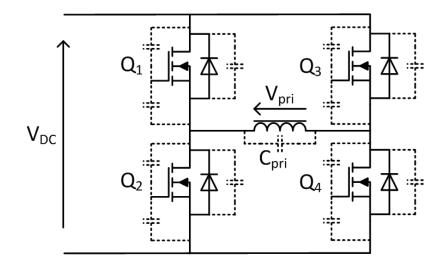

Research by Rosekeit and DeDonker [27] and Xue *et al.* [28] proposes a constant voltage sinusoidal ripple current charging technique which results in a very high input power factor from a compact converter design. Low value film capacitors are used in place of large electrolytics, saving valuable space and increasing the system lifetime, particularly important issues in the electric vehicle application. The chargers use a two stage approach as shown in Figure 2.4, with the full bridge front end providing power factor correction and DC link voltage regulation, and the Dual Active Bridge (DAB) providing charging current control.

Figure 2.4: Battery charger with Full Bridge AC/DC stage and Dual Active Bridge DC/DC stage

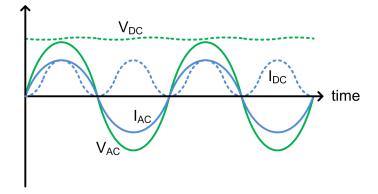

Much like the low DC link capacitance motor drives discussed in Section 2.1.2 and 2.1.1, the charger uses the concept of instantaneously balanced input and output power to minimise the required energy storage. As the system is single-phase, this means the output power must vary sinusoidally, but without significant modulation of the charging voltage. The only option therefore is to force the charging current,  $I_{charge}$ , to have a sinusoidal component in phase with the converter input power as shown in Figure 2.5. Due to the transformer  $I_{charge}$  is equal to  $I_{DC}$  multiplied by the turns ratio.

Figure 2.5: Key waveforms of the two stage low DC link capacitance charger

The input and output current control loops have a high bandwidth to ensure a significant imbalance does not occur, as this would produce a large fluctuation in the DC link voltage through the subsequent charging or discharging of the DC link capacitor. Theoretically, if the control system was fast enough the DC link capacitor would not be necessary other than to filter the power device switching noise, and would consequently be extremely small. In a realistic design such as [27] or [28], a certain amount of DC link voltage ripple will be produced however.

The dual active bridge is combined with  $L_{out}$  to produce current source behaviour, giving a predictable enough output to allow open loop control if desired. On the other hand it is noted in [28] that a larger current error is produced, requiring a larger DC link capacitor to account for the greater power imbalance. The error stems from the slightly nonlinear relationship between DAB phase shift (i.e. angle between inverter and rectifier bridge switching waveform) and output current.

A limitation of sinusoidal ripple current charging is that the mean charging power has to be reduced slightly to prevent over-voltage damage to lithium ion cells. The varying charge current will produce a corresponding voltage ripple due to the internal impedance of the cells, and the peak of this voltage cannot be allowed to go above a maximum value. So rather than charging constantly at the maximum allowable voltage, a reduced mean value must be used as shown in Figure 2.6.

Figure 2.6: Reduction in mean charging voltage to prevent cell damage (exaggerated)

Despite the more stringent voltage regulation issue, battery charging lends itself well to the low DC link capacitance concept for two key reasons. Firstly, it presents a reasonably linear and constant load such that the converter input power always has a sink, and therefore does not require storage in reactive components. The second advantage is that the load time constant of a battery is very long, meaning that the reference value for the current control loop will subsequently change very slowly, helping to prevent second harmonic distortion of the line input current through changes in load behaviour [27]. This is the same reason that conventional Active Power Factor Correction (APFC) systems have a very slow voltage control loop (<20Hz), a point which is discussed further in section 2.3.2.

#### 2.1.4 LED lighting

The use of LED lighting over conventional incandescent/fluorescent sources is becoming more popular as the technology is improved. There are a number of factors behind this, the most significant being high efficiency and increased lifetime. The most significant drawback is the low voltage DC operation and thus the need for a power supply which matches the performance of the LED modules themselves. Given the lifetime of LEDs is in the order of 50,000 to 100,000 hours this poses a problem for power supplies using electrolytic capacitors which will typically fail much sooner than this [29,30]. In response to the problem, research has been carried out [29–32] into the reduction of DC link capacitance such that longer lifetime 'dry' capacitor topologies can be used.

Unlike certain motor drive and battery charging applications, it is not desirable to have a  $sin^2$  fluctuation in power with LED lighting due to the flicker effect this produces, and subsequently a large net reduction in energy storage is not possible. Despite the fact that conventional lighting systems produce flicker at twice the line frequency (i.e. 100Hz in Europe), the effect is less severe due to the long load time constant. The brightness of an incandescent bulb does not vary significantly over one half cycle of the mains, and so the flicker it produces is equally small. This is analogous to the inertia of a motor preventing 100Hz modulation of its power from producing a noticeable variation in speed (discussed in section 2.1.2). LEDs on the other hand have virtually no load time constant and will produce a light output proportional to the instantaneous driving current, giving them a 'flicker depth' of 100% if driven from a sinusoidally varying power supply [33]. This means that over one half cycle of the mains, LEDs will transition from zero output to full output and back again. Although it is accepted that humans can only perceive light flicker up to approximately 70Hz, prolonged exposure to higher invisible frequencies can be detrimental to health, causing headaches, migraines and reduced visual performance [33].

The four power supply designs discussed in this section all get round the problem by using a large filter capacitor on the converter output, where the low voltage enables the use of long lifetime devices with a relatively high capacity. This removes the second harmonic ripple from the output, driving the LEDs with constant current and thus eliminating flicker. The high voltage DC link is still designed to have a large (but not 100%) ripple, requiring minimal capacitance which subsequently enables the use of film [30–32] or ceramic [29] devices instead of electrolytics. An advantage that LED power supplies have over other reduced capacitance converters is that their power rating is normally very low, meaning that less capacitance is required for a given DC link voltage ripple. For example, a 13.5W converter is designed in [32] with a 3uF DC link capacitance, small enough to allow a film device to be used. However, when the very low power (and therefore load current) of the system is considered, it can be seen that in a relative sense this is a significant amount of energy storage.

Due to the constant power output, all of the designs require an APFC stage to overcome the severe input current distortion that would otherwise result. The active shaping of the input current increases the short term imbalance between input and output power, causing a proportional increase in DC link voltage ripple. As identified by Gu *et al.* [30], the operational stability of the system is limited to the point at which the DC link voltage becomes smaller than the input voltage; an issue with any boost-derived topology. This is normally an unlikely scenario, as a conventional DC link design provides sufficient decoupling to safely limit the voltage ripple. In this case however, the voltage on the DC link capacitor can change rapidly, potentially pushing the boost converter outside of its operating range, resulting in loss of input current control.

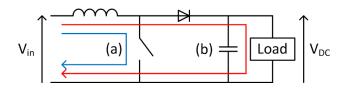

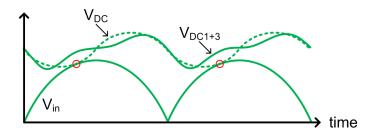

The reason for this is down to the fact that a boost converter can only provide uni-directional current control. By referring to Figure 2.7 it can be seen that the input current can always be increased by closing the switch (Figure 2.7 (a)) but it cannot necessarily be decreased by opening the switch (Figure 2.7 (b)) due to its parallel connection with the load. If the output voltage of the converter,  $V_{DC}$ , is less than the input voltage,  $V_{in}$ , then the load will draw current directly from the input rather than the capacitor. Under this condition the input current will be unregulated, resulting in distortion and therefore reduced power factor. If  $V_{DC}$  can be maintained above  $V_{in}$ , opening the boost switch will always cause the input current to fall, allowing total control of the input current shape. The boundary condition for stability is shown in Figure 2.8.

Figure 2.7: Uni-directional current control limitation of a boost converter PFC circuit

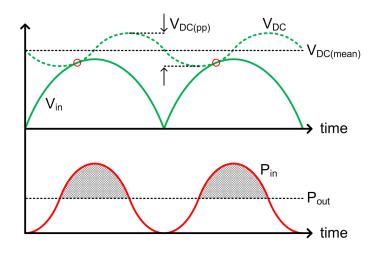

Figure 2.8: Stability limit for boost converter operation and DC link capacitor energy storage cycle

Three solutions to the boost converter instability issue are proposed. The first is to increase the mean capacitor voltage,  $V_{DC(mean)}$ , such that a given ripple magnitude,  $V_{DC(pp)}$ , cannot cause an intersection between  $V_{DC}$  and  $V_{in}$ . This can be achieved by increasing the mean duty cycle of the boost converter without altering the shape of the modulation waveform. The downside of this approach is increased stress on the components and a potential increase in cost if higher rated devices are necessary.

The second option is to reduce the ripple voltage by limiting the input-output power imbalance. As can be deduced from Figure 2.8 and 2.7, the integral of  $P_{in} - P_{out}$ is equal to the change in DC link capacitor energy  $\Delta E_c$  (the boost inductor stores a minimal amount of energy in comparison). The shaded area where  $P_{in} > P_{out}$  is equal to the energy stored by the capacitor, and the area where  $P_{in} < P_{out}$  is equal to the energy released. If the input power is allowed to move away from the ideal  $sin^2$  shape towards the constant value of the load,  $\Delta E_c$  will be reduced giving a corresponding reduction in the ripple voltage. The obvious downside of this approach is the input current will no longer be sinusoidal, decreasing the power factor.

$$E_c = -\frac{1}{2}CV^2 \tag{2.2}$$

$$\Delta E_c = \int P_{in} - P_{out} \, \mathrm{d}t \tag{2.3}$$

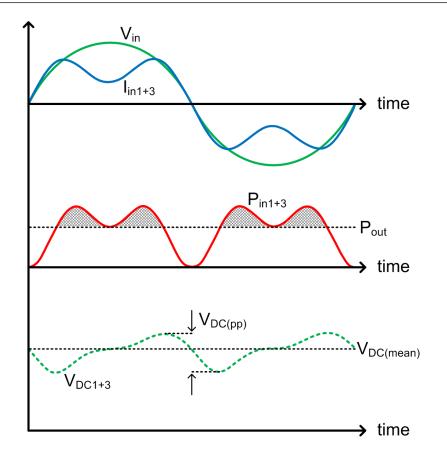

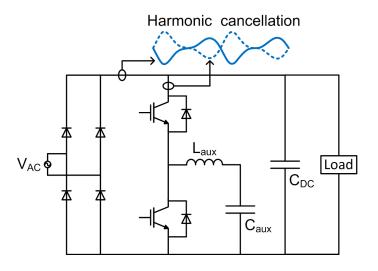

The final and most complex option is put forward by Gu *et al.* [30], and involves injection of a 3rd harmonic component into the input current. Whilst this will clearly have an impact on power factor, it allows a greater level of voltage ripple before  $V_{in}$ intersects  $V_{DC}$ . By adding a 3rd harmonic signal to the APFC reference current, the input current and DC link voltage will be modulated in a corresponding fashion as shown in Figure 2.9.

Figure 2.9: Modulation of  $I_{in}$ ,  $P_{in}$  and  $V_{DC}$  with 3rd harmonic injection

Figure 2.10 shows that the 3rd harmonic component does not reduce the magnitude of the ripple voltage, but instead shifts the  $V_{DC}$  minimum point such that an intersection with  $V_{in}$  is avoided. The results in [30] show that for a given DC link voltage, the DC link capacitor can be reduced in size by 34% over a system without 3rd harmonic injection. This allowed the 60W converter to use a 2µF DC link capacitor where a 3µF device was previously required. The penalty for this improvement is a reduction in power factor from 1 to 0.9 due to the 3rd harmonic.

Figure 2.10:  $V_{DC}$  comparison showing the increased ripple voltage limit through 3rd harmonic injection

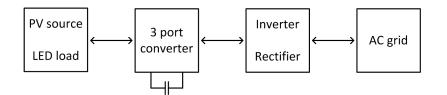

### 2.1.5 Auxiliary Ripple Energy Storage

The final application area for reduced DC link capacitance is in converters with an Auxiliary Ripple Energy Storage (ARES) system. Unlike the other applications discussed previously, converters with ARES can have small film based DC link capacitors without having to compromise on the DC side performance or introduce distortion to the AC side [3]. The advantage of such a system is best demonstrated by the poor energy utilisation of a conventional DC link capacitor. As described by Equation 2.3, the change in capacitor energy,  $\Delta E_c$ , is equal to the difference between the input and output energy of the converter (i.e. integral of the power difference over time). In an ideal case the capacitor would be just big enough to store the peak input/output energy imbalance such that it is completely charged and discharged over every half cycle of the mains. This represents the theoretical minimum energy storage requirement, and thus the minimum capacitor size.

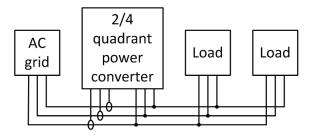

The difficulty with this is that a change in energy implies a change in voltage for a capacitor (see Equation 2.2), creating DC link voltage ripple which is unsuitable for many converter loads. If a small DC link voltage ripple is desired, then a small relative change in energy takes place as energy is proportional to voltage<sup>2</sup>. For example, a DC link capacitor with a mean voltage of 400V and a ripple of 10V peak-peak has a relative energy change of 5% over half a mains cycle, meaning that 95% of the stored energy is unused. To overcome this issue an ARES converter is proposed in [3, 34–37] which involves storing the ripple energy in a capacitor which is not directly connected to the DC link, allowing its voltage to vary without affecting the DC link voltage. The auxiliary capacitor can therefore be much smaller than the equivalent conventional DC link capacitor. As shown in Figure 2.11, this system can be applied in situations where the mains is either the source (e.g. LED ballast) or the load (photovoltaic generator), and is particularly useful where long converter lifetimes require the use of film capacitors.

Figure 2.11: Auxiliary Ripple Energy Storage system block diagram

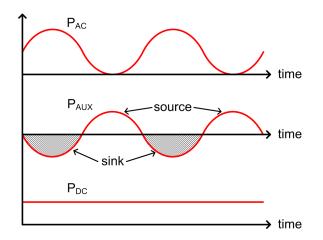

$$P_{aux} = P_{DC} - P_{AC} \tag{2.4}$$

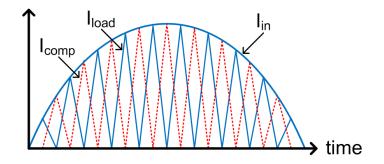

Figure 2.12: Waveforms showing the AC, DC and auxiliary power flow in the three port converter

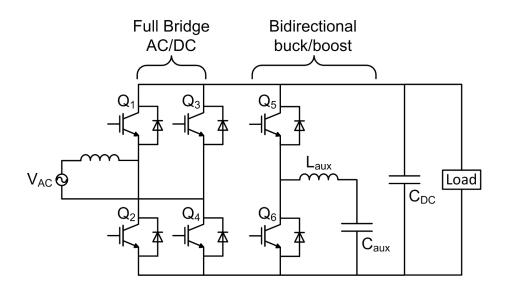

The simplest implementation of the ARES converters proposed in [3,34,36,37] is put forward by Wang *et al.* [36], and can be seen in Figure 2.13. The auxiliary capacitor is connected to the DC link via a bidirectional buck/boost converter, allowing it to store energy when  $P_{AC} > P_{DC}$  and release energy when  $P_{AC} < P_{DC}$ . Through appropriate modulation of switches Q<sub>5</sub> and Q<sub>6</sub>, a stable DC link voltage can be produced from a heavily rippling auxiliary capacitor voltage. The DC link capacitor  $C_{DC}$  is small as it only serves to filter the power electronic switching noise from the buck/boost converter and provide a buffer for error in the ARES control.

In theory this arrangement allows the absolute minimum capacitor energy/size to be used as defined by Equation 2.3. For the design in [36] requiring 4% peak-peak ripple, this leads to a capacitor size reduction of 12.5 times over that of a conventional DC link set-up (1.6mF to 125 $\mu$ F). In practice this cannot quite be achieved due to limits on the auxiliary capacitor ripple current and the maximum converter duty cycle. It becomes impossible for the buck/boost converter to maintain a constant output voltage when the input (auxiliary capacitor) voltage becomes very small due to the extremely high duty cycle required. 200 $\mu$ F was found to be the practical minimum to maintain a 4% peak-peak ripple, a reduction of 8 times from the 1.6mF required with a conventional design. Use of the ARES converter in this case lead to an overall power density increase of 100% for the PWM rectifier and enabled the use of long lifetime film capacitors where electrolytic devices would otherwise have been necessary.

Figure 2.13: ARES converter topology used in [36] with full bridge APFC front end

### 2.2 Capacitor Technology

As discussed previously, reducing DC link capacitance can have a number of benefits when film based devices are employed. Recent improvements have made these capacitors suitable for high voltage, high ripple current applications such as the DC link of an offline power supply where electrolytic devices have traditionally been used.

As polypropylene capacitors have no electrolyte they do not suffer from 'dry-out' issues, and are also self healing, as faults are removed through vaporisation of the electrode in the region of the short. This provides a significant advantage for many power electronic systems as electrolytic capacitors will normally be the first components to fail, often in short-circuit which creates a high risk of explosion [19, 38]. It is for these reasons that film based capacitors exhibit failure rates almost two orders of magnitude lower than electrolyic devices [3]. In the consumer electronics market however, this feature can be of limited value as product lifetimes are often less than a few thousand operating hours. As a point of comparison, at 85°C Epcos MKP polypropylene capacitors have an Mean Time Between Failures (MTBF) of 200,000 hours, whereas their B43564 electrolytic devices have an MTBF of only 15,000 hours [39]. It should be noted however, that  $85^{\circ}$ C is typically the maximum temperature polypropylene devices can handle without de-rating; for every  $10^{\circ}$ C above this the life expectancy is approximately halved [40] [41].

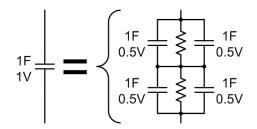

Polypropylene devices possess an extremely high dielectric strength, allowing them to be rated for operation well above 1000V DC and thus removing the need to use series/parallel connected capacitors across a high voltage bus. This is advantageous in that capacitor balancing is not required, and a single component can replace a number of smaller components, potentially reducing manufacturing time and cost.

A further benefit is that of minimal equivalent series resistance, which gives rise to low power dissipation and therefore high ripple current handling capabilities. For example, a 2.2 $\mu$ F 450V Epcos MKP polypropylene capacitor has a ripple current rating of 7.5A [39]. An equivalent Panasonic NHG electrolytic capacitor has a rating of only 29mA [42]. To put this into perspective, building up a ripple current rating of 7.5A would require 259 electrolytic capacitors in parallel. This would clearly be impractical, outweighing the capacitance to volume advantage that electrolytics have. This represents a common problem when specifying DC link capacitor values, and is often rectified by over-rating the capacitance in order to achieve an appropriate ripple current rating.

The use of stacked polypropylene film layers give the devices a much reduced equivalent series inductance when compared with spiral-wound electrolytic designs. This aids in mitigating the DC link voltage spikes induced by power device switching, as demonstrated in [40] where voltage overshoot was reduced by 58%. This reduction was significant enough to allow all of the DC link snubber capacitors to be removed.

Polypropylene devices are stable over a wide range of operating conditions; within the specified operating range, the performance of polypropylene capacitors is not significantly affected by temperature, humidity or frequency. ESR and capacitance values are virtually constant under all rated conditions (+/-2%), making them far easier to specify for a particular application. For electrolytic devices, a 20% change in capacitance over the rated temperature range is not unreasonable [39]. Despite the many advantages of film capacitor technology, electrolytic devices remain the popular choice for two main reasons; capacitance to volume ratio (factor of 100x higher) and capacitance to cost ratio (factor of 10x cheaper). Having said this, the cost can be offset somewhat by the saving in reduced EMI filtering requirements. In applications such as line frequency filtering, where large amounts of capacitance are required, electrolytic devices remain the obvious choice [2]. However for this application, where a very high ripple current to capacitance rating is required, the advantages of electrolytic devices are negated. Not only this, but their use is virtually impossible as an excessive capacitance rating is required to achieve the ripple current handling, defeating the point of a low capacitance DC link system.

### 2.3 Power Factor Correction

As discussed in the introduction, the ever increasing number of electronic loads on the mains has made power factor an important issue. With the introduction of Electro-Magnetic Compatibility (EMC) standards such as EN 61000-3-2 it is a requirement for mains connected loads to have a minimum harmonic performance [7]. Almost any load with an AC/DC conversion stage will require some form of power factor correction circuitry in order to meet this standard, making it an area of considerable interest for the electronics industry. As always in the consumer market, the challenge lies in meeting this specification at a minimum cost and generally in the smallest package possible. At the higher end of the market, further voluntary standards can be met to provide an additional selling point to the customer. One such standard is Energy Star, a government-backed initiative which highlights particularly energy efficient products, and in many cases includes a minimum power factor rating (e.g. >0.9 at 100% load for a computer power supply) [43]. This section of the thesis provides an overview of the current techniques available for meeting these standards, with a particular emphasis placed on low complexity and cost.

#### 2.3.1 Passive PFC

A simple, reliable and efficient approach to reducing load harmonics from an AC/DC converter is the addition of a passive filter. In many cases this will simply require an inductor to be placed between the supply and the bridge rectifier. A further

benefit of the passive approach is that no additional EMI is created as there is no high frequency switching involved. The basic nature of this modification allows it to be retrofitted to existing designs to make them compliant, generally increasing the power factor from under 0.7 to around 0.9 [4]. However, the level of improvement seen is greatly affected by variations in load and input voltage, and furthermore the low cutoff frequency of such a filter makes the input inductor very large. The fixed component values of a passive PFC approach also mean that it will not work with universal line voltage (85-250V) which is vitually a given feature of modern electronic equipment. Resonant LC filters can be used to target specific harmonics (generally the third, fifth and seventh) and achieve a greater power factor, but the additional size and cost of the reactive components makes this uneconomical for many applications. Despite these drawbacks, for very cost sensitive and low performance applications the simplicity of a passive PFC system often makes it the preferred approach.

### 2.3.2 Active PFC

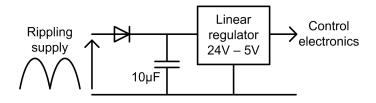

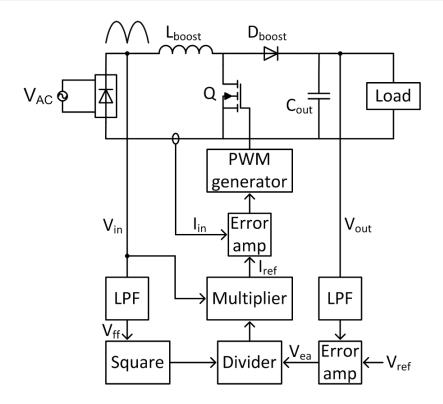

#### Conventional APFC Hardware and Control System

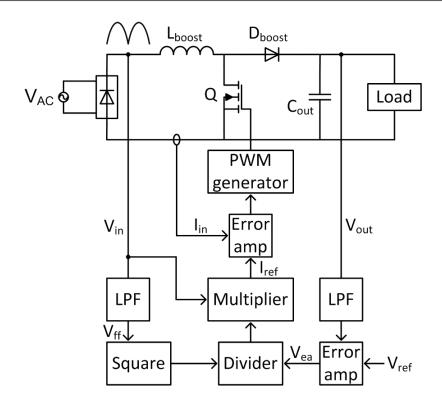

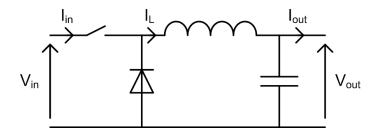

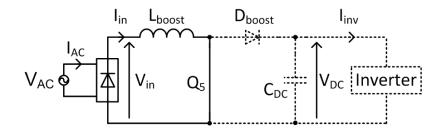

In order to overcome the poor performance, size and adaptability of passive PFC techniques, a range of active solutions have been created [44]. For low cost singlephase applications, the most common approach is to place a boost converter after the diode bridge as shown in Figure 2.14. This arrangement benefits from a low side/grounded switching device and an input side inductor which allows for Continuous Conduction Mode (CCM) current, reducing the amount of EMI filtering required. The addition of this active element allows for precise shaping of the input current, achieving unity power factor over a wide range of input voltage and load conditions. Regulation of the DC link voltage also allows the design of the load or secondary DC/DC stage to be optimised around a specific operating point [45]. The main disadvantage of a boost derived solution is that the output voltage,  $V_{out}$ , must be greater than the input voltage,  $V_{in}$ , which places additional stresses on the switching components.

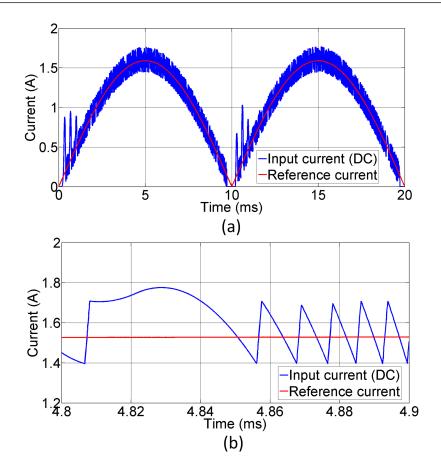

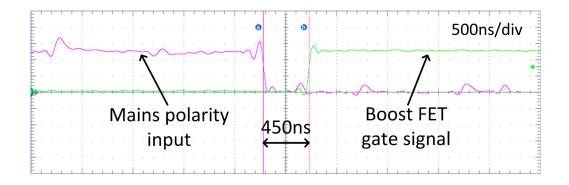

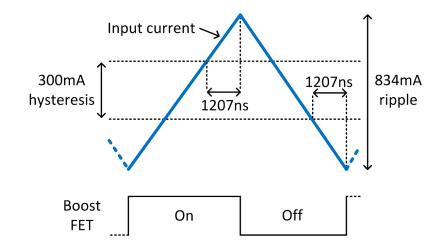

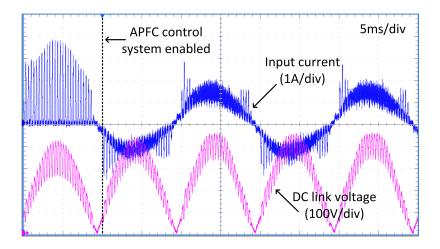

Figure 2.14: Hardware and control for a conventional boost APFC system

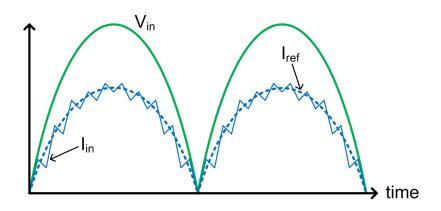

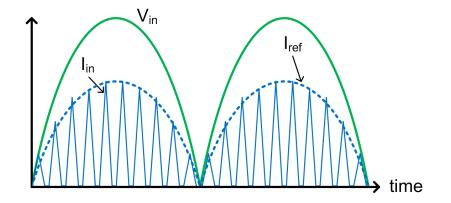

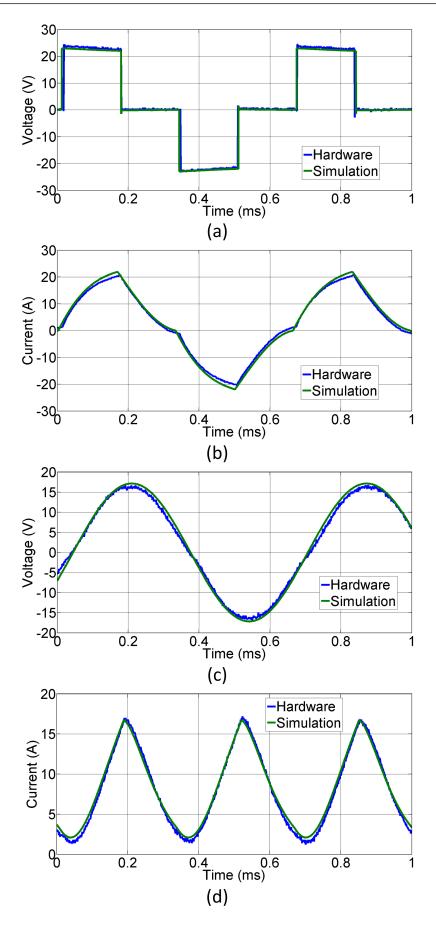

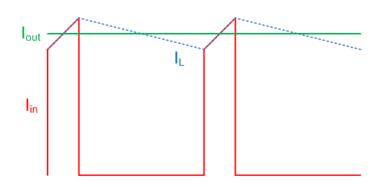

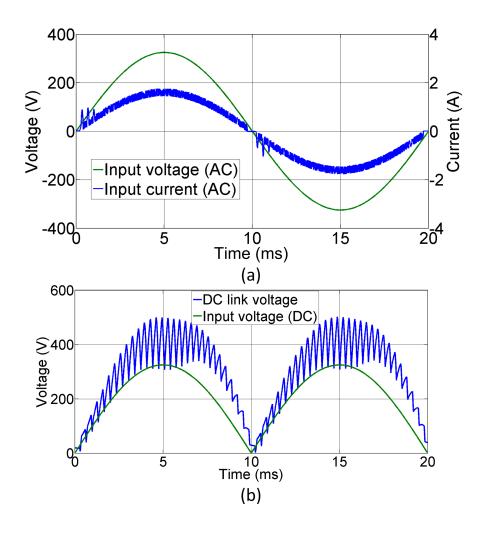

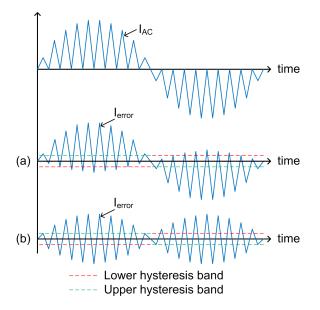

The primary function of the boost PFC system is to shape the input current,  $I_{in}$ , to be proportional to the input voltage,  $V_{in}$ , thus making the load appear resistive. This is carried out by actively controlling the boost switch such that the input current tracks a reference,  $I_{ref}$ , as closely as possible. To achieve the lowest input current distortion, CCM control is used whereby the input current does not fall to zero between switching events (see Figure 2.15). For situations where higher input current distortion can be tolerated, Discontinuous Conduction Mode (DCM) may be used with the benefits of reduced switching frequency and/or inductor size, as well as reduced control complexity given that the input current is zero at the start of each switching event (see Figure 2.16).

Figure 2.15: Boost APFC waveforms showing input current tracking reference in CCM

Figure 2.16: Boost APFC waveforms showing input current tracking reference in DCM

The secondary function of the boost PFC system is to regulate the output voltage. Conventionally this is a stable DC voltage with a small ripple component dependent on the size of the DC link capacitor. The output voltage is controlled by altering the mean amplitude of the reference current signal. As can be seen in Figure 2.14 this signal is generated by multiplying the rectified line voltage,  $V_{in}$ , with the output of the voltage error amplifier  $V_{ea}$ . The current reference therefore has a shape which is proportional to the input voltage and a mean amplitude dependent on the output voltage error.

Before the voltage error signal reaches the multiplier, it is first divided by the square of the mean input voltage  $(V_{ff})$  in order to keep the gain of the voltage control loop constant. This is required because the mean input voltage will vary with changes in the mains supply voltage, and would otherwise affect the power of the system. For example, if the mains voltage were to double,  $V_{in}$  would double causing the output of the multiplier block  $(I_{ref})$  to double. For a constant power load, if the input voltage doubles the input current must halve, so clearly the previously described operation would not be appropriate. However, by dividing the voltage error signal by the square of the mean input voltage, the current reference will be reduced proportionally, maintaining constant input power [46].

The simultaneous regulation of input current and output voltage with a single switch poses somewhat of a problem for the control system. By forcing the input current to be proportional to the input voltage, the input power becomes a  $sin^2$  function at twice the line frequency. This causes the DC link capacitor to be charged/discharged at the same frequency, creating a ripple voltage which lags 90 degrees behind the charging current. Eliminating this voltage ripple would require a high bandwidth voltage control loop to modulate the reference current amplitude, subsequently distorting the input current shape. The contention between the two aspects of the control system means that the only way to achieve the desired result is to have a fast current control loop and a slow voltage control loop (typically < 20Hz) which will not distort the input current shape. A very large DC link capacitor is required to account for the low bandwidth of the voltage regulation and smooth the second harmonic power flow.

A further challenge is presented in the form of second harmonic ripple in the  $V_{ff}$  and  $V_{ea}$  signals. Despite using a low pass filter to generate these signals from the input and output voltages, a certain amount of second harmonic will still be present. This distortion passes through the divider and multiplier, affecting the reference current and therefore the actual input current. When passed through the diode bridge, the second harmonic creates both a third harmonic and a fundamental component phase shifted 90 degrees from the input voltage, increasing the distortion and displacement of the input current which reduces the power factor.

Ripple in the feedforward voltage signal  $(V_{ff})$  clearly needs to be low if a high power factor is to be achieved, implying the need for a lowpass filter with a very low cutoff frequency. The downside of this is that the system will have a very slow response to changes in input voltage. Conventionally a compromise is made by using a two pole filter which will have a faster transient response for a given attenuation, with the added benefit of phase shifting the second harmonic by 180 degrees, removing the phase displacement issue mentioned previously. A similar issue exists with second harmonic ripple in the output voltage error signal, requiring the error amplifier to shift the ripple by 90 degrees to bring it back in phase with the input voltage [46].

## Alternative APFC Control Systems

The use of a conventional APFC control system with reduced DC link capacitance poses a considerable problem. Not only is there little energy storage to buffer the already low bandwidth voltage regulation, but the very large DC link voltage ripple requires the input to the voltage error amplifier to be heavily filtered. As discussed in the previous section, it is necessary to remove the ripple from the DC link voltage measurement to prevent it from modulating the input current reference. Where a conventional APFC system will typically have less than 10% DC link voltage ripple, a reduced capacitance converter has up to 100% ripple. It is therefore necessary to have ten times the attenuation (-20dB) to produce the same amount of ripple in the DC link voltage sensor signal. For a first order lowpass filter (-20dB/decade rolloff) this requires the cutoff frequency to be reduced by a factor of 10, resulting in a proportional reduction in the control system bandwidth. Subsequently, such a system would only work if the input voltage and load conditions could be guaranteed to change at a very slow rate, greatly limiting the range of possible applications.

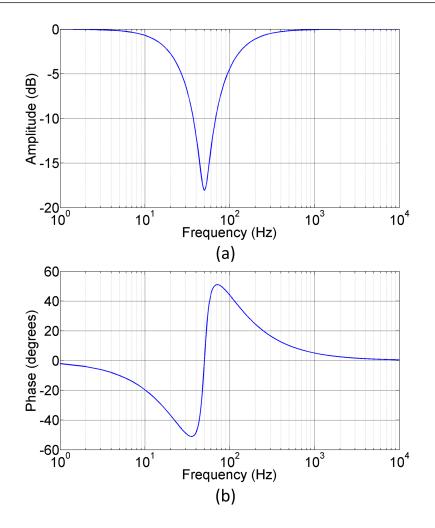

A number of options are available which avoid or improve the voltage control bandwidth issue by breaking the twice line frequency bandwidth limit [47]. One option is to place a notch filter between the divider and multiplier blocks to remove the second harmonic ripple. This allows the voltage control loop bandwidth to be increased, improving the dynamic response of the system and reducing the DC link voltage ripple. Research by Williams [48] demonstrated that the addition of a notch filter with a Q factor of 10 tuned to the second harmonic frequency allowed unity input power factor to be maintained whilst reducing the the output voltage ripple by 73%. Two limitations of this approach are noted; very tight component tolerances are required to obtain the high Q factor and the filter will only work at the precise tuned frequency, ruling out operation at 50Hz or 60Hz without modification. However, this research was carried out before the prevalence of low cost microcontrollers, and as such an adaptive and precise digital filter could potentially alleviate these issues.

An alternative approach is not to use a multiplier based controller and instead operate the boost converter in discontinuous conduction mode, allowing the system to behave as a natural voltage follower [45]. By allowing the input current to fall to zero after each switching event, it will have a mean value proportional to the input voltage as can be seen in Figure 2.16. When the boost switch is closed, the boost inductor is shorted across the mains supply and therefore the input current ramp rate is dependent solely on the input voltage and not the load. Given a fixed switching time period, mean current is proportional to  $\frac{\delta i}{\delta t}$  and therefore voltage, allowing the current control loop and input current sensor to be removed. This type of control is best suited to applications where higher input current distortion can be offset against reduced cost, control complexity and boost inductor size [49]. Work by Caruso *et al.* [50] has shown that the use of this technique can lend itself well to drives used in domestic appliances as the operating conditions are generally predictable and known in advance. As DCM operation is necessary for the voltage follower behaviour to take place, it is common for other hardware topologies such as flyback, SEPIC or Ćuk to be used which do not require  $V_{out}$  to be higher than  $V_{in}$  and also provide galvanic isolation.

Rather than removing the current sensor as with the DCM voltage follower technique, other control system designs have been produced to eliminate input voltage sensing [51, 52]. Similarly, this approach is most effective where the operating conditions are known in advance, allowing predictive open loop control to compensate for the lack of feedback. The steady state transfer function of the power converter and load is used to derive a non-linear PWM sequence which results in a high input power factor. As input current sensing is still present, CCM operation is possible which improves the power factor over DCM approaches, with the design in [52] exceeding the performance of a conventional APFC system with complete voltage and current feedback information. An alternative design is put forward by Ohnishi and Hojo [53] which has no input current or DC link voltage sensors, and relies solely on an input voltage measurement with semi open-loop control. The control system is simple and low cost, producing a high quality input current waveform, but is dependent on a predictable known load and stable DC link voltage in order to function properly. Such 'sensorless' techniques are therefore challenging to implement with a reduced DC link capacitance system. The authors suggest it is well suited to an application such as a lighting dimmer where the load does not vary and the cost must be minimised.

For very cost sensitive applications, there are power factor control schemes which meet the requirements of EN 61000-3-2 but do not necessarily produce a high power factor [54–60]. Conventional AC/DC converters with a power rating of between 75W and 600W will normally fall into the Class D category of equipment due to having an input current waveform shape which falls within the envelope shown in Figure 2.17 for at least 95% of each half period of the mains.

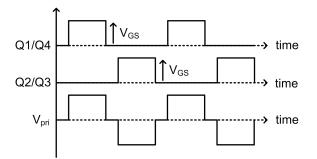

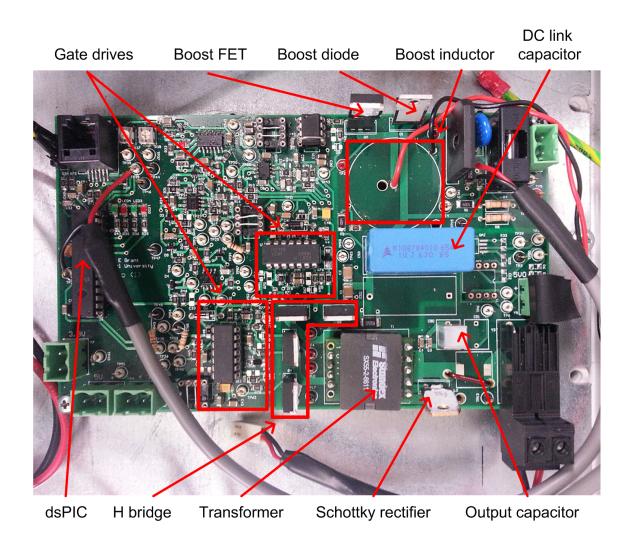

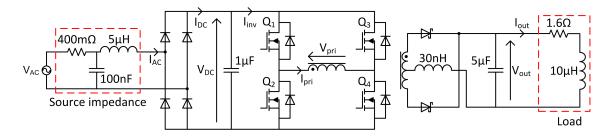

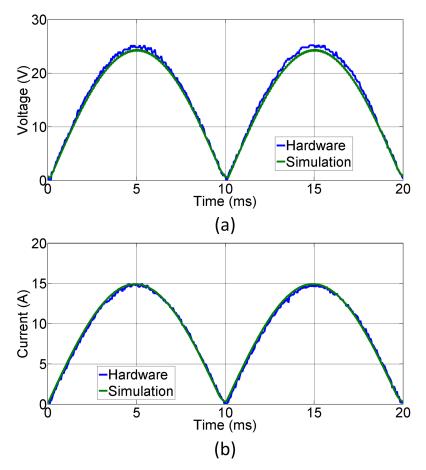

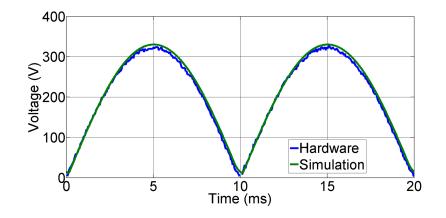

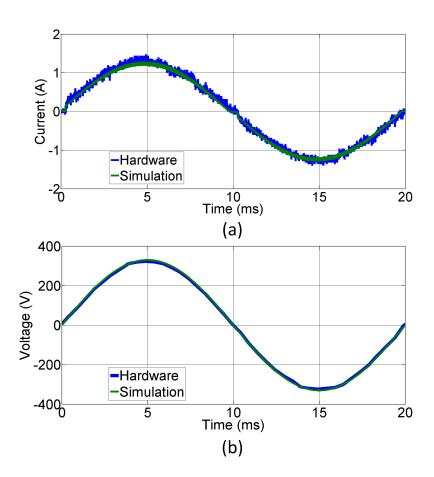

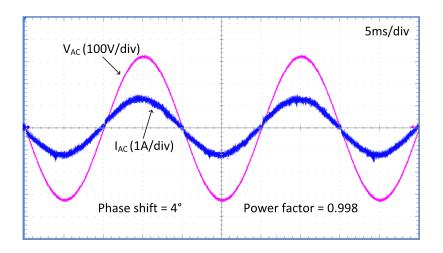

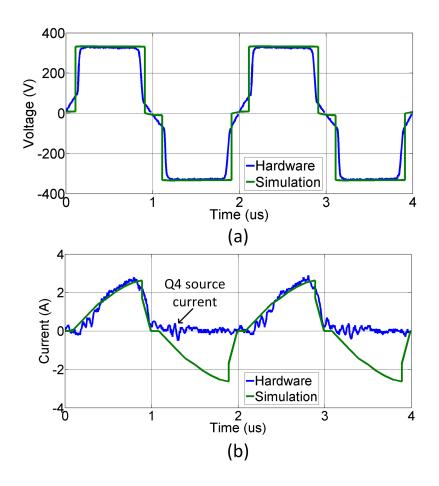

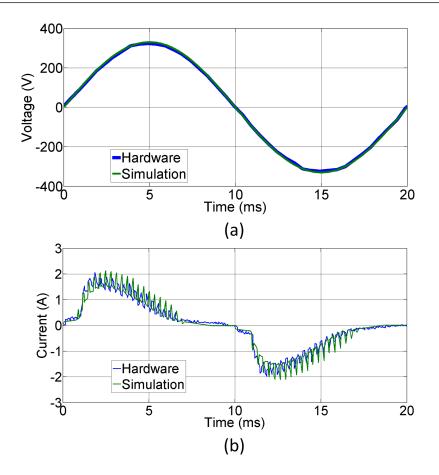

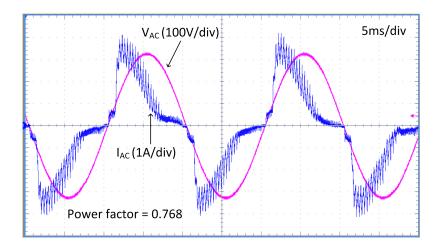

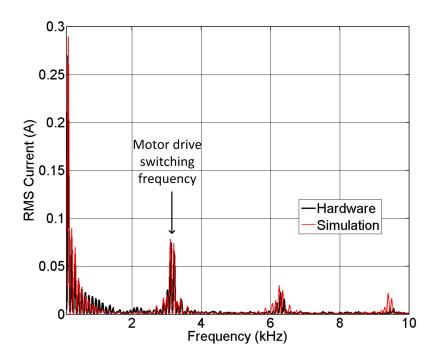

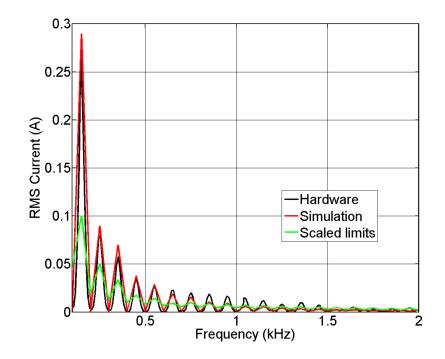

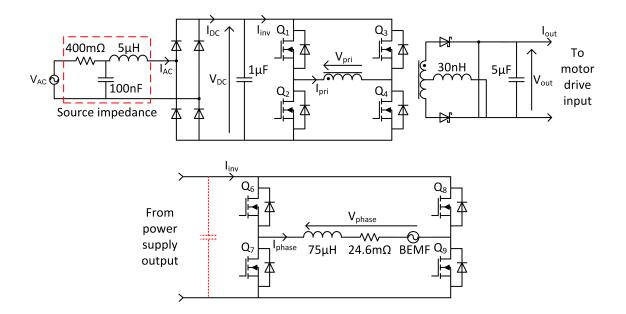

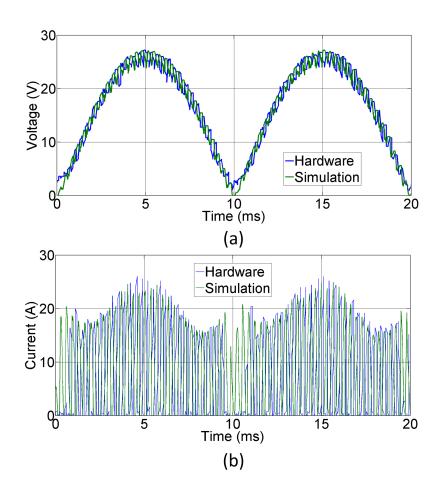

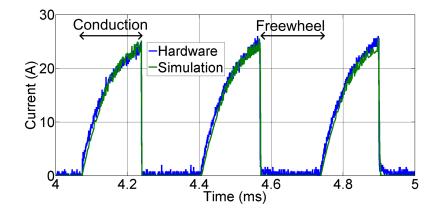

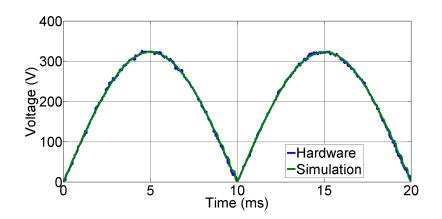

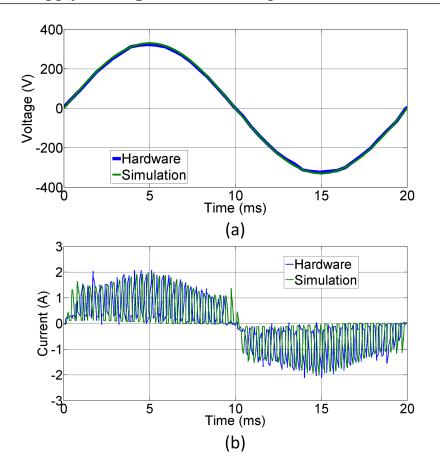

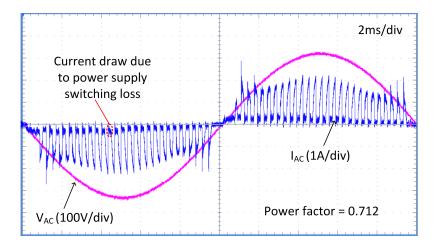

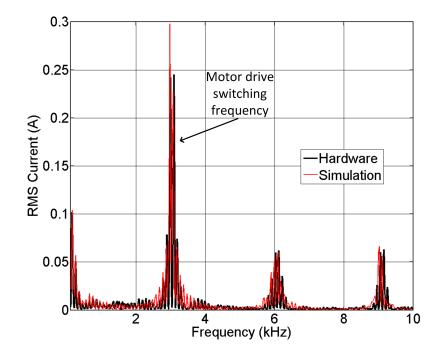

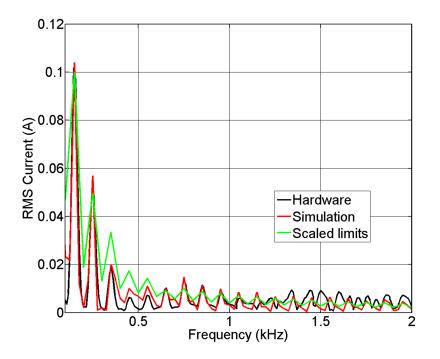

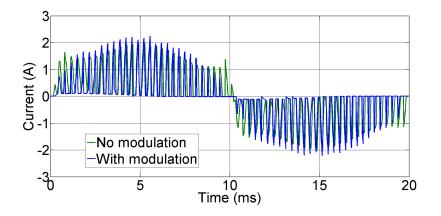

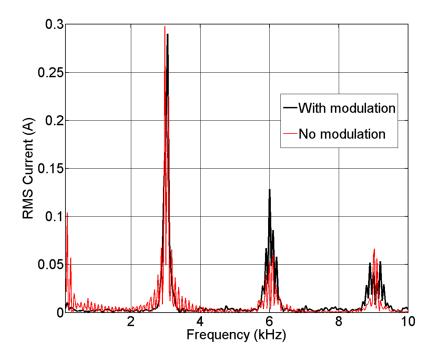

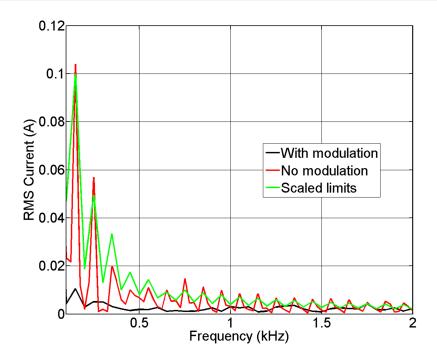

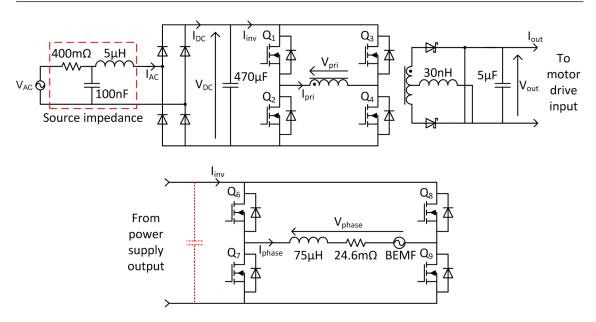

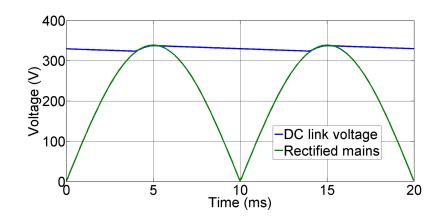

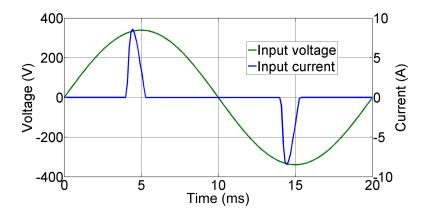

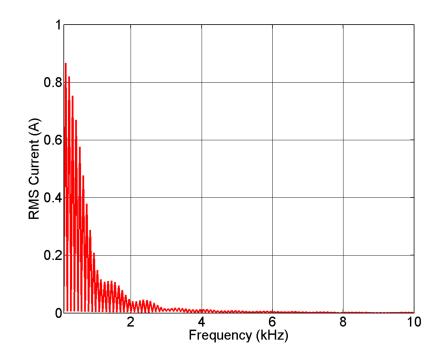

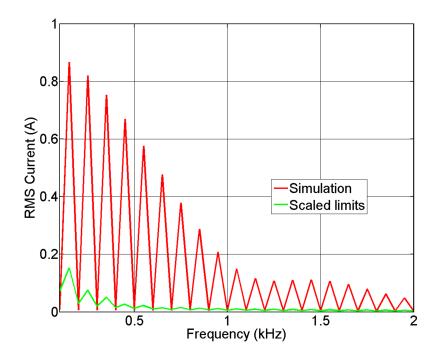

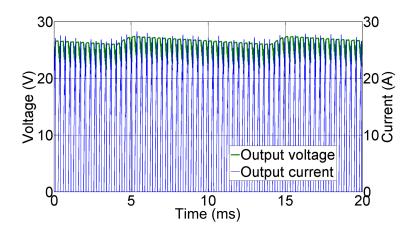

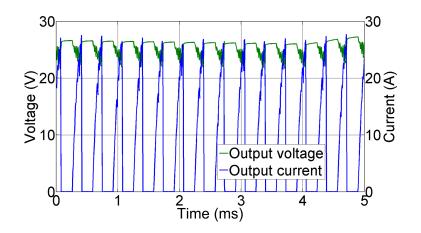

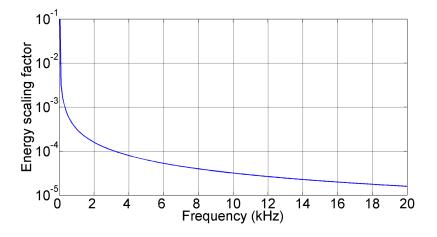

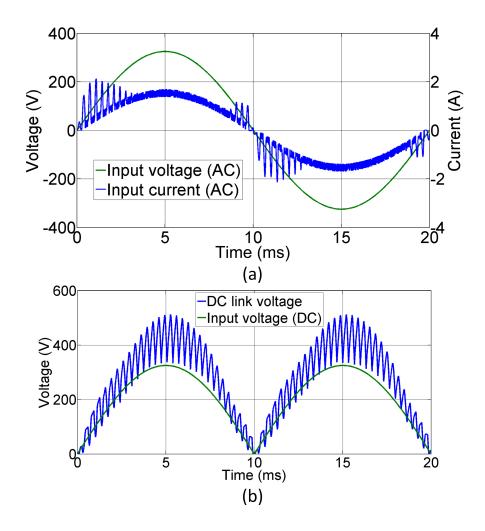

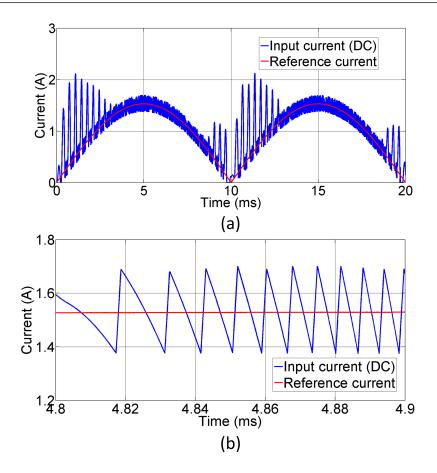

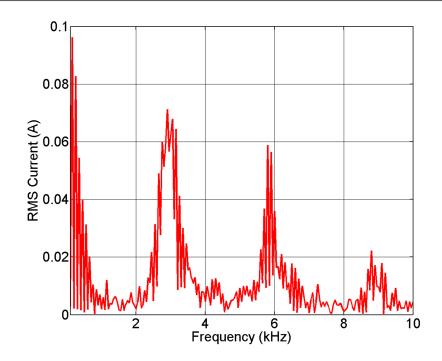

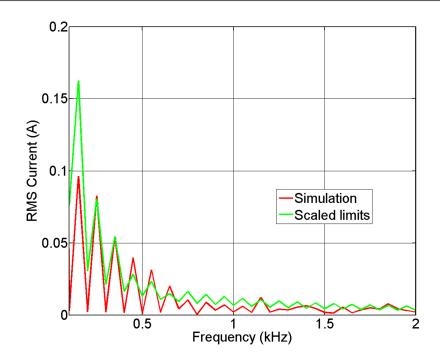

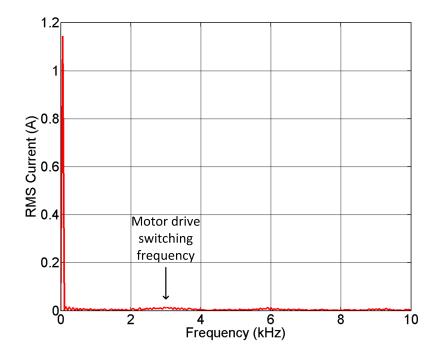

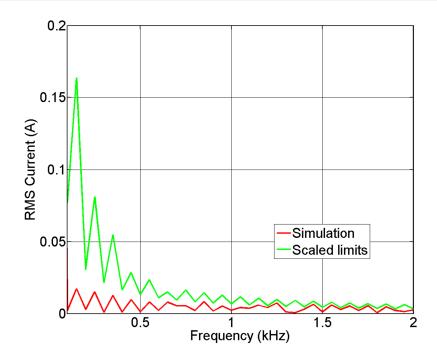

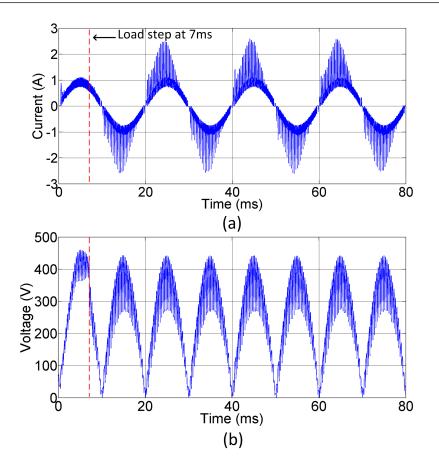

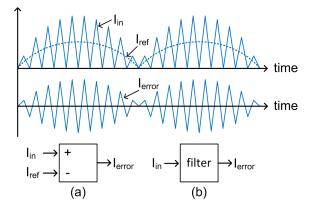

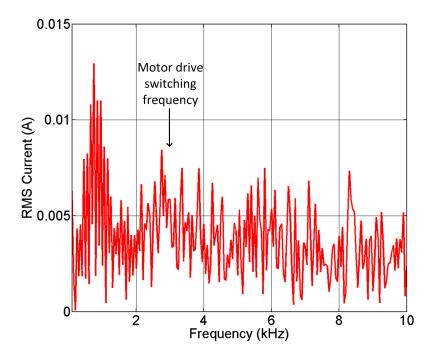

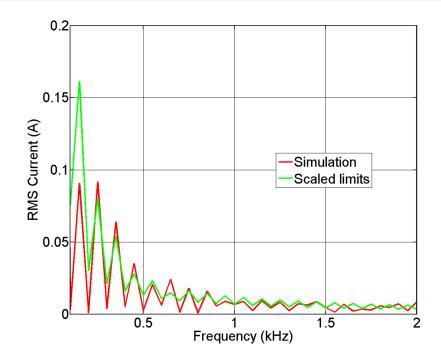

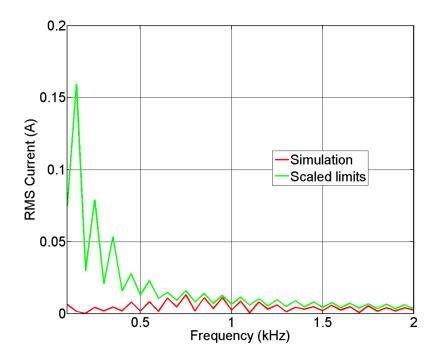

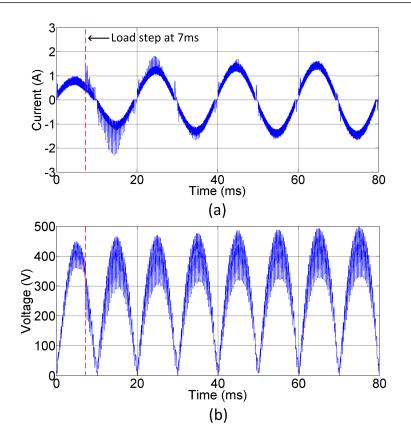

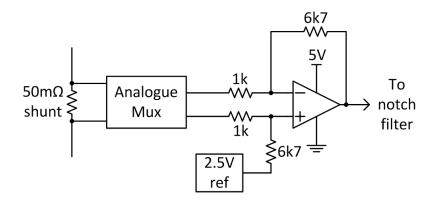

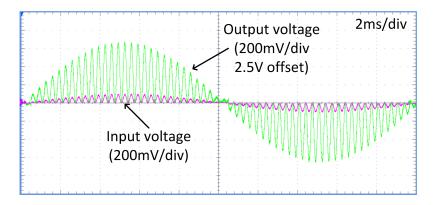

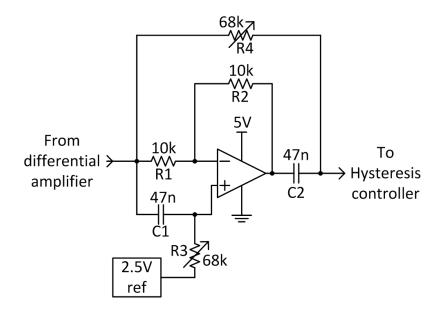

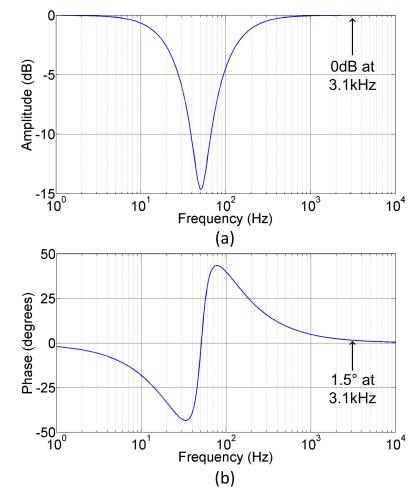

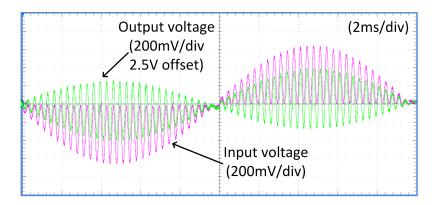

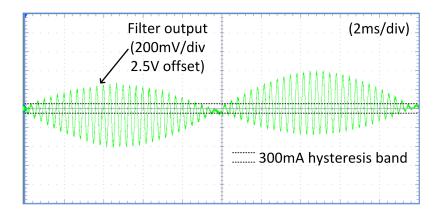

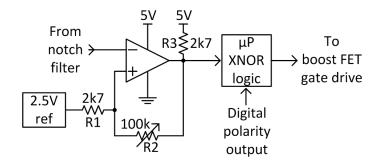

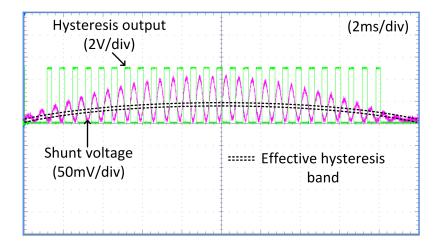

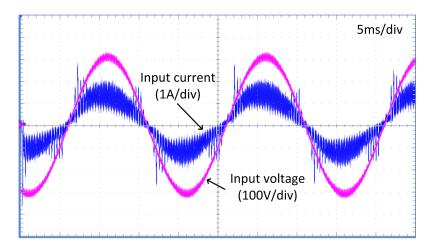

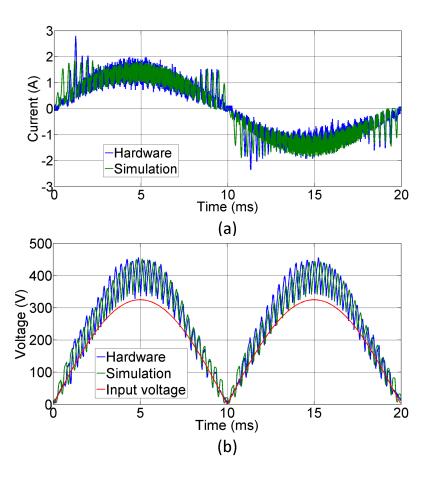

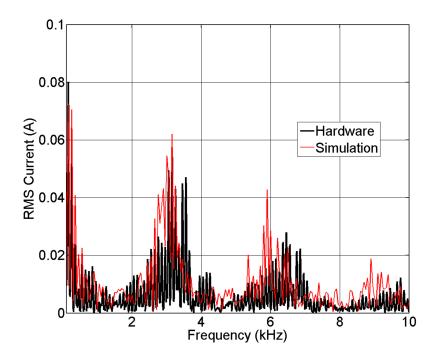

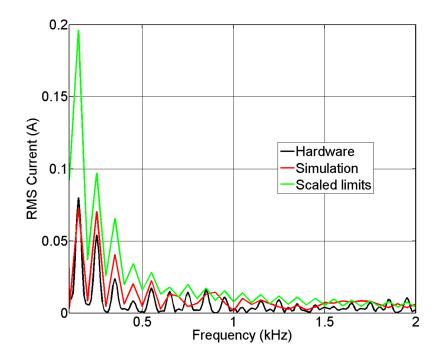

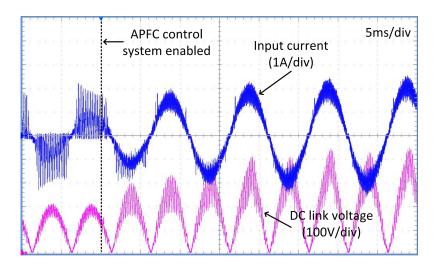

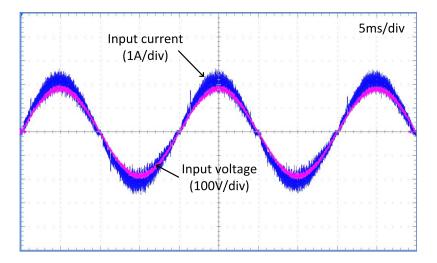

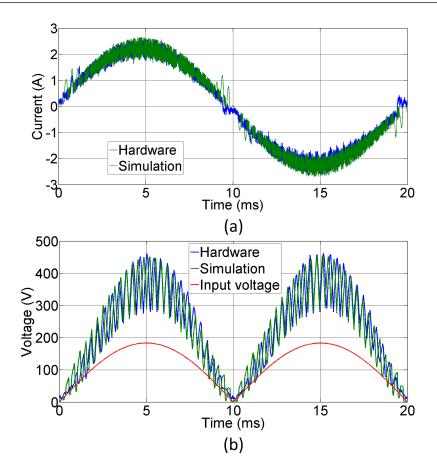

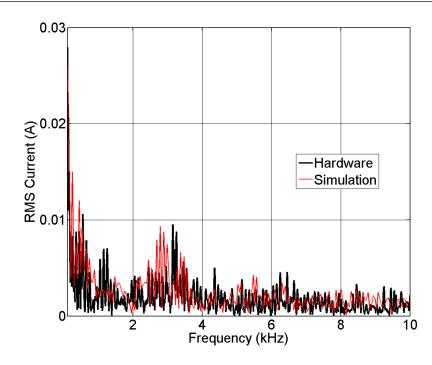

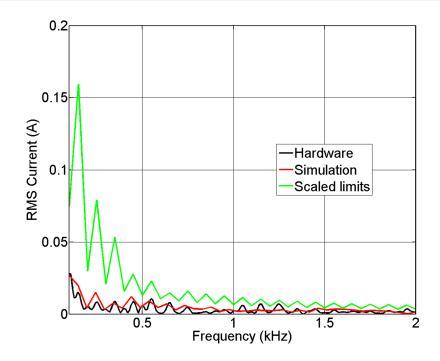

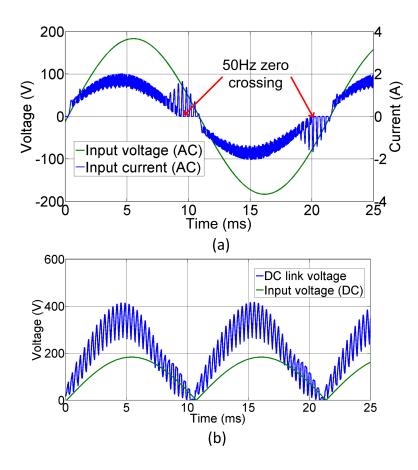

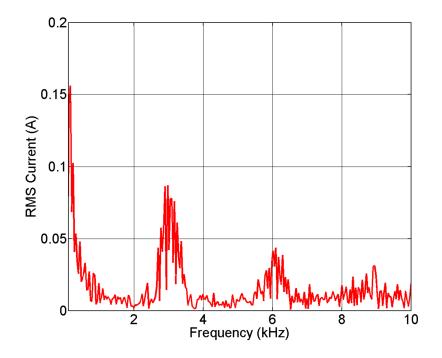

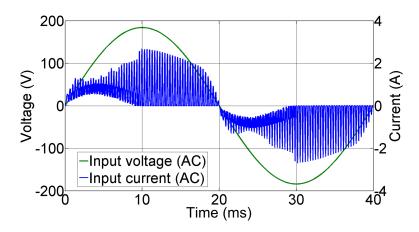

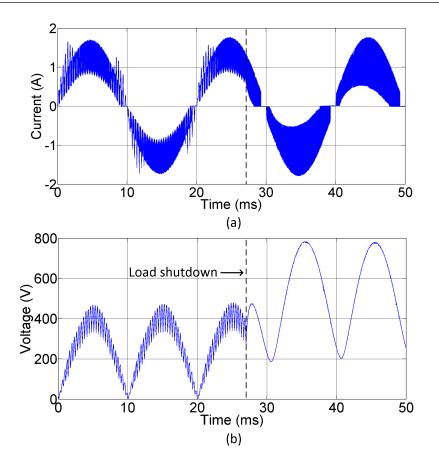

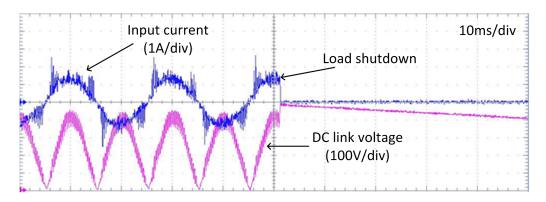

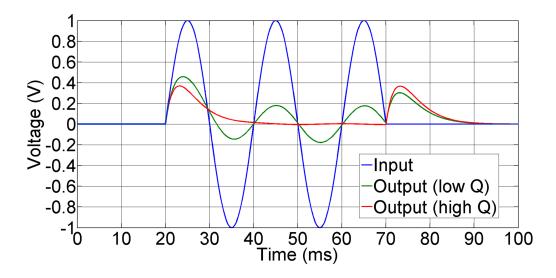

Figure 2.17: Class D input current envelope for EN 61000-3-2