# Newcastle University, UK School of Electrical and Electronic Engineering (EEE)

# Compositional Circuit Design with Asynchronous Concepts

PhD Thesis

Jonathan Richard Beaumont

March 2018

## **Abstract**

Synchronous circuits are pervasive in modern digital systems, such as smart-phones, wearable devices and computers. Synchronous circuits are controlled by a global clock signal, which greatly simplifies their design but is also a limitation in some applications. Asynchronous circuits are a logical alternative: they do not use a global clock to synchronise their components. Instead, every component reacts to input events at the rate they occur. Asynchronous circuits are not widely adopted by industry, because they are often harder to design and require more sophisticated tools and formal models.

Signal Transition Graphs (STGs) is a well-studied formal model for the specification, verification and synthesis of asynchronous circuits with state-of-the-art tool support. STGs use a graphical notation where vertices and arcs specify the operation of an asynchronous circuit. These graphical specifications can be difficult to describe compositionally, and provide little reusability of useful sections of a graph. In this thesis we present Asynchronous Concepts, a new design methodology for asynchronous circuit design. A concept is a self-contained description of a circuit requirement, which is composable with any other concept, allowing compositional specification of large asynchronous circuits. Concepts can be shared, reused and extended by users, promoting the reuse of behaviours within single or multiple specifications. Asynchronous Concepts can be translated to STGs to benefit from the existing theory and tools developed by the asynchronous circuits community.

Plato is a software tool developed for Asynchronous Concepts that supports the presented design methodology, and provides automated methods for translation to STGs. The design flow which utilises Asynchronous Concepts is automated using Plato and the open-source toolsuite Workcraft, which can use the translated STGs in verification and synthesis using integrated tools. The proposed language, the design flow, and the supporting tools are evaluated on real-world case studies.

## Acknowledgments

I would like to thank my supervisor, Andrey Mokhov, for his wisdom and guidance throughout my postgraduate studies. He introduced me to graphical design methods, and helped me shape what has become the subject of this thesis, and I am very grateful. I would also like to thank Danil Sokolov, who has greatly helped my skills and knowledge in this field and in software design, and Alex Yakovlev, who often helped me expand my understandings and bring this into my research.

I also extend my thanks to my colleagues Alessandro de Gennaro, Vladimir Dubikhin and Adiran Wheeldon. We have worked together and discussed many topics over the years, and from them all I have learned many things. I hope they continue to be successful with their research and future careers.

To my friends, whom I have had the pleasure of spending time with since I began my studies. I thank you for all of your support and the fun times we have had. To Chris Dunn, thank you for your hospitality, and to Ashley Matthews, thank you for always being up for a chat, and your interest in my work. I also thank my family for their support throughout my studies.

Finally, and most importantly, I am thankful to Elie Howes for all of her love, support and patience throughout my PhD. She was there to help me at difficult times, and to share in the good times. Her encouragement has helped me with the research and with the writing of this thesis, and I am very grateful.

This research was supported by EPSRC research grant 'A4A: Asynchronous design for Analogue electronics' (EP/L025507/1) and the Royal Society Research Grant 'Computation Alive: Design of a Processor with Survival Instincts'

## **Contents**

| ΑI | bstrac          | it and the second of the secon | ı   |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Αd | cknov           | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ii  |

| C  | onten           | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iii |

| Li | st of           | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vi  |

| Li | st of           | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xi  |

| Pı | u <b>blic</b> a | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xii |

| 1  | Intr            | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   |

|    | 1.1             | Current usage of asynchronous technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   |

|    | 1.2             | Motivation for a new design method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4   |

|    | 1.3             | Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6   |

|    | 1.4             | Thesis layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7   |

| 2  | Tec             | nnical background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   |

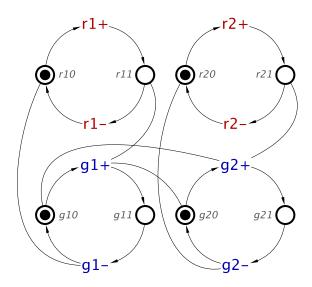

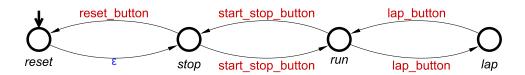

|    | 2.1             | Finite State Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9   |

|    | 2.2             | Petri Nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12  |

|    | 2.3             | Signal Transition Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15  |

|    |                 | 2.3.1 STG design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17  |

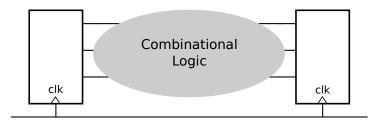

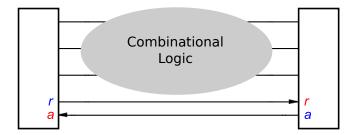

|    | 2.4             | Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18  |

|    | 2.5             | Monoids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21  |

|    | 2.6             | Boolean functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23  |

|    |                 | 2.6.1 Converting any Boolean function to CNF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24  |

|    |                 | 2.6.2 Converting CNF functions to DNF functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26  |

|    | 2.7             | Haskell syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27  |

|   | 2.8 | Summary                                          | 28  |

|---|-----|--------------------------------------------------|-----|

| 3 | Asy | nchronous Concepts                               | 30  |

|   | 3.1 | Circuit-specific concepts                        | 31  |

|   |     | 3.1.1 Signal-level concepts                      | 31  |

|   |     | 3.1.2 Gate-level and Protocol-level concepts     | 40  |

|   | 3.2 | Generalising to multiple inputs                  | 52  |

|   | 3.3 | High-level concept functions                     | 55  |

|   |     | 3.3.1 Boolean function concepts                  | 55  |

|   |     | 3.3.2 Bubble transformation                      | 57  |

|   |     | 3.3.3 Dual transformation                        | 63  |

|   |     | 3.3.4 Enable transformation                      | 66  |

|   | 3.4 | Set-Reset latch example                          | 70  |

|   | 3.5 | Abstract concepts                                | 73  |

|   | 3.6 | Summary                                          | 77  |

| 4 | Asy | nchronous Concepts design flow                   | 79  |

|   | 4.1 | Design approach                                  | 80  |

|   | 4.2 | Generating concepts from set and reset functions | 83  |

|   | 4.3 | Process mining for Asynchronous Concepts         | 84  |

|   | 4.4 | User generated libraries of concepts             | 86  |

|   | 4.5 | Asynchronous Concept translation                 | 87  |

|   | 4.6 | Combining concept specifications                 | 89  |

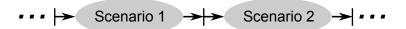

|   |     | 4.6.1 Sequential template                        | 90  |

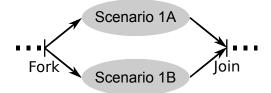

|   |     | 4.6.2 Concurrent template                        | 90  |

|   |     | 4.6.3 Choice template                            | 91  |

|   |     | 4.6.4 Complex combinations                       | 92  |

|   | 4.7 | Verification                                     | 92  |

|   | 4.8 | Synthesis                                        | 94  |

|   | 4.9 | Summary                                          | 95  |

| 5 | Aut | omation of the design flow                       | 97  |

|   | 5.1 | Plato                                            | 100 |

|   |     | 5.1.1 Translation to STG                         | 101 |

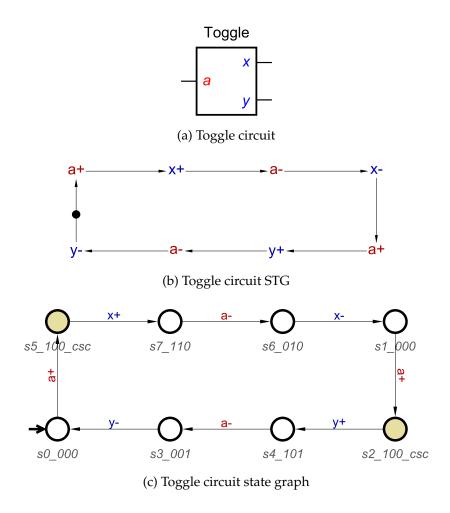

|   |     | 5.1.2 Translation to State Graphs                | 107 |

|               |                                                                             | 5.1.3                                                                                   | Generating concepts from Boolean functions                                                                                                                                                                                                         | 2                                   |

|---------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|               | 5.2                                                                         | Workc                                                                                   | raft                                                                                                                                                                                                                                               | 6                                   |

|               |                                                                             | 5.2.1                                                                                   | Plato integration                                                                                                                                                                                                                                  | 6                                   |

|               |                                                                             | 5.2.2                                                                                   | PGminer integration                                                                                                                                                                                                                                | 8                                   |

|               |                                                                             | 5.2.3                                                                                   | Verification and synthesis tools                                                                                                                                                                                                                   | 9                                   |

|               | 5.3                                                                         | Summ                                                                                    | ary                                                                                                                                                                                                                                                | 3                                   |

| 6             | Case                                                                        | e Studi                                                                                 | es 12                                                                                                                                                                                                                                              | 5                                   |

|               | 6.1                                                                         | Case S                                                                                  | tudy 1: A simple buck controller                                                                                                                                                                                                                   | 5                                   |

|               |                                                                             | 6.1.1                                                                                   | Combining the scenarios                                                                                                                                                                                                                            | 1                                   |

|               |                                                                             | 6.1.2                                                                                   | Simulation and verification                                                                                                                                                                                                                        | 2                                   |

|               |                                                                             | 6.1.3                                                                                   | Synthesis of a speed-independent controller                                                                                                                                                                                                        | 4                                   |

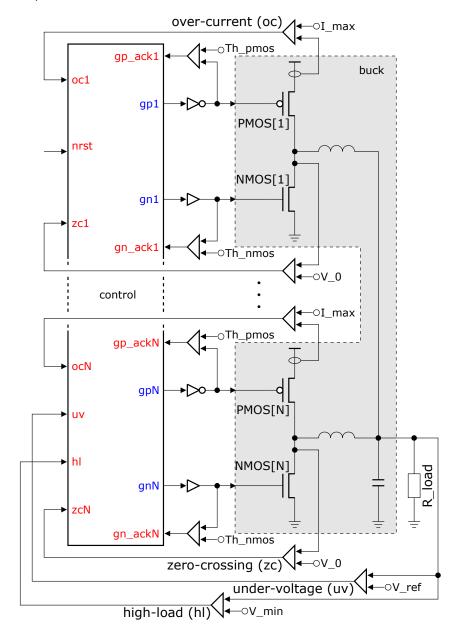

|               | 6.2                                                                         | Case S                                                                                  | tudy 2: Multiphase buck controller                                                                                                                                                                                                                 | 5                                   |

|               |                                                                             | 6.2.1                                                                                   | Single phase block diagram                                                                                                                                                                                                                         | 7                                   |

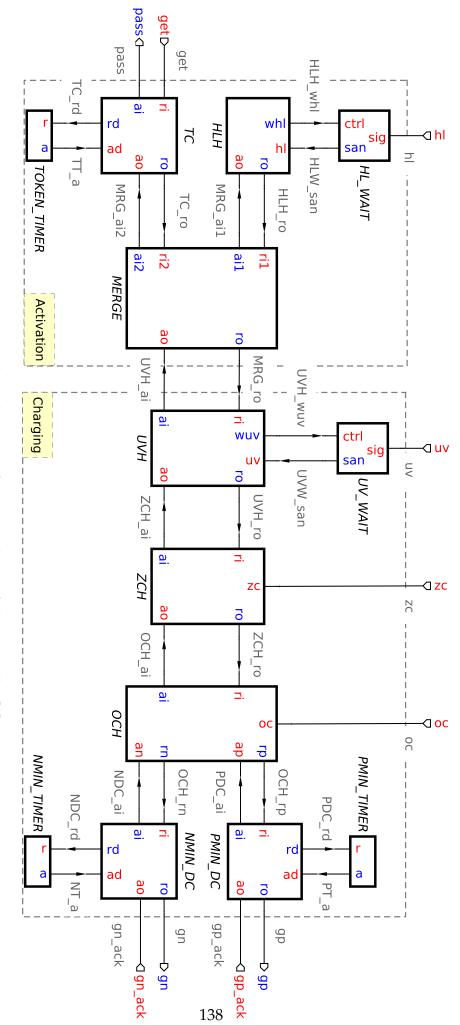

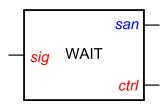

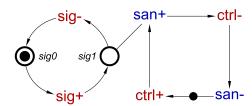

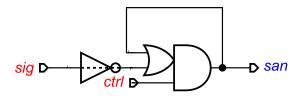

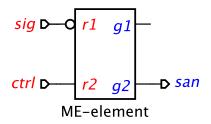

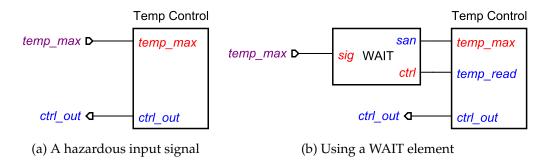

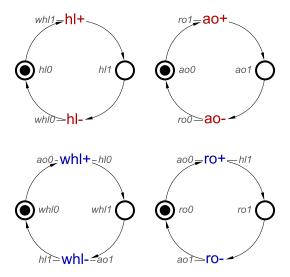

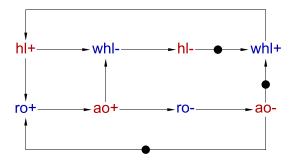

|               |                                                                             | 6.2.2                                                                                   | WAIT element                                                                                                                                                                                                                                       | 1                                   |

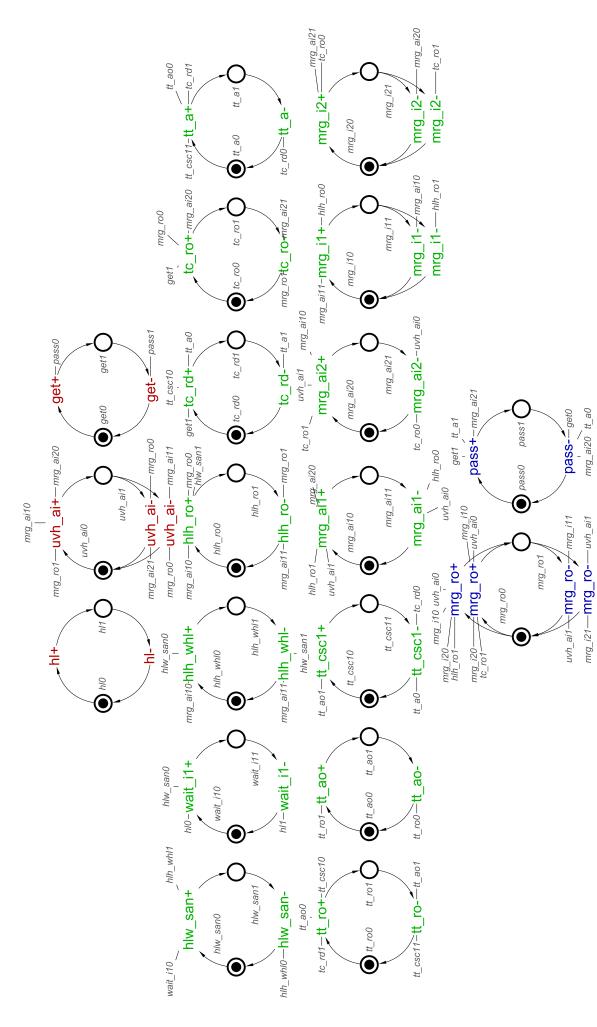

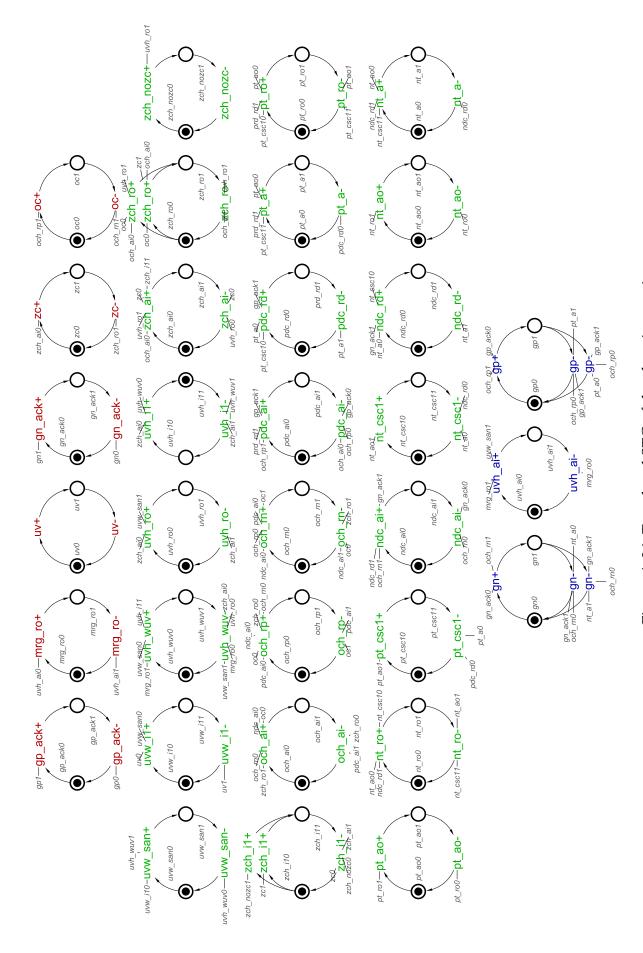

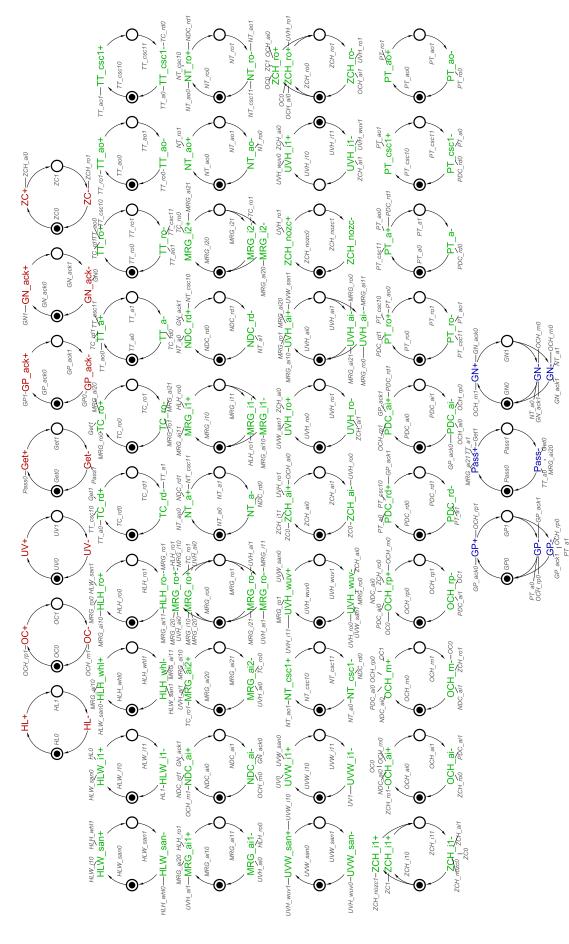

|               |                                                                             | 6.2.3                                                                                   | Full specification                                                                                                                                                                                                                                 | 4                                   |

|               | 6.3                                                                         | Summ                                                                                    | ary                                                                                                                                                                                                                                                | 1                                   |

|               |                                                                             |                                                                                         |                                                                                                                                                                                                                                                    |                                     |

| 7             | Rela                                                                        | ited W                                                                                  | ork 15                                                                                                                                                                                                                                             | 4                                   |

| <b>7</b><br>8 |                                                                             | ited Wo                                                                                 |                                                                                                                                                                                                                                                    |                                     |

|               |                                                                             | clusion                                                                                 |                                                                                                                                                                                                                                                    | 5                                   |

|               | <b>Con</b> 8.1                                                              | <b>clusion</b><br>Main c                                                                | s 16                                                                                                                                                                                                                                               | <b>5</b>                            |

|               | <b>Con</b> 6<br>8.1<br>8.2                                                  | <b>clusion</b><br>Main c<br>Future                                                      | <b>S 16</b> contributions                                                                                                                                                                                                                          | <b>5</b> 5                          |

| 8             | <b>Con</b> 6<br>8.1<br>8.2                                                  | clusion  Main o  Future  tiphase                                                        | s 16 contributions                                                                                                                                                                                                                                 | <b>5</b> 5 8                        |

| 8             | <b>Con</b> 8.1 8.2 <b>Mul</b>                                               | clusion  Main c  Future  tiphase  High-lo                                               | s 16 contributions                                                                                                                                                                                                                                 | <b>5</b> 8 <b>4</b> 74              |

| 8             | Cone<br>8.1<br>8.2<br>Mult                                                  | clusion  Main c  Future  tiphase  High-lo                                               | s 16 contributions                                                                                                                                                                                                                                 | <b>5</b> 8 <b>4</b> 6               |

| 8             | 8.1<br>8.2<br>Mult<br>A.1<br>A.2                                            | clusion  Main of Future  tiphase High-lood Token- Delay                                 | s 16 contributions                                                                                                                                                                                                                                 | 5<br>5<br>8<br>4<br>7               |

| 8             | Cone<br>8.1<br>8.2<br>Mult<br>A.1<br>A.2<br>A.3                             | clusion  Main of Future  tiphase  High-lo Token- Delay  MERG                            | s 16 contributions                                                                                                                                                                                                                                 | 5<br>5<br>8<br>4<br>4<br>7<br>9     |

| 8             | Cone<br>8.1<br>8.2<br>Mult<br>A.1<br>A.2<br>A.3<br>A.4                      | clusion  Main of Future  tiphase  High-lo Token- Delay  MERG  Under-                    | s       16         contributions       16         research and development       16         buck controller components       17         coad handler       17         control       17         E element       17                                  | 5<br>5<br>8<br>4<br>7<br>9          |

| 8             | Cone<br>8.1<br>8.2<br>Muli<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5               | clusion  Main of Future  tiphase High-lo Token- Delay MERG Under- Zero-c                | s       16         contributions       16         research and development       16         buck controller components       17         coad handler       17         control       17         E element       17         voltage handler       18 | 5 8 4 4 6 7 9 1 3                   |

| 8             | Muli<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6                              | clusion  Main of Future  tiphase High-lo Token- Delay MERG Under- Zero-c Over-c         | s 16 contributions 16 research and development 16 buck controller components 17 control 17 control 17 E element 17 voltage handler 18 rossing handler 18                                                                                           | <b>5</b> 5 8 <b>4</b> 4 6 7 9 1 3 6 |

| 8             | Cone<br>8.1<br>8.2<br>Muli<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7 | clusion  Main of Future  tiphase High-lo Token- Delay MERG Under- Zero-c Over-c Transis | s16contributions16research and development16buck controller components17coad handler17control17E element17voltage handler18cossing handler18urrent handler18                                                                                       | 5 8 4 6 7 9 1 3 6 7                 |

# **List of Figures**

| 1.1  | Interconnect examples                                            | 3  |

|------|------------------------------------------------------------------|----|

| 1.2  | Example of an STG with hidden patterns of behaviour              | 5  |

| 1.3  | Equivalent concept specification for the STG in Figure 1.2       | 5  |

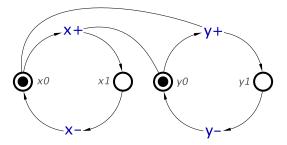

| 2.1  | Abstract FSM of a stopwatch                                      | 10 |

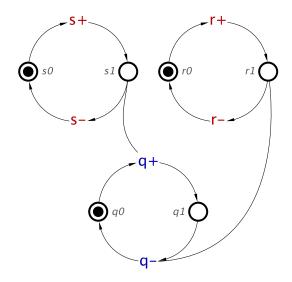

| 2.2  | An example FSM with signals as transition conditions             | 10 |

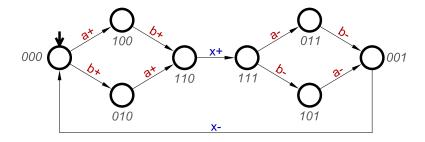

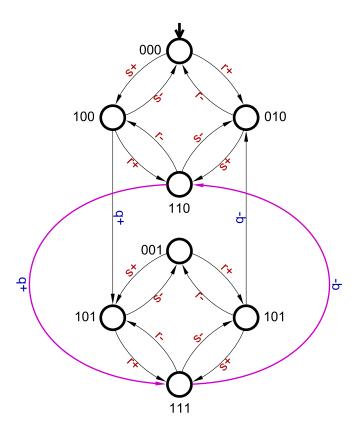

| 2.3  | An FSM featuring 3 concurrent transitions                        | 11 |

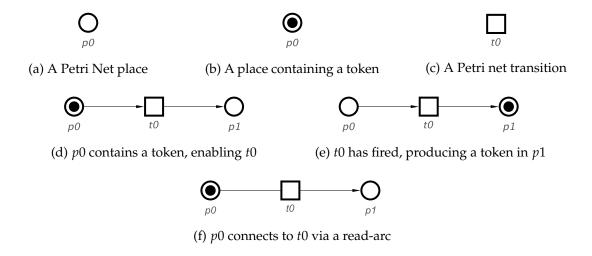

| 2.4  | The elements of a Petri Net                                      | 12 |

| 2.5  | A stopwatch PN model                                             | 13 |

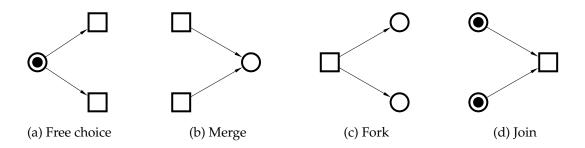

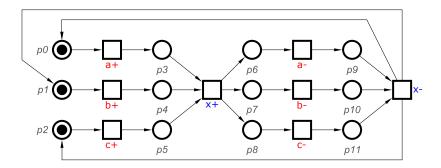

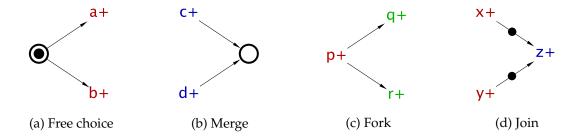

| 2.6  | Constructs for modelling concurrency and choice in PNs           | 14 |

| 2.7  | An example of a system with concurrency modelled as a PN $\dots$ | 14 |

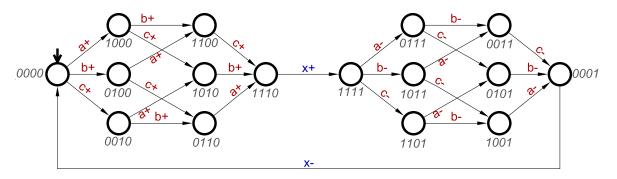

| 2.8  | A PN featuring 3 concurrent transitions                          | 15 |

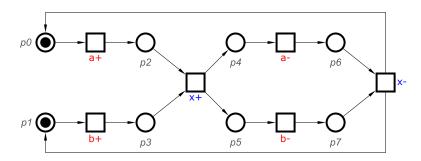

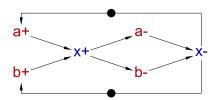

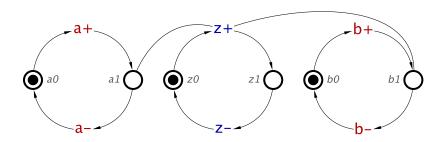

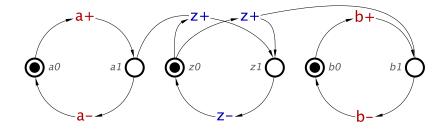

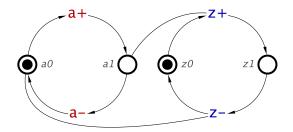

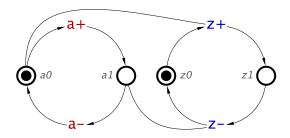

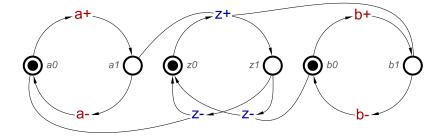

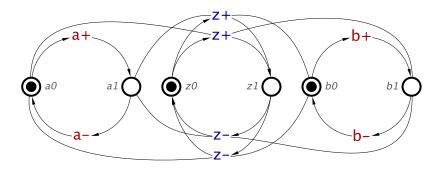

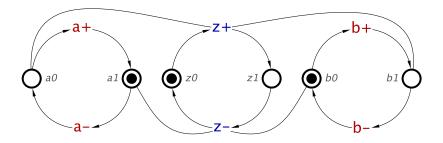

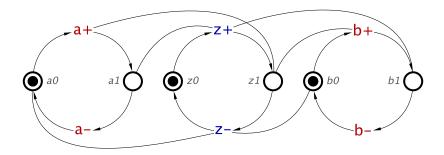

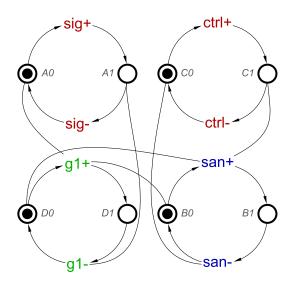

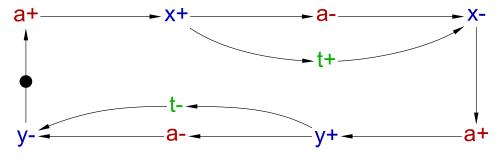

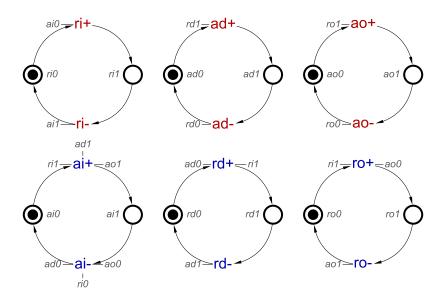

| 2.9  | STG constructs for modelling choice and concurrency              | 16 |

| 2.10 | A system featuring concurrency in STG form                       | 16 |

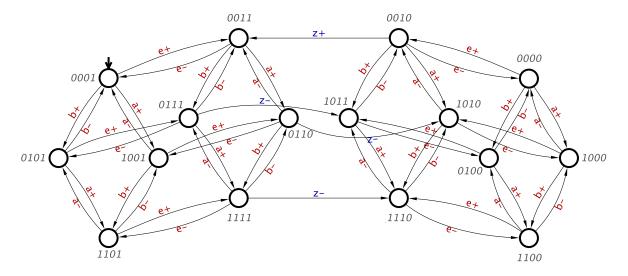

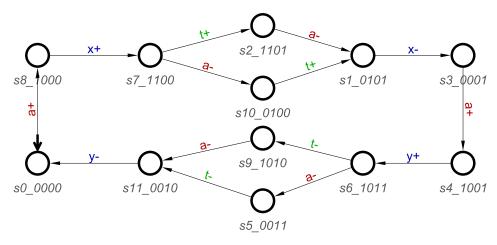

| 2.11 | An STG with 3 concurrent signal transitions                      | 17 |

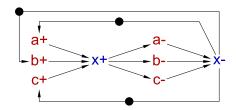

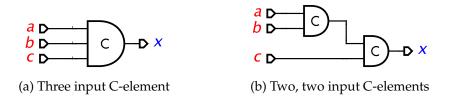

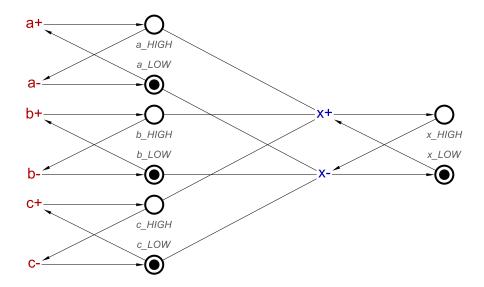

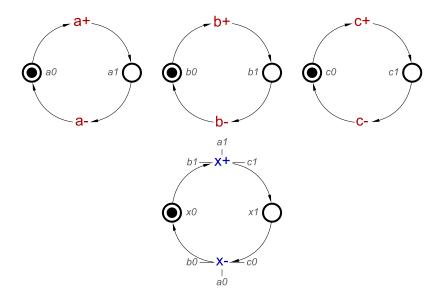

| 2.12 | Two possible implementations of a 3 input C-element              | 19 |

| 2.13 | Digital circuit converted to an STG                              | 20 |

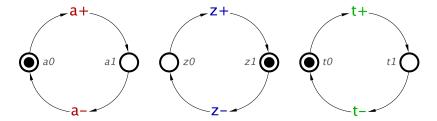

| 2.14 | Two formations of signal transition loops                        | 20 |

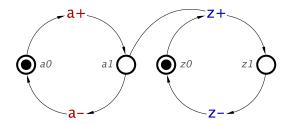

| 2.15 | An STG using loop formation of signal transition loops           | 21 |

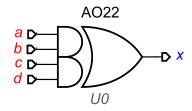

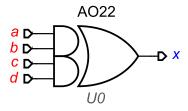

| 2.16 | AND-OR, or AO22 circuit icon                                     | 21 |

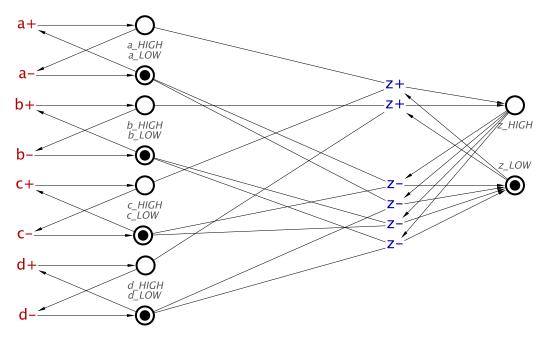

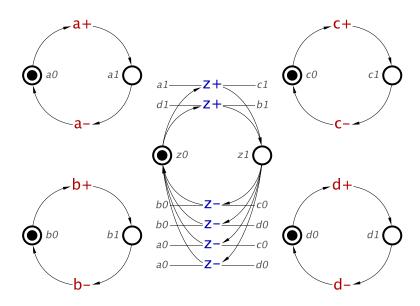

| 2.17 | Equivalent STGs for an AO22, both featuring an error             | 22 |

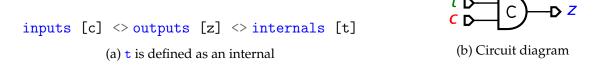

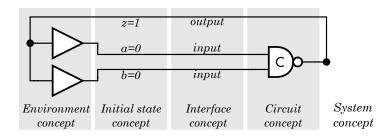

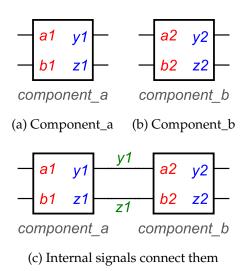

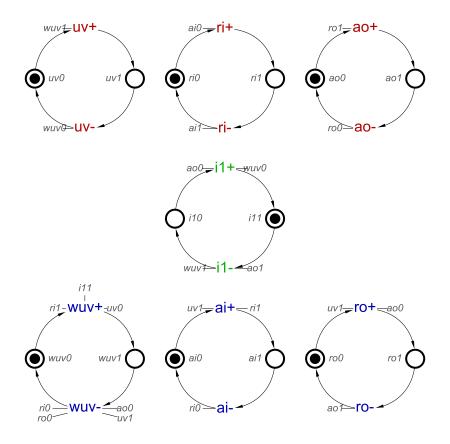

| 3.1  | Example of interface in a digital circuit                        | 33 |

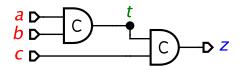

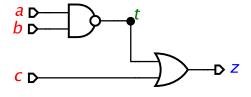

| 3.2  | First example specification with ${\tt t}$ as an output          | 34 |

| 3.3  | Second example specification with ${\tt t}$ as an internal       | 35 |

| 3.4  | Concepts and the translated STG for interface and initial state  | 36 |

| 3.5  | Translated STG with a single causality concept                   | 38 |

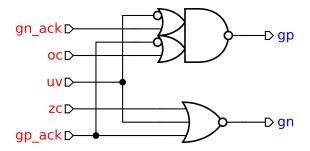

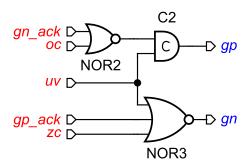

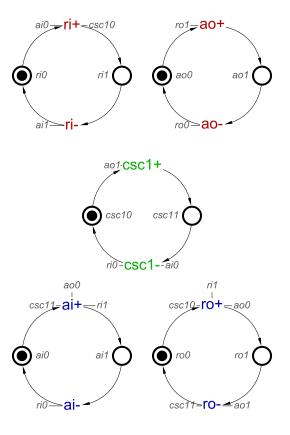

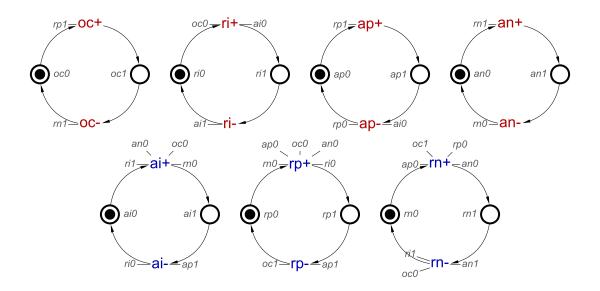

| 3.6  | Translated STG containing AND causality                                              | 38         |

|------|--------------------------------------------------------------------------------------|------------|

| 3.7  | Translated STG showing OR causality                                                  | 40         |

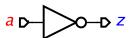

| 3.8  | Buffer circuit                                                                       | 41         |

| 3.9  | Translated STG of a buffer                                                           | 42         |

| 3.10 | Inverter circuit                                                                     | 42         |

| 3.11 | Translated STG of an inverter                                                        | 43         |

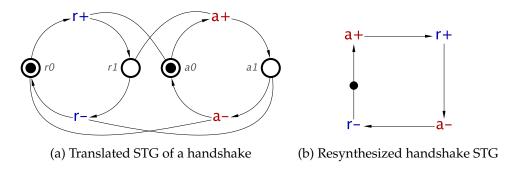

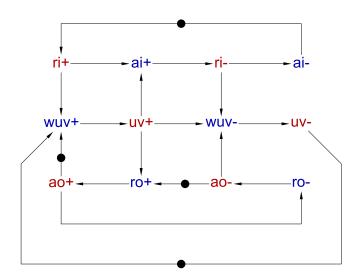

| 3.12 | The translated STG of a handshake, and its resynthesized version $\ \ldots \ \ldots$ | 44         |

| 3.13 | C-element circuit                                                                    | 45         |

| 3.14 | Translated STG of a C-element                                                        | 46         |

| 3.15 | OR gate circuit                                                                      | 46         |

| 3.16 | Translated STG of an OR gate                                                         | 47         |

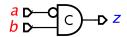

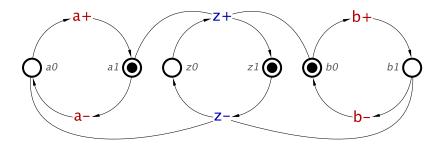

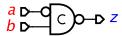

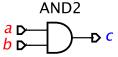

| 3.17 | AND gate circuit                                                                     | 47         |

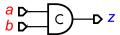

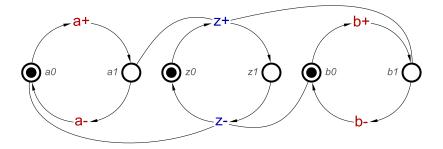

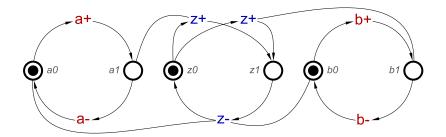

| 3.18 | Translated STG of an AND gate                                                        | 48         |

| 3.19 | XOR gate circuit                                                                     | 48         |

| 3.20 | Translated STG of an XOR gate                                                        | 50         |

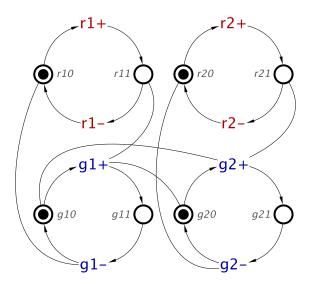

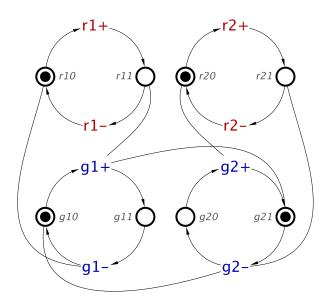

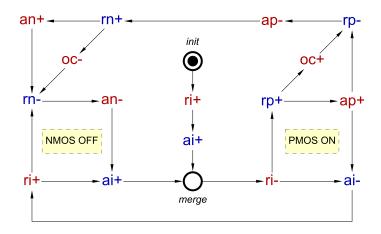

| 3.21 | Translated STG of a mutual exclusion concept                                         | 51         |

| 3.22 | Mutual exclusion element (metastability filter omitted for clarity)                  | 51         |

| 3.23 | Translated STG of a mutual exclusion element                                         | 52         |

| 3.24 | Commonly used gates that we have not specified before                                | 57         |

| 3.25 | Translated STG of example7                                                           | 58         |

| 3.26 | Translated STG of example8                                                           | 59         |

| 3.27 | Translated STG of example9                                                           | 60         |

| 3.28 | STG and circuit generated from example10                                             | 61         |

| 3.29 | STG and circuit generated from example11                                             | 62         |

| 3.30 | Example circuit to apply dual to                                                     | 64         |

| 3.31 | The dual of Figure 3.30                                                              | 65         |

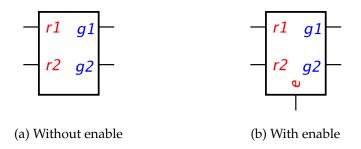

| 3.32 | Mutual exclusion elements with and without enable                                    | 67         |

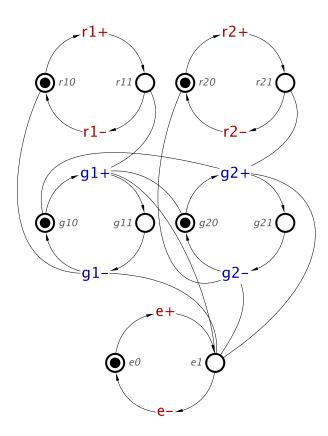

| 3.33 | STG of a mutual exclusion element with an enable signal                              | 69         |

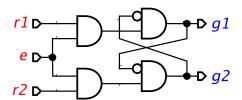

| 3.34 | Circuit implementation of a mutual exclusion element with enable                     | 69         |

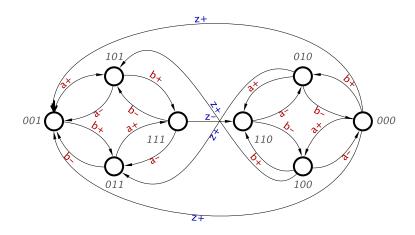

| 3.35 | Translated STG of example19                                                          | 71         |

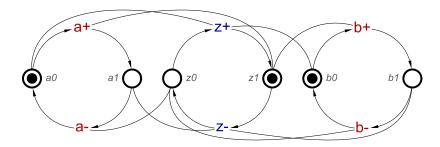

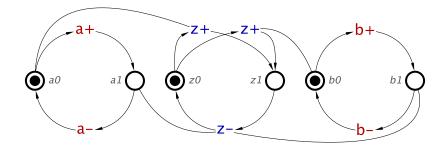

| 3.36 | Translated FSM of example19                                                          | 72         |

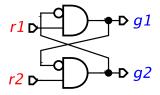

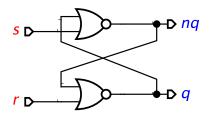

| 3.37 | Synthesized set-reset latch circuit                                                  | <b>7</b> 3 |

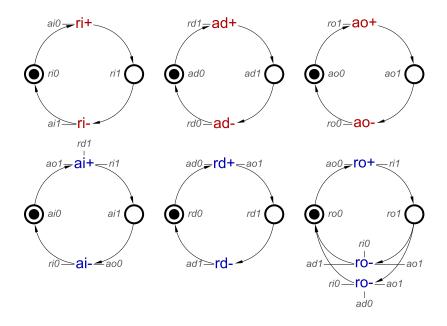

| 4.1  | Translated STG of example20                                                          | 82         |

| 4.2  | Synthesized circuit of example20                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 4.3  | Synthesized circuit from example21                                                                                         |

| 4.4  | InvertedGates user concept file, with reusable concepts 87                                                                 |

| 4.5  | A concept specification ready for translation                                                                              |

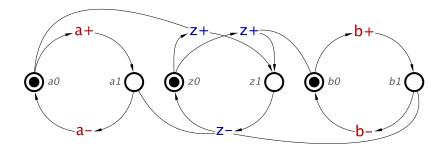

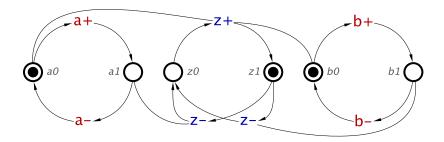

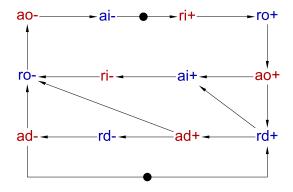

| 4.6  | STG and state graph translations of example23                                                                              |

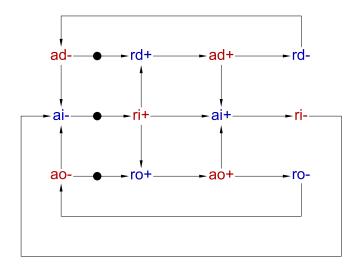

| 4.7  | Example of sequential combination                                                                                          |

| 4.8  | Example of concurrent combination                                                                                          |

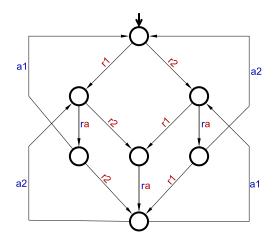

| 4.9  | Example of a choice combination                                                                                            |

| 4.10 | example24 translated to an STG                                                                                             |

| 4.11 | Technology mapped AND gate                                                                                                 |

| 4.12 | A circuit synthesized without technology mapping                                                                           |

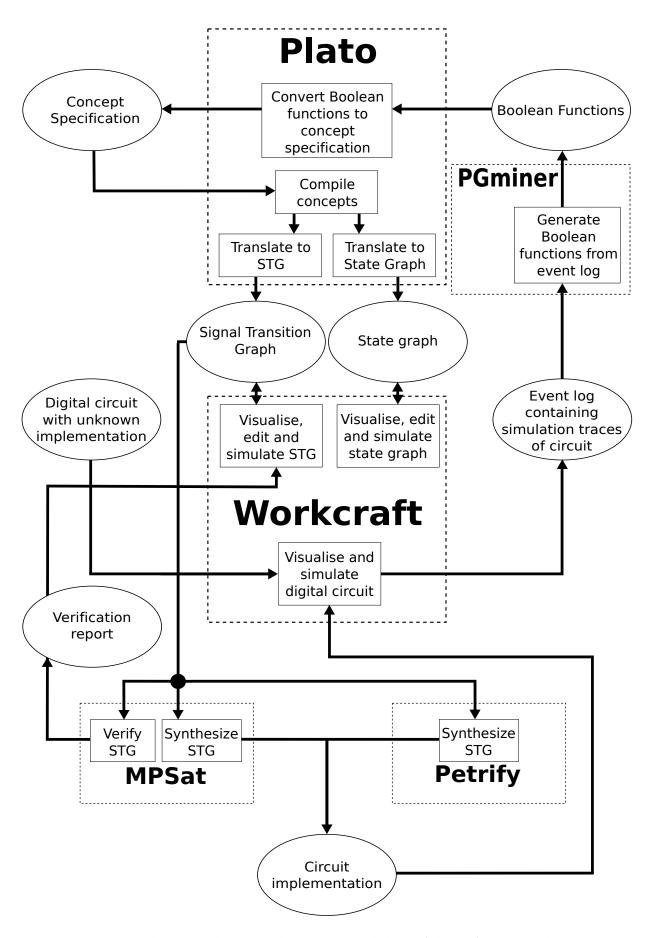

| 5.1  | A diagram showing the interoperability of the software tools                                                               |

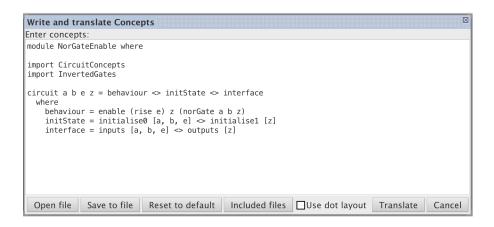

| 5.2  | 3-input NOR gate concept specification file                                                                                |

| 5.3  | behaviour concept in atomic form                                                                                           |

| 5.4  | Translated STG with initial states inserted                                                                                |

| 5.5  | Translated STG with one read arc inserted                                                                                  |

| 5.6  | Fully translated STG                                                                                                       |

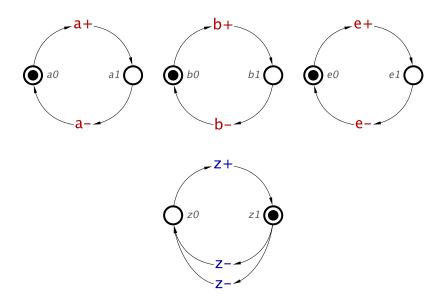

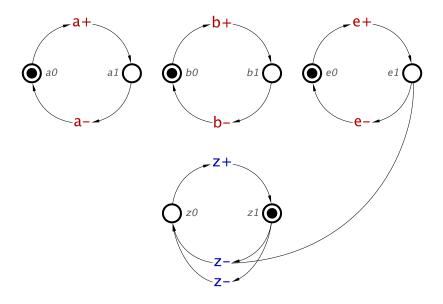

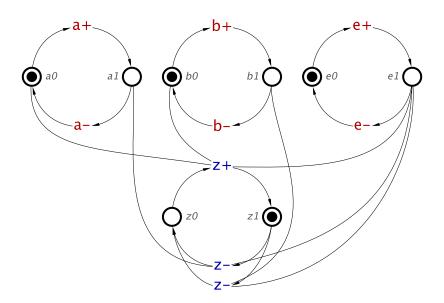

| 5.7  | example25 translated to a state graph                                                                                      |

| 5.8  | 3-input NOR gate concept file generated by Bool-to-Concepts $115$                                                          |

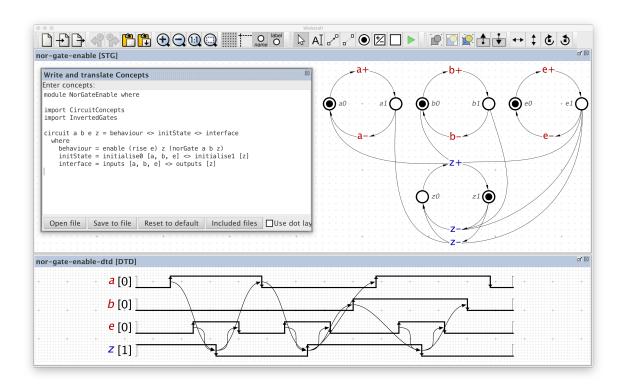

| 5.9  | Plato dialogue for authoring concepts                                                                                      |

| 5.10 | Plato include dialogue in Workcraft                                                                                        |

| 5.11 | Completed translation, and timing diagram of a concept specification $$ . $$ . $$ $$ $$ $$ . $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ |

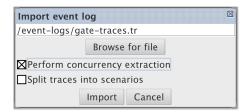

| 5.12 | PGminer import dialogue                                                                                                    |

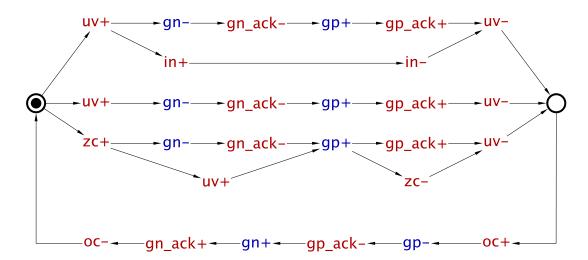

| 5.13 | STG specification of a simple buck controller                                                                              |

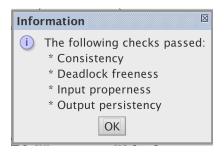

| 5.14 | Workcraft dialogue showing multiple satisfied verification properties $\dots$ 121                                          |

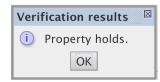

| 5.15 | Custom property dialogue for MPSAT                                                                                         |

| 5.16 | Dialogue indicating the custom property is satisfied                                                                       |

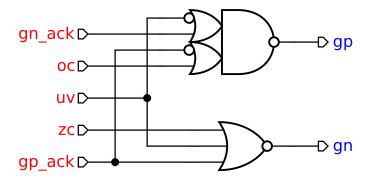

| 5.17 | Synthesized circuit from the STG seen in Figure 5.13                                                                       |

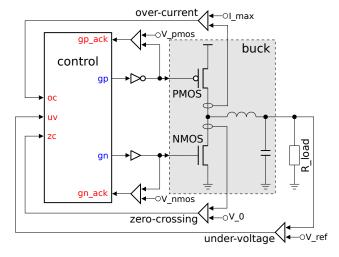

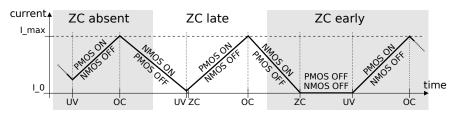

| 6.1  | Buck converter and its informal description                                                                                |

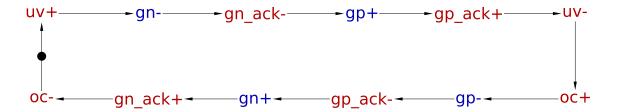

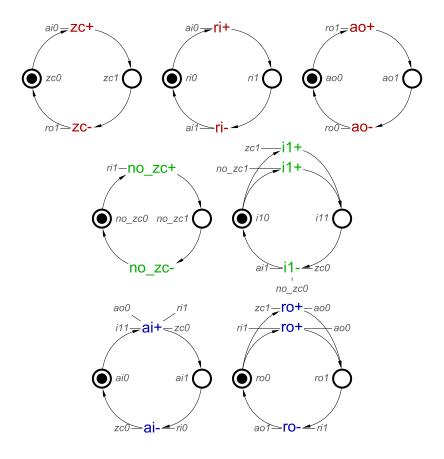

| 6.2  | Concept specification for the ZC absent scenario                                                                           |

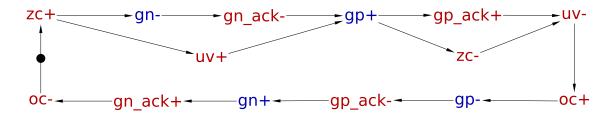

| 6.3  | STG translated from the zcAbsent concept and resynthesized 129                                                             |

| 6.4  | Concept specification for the ZC late scenario                                                                             |

| 6.5  | STG translated from the zcLate concept and resynthesized 129                                                               |

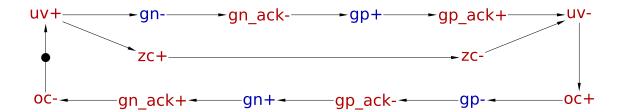

| 6.6  | Concept specification for the ZC early scenario                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.7  | STG translated from the zcEarly concept and resynthesized 131                                                                                                              |

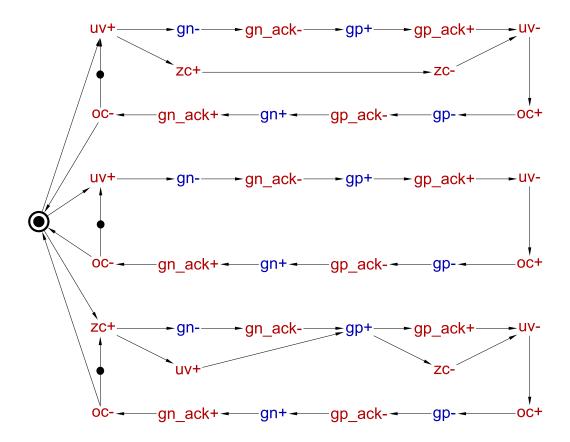

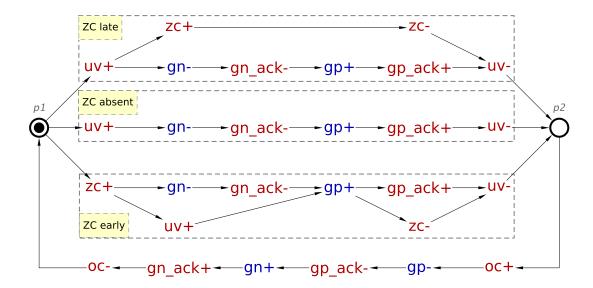

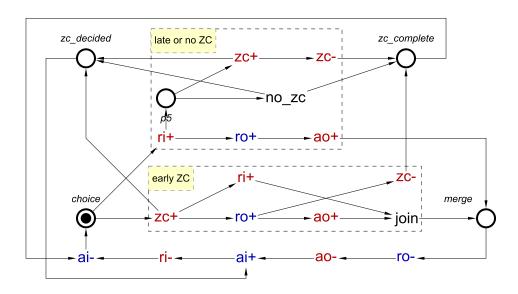

| 6.8  | Combined STG for a buck converter, featuring all three scenarios 132                                                                                                       |

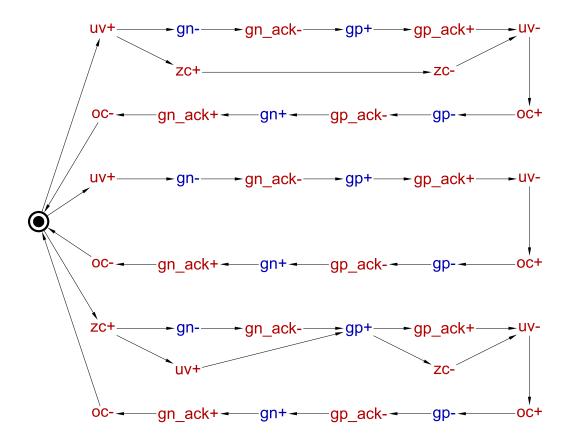

| 6.9  | STG for a buck converter, with some redundant arcs removed                                                                                                                 |

| 6.10 | Combined STG for a buck converter, featuring all three scenarios 134                                                                                                       |

| 6.11 | Complex gate synthesis result of full STG                                                                                                                                  |