## School of Engineering

Newcastle University

# Exploiting Robustness in Asynchronous Circuits to Design Fine-Tunable Systems

## Benafa Ikechukwu Oyinkuro

A thesis submitted for the degree of Doctor of Philosophy

#### **Declaration**

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements. This dissertation contains fewer than 65,000 words including appendices, bibliography, footnotes, tables and equations and has fewer than 150 figures.

Benafa Ikechukwu Oyinkuro

August 2018

#### **Abstract**

Robustness property in a circuit defines its tolerance to the effects of process, voltage and temperature variations. The mode signaling and event communication between computing units in a asynchronous circuits makes them inherently robust. The level of robustness depends on the type of delay assumptions used in the design and specification process. In this thesis, two approaches to exploiting robustness in asynchronous circuits to design self-adapting and fine-tunable systems are investigated. In the first investigation, a Digitally Controllable Oscillator (DCO) and a computing unit are integrated such that the operating conditions of the computing unit modulated the operation of the DCO. In this investigation, the computing unit which is a self-timed counter interacts with the DCO in a four-phase handshake protocol. This mode of interaction ensures a DCO and computing unit system that can fine-tune its operation to adapt to the effects of variations. In this investigation, it is shown that such a system will operate correctly in wide range of voltage supply. In the second investigation, a Digital Pulse-Width Modulator (DPWM) with coarse and fine-tune controls is designed using two Kessels counters. The coarse control of the DPWM tuned the pulse ratio and pulse frequency while the fine-tune control exploited the robustness property of asynchronous circuits in an addition-based delay system to add or subtract delay(s) to the pulse width while maintaining a constant pulse frequency. The DPWM realized gave constant duty ratio regardless of the operating voltage. This type of DPWM has practical application in a DC-DC converter circuit to tune the output voltage of the converter in high resolution. The Kessels counter is a loadable self-timed modulo-n counter, which is realized

by decomposition using Horner's method, specified and verified using formal asynchronous design techniques. The decomposition method used introduced parallelism in the system by dividing the counter into a systolic array of cells, with each cell further decomposed into two parts that have distinct defined operations. Specification of the decomposed counter cell parts operation was in three stages. The first stage employed high-level specification using Labelled Petri nets (LPN). In this form, functional correctness of the decomposed counter is modelled and verified. In the second stage, a cell part is specified by combing all possible operations for that cell part in high-level form. With this approach, a combination of inputs from a defined control block activated the correct operation for a cell part. In the final stage, the LPNs were converted to Signal Transition Graphs, from which the logic circuits of the cells were synthesized using the WorkCraft Tool. In this thesis, the Kessels counter was implemented and fabricated in 350 nm CMOS Technology.

### Acknowledgements

I would like to express appreciation to Prof. Alex Yakovlev my supervisor who introduced me to asynchronous circuits and systems and also guided and supported me during my PhD research.

I am grateful to my parents Mr Penakeme Benafa and Mrs Preye Benafa for their encouragement, support and advice before and during the period of this research.

I am also grateful to Dr Delong Shang and Dr Danil Sokolov for their assistance and valuable contributions to circuit design and modelling.

I would like to thank Mr Imran Ahmed, for his support and encouragement and not forgetting to mention Lorna Marshall.

I am also grateful to Graham Ewart, Darren Mackie, Paul Killan and Jeffrey Warren for their assistance in the electronics workshop.

This research was supported by the Niger Delta Development Commission (NDDC).

## **Table of contents**

| Li | st of f | igures  |             |                                    |       | xix  |

|----|---------|---------|-------------|------------------------------------|-------|------|

| Li | st of t | ables   |             |                                    |       | xxv  |

| 1  | Intr    | oductio | n           |                                    |       | 1    |

|    | 1.1     | Motiva  | ntion and ( | Objectives                         |       | . 1  |

|    | 1.2     | Resear  | ch Contril  | butions                            |       | . 2  |

|    | 1.3     | Public  | ations      |                                    |       | . 5  |

|    | 1.4     | Structu | ire of the  | Thesis                             |       | . 6  |

| 2  | Bac     | kground | ì           |                                    |       | 9    |

|    | 2.1     | Async   | hronous C   | Circuits                           | <br>• | . 9  |

|    | 2.2     | Classe  | s of async  | Phronous circuits                  |       | . 11 |

|    | 2.3     | Signal  | ling and d  | ata path communication conventions |       | . 12 |

|    |         | 2.3.1   | Single-ra   | ail encoding                       | <br>• | . 12 |

|    |         |         | 2.3.1.1     | Dual-rail encoding                 | <br>• | . 14 |

|    |         |         | 2.3.1.2     | Transition signalling protocol     | <br>• | . 14 |

|    |         |         | 2.3.1.3     | Level signalling protocol          | <br>• | . 14 |

|    | 2.4     | Forma   | l Specifica | ation of Asynchronous Circuits     |       | . 15 |

|    |         | 2.4.1   | Petri Net   | ts                                 | <br>• | . 15 |

|    |         | 242     | Petri Net   | t Fragments                        |       | 17   |

**xii** Table of contents

|   |      | 2.4.3    | Labelled     | Petri Nets (LPN)                          | 18 |

|---|------|----------|--------------|-------------------------------------------|----|

|   |      | 2.4.4    | Signal Tr    | ansition Graphs (STG)                     | 18 |

|   | 2.5  | Formal   | Verification | on of Asynchronous circuits               | 19 |

|   | 2.6  | Comple   | ete State C  | Coding                                    | 20 |

|   | 2.7  | Synthe   | sis of Asyı  | nchronous Circuits from STGs              | 21 |

|   | 2.8  | Approa   | ches to Ex   | aploiting Asynchronous Properties         | 22 |

|   |      | 2.8.1    | Low Pow      | er                                        | 23 |

|   |      | 2.8.2    | Robustne     | ss to Timing Variations                   | 23 |

|   |      | 2.8.3    | Elasticity   | in Data-Driven Circuits                   | 24 |

|   | 2.9  | Design   | process us   | sed in the thesis                         | 24 |

|   | 2.10 | Conclu   | sion         |                                           | 25 |

| 3 | Cour | nter Dec | compositio   | ons                                       | 27 |

|   | 3.1  | Introdu  | ction        |                                           | 27 |

|   | 3.2  | Synchr   | onous Mo     | dulo-nounters                             | 30 |

|   |      | 3.2.1    | Prescaled    | Binary Counters                           | 30 |

|   |      | 3.2.2    | Partitione   | ed Counters                               | 34 |

|   |      |          | 3.2.2.1      | Pipelined Non-Binary Counters             | 34 |

|   |      |          | 3.2.2.2      | Pipelined Binary Counters                 | 38 |

|   | 3.3  | Asynch   | ronous M     | odulo- <i>n</i> Counters                  | 39 |

|   |      | 3.3.1    | Decompo      | osition to interacting cells              | 40 |

|   |      |          | 3.3.1.1      | Kees van Berkel et al                     | 40 |

|   |      | 3.3.2    | Decompo      | osition to asynchronous circuit fragments | 43 |

|   |      |          | 3.3.2.1      | Ebergen et al                             | 43 |

|   |      | 3.3.3    | Cascaded     | toggle with completion detection          | 48 |

|   |      | 3.3.4    | Cascaded     | toggle with comparison circuit            | 51 |

|   | 3.4  | Conclu   | sion         |                                           | 52 |

Table of contents xiii

| 4 | Ada | ptive Digitally Controlled Oscillator based on Self-Timed Counter        | 55 |

|---|-----|--------------------------------------------------------------------------|----|

|   | 4.1 | Introduction                                                             | 55 |

|   | 4.2 | Overview of the Adaptive DCO                                             | 58 |

|   | 4.3 | Circuit Implementation                                                   | 60 |

|   |     | 4.3.1 Computing Unit (Self-Timed Counter)                                | 60 |

|   |     | 4.3.1.1 Measurements and Post-Layout Simulation of a 5-bits              |    |

|   |     | Counter                                                                  | 62 |

|   |     | 4.3.2 Delay system                                                       | 64 |

|   |     | 4.3.2.1 Coarse Delay Path                                                | 66 |

|   |     | 4.3.2.2 Asynchronous Controller                                          | 67 |

|   |     | 4.3.2.3 Fine Delay                                                       | 68 |

|   | 4.4 | Simulation Measurement                                                   | 68 |

|   | 4.5 | Conclusion                                                               | 71 |

| 5 | Loa | dable Kessels Counter                                                    | 73 |

|   | 5.1 | Introduction                                                             | 73 |

|   | 5.2 | Loadable Modulo- <i>n</i> Counter Overview                               | 75 |

|   | 5.3 | Decomposition of $-n$ by recursive rewriting                             | 76 |

|   | 5.4 | Decomposition of $-n$ using Horner's Method (Kessels approach)           | 77 |

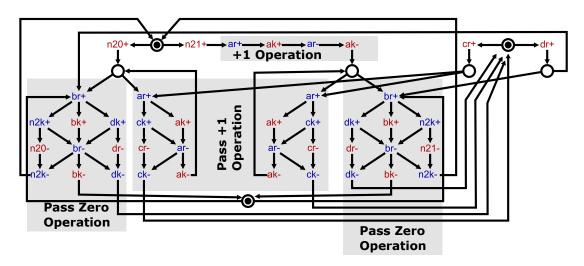

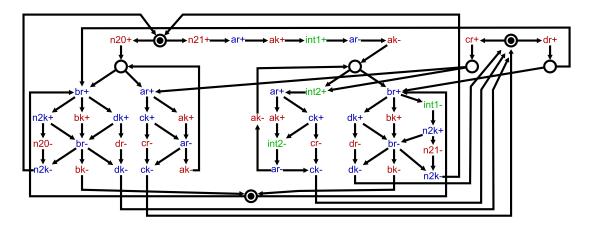

|   |     | 5.4.1 Identification of Cells and Cell Parts in decomposed counter       | 77 |

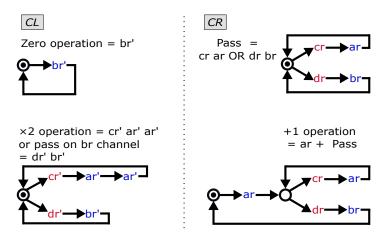

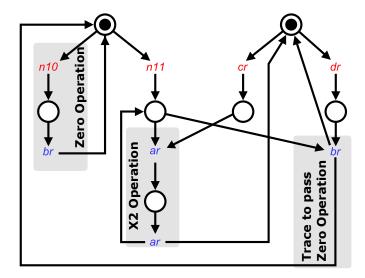

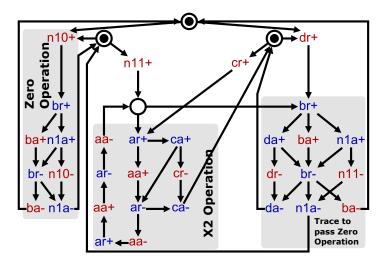

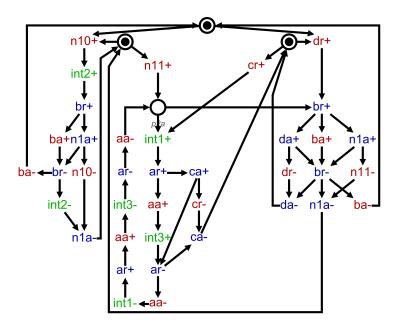

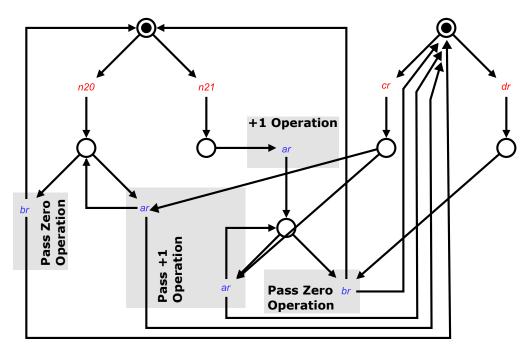

|   | 5.5 | Operations of Counter Cell Parts                                         | 78 |

|   |     | 5.5.1 Concurrency in Decomposed $CT_n$                                   | 80 |

|   | 5.6 | High Level Specification of Counter Cell Parts Operations                | 81 |

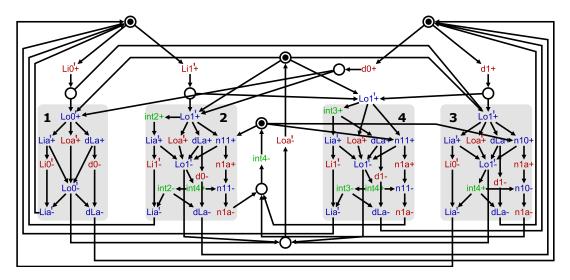

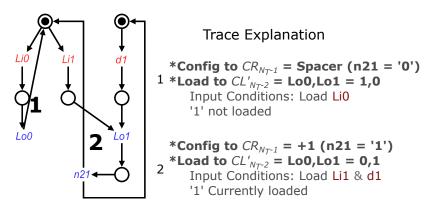

|   |     | 5.6.1 Modelling of Decomposed Count Modulo 5 by Unfolding                | 83 |

|   | 5.7 | Loadable Modulo $-n$ Counter decomposed into control and counter blocks. | 87 |

|   | 5.8 | Specification of Combined Operations in Each Counter Cell Part           | 90 |

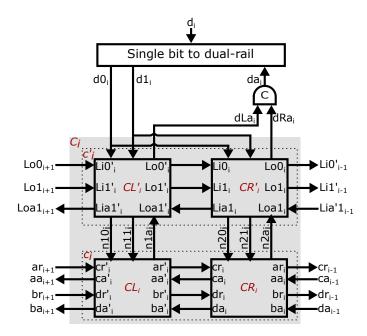

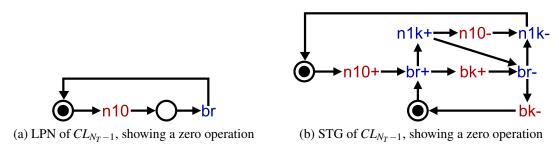

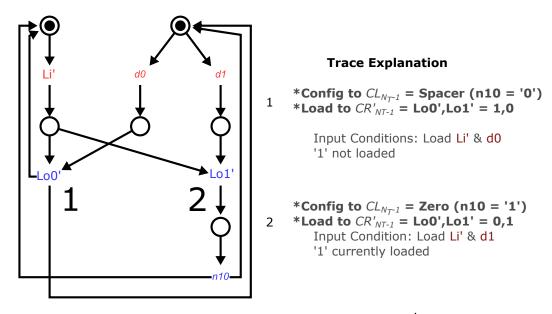

|   |     | 5.8.1 Counter Cell Part $CL_{N_T-1}$ Specification                       | 91 |

**xiv** Table of contents

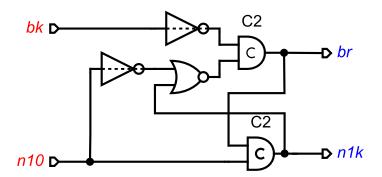

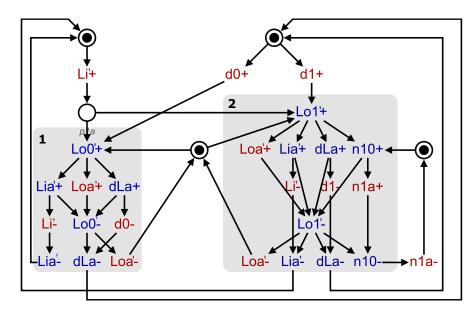

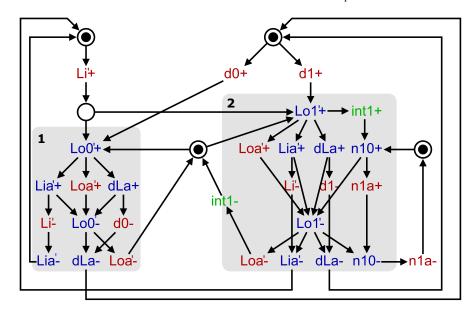

|     |         | 5.8.1.1   | High Level Specification                               | 91  |

|-----|---------|-----------|--------------------------------------------------------|-----|

|     |         | 5.8.1.2   | Circuit Synthesis and Implementation                   | 91  |

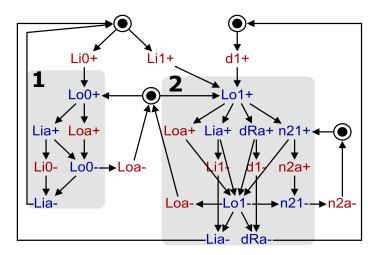

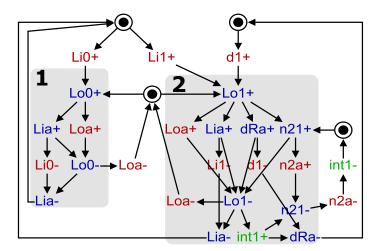

|     | 5.8.2   | Counter   | Cell Part $CL_i (0 \le i < N_T - 1) \dots \dots \dots$ | 91  |

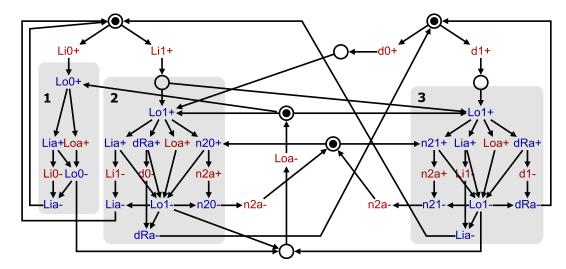

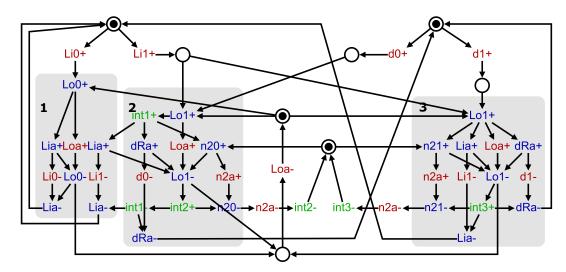

|     |         | 5.8.2.1   | High Level Specification                               | 92  |

|     |         | 5.8.2.2   | Low Level Specification                                | 92  |

|     | 5.8.3   | Counter   | Cell Part $CR_{N_T-1}$                                 | 94  |

|     |         | 5.8.3.1   | High Level Specification                               | 94  |

|     |         | 5.8.3.2   | Low Level Specification                                | 94  |

|     | 5.8.4   | Counter   | Cell Part $CR_i (0 \le i < N_T - 1) \dots \dots \dots$ | 94  |

|     |         | 5.8.4.1   | High Level Specification                               | 95  |

|     |         | 5.8.4.2   | Low Level Specification                                | 96  |

| 5.9 | Specifi | cation of | Control Block Parts                                    | 97  |

|     | 5.9.1   | Channel   | Encodings                                              | 97  |

|     |         | 5.9.1.1   | Single Bit to Dual-Rail Conversion of $d_i$            | 98  |

|     |         | 5.9.1.2   | Wrapper                                                | 99  |

|     |         | 5.9.1.3   | Control Cell Parts                                     | 99  |

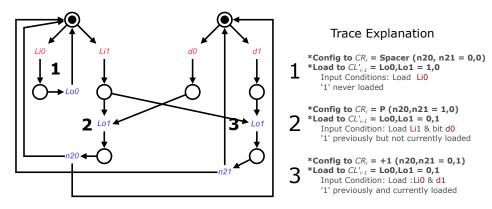

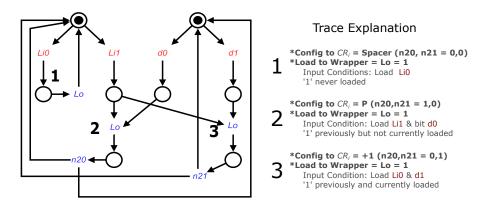

|     | 5.9.2   | Wrapper   | Specification                                          | 101 |

|     |         | 5.9.2.1   | High Level Specification                               | 101 |

|     |         | 5.9.2.2   | Low Level Specification                                | 101 |

|     | 5.9.3   | Control ( | Cell $CL'_{N_T-1}$ pecification                        | 103 |

|     |         | 5.9.3.1   | High Level Specification                               | 103 |

|     |         | 5.9.3.2   | Low Level Specification                                | 104 |

|     | 5.9.4   | Control ( | Cell $CL'_i(0 \le i < N_T - 1)$                        | 104 |

|     |         | 5.9.4.1   | High Level Specification                               | 106 |

|     |         | 5.9.4.2   | Low Level Specification                                | 107 |

|     | 5.9.5   | Control   | Cell $\mathit{CR}'_{N_T-1}$                            | 108 |

Table of contents xv

|   |       |           | 5.9.5.1    | High Level Specification                              | 108 |

|---|-------|-----------|------------|-------------------------------------------------------|-----|

|   |       |           | 5.9.5.2    | Low Level Specification                               | 109 |

|   |       | 5.9.6     | Control C  | Cell $CR'_i(0 \le i < N_T - 1)$                       | 109 |

|   |       |           | 5.9.6.1    | High Level Specification                              | 110 |

|   |       |           | 5.9.6.2    | Low Level Specification                               | 110 |

|   |       | 5.9.7     | Control C  | Cell $CR'_0$                                          | 111 |

|   |       |           | 5.9.7.1    | High Level Specification                              | 112 |

|   |       |           | 5.9.7.2    | Low Level Specification                               | 112 |

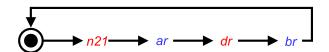

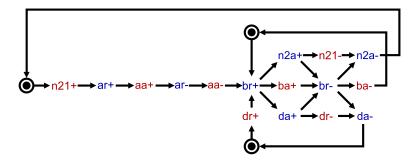

|   | 5.10  | Respon    | ise Time   |                                                       | 114 |

|   |       | 5.10.1    | Response   | e Time on Load Channel                                | 114 |

|   |       | 5.10.2    | Response   | e Time on ar Channel                                  | 116 |

|   |       | 5.10.3    | Response   | e Time on br Channel                                  | 117 |

|   | 5.11  | Power     | Consumpt   | ion                                                   | 117 |

|   | 5.12  | Measur    | rement Re  | sults                                                 | 118 |

|   |       | 5.12.1    | Post Laye  | out Simulation                                        | 118 |

|   |       | 5.12.2    | Testing o  | f Implemented Counter                                 | 119 |

|   |       |           | 5.12.2.1   | Continuous Counting and Seamless Loading Operations . | 121 |

|   |       |           | 5.12.2.2   | Average Power Consumption                             | 122 |

|   | 5.13  | Conclu    | sion       |                                                       | 123 |

| 6 | Digit | tal Pulse | e-width M  | lodulator                                             | 125 |

|   | 6.1   |           |            |                                                       | 125 |

|   | 6.2   | Propos    | ed Fine-Tu | ınable DPWM                                           | 128 |

|   |       | 6.2.1     |            | nisation Block                                        |     |

|   |       | 6.2.2     | •          | able Delay Block                                      |     |

|   |       | 6.2.3     |            | lock (Latch Control and Latch)                        |     |

|   | 6.3   |           | •          | sults                                                 |     |

|   |       |           |            |                                                       |     |

xvi Table of contents

|    | 6.4   | Conclu  | asion                                                             | 142 |

|----|-------|---------|-------------------------------------------------------------------|-----|

| 7  | Con   | clusion |                                                                   | 143 |

|    | 7.1   | Conclu  | nsion                                                             | 144 |

|    | 7.2   | Future  | Work                                                              | 147 |

| Aj | ppend | ix A V  | erilog Code For synthesised Counter Circuits                      | 149 |

|    | A.1   | Contro  | ol Cell Parts                                                     | 149 |

|    |       | A.1.1   | Synthesised Verilog Specification for the Single Bit to Dual-Rail |     |

|    |       |         | Converter                                                         | 149 |

|    |       | A.1.2   | Synthesised Verilog Specification for the Wrapper                 | 150 |

|    |       | A.1.3   | Synthesised Verilog Specification for Cell Part $CL'_{N_T-1}$     | 151 |

|    |       | A.1.4   | Synthesised Verilog Specification for Cell Part $CL'_i$           | 154 |

|    |       | A.1.5   | Synthesised Verilog Specification for Cell Part $CR'_{N_T-1}$     | 160 |

|    |       | A.1.6   | Synthesised Verilog Specification for Cell Part $CR'_i$           | 161 |

|    |       | A.1.7   | Synthesised Verilog Specification for Cell Part $CR'_0$           | 162 |

|    | A.2   | Contro  | l Cells                                                           | 166 |

|    |       | A.2.1   | Synthesised Verilog Specification for Control Cell $c'_{N_T-1}$   | 166 |

|    |       | A.2.2   | Synthesised Verilog Specification for Control Cell $c_i'$         | 166 |

|    |       | A.2.3   | Synthesised Verilog Specification for Control Cell $c_0'$         | 167 |

|    | A.3   | Contro  | l Block                                                           | 168 |

|    |       | A.3.1   | Synthesised Verilog Specification for Five Bit Control Block      | 168 |

|    | A.4   | Counte  | er Cell Parts                                                     | 169 |

|    |       | A.4.1   | Synthesised Verilog Specification for Cell Part $CL_{N_T-1}$      | 169 |

|    |       | A.4.2   | Synthesised Verilog Specification for Cell Part $CL_i$            | 170 |

|    |       | A.4.3   | Synthesised Verilog Specification for Cell Part $CR_{N_T-1}$      | 174 |

|    |       | A.4.4   | Synthesised Verilog Specification for Cell Part $CR_i$            | 176 |

| Table of contents | xvii |

|-------------------|------|

|                   |      |

| A.5               | Contro                                       | l Cells                                                                   | 179                                    |

|-------------------|----------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|

|                   | A.5.1                                        | Synthesised Verilog Specification for Control Cell $c_{N_T-1}$            | 179                                    |

|                   | A.5.2                                        | Synthesised Verilog Specification for Control Cell $c_i$                  | 180                                    |

| A.6               | Contro                                       | l Block                                                                   | 180                                    |

|                   | A.6.1                                        | Synthesised Verilog Specification for Five Bit Counter Block              | 180                                    |

| A.7               | Comple                                       | ete Counter                                                               | 182                                    |

|                   | A.7.1                                        | Verilog Specification for Five Bit Loadable Modulo $-n$ Counter $$ . $$ . | 182                                    |

| A.8               | Counte                                       | r Test                                                                    | 184                                    |

|                   | A.8.1                                        | VHDL Code to Test Implemented Counter                                     | 184                                    |

|                   |                                              |                                                                           |                                        |

| Append            | ix B V                                       | erilog Code For DPWM Circuits                                             | 189                                    |

| Append<br>B.1     |                                              | erilog Code For DPWM Circuits  ent                                        |                                        |

|                   | C elem                                       |                                                                           | 189                                    |

| B.1               | C elem                                       | ent                                                                       | 189<br>190                             |

| B.1               | C elem<br>Output                             | ent                                                                       | 189<br>190<br>190                      |

| B.1               | C elem<br>Output<br>B.2.1<br>B.2.2           | ent                                                                       | 189<br>190<br>190<br>190               |

| B.1<br>B.2        | C elem<br>Output<br>B.2.1<br>B.2.2<br>Synchr | ent                                                                       | 189<br>190<br>190<br>190<br>191        |

| B.1<br>B.2<br>B.3 | C elem<br>Output<br>B.2.1<br>B.2.2<br>Synchr | ent                                                                       | 189<br>190<br>190<br>190<br>191<br>192 |

# **List of figures**

| 1.1  | Illustration of LCO due to the effect of quantisation | 2  |

|------|-------------------------------------------------------|----|

| 2.1  | Modes of communication: Synchronous and Asynchronous  | 12 |

| 2.2  | Bundled data                                          | 13 |

| 2.3  | Bundled Data Communication Protocols                  | 13 |

| 2.4  | Dual-Rail Protocol                                    | 14 |

| 2.5  | Example: Single dining philosopher Petri net [1]      | 16 |

| 2.6  | Petri net Fragments                                   | 17 |

| 2.7  | Symbols of Asynchronous Circuits Fragments            | 17 |

| 2.8  | Example: STG of VME Bus Controller [1]                | 18 |

| 2.9  | CSC conflicts of STG of Figure 2.8 [1]                | 20 |

| 2.10 | Internal signal used to resolve conflicts [1]         | 21 |

| 2.11 | Resolved CSC conflicts of STG of Fig 2.8 [1]          | 21 |

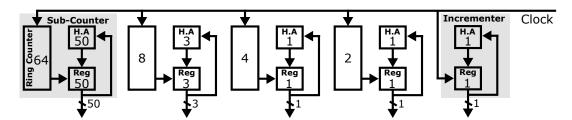

| 3.1  | Prescaled Counter                                     | 31 |

| 3.2  | Scaled Sub-Counter Decomposition Tree                 | 32 |

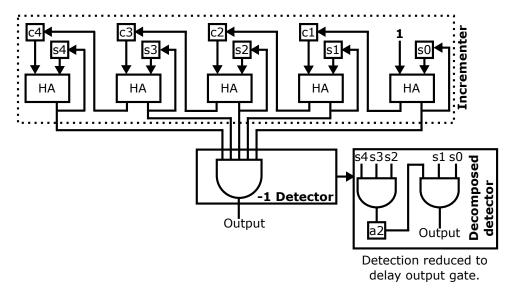

| 3.3  | Incrementer circuit which includes programmable unit  | 33 |

| 3.4  | Pipelined Half Adder Based Counter                    | 34 |

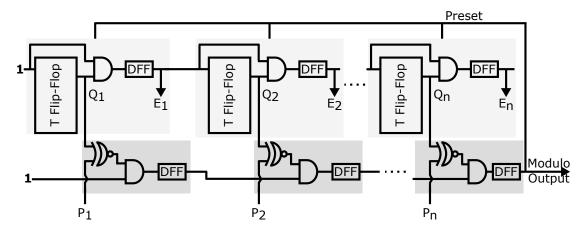

| 3.5  | Pipelined Counter with preset logic                   | 36 |

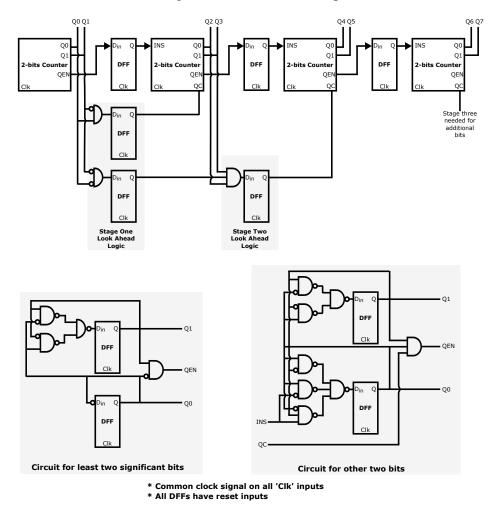

| 3.6  | Schematic of the State Look Ahead Logic Counter       | 38 |

xx List of figures

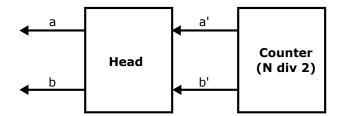

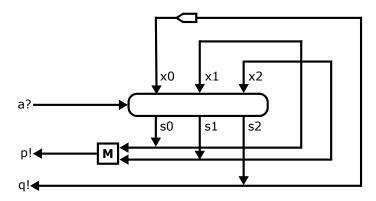

| 3.7  | Modulo-N counter showing Head and Count (N div 2) blocks                         | 41         |

|------|----------------------------------------------------------------------------------|------------|

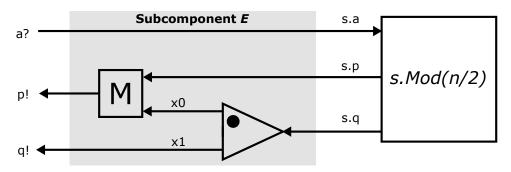

| 3.8  | Modulo-3 Counter decomposed into standard asynchronous fragments                 | <b>4</b> 4 |

| 3.9  | Counter decomposed into two sub-counters E and s.ModC(M) $\ \ \ldots \ \ \ldots$ | 46         |

| 3.10 | Counter decomposed into parallel operating parts                                 | 47         |

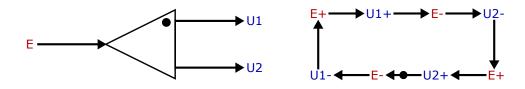

| 3.11 | Toggle Symbol and STG illustrating the sequence of operation from initial state  | 49         |

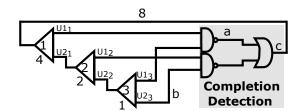

| 3.12 | Three-stage Cascaded Toggle showing count output at point a and Comple-          |            |

|      | tion Detection on point $b$                                                      | 49         |

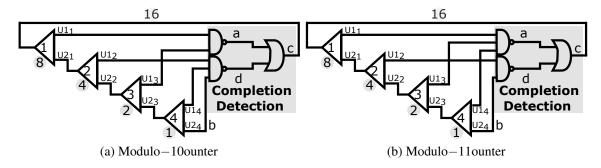

| 3.13 | Four stage Cascaded Toggle and Different Completion Detection Circuit to         |            |

|      | form a 10/11 to 1 output on points $a$ and $b$                                   | 50         |

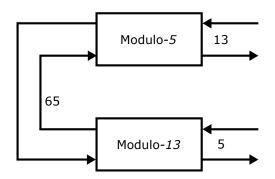

| 3.14 | Interaction of a modulo-5 counter and a modulo-13 counter to form a              |            |

|      | rational modulo 5/13 counter                                                     | 51         |

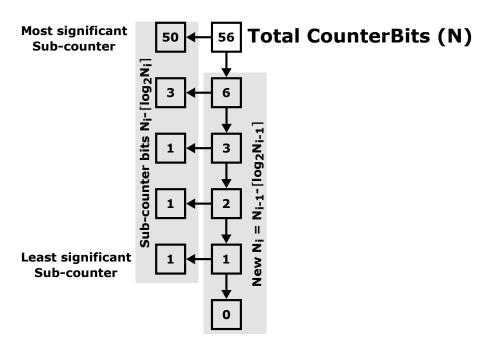

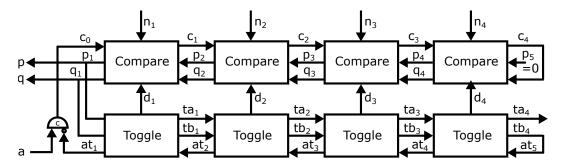

| 3.15 | Block diagram of the compare and toggle modulo $-n$ counter                      | 51         |

| 4.1  | Block diagram of the adaptive system proposed in [2]                             | 56         |

| 4.2  | Block Diagram of Proposed adaptive DCO System                                    | 59         |

| 4.3  | Schematic of a 1-bit Self-timed counter                                          | 60         |

| 4.4  | STG of 1-bit T-Latch counter                                                     | 60         |

| 4.5  | Schematic of a 3-bits Self-timed counter                                         | 61         |

| 4.6  | General State Transition Graph of a 3-bits Self-timed counter                    | 61         |

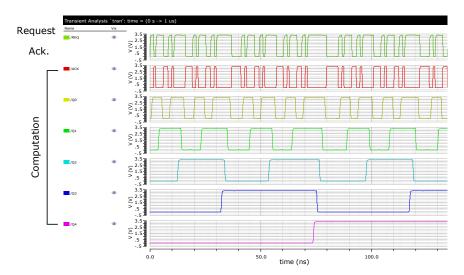

| 4.7  | Simulated Operation of the Self-Time Counter                                     | 63         |

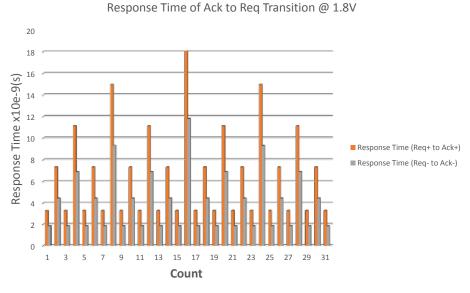

| 4.8  | Response Time Plots at $V_d d = 1.8V$                                            | 63         |

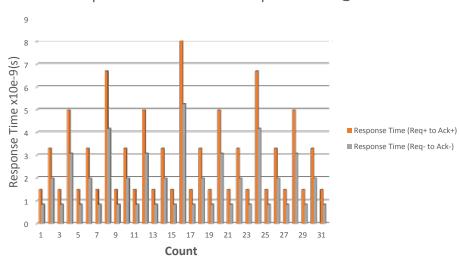

| 4.9  | Response Time Plots at $V_d d = 3.3V$                                            | 64         |

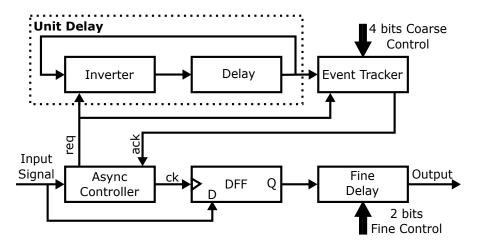

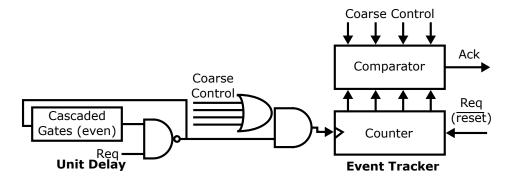

| 4.10 | Block Diagram of the Proposed Digital Controllable Delay                         | 65         |

| 4.11 | Unit Delay and Event Tracker Circuits that forms the Coarse Delay Path           | 66         |

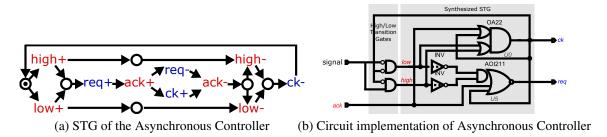

| 4.12 | STG and Circuit of the Asynchronous Controller                                   | 67         |

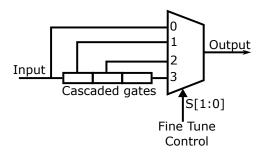

| 4.13 | Fine Tuning Circuit                                                              | 68         |

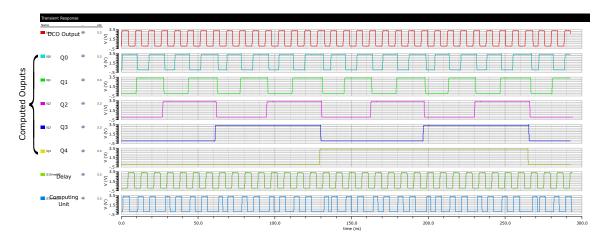

| 4.14 | Simulation Result of the DCO and integrated computing unit system at 3.3V        | 69         |

List of figures xxi

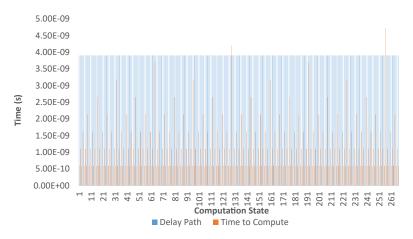

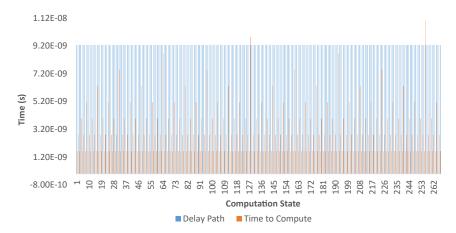

| 4.15 | Response Time of Delay Path and the Computing Unit @ 3.3V                    | 69 |

|------|------------------------------------------------------------------------------|----|

| 4.16 | Response of DCO output period to change in computing time @ 3.3V             | 69 |

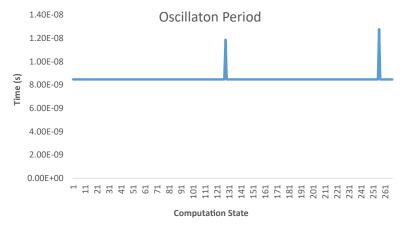

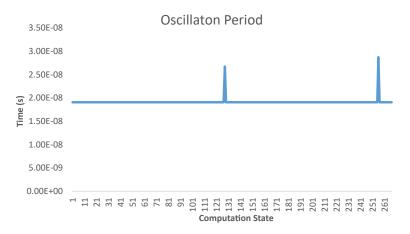

| 4.17 | Response Time of Delay Path and the Computing Unit @ 1.8 V                   | 70 |

| 4.18 | Response of DCO output period to change in computing time @ $1.8~\mathrm{V}$ | 70 |

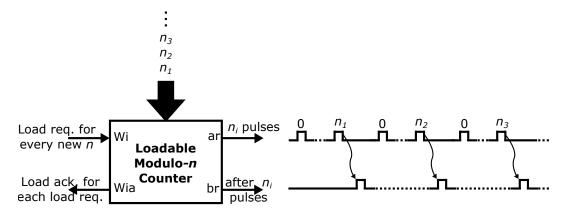

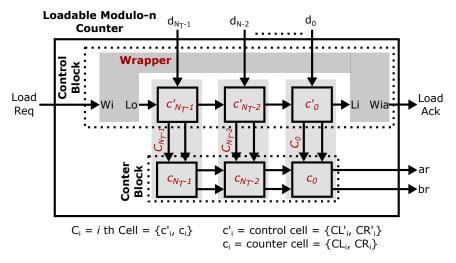

| 5.1  | Block Diagram of the Loadable Counter                                        | 75 |

| 5.2  | High Level Specification of the Loadable Modulo $-n$ Counter                 | 76 |

| 5.3  | Diagram illustrates parallel operation in counter cells for count 5 with no  |    |

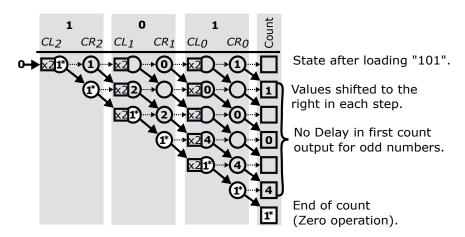

|      | delay before first count output                                              | 80 |

| 5.4  | LPN specifying even operations                                               | 82 |

| 5.5  | Counter Configuration for count 5                                            | 83 |

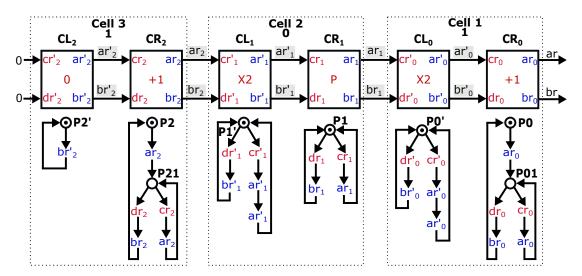

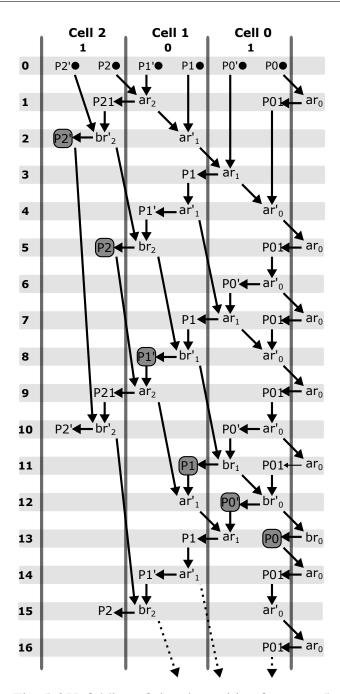

| 5.6  | Unfolding of signal transition for count 5                                   | 84 |

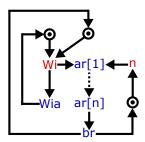

| 5.7  | Block diagram of the loadable modulo– $N$ counter                            | 88 |

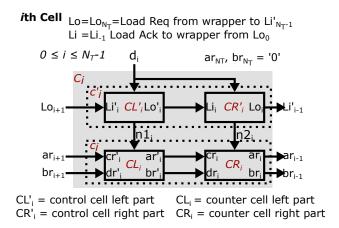

| 5.8  | Decomposed control and counter cells left and right parts                    | 89 |

| 5.9  | Block diagram of cell parts showing refined signal names                     | 90 |

| 5.10 | High and low level specifications for $CL_{N_T-1}$                           | 91 |

| 5.11 | Synthesised circuit of $CL_{N_T-1}$ STG                                      | 92 |

| 5.12 | LPN of $CL_i$ , with all possible operations                                 | 92 |

| 5.13 | STG of $CL_i$ , with all possible operations                                 | 93 |

| 5.14 | STG of $CL_i$ , with csc resolved                                            | 93 |

| 5.15 | LPN of $CR_{N_T-1}$ , showing a +1 operation                                 | 94 |

| 5.16 | STG of $CR_{N_T-1}$ , showing a +1 operation                                 | 94 |

| 5.17 | STG of $CR_{N_T-1}$ , with csc resolved                                      | 95 |

| 5.18 | LPN of $CR_i$ , showing a +1 and Pass operations                             | 95 |

| 5.19 | STG of $CR_i$ , showing a +1 and Pass operations                             | 96 |

| 5.20 | STG of $CR_i$ , with csc resolved                                            | 96 |

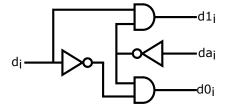

| 5.21 | Single Bit to Dual-Rail Conversion Circuit                                   | 98 |

**xxii** List of figures

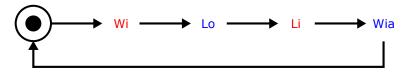

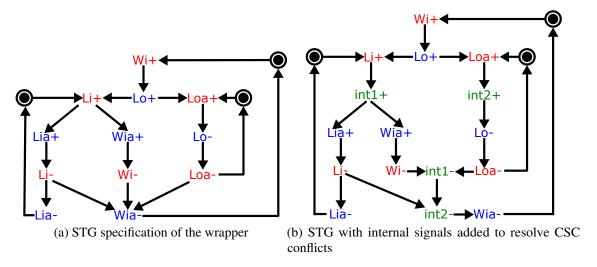

| 5.22 LPN of the Wrapper                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.23 Specification of the wrapper                                                                                                                                            |

| 5.24 LPN of MSC left control cell part $(CL'_{N_T-1})$                                                                                                                       |

| 5.25 STG specification for $CL'_{N_T-1}$                                                                                                                                     |

| 5.26 Resolved CSC conflicts for STG Fig 5.25                                                                                                                                 |

| 5.27 LPN of left control cell part $(CL'_i, 0 \le i < N_T - 1) \dots $ |

| 5.28 STG of control cell part $(CL'_i, 0 \le i < N_T - 1)$                                                                                                                   |

| 5.29 Resolved CSC conflicts for STG of Fig 5.28                                                                                                                              |

| 5.30 LPN of MSC right control cell part $(CR'_{N_T-1})$                                                                                                                      |

| 5.31 STG specification for $CR'_{N_T-1}$                                                                                                                                     |

| 5.32 Resolved CSC conflicts for STG of Fig 5.31                                                                                                                              |

| 5.33 LPN of Right Control Cell Part $(CR'_i, 0 < i < n_s - 1)$                                                                                                               |

| 5.34 STG specification for $CR'_{i}$ , $0 < i < N_{T} - 1$                                                                                                                   |

| 5.35 Resolved CSC conflicts for STG of Fig 5.34                                                                                                                              |

| 5.36 LPN of LSB Right Control Cell Part $(CR'_0)$                                                                                                                            |

| 5.37 STG specification for $CR'_0$ )                                                                                                                                         |

| 5.38 Resolved CSC conflicts for STG of Fig 5.37                                                                                                                              |

| 5.39 Layout of the implemented 5-bits counter                                                                                                                                |

| 5.40 Die photo of a 5-bits self-timed modulo $-n$ counter                                                                                                                    |

| 5.41 Oscillogram of implemented counter output showing continuous count oper-                                                                                                |

| ation                                                                                                                                                                        |

| 5.42 Oscillogram of implemented counter output showing seamless count transition 12:                                                                                         |

| 5.43 Average Power at delay of $1\mu$ s to acknowledgement to $ar$ and $br$ events 12                                                                                        |

| 5.44 Average Power at delay of $5\mu$ s to acknowledgement to $ar$ and $br$ events 12                                                                                        |

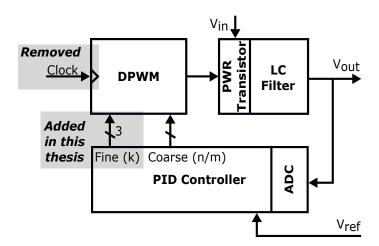

| 6.1 Block Diagram of DC-DC Converter                                                                                                                                         |

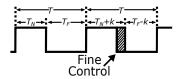

| 6.2 Illustration of fine tune control on a DPWM output                                                                                                                       |

|                                                                                                                                                                              |

| T : C C         | •••   |

|-----------------|-------|

| List of figures | XXIII |

| List of figures | AAIII |

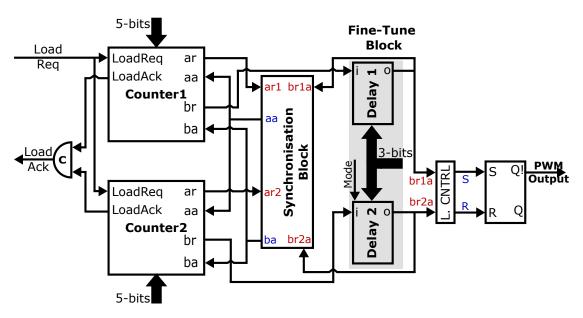

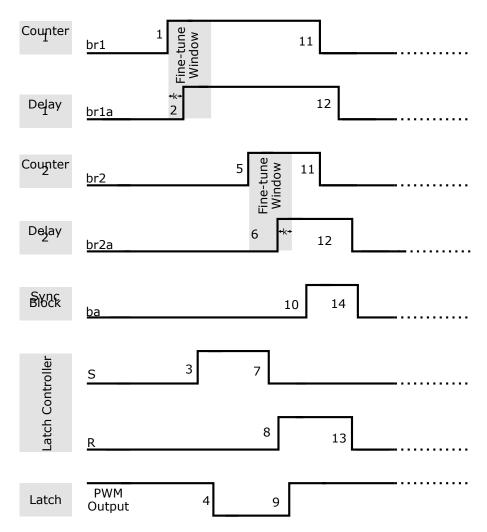

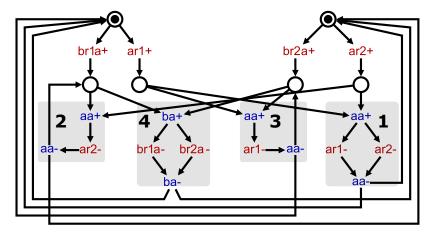

| 6.3 | Block diagram of proposed PWM                    | 129 |

|-----|--------------------------------------------------|-----|

| 6.4 | Timing diagram of the proposed DPWM              | 130 |

| 6.5 | STG of the Synchronisation Block                 | 131 |

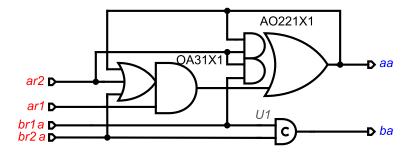

| 6.6 | Synthesised circuit of the Synchronisation Block | 132 |

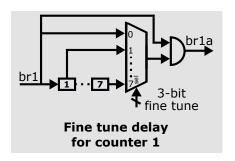

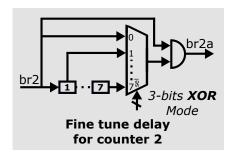

| 6.7 | Circuit of Fine tunable delay block              | 133 |

| 6.8 | STG of the Latch Control                         | 135 |

| 6.9 | Synthesised Circuit of the Latch Control         | 135 |

# List of tables

| 3.1  | Table shows scan sequence and state of carry-ins for a modulo-20 counter,     |     |

|------|-------------------------------------------------------------------------------|-----|

|      | starting from 20's complement                                                 | 35  |

| 3.2  | Table shows sequence of scan and state of combinational circuit at each scan. | 37  |

| 3.3  | Table shows the logic for completion detection circuit for each count output  |     |

|      | on point $a$ and $d$                                                          | 50  |

| 5.1  | Table shows decomposition of $N$ in the range of 0 to 15 into Left and Right  |     |

|      | operation                                                                     | 78  |

| 5.2  | Table shows operation of dormant cell parts as spacers (-) in both left and   |     |

|      | right parts                                                                   | 79  |

| 5.3  | Input Signal Names of Counter Cell Parts in each Channel                      | 82  |

| 5.4  | Output Signal Names of Counter Cell Parts in each Channel                     | 82  |

| 5.5  | Relationship between refined signal names of Figure 5.9                       | 98  |

| 5.6  | Relationship between refined signal names of Figure 5.9                       | 98  |

| 5.7  | Response Time of the wrapper                                                  | 103 |

| 5.8  | Measured Response Time on Load Channel for each Control Cell Part             | 115 |

| 5.9  | Measured Response Time on Configuration Channel for each Control Cell Part    | 116 |

| 5.10 | Response Time                                                                 | 119 |

| 5.11 | Measured Area Consumed by each Cell Part                                      | 120 |

| <b>:</b> | I int of told of |

|----------|------------------|

| XXVI     | List of tables   |

| 6.1 | DPWM Output Ratio with Fine-Tune Mode Off |  |

|-----|-------------------------------------------|--|

| 6.2 | Coarse Control Ratio 3/11                 |  |

| 6.3 | Coarse Control 10/17                      |  |

| 6.4 | Coarse Control 4/8                        |  |

| 6.5 | Coarse Control 21/31                      |  |

# Acronyms

| CL counter cell left part.                    |

|-----------------------------------------------|

| CR counter cell right part.                   |

| $CT_n$ counter.                               |

| $C_i$ ith cell.                               |

| $c_i'$ ith control cell.                      |

| $c_i$ ith counter cell.                       |

| Ack Acknowledgement.                          |

| CSC Complete State Coding Conflict.           |

| <b>CSP</b> Communicating Sequential Protocol. |

| <b>DFF</b> D Flip-Flop.                       |

| DI Delay Insensitive.                         |

| DLL Delay locked loop.                        |

| <b>DPWM</b> Digital Pulse-width Modulator.    |

| HA Half adder.                                |

**xxviii** Acronyms

**IoT** Internet of Things. LCO Limit Cycle Oscillation. LPN Labelled Petri net. LSB Least significant bit. MSBs Most significant bits. PLL Phase locked loop. PN Petri net. **PVT** Process Voltage and Temperature. **QDI** Quasi-delay Insensitive. Req Request. SI Speed Independent. **STG** Signal Transition Graph.

VLSI Very Large Scale Integration.

## Chapter 1

## Introduction

## 1.1 Motivation and Objectives

Time constraints which includes setup and hold times are subject to Process Voltage and Temperature (PVT), ageing, coupling and clock jitter etc must be considered when choosing the minimum clock period in synchronous systems [3]. These timing requirements present two operational limits which are of concern in this thesis.

Firstly, a computing system operating in a harsh environment may require an intelligent input clock control system that is sensitive to changes in the operating environment of the computing system to avoid computational error by dynamically tuning the clock frequency [3–10, 2]. In this approach, response time, metastability and sensing precision of the control system are factors which determine the reliability of the system. Addressing these factors are non trivial.

Secondly, due to the discrete nature of digital circuits and the coarse nature of the clock, digital systems are prone to issues of quantisation when applied in measuring or controlling analogue quantities.

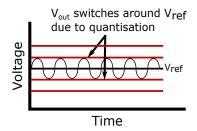

For example, quantisation in DC-DC converter that employs a Digital Pulse-width Modulator (DPWM) may cause the converter to go into a state known as Limit Cycle 2 Introduction

Fig. 1.1 Illustration of LCO due to the effect of quantisation

Oscillation (LCO) [11], illustrated in Figure 1.1. The converter system may spend time and energy trying to exit this state by tuning the input clock frequency and the pulse ratio of the DPWM and this can ultimately affect the quality of the converter output. The minimum clock period required for correct and reliable operation of the DPWM can limit fine-tuning its pulse-width in high frequency.

In this thesis, the two operational limits of synchronous systems mentioned above are addressed by investigating methods by which robustness in asynchronous circuits can be exploited to design adaptable and fine-tunable systems.

Asynchronous systems operate by local synchronisation and communication of events between computing units. The mode of communication and data validation between computing units enable asynchronous systems to perform reliably in the presence of PVT variations and logic gates delay changes, thus asynchronous circuits are said to be robust in nature. Robustness can be exploited in the design of systems that can adapt their operations to changes in circuit operating conditions [12, 13]. In the asynchronous circuits review section in this thesis, it is shown that robustness in asynchronous systems depend on the delay assumptions used in specifying and realising their circuits.

#### 1.2 Research Contributions

Two approaches to methods by which robustness in asynchronous circuits can be exploited to design adaptable and fine-tunable systems were investigated in this thesis.

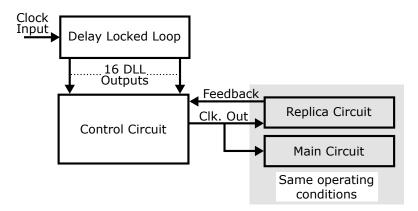

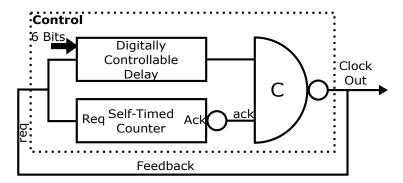

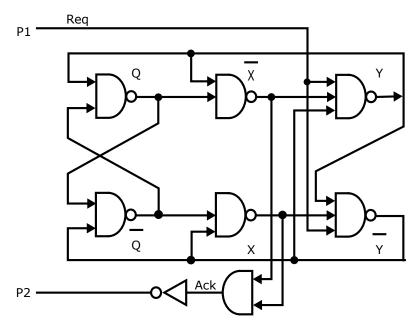

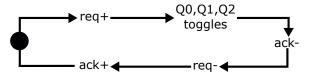

The first investigation presented a method of integrating a tunable input clock and its triggered computational unit which is self-timed, such that the operation of the system dynamically adapts to annul the effects of variation. In this investigation, a self-timed computing unit and a Digitally Controlled Oscillator (DCO) with coarse and fine-tune controls were integrated as one unit such that the structure of the system ensured the status and operating conditions of the computing unit modulated the DCO operation. This is achieved with the use of a completion detection system between the DCO and the computing unit in a feedback loop ensuring that the oscillator can only send a request (rising transition) when the computing unit is idle.

The computing unit used in the first approach is a self-timed counter whose next task completion time varies, depending on its present state. This behaviour can be seen to model changes in circuit delay due to variation making it suitable for this investigation. Later in this thesis, it is shown through simulation that the operation of the integrated DCO-computation system would operate correctly over a wide range of voltage supply.

The second investigation presented an application in which a more complex and reconfigurable asynchronous system is used to demonstrate how robustness can be exploited to design fine-tunable digital systems employed in analogue control circuitry like the DC-DC converter. A DPWM with coarse and fine-tune controls was designed in this investigation. The main component of the DPWM is a loadable Kessels counter which is a loadable self-timed modulo—n counter. Two such counters formed the coarse control of the DPWM, while a fine-tune control system which is an addition based delay ensured a constant pulse period while fine-tuning the pulse-width. It is proposed that an asynchronous DPWM will accommodate the addition of arbitrary delay(s) to fine-tune the pulse-width in a given period without violating time margin requirements of its circuit. This is investigated in chapter 6 of this thesis.

4 Introduction

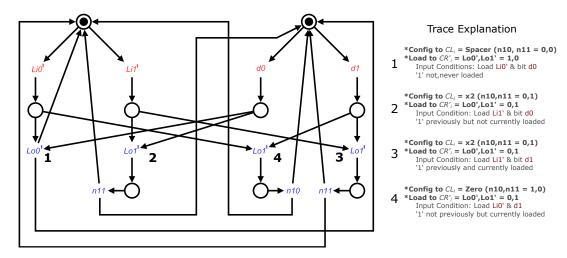

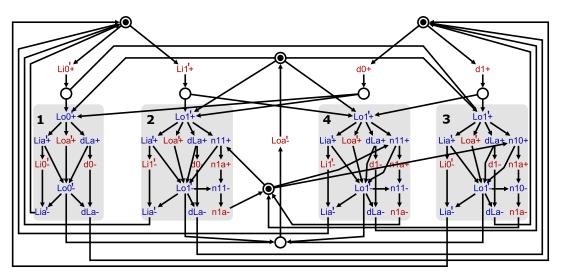

The loadable kessels counter was realised in a top-down approach in which formal methods are employed in defining, decomposing and specifying the counter behaviour. This includes the following steps:

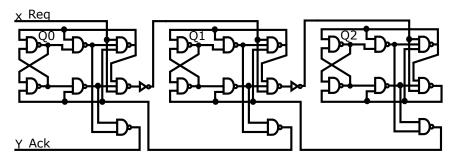

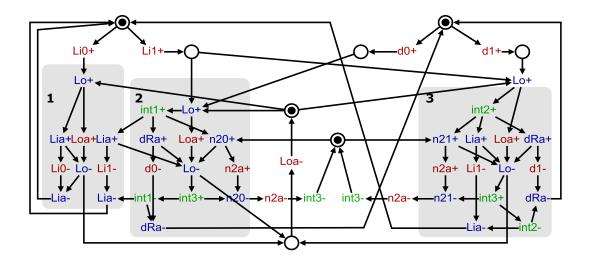

- High-level rewriting, specification and decomposition of the loadable counter into systolic array of cells using Horner's Method. Each counter cell is further decomposed into left and right cell parts. This method of decomposition was first proposed by Kessels [14].

- Definition of the different conditions and range of possible operations for each counter cell parts. This approach led to a reconfigurable counter operation.

- Specification of the counter cells operations using formal models: High level specification using Labelled Petri net (LPN) [15] and low level specification using Signal Transition Graph (STG) [16]. Low level specification also included Complete State Coding Conflict (CSC) conflict resolution when needed to realise synthesisable specifications. The WorkCraft Tool [1] developed at Newcastle University was used extensively at this stage for LPN and STG editing, verification and simulation of each specification and synthesis of the STGs. This stage involved three steps:

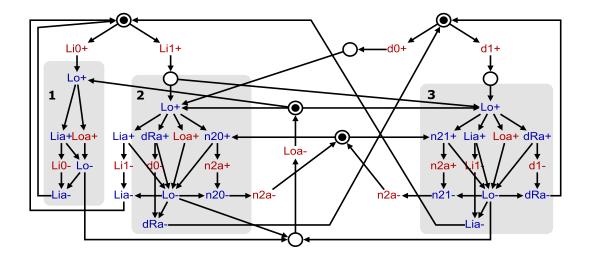

- Each cell part operation was specified using LPN. In this stage, the functional correctness of the decomposed counter was modelled and verified by unfolding of actions using directed graphs.

- 2. The LPN of all possible operations for each cell part were combined such that a combination of inputs from a defined control block and an adjacent cell part activated the correct operation in a given cell part.

- 3. The LPNs were converted to STG, which showed ordered rising and falling transitions of interacting signals in the system. At this stage, CSC errors present

1.3 Publications 5

in the specification were resolved by strategic addition of internal signals. The logic equations for each cell part were synthesized from its CSC error free STG.

- Design of a control block which consists of interacting control cells (each cell is divided into two cell parts), each in a one-to-one configuration relationship with the counter cells.

- Specifications of load channel encodings between interacting control cell parts and configuration channel encodings between each interacting control and counter cell parts.

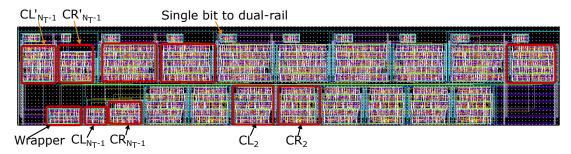

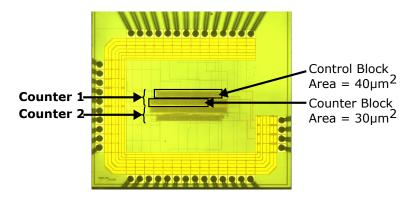

- Synthesis of the logic equations of the specifications from which the counter was implemented and fabricated in 350 nm CMOS Technology. This involved technology mapping of synthesised gates to AMS 350 nm CMOS standard cells library.

- Characterisation of the loadable self-timed modulo—n counter response time and power consumption.

A DPWM with both coarse and fine-tune controls is realised by synchronising the operations of two loadable Kessels counters. A practical example of how robustness in asynchronous circuits can be exploited actively is presented with an addition based tunable delay system used to provide the fine-tuning circuit of the DPWM.

#### 1.3 Publications

The following is a list of publications and paper(s) to be submitted for review as a result of this research work.

D. Shang, O. Benafa, F. Xia, Y. Xu and A. Yakovlev, "An elastic timer for wide dynamic working range," 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, 2015, pp. 1-4. 6 Introduction

O. Benafa, A. Ogweno, D. Shang and A. Yakovlev, "Design of a DCO based on the worst-case delay of a self-timed counter and a digitally controllable delay path,"

2016 14th IEEE International New Circuits and Systems Conference (NEWCAS),

Vancouver, BC, 2016, pp. 1-4.

- O. Benafa, D. Sokolov and A. Yakovlev, "Loadable Kessels Counter" Presented in ASYNC 2018 conference in Vienna, Austria.

- O. Benafa and A. Yakovlev, "Exploiting robustness in asynchronous systems using loadable self-timed Kessels Counters," Journal to be submitted for review.

#### 1.4 Structure of the Thesis

This thesis is organised as follows:

- Chapter 2 This chapter gives a background study of asynchronous circuits and systems.

This includes basic definitions of asynchronous terms, classification of asynchronous circuits and formal methods of specifying asynchronous circuits. This chapter also presents methods and applications in which robustness in asynchronous circuits have been exploited.

- Chapter 3 This chapter presents relevant counter and modulo—n counter decompositions. The counters are grouped under synchronous and asynchronous counters. This chapter is a review of counter decompositions, a precursor to the loadable self-timed modulo—n counter realised in Chapter 5.

- Chapter 4 A robust system formed by integrating a DCO and computing unit is investigated and presented in this chapter.

- Chapter 5 In this chapter, a loadable self-timed modulo-n counter which takes a quantity, n, in space and converts it to time is realised by formal specification and formal

asynchronous design techniques. The counter was also synthesised and fabricated in 350 nm CMOS Technology. Simulation and test results of the counter are included in this chapter.

- Chapter 6 This chapter investigates a practical application of the loadable self-timed counter in the design of a DPWM with coarse and fine-tune controls.

- Chapter 7 This chapter summarises the design methods and results in this thesis. It also discussed the main areas for future works based on the results presented in this thesis.

# Chapter 2

# **Background**

This chapter presents basic definitions of asynchronous terms and formal methods of asynchronous specification and verification. This forms the background study for the asynchronous circuits described in the proceeding chapters. The last two sections before concluding this chapter presents a brief review of methods of synthesizing asynchronous circuits and approaches to exploiting asynchronous circuit properties.

## 2.1 Asynchronous Circuits

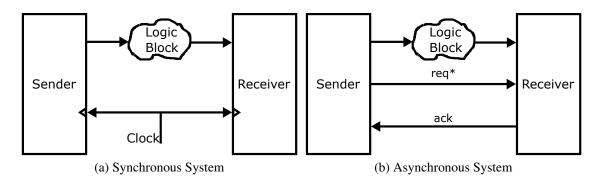

Computing operation between units in an asynchronous system is synchronised using handshaking techniques. This method of synchronisation differentiates asynchronous systems from synchronous systems in which operations are synchronised by a global clock.

The use of a global clock simplifies system design and verification process. However, there are some limits imposed on the system when compared to asynchronous systems. These limits are:

• The clock period and clock distribution must be carefully chosen to accommodate the circuits design margins such as, set-up and hold time of the logic gates, ageing which affects the circuits over time, process, voltage and temperature variations [19–21]. It

is required that the clock period is large enough to guarantee hazard free operation of the circuit as the design margins may change over time or due to environmental conditions.

- The clock period must accommodate the worst-case delay of the combinational logic blocks in the system [22].

- Constant switching of the clock results in dynamic power loss [23], although methods

of controlling and minimising dynamic power loss have been presented (clock gating

[24], dynamic voltage scaling [25] and dynamic frequency and voltage scaling [26]).

However, application of any of these techniques may result in a trade-off in system

performance in terms of operating speed and area consumed.

- Any arbitrary delay introduced into the system without considering the clock period can result in hazardous or incorrect operation.

In asynchronous circuits, a computing unit initiates a handshake process by sending a request signal to the receiving unit, indicating the validity of the data to be sent over for computation. The receiving unit returns an acknowledgement signal to the sender after consuming the data. The sending unit can initiate a new handshake transaction after it has received an acknowledgement from the receiving unit. This gives asynchronous circuits the following advantages over synchronous circuits [27–31].

- Dynamic power loss is minimised because switching in different sections of the system is event-driven.

- Asynchronous circuits operate at average case speed instead of worst-case speed as

in synchronous circuits. This point can be contested especially since bundled data

systems typically allows for 100% overestimate of the matching delay to cater for

variability.

- Asynchronous circuits are robust due to handshake communication between units

and thus can tolerate process, voltage and temperature variations to a large extent

depending on the delay assumptions used in design the system.

- Modularity of design, large circuits can be realised by composing together smaller modules which have been tested and verified to ensure adherence to well-defined interface protocols.

- Lower electromagnetic interference and emission.

## 2.2 Classes of asynchronous circuits

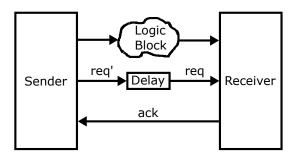

Figure 2.1 illustrates the synchronisation methods for synchronous and asynchronous circuits. While the assumption that data will be ready at every clock edge is made in synchronous systems and therefore every unit is expected to compute at the rising edge or falling edge or both edges of the clock, asynchronous systems operate by local synchronisation of events between two computing units that are ready to transfer and accept data. In Figure 2.1b, the request channel is labelled  $req^*$  because the request must arrive at the receiver when the data from the combinational circuit is valid.

Asynchronous circuits are classified based on the delay assumptions used to realise their circuits. The delay assumptions to a large extent determine the circuit's tolerance to process, voltage and temperature variations. Asynchronous circuits can be classified as Delay Insensitive (DI), Quasi-delay Insensitive (QDI) and Speed Independent (SI) circuits [32–34].

Delay Insensitive (DI) circuits take into account delays associated with wires and gates and assume that they are finite. Therefore the circuit can work correctly with unbounded gate and wire delays. Asynchronous circuits realised as DI are very robust, i.e. they can tolerate variations to a large degree; however, they are limited to simple gates as it is difficult to realise as complex circuits that are DI.

Fig. 2.1 Modes of communication: Synchronous and Asynchronous

Quasi-delay insensitive (QDI) circuits are a modification of DI circuits to allow for complex composition of circuits. Delay matching is achieved by way of isochronic forks. This means that the delay between ends of the fork is assumed to be negligible.

Speed independent (SI) circuits take into account delay associated with gates; however, they assume wire delays are negligible. These circuits require a completion signal to indicate when all computation is complete.

# 2.3 Signalling and data path communication conventions

Special protocols are used to indicate the validity and consumption of data in asynchronous systems. The communication protocol can either be two-phase also called transition signalling protocol or four-phase also called level signalling protocol [32]. For simple applications, each channel can be encoded as single-rail encoding or dual-rail irrespective of the communication protocol used. Each communication protocol is discussed under these two encodings.

## 2.3.1 Single-rail encoding

This encoding uses two separate wires, one for request and the other for acknowledgement, bundled along with the data to communicate between computing units. In Figure 2.2, a

Fig. 2.2 Bundled data

matching delay on the request line between the sender and the receiver is chosen to ensure the validity of the data at the receiving end.

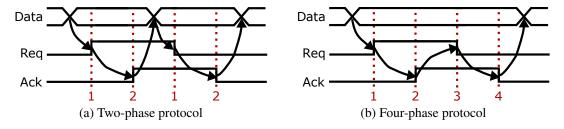

Two protocols of communication are possible on the request and acknowledge channels; these are shown in Figure 2.3. Figure 2.3a illustrates a *two-phase* communication protocol, while Figure 2.3b illustrates a *four-phase* communication protocol.

In Figure 2.3a, a rising or falling transition on the Request(Req) line is a request signal indicating the validity of the data, while a rising or falling transition on the Acknowledgement(Ack) line is an acknowledgement of the previous request input. In Figure 2.3b, a valid data is signalled by a low to high transition on Req which is a request input that must be acknowledged by Ack (low to high transition) after which both Req and Ack must be returned low in the same sequence before another request can be issued.

Bundled data protocol is not very robust because the matching delay may not scale in proportion with the combinational block in the presence of variations [32]. Therefore, the delay line is usually overestimated to improve robustness.

Fig. 2.3 Bundled Data Communication Protocols

### 2.3.1.1 Dual-rail encoding

This encoding uses three wires, two to encode request and data and a one wire for acknowledgement to communicate between computing units.

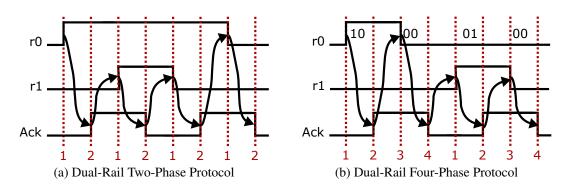

Two protocols of communication are possible on the request and acknowledge channels; these are shown in Figure 2.4a which illustrates a *two-phase* dual-rail communication protocol and Figure 2.4b illustrates a *four-phase* dual-rail communication protocol.

#### 2.3.1.2 Transition signalling protocol

Figure 2.4a shows the dual-rail transition signalling protocol. A transition on either of the request/data wires r0 and r1 is valid and must be acknowledged by a transition on the acknowledge wire Ack. Hence four request states are allowed on the wire pair "r0 r1": "00", "10", "01" and "11".

Fig. 2.4 Dual-Rail Protocol

#### 2.3.1.3 Level signalling protocol

Figure 2.4b shows the dual-rail level signalling protocol. Unlike 2-phase protocol, the data and the request signal can be determined through a low to high transition on only one of the two wire pair r0 and r1. Once an acknowledge signal (low to high transition on Ack) is received, the high signal on the data wire must be returned low. Hence only three states are

valid on the wire pair "r0 r1": "00", "10" and "01" representing empty/spacer, zero and one respectively.

A designer will have to decide if it is best to use 2-phase or 4-phase signalling in a dual-rail protocol. In making a choice, the increased concurrency coupled with the extra power consumption and delay introduced in 4-phase protocols must be considered. However, 4-phase protocols have the advantage of mapping well into CMOS because they are level sensitive.

The 4-phase communication protocol is used in the self-timed counters used in main contributions of this thesis.

## 2.4 Formal Specification of Asynchronous Circuits

Asynchronous circuits can be specified in high level or low level forms. A high-level form of the specification includes but is not limited to: Petri Nets, Labelled Petri Nets, regular expression. Low-level specification includes the use of signal transition graphs. The high-level specification allows for easy modelling and verification of asynchronous designs, while actual circuits can be synthesised from the low-level specification. The design of asynchronous circuits can be approached from any level of specification, depending on the complexity of the system. For complex systems, it is best approached in a high to low-level order.

#### 2.4.1 Petri Nets

Petri nets are used to describe and analyse systems with concurrent actions [35]. Petri nets describe the potential behaviour of discrete systems using a directed graph showing possible state transitions which are labelled.

A Petri net (PN) is a tuple  $\langle P, T, F, m_o \rangle$  [15] [36] where

$P = \{p_1, ...., p_r\}$  is a finite set of places,  $T = \{t_1, ...., t_r\}$  is a finite set of transitions,  $F \in [P \times T \to \mathbb{Z}]$  is the incidence function,

$m_o \in [P \to \mathbb{N}]$  is the initial marking.

A Place P is denoted by a circle; it indicates a condition (preconditions or postconditions) of a Transition. Transitions T are denoted by bars; they represent events. The precondition of a transition is also known as its input place(s), while its postcondition is known as its output place(s).

A transition is enabled when its precondition(s) is/are *marked* (hold a token). An enabled transition will eventually fire, this action consumes token(s) from its input place(s) and adds token(s) to its output place(s). Each place can hold a maximum of one token for 1 - safe Petri nets.

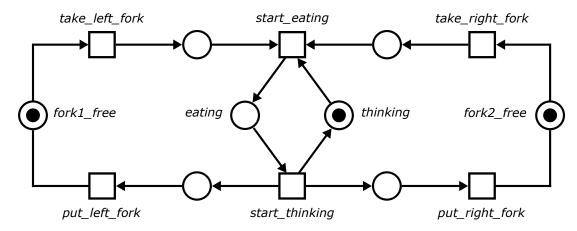

Fig. 2.5 Example: Single dining philosopher Petri net [1]

Figure 2.5 shows a simple PN which consists of eight places, with three places labelled as  $fork1\_free$ , thinking and  $fork2\_free$  each holding a token. In this condition, the transitions  $take\_left\_fork$  and  $take\_right\_fork$  are enabled and each when eventually fired, will consume the token from its input place and output a token in its output place. The firing of both transitions enables transition  $start\_eating$ .

A Preset  ${}^{\bullet}P$  of a place P is the set of all input transitions of the place P. A Postset  $P^{\bullet}$  of a place P is a set of all output transitions of the place P.

### 2.4.2 Petri Net Fragments

Fig. 2.6 Petri net Fragments

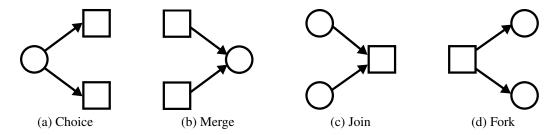

Figure 2.6 depicts PN fragments. A place with more than one postset transitions such that if any one of the transition fires, it consumes the only token thus disabling other transitions from occurring is called a choice (Figure 2.6a). This definition assumes a 1 - safe Petri net. A place with more than one preset transition is called a merge (Figure 2.6b). If more than one place has only one transition as a post set, it is called a Join (Figure 2.6c). If more than one place has only one transition as a preset, it is called a Fork (Figure 2.6d).

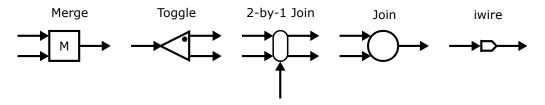

Fig. 2.7 Symbols of Asynchronous Circuits Fragments

Figure 2.7 shows some symbols used to represent standard asynchronous fragments [37]. Two additional fragments are shown, the toggle and iwire. The toggle operates thus, every low to high transition on its input results in a transition in either one of its outputs, with the choice of output alternating, beginning with the output marked by the dot immediately after reset state. The iwire operates thus: it outputs a transition immediately after reset state

after which it must receive an input transition before another output transition can occur. In a 2-by-1 Join, any one of the two inputs on the left enables its adjacent output if a valid transition occurs on the bottom input.

### 2.4.3 Labelled Petri Nets (LPN)

This is a high-level specification in which names are used to denote events when describing asynchronous systems.

A labelled Petri net is a tuple  $N = (PN, S\lambda)$  where PN is a Petri net and  $S\lambda : T \to \Sigma$  is the labelling of transitions.

### 2.4.4 Signal Transition Graphs (STG)

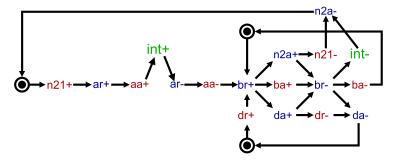

Signal transition graphs (STGs) are a subclass of interpreted Petri nets which detail the firing of transitions as either a rising or falling of a signal in an ordered sequence. For a transition signal denoted by a, a+ means that a transitioned from a logical low to a logical high and a- means vice versa.

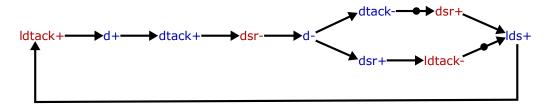

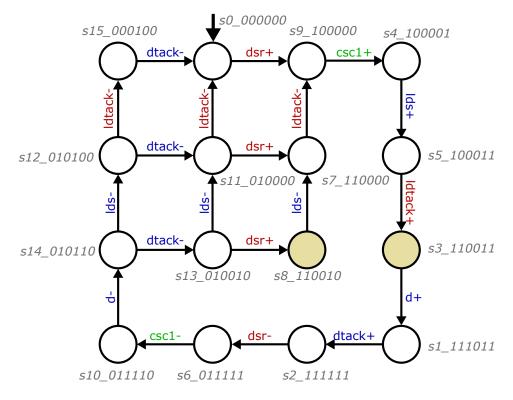

Fig. 2.8 Example: STG of VME Bus Controller [1]

A signal transition graph (STG) is a turple  $N = (PN, In, Out, \ell)$  [16] [38]. Where  $Sig \in (In \cup Out)$  Is a set of all signals (input and output),  $\ell: T \to Sig \times \{+, -\}$  is the labelling function,  $Sig \times \{+, -\}$  is the set of signal transitions.

STGs are drawn as Petri nets; however, unmarked pre and post-conditions of a transition can be eliminated, thus allowing an arc to be connected directly from one transition to another when convenient as shown in Figure 2.8.

# 2.5 Formal Verification of Asynchronous circuits

For an STG to be safe, it needs to satisfy four properties [1]. These are:

- Consistency: All signals in any possible trace must transitions from high/low to low/high and then from low/high to high/low before that trace can be repeated.

- **Deadlock-freeness:** No combination of transitions should result in a state where all signals are disabled.

- **Input properness:** An input signal cannot be triggered by internal signals or disabled by internal and output signals. This property ensures that the system responds correctly when a valid input transition occurs.

- Output persistence: Internal and output signals must not be disabled by any other signals.

For a circuit to be safe, it needs to satisfy three properties [1]. These are:

- Conformation: The circuit must operate as specified by the STG.

- **Deadlock:** In every reachable state, the circuit or the environment (or both) can fire some transition.

- **Hazard:** An excited gate in the circuit cannot be disabled from firing.

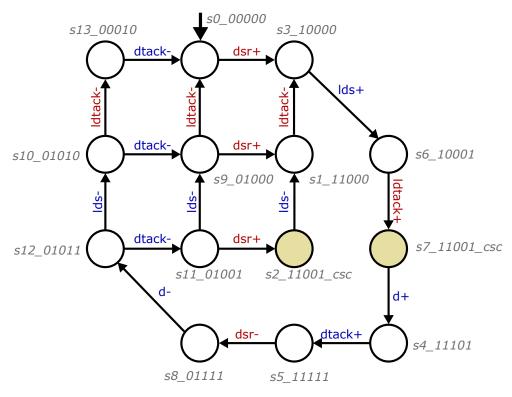

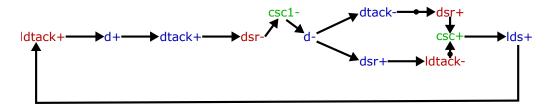

Fig. 2.9 CSC conflicts of STG of Figure 2.8 [1]

# 2.6 Complete State Coding

Implementability of an STG is determined by its consistency and complete state coding (CSC). Complete state coding guarantees that the state of the system due to each signal transition is unique. Where this is not possible, the STG is said to have CSC conflict(s). Figure 2.9 shows the state coding for the STG of Figure 2.8. The numbers next to the circles denote the state of the system after each transition. The coloured circles have the same coding numbers, and this indicates that those states conflict. This means that when in any of those states, any one of transitions Ids- and d+ can occur thus creating a possibility of violating the Conformation property.

One method of resolving this issue is by careful addition of internal signals to distinguish the state coding of the STG at each trace [16, 39].

Fig. 2.10 Internal signal used to resolve conflicts [1]

Figure 2.10 shows the modified STG with an internal signal *csc*1 added to eliminate the CSC conflicts. Therefore, a unique state is guaranteed for the system in each transition path. Figure 2.11 shows the new state space graph with an added state for the internal signal.

Fig. 2.11 Resolved CSC conflicts of STG of Fig 2.8 [1]

# 2.7 Synthesis of Asynchronous Circuits from STGs

Usually after behavioural verification and ensuring encoding error free STGs, the next step is to synthesize the logic equations of the described system from the STGs.

In this thesis, the circuits presented were synthesized using the WorkCraft Tool (developed in Newcastle University). WorkCraft uses various back-end tools like the PUnf, MPSat, and PComp for composition and verification of Petri nets and STGs and for synthesis of electronic circuits from STGs. Other back-end tools include Petrify, PGMiner, ScEnco and GraphViz [1].

Other major tools for synthesizing STGs include Teak (developed in Manchester University), which is a tool for creating asynchronous implementations of circuit descriptions written in the Balsa language. Teak transforms concurrent specification of the Balsa language into data driven network [40–42]. Tangram is a tool by Philips, now known as Philips gambit [43–45]. This tool allowed Very Large Scale Integration (VLSI) design to be realised in form of a computer program [46] - Communicating Sequential Protocol (CSP) [47].

### 2.8 Approaches to Exploiting Asynchronous Properties

Large asynchronous systems can be broken down into a combination of sub-blocks. This approach has the following advantages.

- Reduced design time, efficient testing and verification of each function block. Here, the designer must be aware of the expected input variables, the input combination range and the expected output of each sub-block.

- The behaviour of self-timed systems can be described using mathematical expressions.

This allows the system to be decomposed into mathematically correct subsystems which can then be tested, verified and specified using formal asynchronous design methods.

- Modularity of design which allows reuse of sub-blocks in system expansion. This

advantage is as a result of the mode of communication in asynchronous circuits using

handshake protocols. Thus, the addition or reuse of a verified sub-block in, for instance,

expansion of a design or as part of a different design is not limited by timing issues and technology compatibility [48, 12].

In this section, three methods by which asynchronous circuits properties have been exploited in designing self-timed systems are presented under the following headings: Low Power Circuits, Data-driven Circuits and Circuits Tolerant to timing variations.

### 2.8.1 Low Power

In [49], power gating techniques were employed to power-down or power-up data-driven sub-blocks depending on the computational needs of the whole system. The power gating controls are determined by the input data encoding. A spacer input (no data) to a sub-block results in no computation, therefore to conserve power a spacer is interpreted as a power down command. This approach exploits the robust intrinsic advantages of QDI circuits (channel encoding).

The need for an asynchronous sleep control circuits for power consumption minimisation was proposed in [50]. In [51], two asynchronous sleep controllers for low power Internet of Things (IoT) are discussed. The controllers are event-driven by incoming data or available energy [52, 53] which are used to wake or put to sleep computing sections in a system.

### 2.8.2 Robustness to Timing Variations

In [12], the elastic property of asynchronous circuits is exploited in the design of the self-timed micro-pipeline. The pipeline was first built as a modular unit, which is then cascaded to the desired depth. Communication between neighbouring modular units is governed by transition signalling ensuring that data is transferred between computing units that are ready to send and receive data. In this circuit structure, an arbitrary delay in any modular unit does not affect the result of the computation. Therefore in the presence of PVT variation, the circuit internal gates delay will change, but the system will still operate correctly.

### 2.8.3 Elasticity in Data-Driven Circuits

In [54, 13, 55], event-driven Analogue-to-Digital Converters were presented in which incoming data modulates the operation of the system. Such systems exploited the robust property of asynchronous circuits to tune the granularity of operation from the shape/frequency of the incoming data. The mode of operation of these circuits also gave them a low power consumption profile.

# 2.9 Design process used in the thesis

In this section, the tools and design process used in this thesis is outlined.

- 1. Top level specification of the system. This includes formal specification using mathematical expression.

- 2. From general expression, the system is decomposed into parts that performs specific operation(s).

- 3. The next step after decomposition is specification of each part operation using Labelled Petri nets (LPN) showing signal names as output and input ports.

- 4. The LPNs are converted to signal transition graphs (STGs) by refining the signal names into an ordered and interacting sequence of rising and falling transition.

- 5. The STGs are synthesised using WorkCraft Tool.

- (a) In this stage, the names of the logic gates used in the synthesis were mapped to the logic gates of the standard library to be used in Cadence to minimise gate size and needed connections in the layout implementation.

- 6. The synthesized logic equation of each part was then imported into Cadence Virtuoso EDA from which their schematics can further be edited.

2.10 Conclusion 25

- (a) Each part behaviour is verified by simulation.

- (b) The complete system is composed from the verified parts.

- (c) The complete system is verified by simulation.

- 7. After importation to Cadence, the Encounter SoC tool is used to edit the layout of each part and then the complete system.

- 8. After layout placement, Post Layout simulation is done in Cadence Virtuoso. This step involves design rule checks, layout versus schematic checks and layout extraction before the actual post-layout simulation.

- The counter presented in chapter 5 was fabricated in 350 nm CMOS technology. After post-layout simulation, the gdsi II files were generated and sent to the foundry for fabrication.

- 10. Test PCB was designed for the fabricated chip using Altium Designer.

- 11. Test sequence and patterns for the chip were implemented in an Altera FPGA. The Quartus prime EDA was used for vhdl editing and FPGA configuration.

- 12. The system was tested and measurement results recorded. This involved the used of Oscillator, low voltage power supply, wave form generators, digital ammeters, pen and paper.

### 2.10 Conclusion

Basic definitions of fundamental asynchronous circuit terms and parts have been presented in this chapter. This includes classification of asynchronous systems, the methods of event signalling in asynchronous circuits, specification, modelling and synthesis of asynchronous circuits. Asynchronous circuits were shown to offer advantages like low power consumption

and robust operating characteristics. The design of asynchronous circuits is richly supported by proven mathematical methods which aid modelling, verification and synthesis. The advantages of asynchronous circuits can be exploited in the design of low power and data adaptable circuits.

# Chapter 3

# **Counter Decompositions**

### 3.1 Introduction

Digital counters are widely employed in digital and mixed-signal systems like the Phase locked loop (PLL), timers and in systems that require pulse frequency and pulse width control. In these applications, the counter is designed to function as a programmable modulo—n counter.

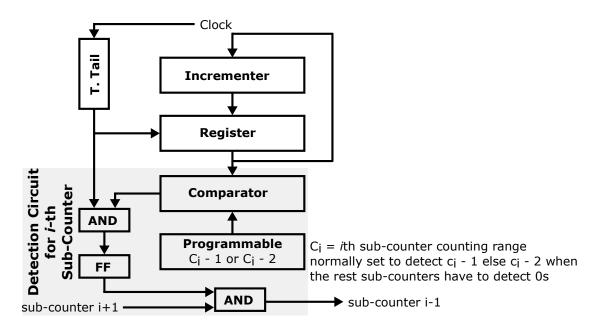

Generally, digital counters operate in ascending or descending binary order. When applied as modulo-n counting systems they are reset at a predefined value. This describes a counting system that may use an end of count detection circuit to monitor the counter state. Such counters require high-speed count modulo detection circuits. The end of count detection must occur before the next clock transition in synchronous systems. This has led designers to address issues of accuracy, safety of operation and response time of the counter by proposing various decomposition methods.

Some systems require only the end of count output, and therefore, the states through which the counter transit may not be important. This also led to various decompositions of non-binary synchronous and self-timed modulo counters. However, issues of safety of operation and response time of the counter are still major issues to be addressed.

In later chapters in this thesis, two self-timed counters are utilised in the two systems investigated. The counter used in chapter 4 is a self-timed binary counter whose count output is valid only when the acknowledgement signal is produced. This behaviour of the counter was used to model a computing unit with varying task completion time in the investigation presented in chapter 4.

The theory behind the digital pulse-width modulator (DPWM) investigated in chapter 6 is that robustness in asynchronous system can be exploited in the design of a fine-tunable DPWM. Therefore in chapter 5 a loadable self-timed modulo—n counter is realised using formal decomposition, specification and verification methods. In the application of the counter to the DPWM, the counter transition states are not as important as the end of count production. Here I am more interested in the response time and correct/reliable operation of the counter. The self-timed modulo—n counter realised in chapter 5 reconfigures its operation to produce an end of count signal after a time determined by n. Therefore, this chapter on review of counters is a precursor to chapter 5.

Previous approaches to modulo-n counter decompositions were determined by the following three factors; signalling method, sequence of bit transition and end of count detection method.

### 1. Signalling protocol

Signalling protocol defines the mode of communication of events between sub-unit that make up the counter. This can be synchronous or asynchronous.

In synchronous modulo—n counters, fast end of count detection time, reduced propagation delay and counter complexity are the main issues addressed in approaches to counter decompositions [56–68]. The aim is to express the counter operation such that propagation delays are eliminated or minimised and the end of count detection reduced to the operation of a fixed circuit or number of gate delays. However quantisation from the coarse nature of the clock can affect the proposed DPWM operation.

3.1 Introduction 29

In asynchronous modulo—n counters (usually called self-timed counters)[69, 37, 70–77], low power consumption (expressed as bounded), response time on the count outputs and robust operating characteristics are factors that determine the decomposition approach. Asynchronous modulo—n counters have potential application in low power devices such as sleep timers in standby circuitry as proposed in [50]. The first task in asynchronous modulo—n counter decompositions is to express the counter in such a way that counting is generated by internal configuration and signalling of events. The next task is to realise the counter as consisting of basic asynchronous components or a distributed system containing modules assigned a specific counting task which operate in parallel while communicating results with each other. The absence of clock

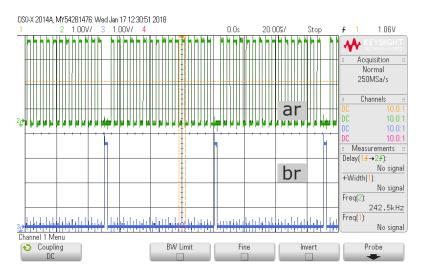

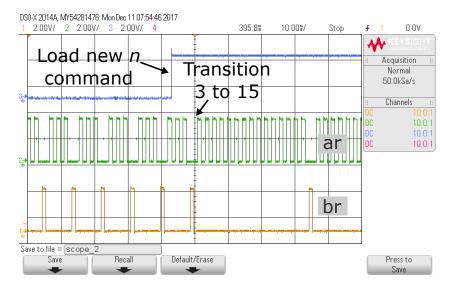

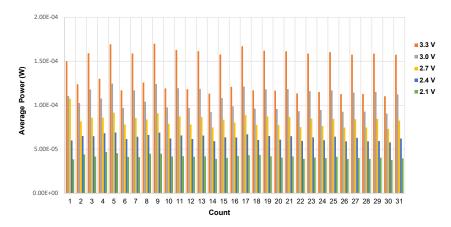

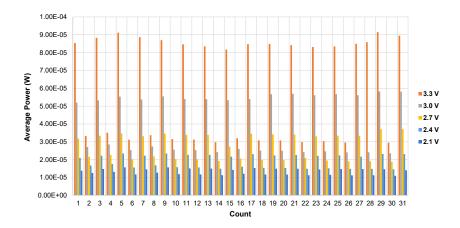

#### 2. Sequence of bit transition