# INVESTIGATION INTO ENERGY-EFFICIENT AND APPROXIMATE MULTIPLIER DESIGN

Issa Hani Qiqieh

A Thesis Submitted for the Degree of

Doctor of Philosophy at Newcastle University

School of Engineering

September 2018

Issa Hani Qiqieh: Investigation into Energy-Efficient and Approximate Multiplier Design ©2018

### **DECLARATION**

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

Newcastle upon Tyne, September 2018

Issa Hani Qiqieh

CERTIFICATE OF APPROVAL

We confirm that, to the best of our knowledge, this thesis is from the

student's own work and effort, and all other sources of information

used have been acknowledged. This thesis has been submitted

with my approval.

Prof. Alex Yakovlev

Dr. Rishad Shafik

Dr. Danil Sokolov

## To the soul of my father who had given me dreams to look forward to To my wonderful mother To my lovely Yara, Hani, Morad and Bassel

— Issa

I would like to express my deep gratitude to my supervisors Prof. Alex Yakovley, Dr. Rishad Shafik and Dr. Danil Sokolov for their wisdom and guidance through my PhD journey. They have always been a source of motivation and my inspirational model as a researcher.

I am grateful to the Ministry of Higher Education and Scientific Research in Jordan and Al-Balqa' Applied University for funding my PhD study and for their support.

I would like also to express my gratefulness and appreciation to my colleagues and friends in the School of Engineering, especially those in MicroSystems Research Group. We have worked together and discussed many topics over the years, and from them all, I have learned many things. I hope they continue to be successful with their research and future careers. Also, I would like to offer my special regards to all the staff of the School of Engineering at Newcastle University.

Thank you, my mother, my mother-in-law and my sisters, without your unconditional support, this thesis never would have come to be. Finally, and most importantly, I am thankful to my lovely family, Yara my wonderful wife and my lovely sons Hani, Morad and Bassel for all of their love, support, motivation and patience throughout my PhD. They were there to help me at difficult times, and to share in good times. Their encouragement has helped me with the research and the writing of this thesis, and I am very grateful.

There is a persistent demand for higher computational performance at low energy cost for emerging compute-intensive applications. Multipliers constitute a major component of these applications with complex logic design and a large gate count compared to other arithmetic units. As such, there is significant interest in designing new approaches to low-complexity multipliers. Approximate multiplier is a promising paradigm, which is particularly suitable for inherently imprecision-tolerant applications, such as image processing, pattern recognition and machine learning. The basic premise is to relax the precision requirements in favour of lower complexity, thereby achieving reduced circuit delay and energy consumption.

This thesis presents an investigation into novel approximate multiplier design and implementation approaches. In the first approach, a multiplier design using significance-driven logic compression (SDLC) is proposed. Fundamental to this approach is a configurable lossy compression of the partial product rows. The compression is carried out by progressively replacing the exclusive-OR logic gates by low-complexity OR gates based on their bit significance. The compression is followed by commutative remapping of the resulting product terms to reduce the number of product rows. This accounts for substantially reduced number of logic cell counts and lengths of critical paths at the cost of errors in lower significant bits.

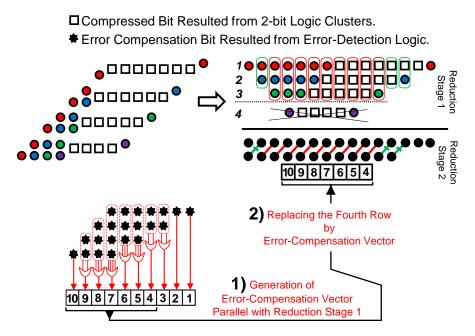

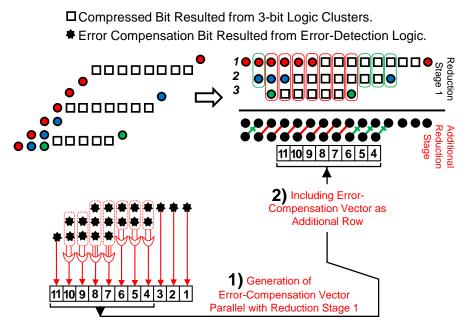

In the second approach, a novel multiplier design is presented by combining a Wallace-tree accumulation method together with the SDLC. The logic compression performed by SDLC approach works for reducing the number of product rows using progressive bit significance, thereby decreasing the number of reduction stages and logic counts in accumulation. The errors introduced by lossy logic compression are minimised through a novel error compensation method (ECM). The core of this method is a parallel error detec-

tion logic used to generate error compensation bit-matrix. This matrix is then compressed using OR gates to generate an error compensation vector. To mitigate the impact of error, this vector is either considered as an additional row in the accumulation tree or used to modify an existing row.

To validate the effectiveness of these approaches, a number of multipliers with different compression levels are designed and synthesized showing substantial savings in energy consumption, and reductions in critical delay and silicon area, compared to an accurate equivalent and other existing approaches. These gains are achieved at the cost of errors introduced in the circuit, which are extensively analysed.

The configurable multiplier designs in the first and second approaches exhibit energy/quality trade-offs at different degrees of compression. These trade-offs can be effectively used to implement multipliers in applications, where energy can be opportunistically minimised within the envelope of quality requirements. As such, in the third study, two implementation methods are demonstrated. In the first method, a Gaussian blur filter was designed, demonstrating energy reduction with a minor loss in image quality. In the second method, the energy/quality trade-offs are leveraged in a perceptron-based machine learning application, showing energy reduction for different SDLC configurations.

The proposed logic compression approach and its prototype implementations in various configurations can be suitably used for energy-efficient multiplier designs, where quality requirements can be relaxed.

### PUBLICATIONS AND CONTRIBUTIONS

The publications that were produced as a part of research reported in this thesis are listed as follows:

### Journal publications:

• Issa Qiqieh; Rishad Shafik; Ghaith Tarawneh; Danil Sokolov; Shidhartha Das; Alex Yakovlev, Significance-Driven Logic Compression for Energy-Efficient Multiplier Design, IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JET-CAS), September 2018, vol. 8, no. 3, pp. 417-430.

### Conference publications:

- Issa Qiqieh; Rishad Shafik; Danil Sokolov; Alex Yakovlev, Energy-Efficient Approximate Multiplier Design using Bit Significance-Driven Logic Compression, Design, Automation Test in Europe Conference Exhibition (DATE), March 2017, pp 7-12.

- Issa Qiqieh; Rishad Shafik; Ghaith Tarawneh; Danil Sokolov; Shidhartha Das; Alex Yakovlev, Energy-Efficient Approximate Wallace-Tree Multiplier using Significance-Driven Logic Compression, IEEE International Workshop on Signal Processing Systems (SiPS), October 2017, pp 1-6.

- Dave Burke; Dainius Jenkus; Issa Qiqieh; Rishad Shafik; Shidhartha Das; Alex Yakovlev, Special Session Paper: Significance-Driven Adaptive Approximate Computing for Energy-Efficient Image Processing Applications, CODES+ISSS, October 2017, pp 1-2.

### CONTENTS

| I | Tŀ                                     | esis C  | Chapters                                  | 1  |

|---|----------------------------------------|---------|-------------------------------------------|----|

| 1 | INT                                    | RODUC   | TION                                      | 2  |

|   | 1.1                                    | Motiva  | ation                                     | 2  |

|   |                                        | 1.1.1   | Energy-Efficient Computing                | 3  |

|   |                                        | 1.1.2   | Approximate Multiplier Design             | 4  |

|   | 1.2                                    | Thesis  | Scope and Contributions                   | 6  |

|   | 1.3                                    | Thesis  | Overview                                  | 8  |

| 2 | BAC                                    | KGROU   | UND AND LITERATURE SURVEY                 | 11 |

|   | 2.1                                    | Introd  | uction                                    | 11 |

|   | 2.2                                    | Appro   | ximate Circuit Design                     | 12 |

|   |                                        | 2.2.1   | Imprecise Hardware Design                 | 12 |

|   |                                        | 2.2.2   | Taxonomy of Approximate Circuits          | 20 |

|   | 2.3                                    | Appro   | ximate Multiplier Design                  | 23 |

|   |                                        | 2.3.1   | Taxonomy and Survey                       | 24 |

|   |                                        | 2.3.2   | Error Evaluation and Challenges           | 33 |

|   | 2.4                                    | Conclu  | nding Remarks and Discussions             | 37 |

| 3 | LOGIC COMPRESSION IN MULTIPLIER DESIGN |         |                                           | 39 |

|   | 3.1                                    | Introd  | uction                                    | 39 |

|   | 3.2                                    | Signifi | cance-Driven Logic Compression Approach . | 40 |

|   |                                        | 3.2.1   | Logic Clustering                          | 41 |

|   |                                        | 3.2.2   | Logic Compression                         | 43 |

|   |                                        | 3.2.3   | Progressive Cluster Sizing                | 44 |

|   |                                        | 3.2.4   | Commutative Remapping                     | 45 |

|   |     | 3.2.5 Example of Utilizing 2-bit SDLC 44                       |  |  |  |  |

|---|-----|----------------------------------------------------------------|--|--|--|--|

|   | 3.3 | Variable Logic Cluster and Scalability 4                       |  |  |  |  |

|   |     | 3.3.1 General Space of $d$ -bit Logic Cluster 40               |  |  |  |  |

|   |     | 3.3.2 <i>d</i> -bit Logic Cluster: Compression Algorithm 50    |  |  |  |  |

|   |     | 3.3.3 Scalability for $(N \times N)$ SDLC Multiplier Design 53 |  |  |  |  |

|   |     | 3.3.4 Examples of Utilizing $d$ -bit SDLC 58                   |  |  |  |  |

|   | 3.4 | Error Analysis                                                 |  |  |  |  |

|   | 3.5 | Design Trade-offs 6                                            |  |  |  |  |

|   | 3.6 | Comparative Analysis                                           |  |  |  |  |

|   | 3.7 | Signed Multiplication using SDLC                               |  |  |  |  |

|   | 3.8 | Concluding Remarks                                             |  |  |  |  |

| 4 | ERR | OR MITIGATION IN LOGIC COMPRESSION 8                           |  |  |  |  |

|   | 4.1 | Introduction                                                   |  |  |  |  |

|   | 4.2 | Proposed Approximate Wallace Multiplier 85                     |  |  |  |  |

|   |     | 4.2.1 Logic Compression using SDLC 85                          |  |  |  |  |

|   |     | 4.2.2 Accumulation with Wallace Method 8                       |  |  |  |  |

|   |     | 4.2.3 Wallace with Variable Logic Compression . 84             |  |  |  |  |

|   | 4.3 | Error Compensation Method (ECM) 9                              |  |  |  |  |

|   |     | 4.3.1 Parallel Error Detection Logic 99                        |  |  |  |  |

|   |     | 4.3.2 Error Compensation Vector 94                             |  |  |  |  |

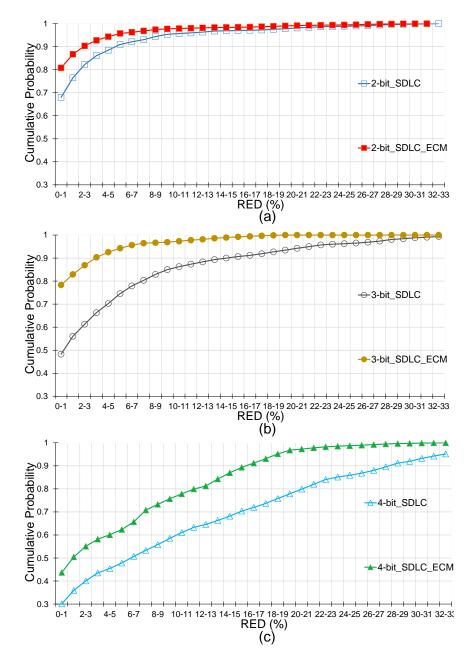

|   | 4.4 | Error Analysis                                                 |  |  |  |  |

|   | 4.5 | Experimental Results and Design Trade-offs 99                  |  |  |  |  |

|   | 4.6 | Concluding Remarks                                             |  |  |  |  |

| 5 | IMP | MPLEMENTATION AND VALIDATIONS 10                               |  |  |  |  |

|   | 5.1 | Introduction                                                   |  |  |  |  |

|   | 5.2 | Case Study 1: Gaussian Blur Filter                             |  |  |  |  |

|   | 5.3 | Case Study 2: Perceptron Classifier                            |  |  |  |  |

|   | 5.4 | Concluding Remarks                                             |  |  |  |  |

| 6 | CON | ICLUSIONS AND FUTURE WORK 11'                                  |  |  |  |  |

|              |    | Summary and Conclusions |     |

|--------------|----|-------------------------|-----|

| 11           | Th | esis Bibliography       | 123 |

| BIBLIOGRAPHY |    | 124                     |     |

CONTENTS xii

### LIST OF FIGURES

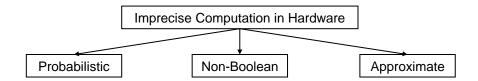

| Figure 2.1 | Taxonomy of imprecise computation in hard-             |    |

|------------|--------------------------------------------------------|----|

|            | ware                                                   | 13 |

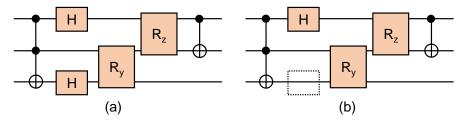

| Figure 2.2 | Example of a small quantum circuit 3qubitc-            |    |

|            | not: (a) fault-free circuit, and (b) faulty cir-       |    |

|            | cuit by eliminating a single H gate [6]                | 14 |

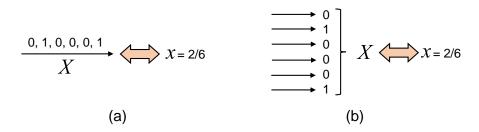

| Figure 2.3 | Stochastic encoding: (a) a stochastic bit              |    |

|            | stream; (b) a stochastic wire bundle. For each         |    |

|            | bit in the bit stream or a bundle, the proba-          |    |

|            | bility that it is 1 is $P(X = 1) = x$                  | 15 |

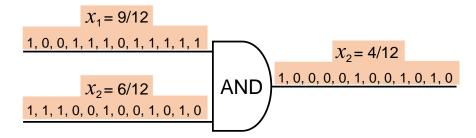

| Figure 2.4 | Stochastic multiplication using an AND gate.           | 15 |

| Figure 2.5 | Example of a $(2 \times 2)$ multiplier: (a) approx-    |    |

|            | imate, and (b) accurate, with the critical             |    |

|            | paths highlighted [65]                                 | 17 |

| Figure 2.6 | Taxonomy of approximate circuits                       | 20 |

| Figure 2.7 | Multi-dimensional taxonomy of approximate              |    |

|            | multiplier designs.                                    | 24 |

| Figure 2.8 | An example of $(2 \times 2)$ multiplier: (a) operating |    |

|            | within safe voltage range; (b) lowering the            |    |

|            | supply voltage below its nominal value                 | 25 |

| Figure 2.9 | Increasing the level of truncation from; (a)           |    |

|            | 3; (b) 4; (c) 5; and (d) 6 columns, translates         |    |

|            | into additional reductions in area and power;          |    |

|            | however, error is maximized and this method            |    |

|            | is not effective to reduce the critical column         |    |

|            | of the accumulation tree (highlighted in dot-          |    |

|            | ted rectangles)                                        | 26 |

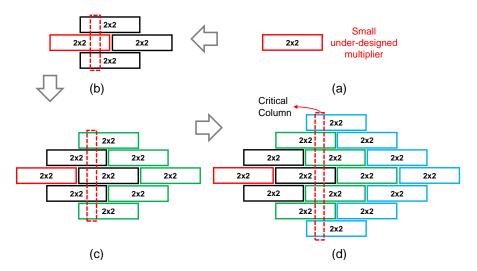

| Figure 2.10 | Using (2 $\times$ 2) approximate multiplier blocks      |    |

|-------------|---------------------------------------------------------|----|

|             | to build larger energy-efficient multipliers [65].      | 27 |

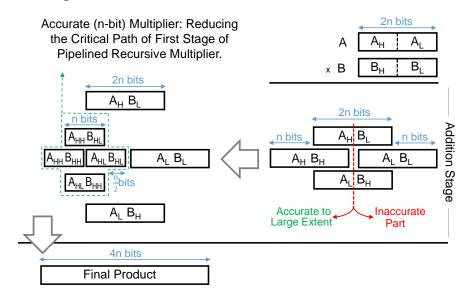

| Figure 2.11 | Different sizes of approximate and accu-                |    |

|             | rate multipliers are used to build large re-            |    |

|             | cursive multiplier for pipelined architec-              |    |

|             | ture [8]; the carry-in logic is used for the ap-        |    |

|             | proximate partial product computation only              |    |

|             | $(A_HB_L,A_LB_H,A_LB_L)$ and not for the accu-          |    |

|             | rate $A_H B_H$                                          | 28 |

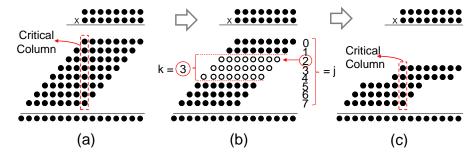

| Figure 2.12 | The partial product accumulation tree: (a) of           |    |

|             | an accurate $(8 \times 8)$ multiplier; (b) design pa-   |    |

|             | rameters are set using multiple EDA tools,              |    |

|             | and (c) the reduced partial product matrix af-          |    |

|             | ter applying the partial product perforation            |    |

|             | with $j = 2$ and $k = 3$ [134]                          | 29 |

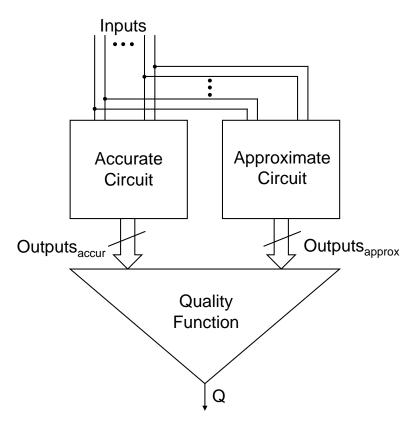

| Figure 2.13 | The quality constraint circuit proposed by              |    |

|             | SALSA [125] (Q is a single Boolean value)               | 31 |

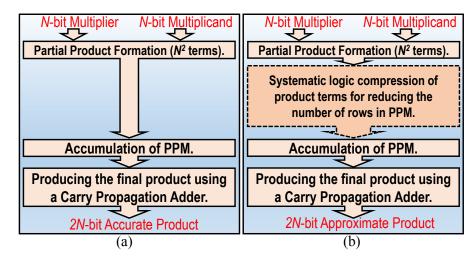

| Figure 3.1  | Process chart showing the difference be-                |    |

|             | tween the major stages in: (a) conventional             |    |

|             | multiplication, and (b) the proposed ap-                |    |

|             | proach to multiplication                                | 41 |

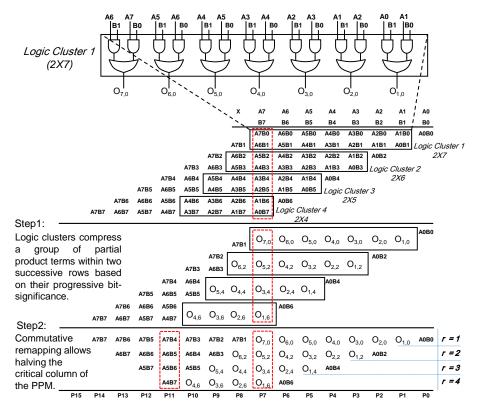

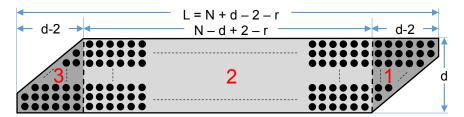

| Figure 3.2  | Stylized demonstration of SDLC approach                 |    |

|             | [93]: four different sizes of logic clusters used       |    |

|             | to compress partial products based on their             |    |

|             | progressive bit-significance in (8 $\times$ 8) parallel |    |

|             | multiplier architecture.                                | 42 |

| Figure 3.3  | Eight different sizes of 2-bit logic clusters           |    |

|             | used to compress partial products based on              |    |

|             | their progressive bit-significance in (16 $\times$ 16)  |    |

|             | parallel multiplier architecture                        | 46 |

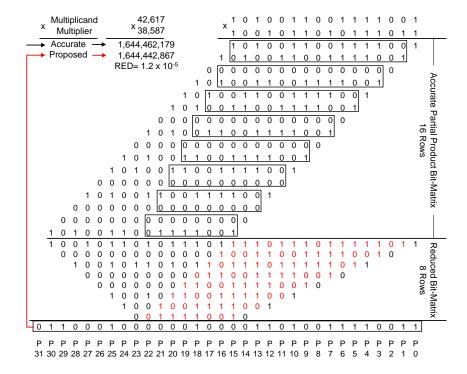

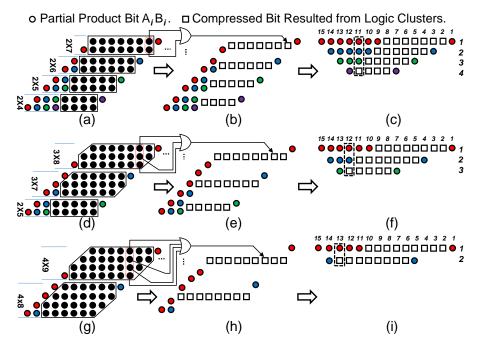

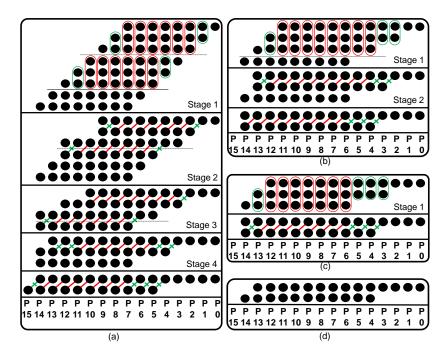

| Figure 3.4 | Dot diagram showing the impact of increas-                |    |

|------------|-----------------------------------------------------------|----|

|            | ing the depth of the logic clusters in the case           |    |

|            | of $(8 \times 8)$ multiplier: (a) clustering a group of   |    |

|            | bits within 2 successive rows in the partial              |    |

|            | product bit-matrix after bitwise multiplica-              |    |

|            | tion; (b) generating a reduced set of prod-               |    |

|            | uct terms after targeting the depth of 2-row              |    |

|            | logic compression; (c) ordered matrix after               |    |

|            | applying commutative remapping of the bit                 |    |

|            | sequence resulting from the SDLC approach;                |    |

|            | (d), (e) and (f) the same process when apply-             |    |

|            | ing 3-bit logic compression; (g), (h) and (i) the         |    |

|            | same process when applying 4-bit logic com-               |    |

|            | pression. The dotted rectangles at the right              |    |

|            | indicate the heights of the critical columns              |    |

|            | which are further reduced compared to the                 |    |

|            | accurate accumulation tree                                | 48 |

| Figure 3.5 | Dot diagram showing the general space of                  |    |

|            | targeted partial product terms compressed                 |    |

|            | by a $(d \times L)$ logic cluster to produce array of $L$ |    |

|            | bits in $r^{th}$ row of the reduced partial product       |    |

|            | matrix for $(N \times N)$ multiplier using SDLC           |    |

|            | approach with $d$ -bit logic compression                  | 49 |

| Figure 3.6 | Five different sizes of 3-bit logic clusters used         |    |

|            | to compress partial products based on their               |    |

|            | progressive bit-significance in (16 $\times$ 16) par-     |    |

|            | allel multiplier architecture                             | 55 |

| Figure 3.7  | Four different sizes of 4-bit logic clusters           |    |

|-------------|--------------------------------------------------------|----|

|             | used to compress partial products based on             |    |

|             | their progressive bit-significance in (16 $\times$ 16) |    |

|             | parallel multiplier architecture                       | 56 |

| Figure 3.8  | Three different sizes of 5-bit logic clusters          |    |

|             | used to compress partial products based on             |    |

|             | their progressive bit-significance in (16 $\times$ 16) |    |

|             | parallel multiplier architecture                       | 57 |

| Figure 3.9  | Two different sizes of 6-bit combined with             |    |

|             | 4-bit logic clusters used to compress par-             |    |

|             | tial products based on their progressive bit-          |    |

|             | significance in (16 $\times$ 16) parallel multiplier   |    |

|             | architecture                                           | 57 |

| Figure 3.10 | Two different sizes of 7-bit combined with             |    |

|             | 2-bit logic clusters used to compress par-             |    |

|             | tial products based on their progressive bit-          |    |

|             | significance in (16 $\times$ 16) parallel multiplier   |    |

|             | architecture                                           | 58 |

| Figure 3.11 | Two different sizes of 8-bit logic clusters used       |    |

|             | to compress partial products based on their            |    |

|             | progressive bit-significance in (16 $\times$ 16) par-  |    |

|             | allel multiplier architecture                          | 58 |

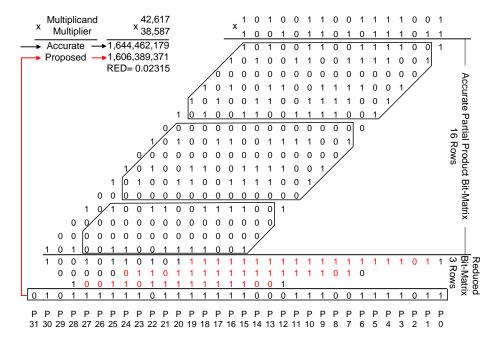

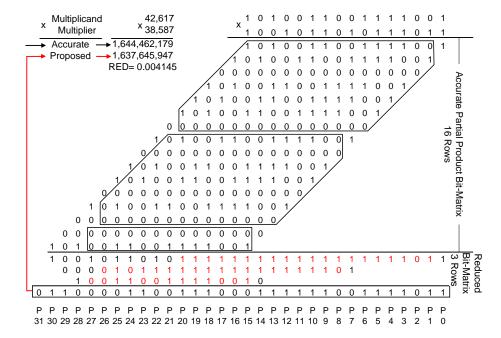

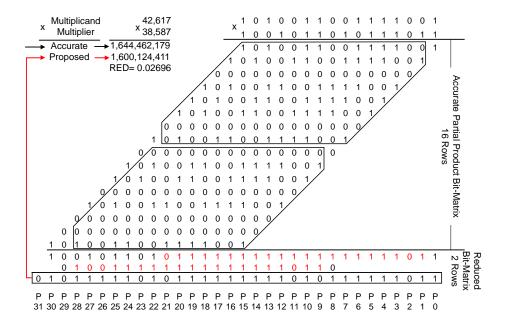

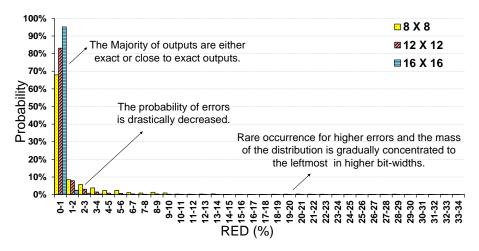

| Figure 3.12 | Error percentage distribution for 8-, 12- and          |    |

|             | 16-bit proposed multiplier after applying 2-           |    |

|             | bit depth compression                                  | 62 |

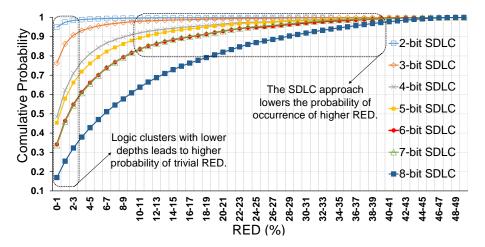

| Figure 3.13 | Cumulative probability distribution for the            |    |

|             | error induced by different logic compression           |    |

|             | levels of the proposed SDLC approach in the            |    |

|             | case of (16 $\times$ 16) multiplier                    | 66 |

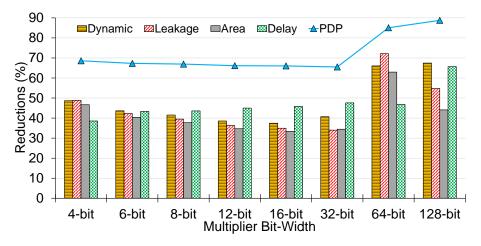

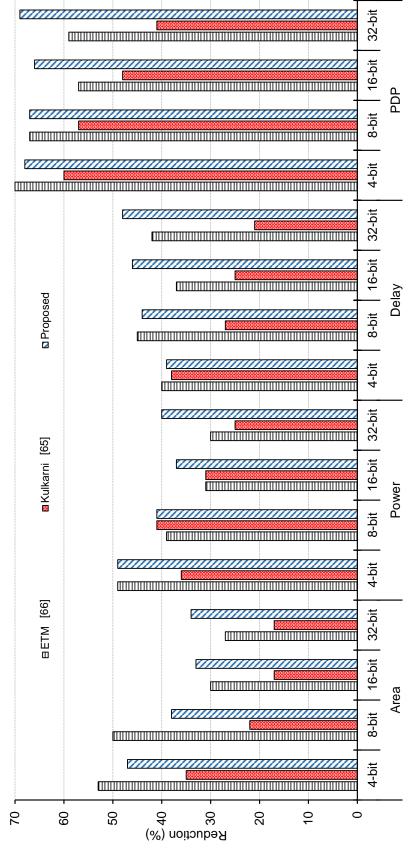

| Figure 3.14 | Dynamic/leakage power, area, delay and                          |            |

|-------------|-----------------------------------------------------------------|------------|

|             | power-delay-product (PDP) trade-offs for dif-                   |            |

|             | ferent bit-widths of the (2-bit SDLC) pro-                      |            |

|             | posed multiplier.                                               | 68         |

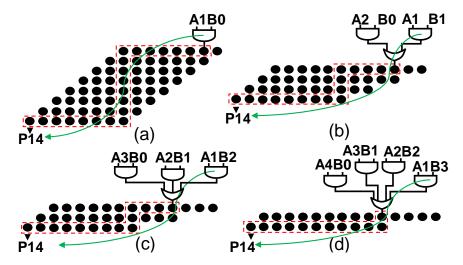

| Figure 3.15 | Dot diagram highlights the impact of in-                        |            |

|             | creasing depth of logic clusters on the critical                |            |

|             | path of $(8 \times 8)$ multiplier: (a) partial prod-            |            |

|             | uct bit-matrix of the conventional multiplier;                  |            |

|             | (b) after 2-bit SDLC; (c) 3-bit SDLC; and (d)                   |            |

|             | 4-bit SDLC. The dotted polygons indicate                        |            |

|             | the maximum propagation path for summing                        |            |

|             | up the accumulation tree. Higher degrees of                     |            |

|             | compression minimize the propagation de-                        |            |

|             | lay associated with accumulation tree (such                     |            |

|             | as (b) and (c)), while a further reduction in                   |            |

|             | (d), since a carry propagation adder is just                    |            |

|             | needed to generate the product (no extra                        |            |

|             | delay required for accumulation tree). The                      |            |

|             | curved lines identify the critical paths for                    |            |

|             | each multiplier (from A1 to P14)                                | 71         |

| Figure 3.16 | Dynamic power, leakage power, delay, area                       |            |

|             | and energy trade-offs for different degrees of                  |            |

|             | logic compression of $(8 \times 8)$ multiplier                  | <b>72</b>  |

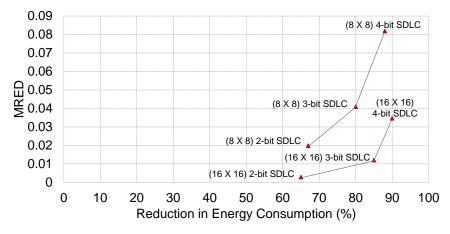

| Figure 3.17 | The mean relative error distance (MRED) and                     |            |

|             | PDP trade-offs for different degrees of logic                   |            |

|             | compression of (8 $\times$ 8) and (16 $\times$ 16) multipliers. | <b>7</b> 3 |

| Figure 3.18 | Area and power trade-offs for various scal-                     |            |

|             | able approximate multipliers                                    | 74         |

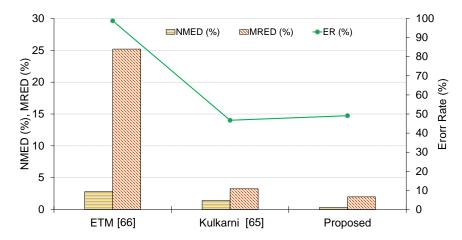

| Figure 3.19 | Comparative errors in terms of MRED,                 |            |

|-------------|------------------------------------------------------|------------|

|             | normalized mean error distance (NMED) and            |            |

|             | also ER for various scalable (8 $\times$ 8) approxi- |            |

|             | mate multipliers.                                    | <b>7</b> 6 |

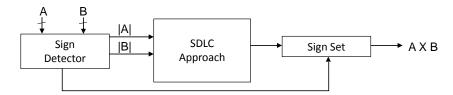

| Figure 3.20 | Block diagram for one of the options of              |            |

|             | hardware implementation required to im-              |            |

|             | plement the proposed signed multiplier (in-          |            |

|             | spired from [132])                                   | 77         |

| Figure 3.21 | Partial product matrix of $(8 \times 8)$ signed mul- |            |

|             | tiplier. Complemented partial products are           |            |

|             | highlighted in blue                                  | <b>7</b> 8 |

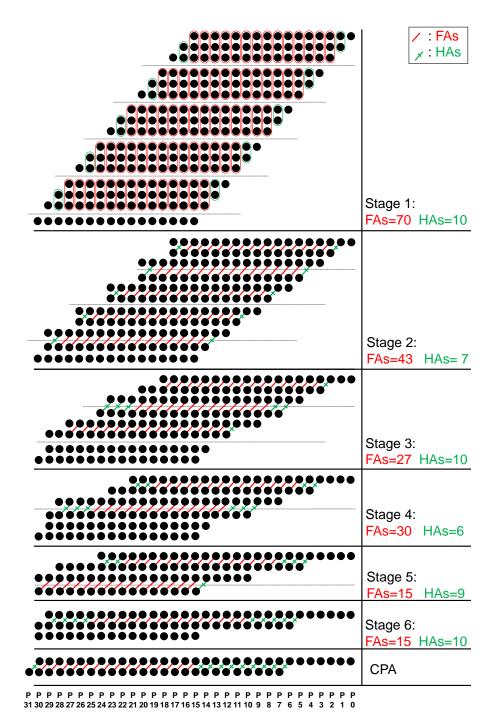

| Figure 4.1  | Reduction stages and logic cell counts for           |            |

|             | $(16 \times 16)$ accurate Wallace                    | 84         |

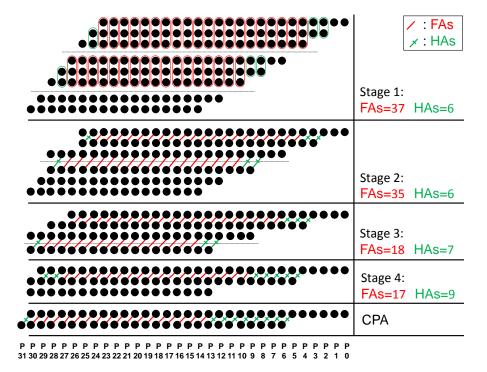

| Figure 4.2  | Reduction stages and logic cell counts for           |            |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |            |

|             | rating 2-bit significance-driven logic com-          |            |

|             | pression (SDLC) with Wallace-tree accumula-          |            |

|             | tion (2-bit SDLC Wallace)                            | 85         |

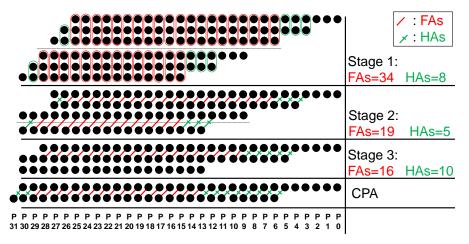

| Figure 4.3  | Reduction stages and logic cell counts for           |            |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |            |

|             | rating 3-bit SDLC with Wallace-tree accumu-          |            |

|             | lation (3-bit SDLC Wallace)                          | 86         |

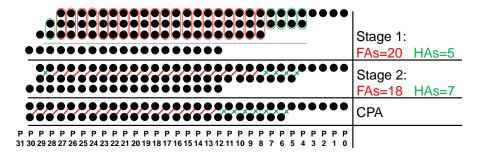

| Figure 4.4  | Reduction stages and logic cell counts for           |            |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |            |

|             | rating 4-bit SDLC with Wallace-tree accumu-          |            |

|             | lation (4-bit SDLC Wallace)                          | 86         |

| Figure 4.5  | Reduction stages and logic cell counts for           |            |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |            |

|             | rating 5-bit SDLC with Wallace-tree accumu-          |            |

|             | lation (5-bit SDLC Wallace)                          | 87         |

| Figure 4.6  | Reduction stages and logic cell counts for           |    |

|-------------|------------------------------------------------------|----|

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |    |

|             | rating 6-bit SDLC with Wallace-tree accumu-          |    |

|             | lation (6-bit SDLC Wallace)                          | 87 |

| Figure 4.7  | Reduction stages and logic cell counts for           |    |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |    |

|             | rating 7-bit SDLC with Wallace-tree accumu-          |    |

|             | lation (7-bit SDLC Wallace)                          | 87 |

| Figure 4.8  | Reduction stages and logic cell counts for           |    |

|             | $(16 \times 16)$ proposed multiplier when incorpo-   |    |

|             | rating 8-bit SDLC with Wallace-tree accumu-          |    |

|             | lation (8-bit SDLC Wallace)                          | 87 |

| Figure 4.9  | Wallace reduction stages of an $(8 \times 8)$ multi- |    |

|             | plier: (a) accurate Wallace tree; then Wallace       |    |

|             | method coupled with (b) 2-bit SDLC; (c) 3-bit        |    |

|             | SDLC and (d) 4-bit SDLC                              | 90 |

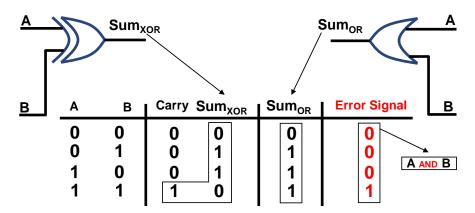

| Figure 4.10 | 2-bit OR gate is sufficient to find the sum of       |    |

|             | two bits.                                            | 92 |

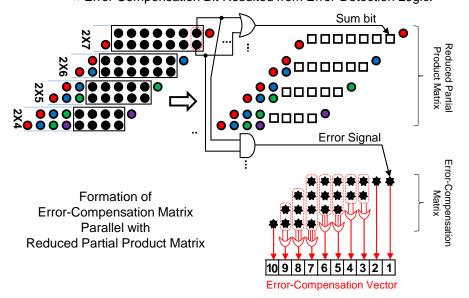

| Figure 4.11 | A parallel error-detection logic to generate         |    |

|             | the error compensation bit-matrix in the case        |    |

|             | of 2-bit SDLC, and then, array of OR gates to        |    |

|             | form the error-compensation vector                   | 93 |

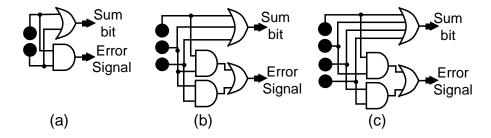

| Figure 4.12 | The error-detection logic circuit parallel with      |    |

|             | the logic clusters required by error compen-         |    |

|             | sation method (ECM) in: (a) 2-bit; (b) 3-bit;        |    |

|             | (c) 4-bit logic clusters.                            | 94 |

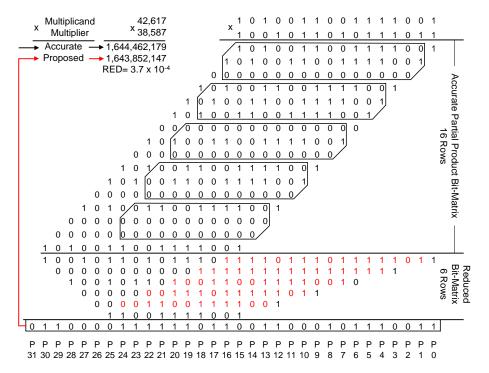

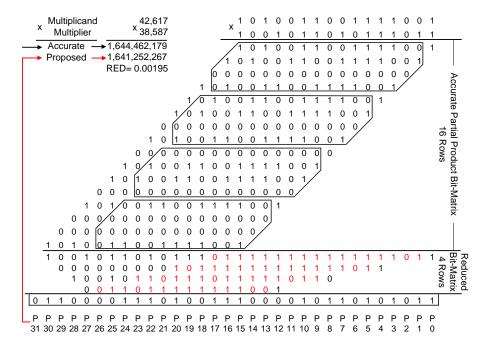

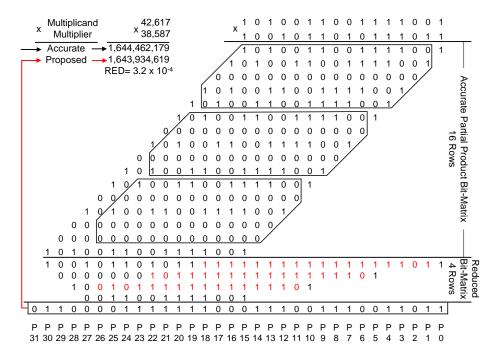

| Figure 4.13 | Improving accuracy by allowing error-                |    |

|             | compensation vector to modify an existing            |    |

|             | row in Wallace accumulation tree                     | 95 |

| Figure 4.14 | Improving accuracy by including error-                     |   |

|-------------|------------------------------------------------------------|---|

|             | compensation vector as an additional row                   |   |

|             | in Wallace accumulation tree 9                             | 6 |

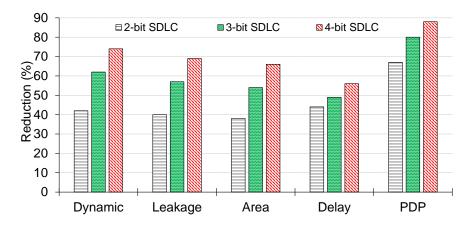

| Figure 4.15 | Cumulative probability distribution for the                |   |

|             | error induced by different logic compression               |   |

|             | levels coupled with the proposed $\underline{ECM}$ in the  |   |

|             | case of $(8 \times 8)$ proposed multiplier 9               | 8 |

| Figure 4.16 | The impact of the proposed ECM on the $(8 \times 8)$       |   |

|             | approximate Wallace multiplier with: (a) 2-                |   |

|             | bit, (b) 3-bit and (c) 4-bit logic compression             |   |

|             | levels                                                     | 0 |

| Figure 4.17 | The impact of the proposed ECM on the (16 $\times$         |   |

|             | 16) approximate Wallace multiplier with: (a)               |   |

|             | 2-bit, (b) 3-bit and (c) 4-bit logic compression           |   |

|             | levels                                                     | 2 |

| Figure 5.1  | Flowchart diagram showing the main steps                   |   |

|             | for evaluating the impact of the proposed                  |   |

|             | multiplier on the final quality of image pro-              |   |

|             | cessed by Gaussian blur filter 10                          | 7 |

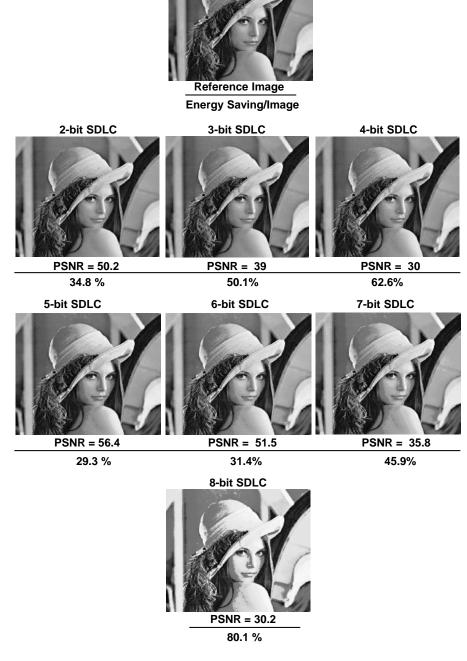

| Figure 5.2  | Output quality after applying Gaussian blur                |   |

|             | filtering for different degrees of logic com-              |   |

|             | pression of the proposed (8 $\times$ 8) multiplier 10      | 9 |

| Figure 5.3  | Output quality after applying Gaussian blur                |   |

|             | filtering for different degrees of logic com-              |   |

|             | pression of of the proposed (16 $\times$ 16) multiplier.11 | 0 |

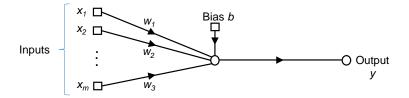

| Figure 5.4  | Signal-flow graph of the perceptron 11                     | 1 |

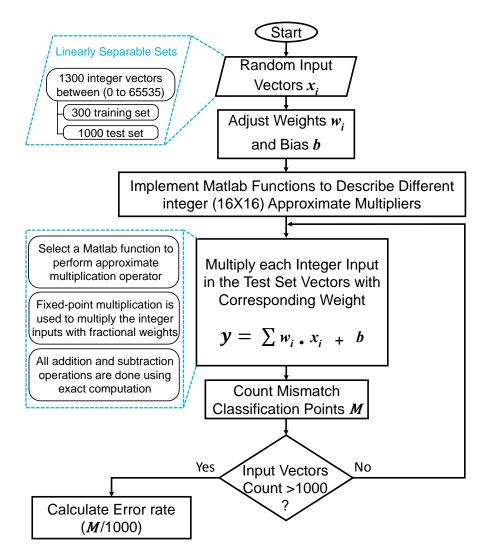

| Figure 5.5  | Flowchart diagram demonstrating the main                   |   |

|             | steps for evaluating the impact of the pro-                |   |

|             | posed multiplier on a perceptron-based Clas-               |   |

|             | sifier                                                     | 2 |

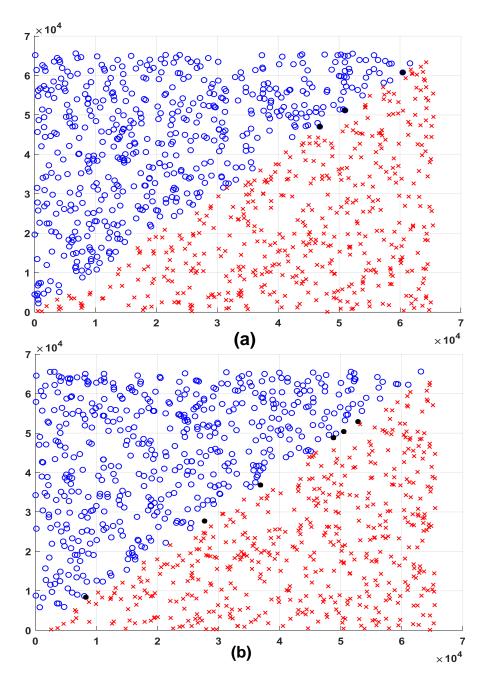

Figure 5.6 The test set perceptron classification using;

(a) accurate multiplier; (b) 2-bit SDLC proposed multiplier, where the axises show the random inputs between 0 to 65535. (blue and red points represent two classes -1 and +1, black dots for mismatch classification points.)114

### LIST OF TABLES

| Table 2.1 | Truth table for the accurate and approxi-              |    |

|-----------|--------------------------------------------------------|----|

|           | mate (2 $\times$ 2) multipliers, used to obtain com-   |    |

|           | parative error analysis in Fig. 2.5, with              |    |

|           | changed entry highlighted                              | 18 |

| Table 2.2 | Summary of approximate multiplier design               |    |

|           | approaches                                             | 32 |

| Table 3.1 | Error metrics for varying sizes of proposed            |    |

|           | multiplier using 2-bit logic cluster                   | 62 |

| Table 3.2 | Error metrics for different depths of logic            |    |

|           | compression in the proposed (8 $\times$ 8) multiplier. | 64 |

| Table 3.3 | Error metrics for different depths of logic            |    |

|           | compression in the proposed (16 $\times$ 16) multi-    |    |

|           | plier                                                  | 65 |

| Table 3.4 | Design trade-offs for different bit-widths of          |    |

|           | the accurate multiplier used to obtain com-            |    |

|           | parative analysis in Fig. 3.14.                        | 69 |

| Table 3.5 | Design trade-offs for different bit-widths of          |    |

|           | the proposed multiplier used to obtain com-            |    |

|           | parative analysis in Fig. 3.14                         | 70 |

| Table 3.6 | Number of library cells instantiated to form                                                            |     |

|-----------|---------------------------------------------------------------------------------------------------------|-----|

|           | different bit-widths of the (2-bit SDLC) pro-                                                           |     |

|           | posed multiplier.                                                                                       | 70  |

| Table 4.1 | Reduction stages and logic cell counts for                                                              |     |

|           | $(16 \times 16)$ proposed multiplier when incorpo-                                                      |     |

|           | rating different levels of logic compression                                                            |     |

|           | with Wallace-tree accumulation                                                                          | 88  |

| Table 4.2 | Reduction stages and logic cell counts for                                                              |     |

|           | $(8 \times 8)$ proposed multiplier when incorporat-                                                     |     |

|           | ing different levels of logic compression with                                                          |     |

|           | Wallace-tree accumulation                                                                               | 90  |

| Table 4.3 | ECM drastically reduces the errors across all                                                           |     |

|           | metrics                                                                                                 | 97  |

| Table 4.4 | Design trade-offs for different compression                                                             |     |

|           | levels of the proposed multiplier used to ob-                                                           |     |

|           | tain comparative analysis in Fig. 4.16                                                                  | 101 |

| Table 4.5 | Design trade-offs for different compression                                                             |     |

|           | levels of the proposed multiplier used to ob-                                                           |     |

|           | tain comparative analysis in Fig. 4.17                                                                  | 103 |

| Table 5.1 | Error rate results and energy savings for                                                               |     |

|           | perceptron classifier                                                                                   | 115 |

|           |                                                                                                         |     |

| LIST OF A | LGORITHMS                                                                                               |     |

|           | rating the output bits of the logic cluster of the $w$ for the proposed $(N \times N)$ multiplier using |     |

| 3.2 | Generating a reduced partial product matrix M for           |    |

|-----|-------------------------------------------------------------|----|

|     | $(N \times N)$ multiplier using SDLC approach with $d$ -bit |    |

|     | logic clusters, $\forall \{d \in \{2,3,,N\}.$               | 54 |

| 4.1 | $(N \times N)$ Wallace-tree multiplier using SDLC approach  |    |

|     | with $d$ -bit logic clusters                                | 91 |

### ACRONYMS

\_\_\_\_\_

CMOS complementary metal-oxide-semiconductor

CPA carry propagating adder

DSP digital signal processing

ECM error compensation method

**ED** error distance

EDA electronic design automation

**EP** error probability

**ER** error rate

ETM error-tolerant multiplier

MBE modified Booth-encoding

MED mean error distance

MRED mean relative error distance

$\textbf{MSE} \hspace{0.2cm} \text{mean squared error} \\$

NMED normalized mean error distance

NMRED normalized mean relative error distance

NMSE normalized mean squared error

PDP power-delay-product

PEQ performance-energy-quality

**PPM** partial product matrix

PSNR peak signal-to-noise ratio

QoR quality of result

**RED** relative error distance

RTL register-transfer level

SDLC significance-driven logic compression

SoC system-on-chip

**vos** voltage over-scaling

### Part I

**Thesis Chapters**

### INTRODUCTION

A promising design paradigm—approximate computing—has recently emerged to harness imprecision resilience, in a broad spectrum of computing applications, to achieve additional optimizations. This chapter presents the motivation and defines the key concepts and terms in context of the research reported in this thesis. It highlights the necessity of approximate computing as a way for improving energy and performance efficiency in the field of arithmetic multiplier design. Then, the main contributions of this research together with thesis organisation are discussed.

### 1.1 MOTIVATION

Over the past decades, the continuing advances in technology scaling have shown an increasingly difficult design challenge to deliver high performance without dramatically increasing energy consumption [53, 26, 14, 7, 129]. Therefore, developing new solutions to tackle this challenge is considered as an imperative need for a number of reasons, such as improving hardware functionality for battery-powered computing devices, or increasing processing capabilities for those devices where energy is harvested from environmental sources. The motivation of this work is introduced as follows.

### 1.1.1 Energy-Efficient Computing

The computational performance demands driven by a massive volume of global data and a vast number of connected users, have exceeded the current processing capacity of the ever-evolving digital world [41]. It is expected that emerging applications will create 163 zettabytes of data by 2025 (ten times as much as was made in 2017) [98]. Furthermore, the global internet users have now passed the 4 billion mark (as of January, 2018) [61]. The vast majority of them were accessing their chosen platforms via mobile devices [61]. Moreover, the evolution of worldwide electricity demand of data centres [4] is related to the exponential growth in global digital-data creation [98]. This opens the way for finding alternative computing systems that use relatively less energy, while providing the processing performance they need.

For the last three decades, the need for higher computational performance has been supported by the exponential scaling of integrated circuits and many-core system-on-chip (SoC) technologies [24]. However, the rapid growth in these technologies is synchronized with the decline of *Moore's law* [81]. This means that, as the downscaling of the complementary metal-oxide-semiconductor (CMOS) is completely stretched to limits, technology scaling will less likely be a driver for computing in the near future [110, 105, 103, 62]. Moreover, the per-transistor performance power efficiency is not keeping pace with known power-reduction techniques at various abstraction levels [88, 34, 31]. This eventually results in the so-called *Dark Silicon* era [108], which means it may only be possible to power-on a fraction of on-chip computing resources in order to stay within the power density and safe thermal limits.

Indeed, there is a genuine need to explore new computing paradigms to deliver more energy efficiency and also, to squeeze more functionality out of computing platforms across the spectrum, from mobile and deeply-embedded devices to servers and data centres. Approximate computing paradigm is a promising approach to this end [33, 48, 78, 109, 107]. In the following sub section we introduce approximate computing and multiplier design in details.

### 1.1.2 Approximate Multiplier Design

Approximate computing is an emerging design paradigm that leverages the presence of inherent-resilience in a broad spectrum of hardware and software implementations by relaxing the need for completely precise or totally deterministic operations. It can offer substantial reductions in circuit complexity, delay and energy consumption by relaxing accuracy requirements [78]. Approximate computing has the potential to benefit a wide range of modern applications, such as media processing (image, audio, and video), digital signal processing (DSP), machine learning (recognition and data mining), wireless communication, web search, and data analytics [109]. It exploits the inherent-resilience code regions in such applications and also perceptual limitations of users to intelligently trade off outcomes accuracy for performance and energy gains [107].

The basic premise of approximate computing, in the hardware domain, is to build hardware blocks whose implementation does not exactly match the specification, either due to the impact of functional approximation (e.g., implement a slightly different Boolean function that has a faster or more power-efficient implementation), or due to timing approximations (e.g., voltage over-scaling

(VOS) and over-clocking). Therefore, approximate computing trades off output quality for achieving much lower power consumption, shorter run times, and often smaller silicon area at the cost of imprecision introduced to the processed data [17].

Over the years, a number of approximate computing approaches have been proposed (see Chapter 2). These approaches aim to reduce the complexity of the circuits and systems in terms of their computation latency and energy consumption [49]. Approximations can be introduced at all design levels, starting from the circuit [46] via the logic [92] and the architecture [2, 37] to programming language [101] and algorithms [57, 32].

Approximate arithmetic, such as approximate adders and multipliers, has gained significant interest in various group of imprecision-resilient applications [59, 49, 29, 120]. Approximate arithmetic is based on replacing traditional complex and energy-wasteful data processing blocks by low-complexity ones with reduced logic counts, and therefore, improving the computational performance and energy efficiency of the computing systems.

Multipliers are crucial arithmetic units in modern applications, for two major factors. Firstly, they are characterized by complex logic design, being one of the most energy-demanding data processing units in modern microprocessors. Secondly, compute-intensive applications typically exercise a large number of multiplication operations to compute outcomes. Thus, any improvement made in the power/speed of a multiplier is expected to substantially impact on overall system power/performance trade-offs [75, 58].

A typical  $(N \times N)$  accurate multiplier generates  $N^2$  product terms, which are then accumulated as a final product of size 2N. The accuracy of this product depends largely on the significance of bits. Hence, preserving higher-significance bits is likely to gen-

erate an outcome close to the exact product than that of lowersignificance bits. This can be exploited to progressively compress higher order combinatorial terms systematically and to achieve substantial energy savings at low loss of accuracy.

Existing multiplier design approaches consist of redesign efforts (such as reducing the circuit complexity (*i.e.*, critical path)) and parametric variations (such as supply voltage/frequency over-scaling). The basic principle in these designs is to improve energy/performance-efficiency at cost of functional or timing-induced errors. While these design approaches have made piecemeal advances in different directions, they leave rooms for further improvements (see Chapter 2). For example, *how can multiplier critical path be progressively reduced using different levels of approximations*.

### 1.2 THESIS SCOPE AND CONTRIBUTIONS

This thesis attempts to address the above fundamental question by exploring promising research directions in the development of energy-efficient multiplier design. It presents novel design approaches for improving energy and performance efficiency of approximate multiplier with variable-accuracy implementations. From the perspective of levels of abstraction, the research work in this thesis focuses on modifying the behavioural description of the multiplier design from gate level and register-transfer level (RTL). The proposed designs targets parallel multiplication, particularly for integer input operands. The aim is to develop design-time configurable prototypes to trade off output accuracy for various performance and energy gains. We apply the design approach of approximate multiplier to standard scheme of multiplication (e.g.

Wallace-tree). Additionally, we demonstrate a methodology to mitigate the impact of errors at various approximation levels, and study their impact on different imprecision-resilient applications. The main contributions of this thesis are listed as follows:

- a novel energy-efficient approach is proposed for approximate multiplier design using significance-driven logic compression (SDLC). The basic principle of the proposed approach is to cut the carry chain needed by accumulation tree, in a way that the significant bits of the product are slightly affected. To achieve this goal, the number of product terms is reduced by using lowcomplexity logic gates (i.e., using OR gates to sum up these terms instead of expensive XOR gates) —we denote this method as *logic compression*. The reduced number of product terms is then followed by remapping, based on their commutative properties, to reduce the resulting number of rows in the partial product matrix (PPM). At the core of SDLC approach is a designtime configurable logic compression of product terms aims at achieving different performance-energy-quality (PEQ) trade-offs. Several multiplier prototypes (extending from 4-bit to 128-bit) are synthesized using electronic design automation (EDA) tools, showing up to an order of magnitude energy savings with various reductions in critical path delay and silicon area. Furthermore, extensive error analysis and comparison are placed to evaluate the efficiency of the proposed multiplier with respect to state-of-the-art multiplier designs [93, 94, 92].

- a novel energy-efficient approximate multiplier design by incorporating SDLC approach together with already existing column-compression methods, such as Wallace and Dadda-tree, to shorten the number of reduction stages. As such, the hardware complexity of the multiplier implementation is drastically re-

duced. Moreover, to minimize the impact of error associated with lossy compression, an error detection technique using parallel logic array along with error compensation method (ECM) is added at low overhead cost. The aim is to generate error compensation vector to either combine it as additional row in the accumulation tree or to replace one of the existing rows. A robust error analysis is included to evaluate the effectiveness of ECM. The post-synthesis experiments shows substantial saving in all design trade-offs, when comparing to accurate equivalent [92],

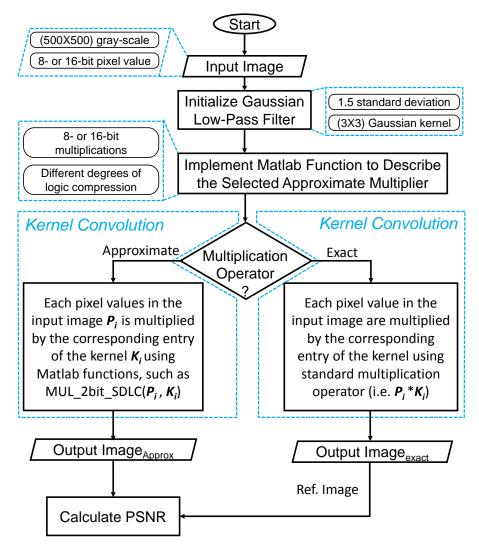

• the PEQ trade-offs achieved by the proposed multiplier designs are extensively investigated into two real-application case studies demonstrating comparative advantages of SDLC approach. First, a Gaussian blur filter with a meagre loss of image quality. Second, machine learning application using perceptron classifier with negligible error rate. For both case studies, substantial energy reductions are achieved and analysed [93, 94, 92].

### 1.3 THESIS OVERVIEW

This thesis is organized into six chapters. The major contributions of this thesis are summarized as follows:

Chapter 2 provides a coherent overview of extensively adopted and recently reported approaches for energy-efficient imprecise hardware. It defines the objectives of approximate computing, and also discusses the design approaches for approximate circuits. This is followed by a survey of approximate multiplier design to date. Various design techniques are discussed and classified based on multi-dimensional taxonomy to emphasize their similarities and differences. This chapter can inspire more efforts to address the

challenges facing quantifying errors derived from approximate arithmetic circuits, in particular, multipliers.

Chapter 3 proposes the SDLC approach for energy-efficient approximate multiplier design. It demonstrates how logic compression and commutative remapping are used to reduce the number of product rows. Error analysis and post-synthesis experiments are discussed, showing the PEQ trade-offs for different input bit-widths and compression levels. This chapter presents an algorithmic and design-time configurable lossy compression of the partial product rows. Additionally, it studies a group of related subjects covering the scalability of the SDLC approach and the feasibility of SDLC in signed multiplication. Comparative results against other existing approaches are also presented.

Chapter 4 studies the multiplier design by combining a Wallace-tree accumulation method together with the SDLC approach. A parallel error-detection logic and also error-compensation method (ECM) are presented, showing different ways to reduce the impact of error associated with SDLC. This chapter provides evaluation of the impact of ECM on variable logic compression, with extensive error analysis supported by a number of post-synthesis experiments.

Chapter 5 demonstrates the effectiveness of the PEQ trade-offs achieved by the proposed multiplier designs in applications. This chapter exhibits two case studies; image processing application using Gaussian blur filter and machine learning application using perceptron classifier. It also discusses the energy savings and quality loss arising from the implementations.

Chapter 6 summarizes the contributions and key highlights of this thesis, showing critical review of this research together with the potential future directions. Overall, this thesis shows promising design and implementation approaches for approximate multiplier design, with different configuration. It can inspire designers to take advantage of the PEQ trade-offs, achieved by the SDLC approach, to achieve more energy and performance efficiency for ubiquitous computing systems.

### BACKGROUND AND LITERATURE SURVEY

### 2.1 INTRODUCTION

In last decade, there has been an increasing interest in approximate computing as one of the most promising energy-efficient computing paradigms. Approximate computing exploits the flexibility provided by inherent application resilience in hardware or software implementations for more performance and energy gains [100]. Approximate computing research combines insights from hardware engineering, architecture, system design, programming languages, and even application domains like image processing [17] and machine learning [84]. However, approximate computing based on software techniques has been deemed out of scope for this thesis.

This chapter highlights the basic concepts behind approximate circuits to understand the motivation and the choices made in the context of this work. First, we introduce and discuss several related imprecise computing in hardware to let the reader distinguish the efforts in approximate circuits from other related imprecise designs in the area. Then, a brief review is proposed for the recent developments in approximate circuits, showing the major approaches for exploiting the imprecision-resilience of various applications. Since the approximate multiplier design is the primary theme of this thesis, the second part of this chapter is made to emphasize the research efforts in the field of approximate multiplier design found so far with taxonomy provided. In

order to identify a trade-off between approximation and reliability, the existing error metrics are defined and classified to help the reader to specify right metric for a given approximate multiplier. Finally, a discussion is placed for the challenges of quantifying the imprecision in the multiplier design.

### 2.2 APPROXIMATE CIRCUIT DESIGN

In the literature, there are various research efforts devoted to addressing different designs of imprecise computing in hardware. In this section, we denote the hardware that does not produce the exact output at all times by *imprecise hardware*. The reason for this concept is to make it include a variety of existing designs that can lead to error in the output, such as in approximate, probabilistic and non-Boolean circuits. The next subsection is to let the reader understand the scope of approximate circuit design by distinguishing the work on it from related but conceptually distinct efforts in probabilistic and non-Boolean circuits.

### 2.2.1 Imprecise Hardware Design

In this section, imprecise hardware, including probabilistic, non-Boolean and approximate designs, is introduced to understand the scope of the approximate circuits from other related efforts in the literature. Fig. 2.1 presents a taxonomy of related terms in this area. Hence, these terms are briefly discussed with some illustrative examples —as follows:

Figure 2.1: Taxonomy of imprecise computation in hardware.

## 2.2.1.1 Probabilistic circuits

Three computing technologies are used by the circuit whose behaviour is inherently probabilistic: probabilistic CMOS (PCMOS), quantum and stochastic circuits. PCMOS and quantum circuits and signals are inherently probabilistic, while stochastic circuits utilize deterministic means for representing and processing probabilistic data [89, 77]. These computing technologies are briefly discussed as follows.

- Probabilistic CMOS is a particular form of CMOS called PC-MOS, which is invented with a hope to compete against current energy-efficient CMOS technology. It is motivated by inherent "erroneous" behaviour in hardware as we move to smaller technology nodes. This is due to process variations and noise susceptibility [63, 83, 112]. Considering that CMOS devices have an exponential relationship between the *probability of exactness* (*P*) and the *switching energy* (*E*). To this end, PCMOS devices can harness the noise as a resource to achieve low-power and high-performance computation [16, 56]. However, the computing platforms based on PCMOS devices can compute efficiently at the cost of introducing error with a probability (1 *P*) [16].

- Quantum circuits show another type of inherently probabilistic computations that perform efficient algorithms for some intractable problems in classical computer science [67, 87], such as fast number factorization [114]. Following the laws of quan-

tum physics, quantum circuits offers enormous processing power through the ability to be in multiple states, and to perform tasks using all possible permutations simultaneously. Quantum computing processes data in the form of qubits (quantum bits). A qubit  $\Psi$  has two parts  $\alpha$  and  $\beta$  indicating its "zeroness" and "oneness" probabilities, respectively. It can be introduced in several standard forms [87]:

$$|\Psi\rangle = \alpha |0\rangle + \beta |1\rangle = \begin{bmatrix} \alpha \\ \beta \end{bmatrix} , \qquad (2.1)$$

here  $\alpha$  and  $\beta$  are complex numbers called *probabilistic amplitudes*. When measuring the *qubit*'s value  $\Psi$ , quantum mechanics requires that the output be 0 or 1 with specific probabilities, implying that  $|\alpha|^2 + |\beta|^2 = 1$ . Generally, the inherent imprecision behaviour in quantum circuits comes from two reasons. First, the probabilistic results, *i.e.*, a quantum circuit generates different output values when run more than once with the same inputs. Second, when quantum circuit is implemented by a reduced number of quantum gates, *i.e.*, one or more quantum gates is missing, an example is demonstrated in Fig. 2.2.

Figure 2.2: Example of a small quantum circuit *3qubitcnot*: (a) fault-free circuit, and (b) faulty circuit by eliminating a single H gate [6].

• Stochastic circuits is a class of computing circuits in which a number is represented by randomized values in serial "streams" or on parallel "bundles" of wires [91]. In the case of serially

streaming, the signals are probabilistic in *time* whereas, in parallel, they are probabilistic in *space*, as demonstrated in Fig. 2.3. Consider an n-bit stream X containing j "ones" and n-j "zeros". The ratio j/n can be seen as the probability x of a randomly-observed bit in X being "one".

Figure 2.3: Stochastic encoding: (a) a stochastic bit stream; (b) a stochastic wire bundle. For each bit in the bit stream or a bundle, the probability that it is  $1 ext{ is } P(X = 1) = x$ .

The main attraction of stochastic hardware is its ability to carry out complex operations with simple circuits. For example, serial multiplication can be implemented by a two-input AND gate, see Fig. 2.4. Stochastic computing consists of operations on the  $x_i$ 's associated with a set of  $X_i$ 's of fixed or variable length n. In Fig. 2.4, the inputs denoted  $x_1 = 9/12 = 0.75$  and  $x_2 = 6/12 = 0.5$ ; the output signal probability is 4/12 = 0.333, which roughly approximates the product by using the input signal probabilities to  $x_1 \times x_2 = 0.75 \times 0.5 = 0.375$ .

Small errors like a 0 replacing a 1 due to a lost 1-pulse, have little effect on bit-stream signal probabilities, hence stochas-

Figure 2.4: Stochastic multiplication using an AND gate.

tic computing is inherently tolerant of bit-flip errors. However, such computing has some drawbacks. For instance, meeting higher precision requirement leads to exponential increase in the computing times of the stochastic circuits, especially when not ensuring sufficiently low correlation among the circuit's signals [3]. To explain, the stochastic multiplier in Fig. 2.4 requires input signals that are pseudo-random and uncorrelated. Meaning that, if the input bit-streams are both identical in bit-for-bit representation X of x=0.5, *i.e.*, maximally correlated, the output will be the same as X with 0.5 instead of the expected product of  $x_1 \times x_2 = 0.5^2 = 0.25$ —which is a huge error.

## 2.2.1.2 Non-Boolean circuits

Non-Boolean computing refers to the class of computing where analog devices are used to store/process data. For example, a single storage bit can correspond to more than 2 values at any instant of time as opposed to combinational logic where a bit can only correspond to truth-values (0 or 1) [111, 68, 22]. Non-Boolean circuits can go beyond these definitions. It has proven to be much more efficient at various computational task, such as simulating biological systems using analog transistors [50], than digital computing. However, since analog computing uses continuous values, processes cannot be reliably repeated with exact equivalence [19]. Moreover, existing analog computers have to be programmed manually, *i.e.*, a complex process that would be very time consuming for large-scale and application-specific simulations [51]. However, the potential for these technologies to perform useful non-Boolean computations remains an opportunity to be explored.

# 2.2.1.3 Approximate Circuits

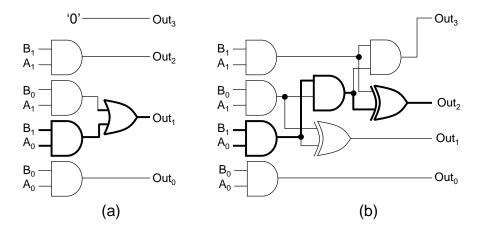

Approximate circuits refer to a class of computing where deterministic designs are used to produce outputs with some tolerable level of missing accuracy in favour of improving performance and energy-efficiency. Approximate computing does not involve assumptions on the probabilistic nature when implementing circuits. However, it often utilizes statistical properties to trade quality for energy/power reduction [48]. For example, Fig. 2.5 illustrates the accurate and approximate circuits for  $(2 \times 2)$  multiplier suggested in [65]. The error statistics of the approximate circuit are shown in Table 2.1. The main objective is to introduce error into the multiplier by manipulating its logic function. It can be observed that it is possible to represent the output of  $(2 \times 2)$  multiplication using just three bits instead of four. As a result, the approximate circuit has an incorrect output out of the sixteen possible inputs (with a magnitude of 9-7=2 and a probability of 1/16 (assuming a uniform input distribution). However, the approximate multiplier in Fig. 2.5-(a) has nearly half the area of the accurate one, with shorter critical path and less interconnect. Thus, the approximate version offers the potential for significant dynamic power reduction

Figure 2.5: Example of a  $(2 \times 2)$  multiplier: (a) approximate, and (b) accurate, with the critical paths highlighted [65].

**Inputs Outputs** Error B0Accurate Free Distance **B1** A1 A0 Approximate  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$  $\sqrt{}$

Table 2.1: Truth table for the accurate and approximate  $(2\times2)$  multipliers, used to obtain comparative error analysis in Fig. 2.5, with changed entry highlighted.

for the same frequency of operation —due to smaller switching capacitance.

$\sqrt{}$

The key principle of the above imprecise hardware designs (*i.e.*, probabilistic, non-Boolean and approximate) is to trade little accuracy loss in the output for improving performance and energy efficiency in emerging computing systems. However, a taxonomy of approximate circuits is further discussed in the following sections, showing their potential to benefit many emerging applications using different design approaches. In the next subsection, we define the intrinsic attribute of imprecision-resilience in a wide range of applications.

# 2.2.1.4 Expliciting Imprecision-Resilience

Approximate computing exploits the inherent resilience in a broad spectrum of hardware implementations by relaxing the need for completely precise or totally deterministic operations. Recently, however, ideas have emerged how to make errors help reduce runtime of operations and power consumption. Errors are becoming an intentional feature in the hardware design because of tangible trade-offs and application-based error-resilience. Error-resilience can be defined as the characteristic of a system to produce acceptable results regardless of task computations being achieved imprecisely.

Approximate computing design requires a deeper knowledge of inherent resilience applications [48]. It can improve the performance and energy efficiency by exploiting perceptual limitation (*i.e.*, errors are not recognizable because human perception capabilities, *e.g.*, in multimedia applications). Such applications can adequately operate without the need of functional equivalence of the specification and implementation. These applications are common in the hardware circuits mobile, embedded, and server systems and can be broadly classified into four categories [127, 35, 48]:

- applications with analog inputs that operate on noisy real-world data, such as image processing, sensor data processing, voice recognition,

- applications with analog output prepared for human perception,

such as multimedia, image rendering, sound synthesis,

- applications with no golden answer, such as web search and machine learning, and

- iterative and convergent applications that iteratively process large amounts of redundant data and the quality of result (QoR)

depends on the number of iterations. This redundancy often means that an algorithm can be lossy and still be sufficient.

Approximate circuits harness imprecision-resilience in the above applications and thereby offer substantial reduction in delay and energy consumption. This can be done by different explicit design approaches, which are discussed as follows.

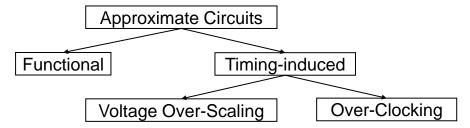

# 2.2.2 Taxonomy of Approximate Circuits

Applying the concept of approximate computing in hardware consists of two basic design approaches [107, 109, 78]:

- Timing-induced approximation (voltage over-scaling (VOS) and over-clocking), and

- Functional approximation.

Fig. 2.6 shows a taxonomy of design approaches in approximate circuits. The voltage over-scaling [96, 76] and over-clocking [27, 28] approaches use ordinary circuits that work perfectly fine under usual circumstances. The first design approach can reduce power consumption by scaling the supply voltage below nominal value, which can cause the occurrence of occasional violations. Generally, in CMOS technology, the power consumption associated with task

Figure 2.6: Taxonomy of approximate circuits.

is dominated by dynamic power dissipation  $P_{dynamic}$ , which is given by [95]:

$$P_{dynamic} = C_{eff} \cdot V_{dd}^2 \cdot f \quad , \tag{2.2}$$

where  $V_{dd}$  is the supply voltage,  $C_{eff}$  is the effective switched capacitance, and f is the clock frequency. Therefore, scaling down the supply voltage leads to an overall quadratic reduction in the energy to complete a task. However, while maintaining a fixed performance, aggressive scaling of supply voltage leads to timing errors. The literature have shown different ways to reduce the impact of such induced errors in the systems, such as adding error detection and correction circuits, which often operate within normal supply voltage [86].

Over-clocking can achieve more performance by improving circuit's working frequency over the maximum frequency. This leads to the occurrence of timing errors, but better overall performance [27, 28]. Generally, for any given voltage, the circuit will have a maximum "stable" speed where they still operate correctly. However, while operating on constant voltage, a designer may trade the manufacturer's safety margin by setting the device to run in the higher end of the margin. For example, a work towards "overclocking friendly", in online arithmetic implementations, shows that exercising over-clocking technique for serial operations can gain large performance benefits with a graceful degradation of timing violations [113].

Unlike voltage/frequency over-scaling, functional approximation does not use the original circuit but a specially designed one instead. This circuit is redesigned without fully Boolean logic implementation described in the specification. For instance, a common method for implementing functional approximation is to omit the

less significant bits of the result by removing related logic. This is expected to reduce the circuit complexity (*i.e.*, critical path), and therefore, achieving more performance/energy efficiency than the accurate version, with some amount of error in the less significant bits of output. However, the above-mentioned approaches used by approximate circuits are further discussed from the perspective of multiplier design, since it is the main theme of this thesis. The next subsection introduces a brief overview for applying the concept of approximate computing in arithmetic circuits.

# 2.2.2.1 Approximate Arithmetic

Approximate arithmetic, such as approximate adders and multipliers, can be exploited as means of reducing energy requirements, increasing speed, minimizing cost and improving reliability in various computing systems [59]. They have been largely present in computing systems using fixed-point [42] and floating point operations [120]. The main goal has been to obtain exact or close to exact outputs by using error mitigation techniques ranging from increasingly sophisticated rounding to interval arithmetic [29].

Literature has presented different techniques for approximate arithmetic [59], particulary for adders and multipliers. Comparing to multipliers, approximate adders have been attracting most attention [48]. The main design approaches for approximate adders are surveyed into [59, 29, 48]. The next section discusses the related work in the domain approximate multipliers found up to date.

#### 2.3 APPROXIMATE MULTIPLIER DESIGN

A multiplier design has a significant impact on the performance and power dissipation of modern applications [58, 29], such as digital signal processing, multi-media, computer vision, robotics, machine learning, pattern recognition and data analytics. This is due to two main reasons:

- Multiplier is one of the most energy-demanding data processing units in arithmetic processors. Compared to other units, such as adders, multipliers have complex logic design in terms of logic cell counts and length of critical path.

- Most of the algorithms exercised by compute-intensive applications use a large number of multiplication operations to compute results.

Thus, as a crucial arithmetic unit, any improvement made in the power/speed of a multiplier are expected to largely impact on the overall system performance/energy trade-offs. In the literature, many approaches have been used to generate various approximate multiplier designs. Not all of these approaches are entirely fall under the concept of approximate computing. For instance, multipliers have been redesigned based on PCMOS technology [43], quantum theory [18] and stochastic concept [115]. Another design approaches target the multiplier for FPGA-based hardware accelerators [123, 122]. However, the next part presents a taxonomy of approximate multiplier designs that is then used to survey and classify the state-of-the-art research in this area.

# 2.3.1 Taxonomy and Survey

In this section, we present a taxonomy of six different directions to classify the related research efforts of approximate multiplier design (see Fig. 2.7). From the perspective of approximate circuit approaches, these efforts can be largely categorized as modifications of either timing or functional behaviours.

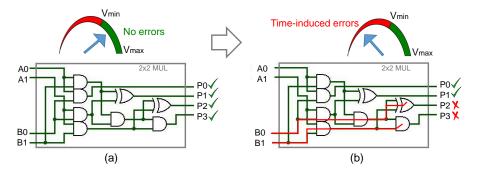

Firstly, the timing behaviour of multiplier design can be altered using aggressive supply voltage scaling or over-clocking techniques [79, 73, 113]. Operating below nominal voltage allows for reductions in energy consumption at the cost of time-induced errors. The bounds of these errors can be predicted, and so extra error-

Figure 2.7: Multi-dimensional taxonomy of approximate multiplier designs.

compensation circuits need to be incorporated [30, 44]. Fig. 2.8 demonstrates an example of subjecting VOS to sequential 2-bit multiplier circuit. After scaling the supply voltage below the nominal value, a number of paths fails to meet the delay constraints. However, the timing failures are typically caused by long carry chains, *i.e.*, impact the more significant bits of the final product (seeFig. 2.8-b). It is therefore necessary to quantify the impact of timing violation by modifying the conventional multiplier to allow for graceful degradation [113]. Subjecting VOS or over-clocking to arithmetic circuits without losing the accuracy of the output is still an open challenge (This challenge will be discussed further in Section 2.3.2).

Figure 2.8: An example of  $(2 \times 2)$  multiplier: (a) operating within safe voltage range; (b) lowering the supply voltage below its nominal value.

Secondly, functional modifications deal with logic reduction techniques and can be performed by relaxing the need for accurate Boolean equivalence of the specification and implementation. This is leveraged to achieve more energy-efficiency and to accelerate computations.

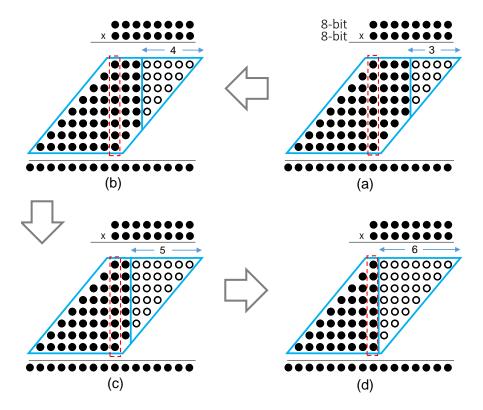

A common example of functional modifications of approximate multipliers is truncation of the least significant columns, such as when performing fixed-point [25] (*i.e.*, two n-bit input multiplicands producing an n-bit output) and floating-piont multiplication [131]. Truncating multiplier product terms allows for the

elimination of some of the least significant columns in the partial product matrix (PPM). Fig. 2.9 shows different degrees of truncation in the case of (8 × 8) approximate multiplier. Truncated multiplication provides an efficient method for reducing the power dissipation and silicon area [25, 90, 118, 119, 60]. As more columns are eliminated, further energy reduction is achieved; however, errors increase very rapidly. Additionally, as the operand size increases, the relative reduction in energy and cell count also increase [104]. Note that, critical path will not be remarkably shortened unless the columns truncated exceed the critical column—which leads to a huge error (see Fig. 2.9). Therefore, there is an essential need to verifying the truncated multipliers and quantifying associated

Figure 2.9: Increasing the level of truncation from; (a) 3; (b) 4; (c) 5; and (d) 6 columns, translates into additional reductions in area and power; however, error is maximized and this method is not effective to reduce the critical column of the accumulation tree (highlighted in dotted rectangles).

errors. A number of heuristically inspired schemes exist in the literature and attempt to minimise the impact of error, such as average absolute error or mean square error. Another attempts to create faithfully rounded multipliers based on truncation [64] and analytic error bounds [25].

Modular re-design with low-complexity combinational logic is another effective technique [65, 71]. This allows for building larger energy-efficient multipliers using small approximate ones; however, the hierarchical organization of small approximate blocks will eventually propagate errors, which increase with the multiplier size. Fig. 2.10 describes the process of designing larger multipliers when using  $(2 \times 2)$  approximate multiplier as a building blocks. The increased input bit-width of the multiplier translates into higher size of accumulation tree leading to increased height of critical column. However, scalability is not simple and this method may not significantly reduce the critical path, also the hierarchical organization of small approximate blocks will eventually propagate errors which increase with the multiplier size (see Fig. 2.10).

Figure 2.10: Using  $(2 \times 2)$  approximate multiplier blocks to build larger energy-efficient multipliers [65].

Fig. 2.11 describes another attempt to design large efficient multiplier, constructed by small approximate and accurate ones, using recursive multiplication scheme [8]. The idea is to use the approximate multiplier blocks to produce the less significant bits of the product while the more significant bits are generated using accurate blocks. To reduce the latency of the accurate multiplier two ways have been applied; (i) applying the recursive scheme once more using smaller multiplier blocks, and (ii) adding carry-in prediction logic to reduce the carry chain through addition stage (see Fig. 2.11).

Figure 2.11: Different sizes of approximate and accurate multipliers are used to build large recursive multiplier for pipelined architecture [8]; the carry-in logic is used for the approximate partial product computation only  $(A_HB_L,A_LB_H,A_LB_L)$  and not for the accurate  $A_HB_H$ .