# Battery Charging System Incorporating an Equalisation Circuit for Electric Vehicles

Huaxia Zhan

A thesis submitted for the degree of Doctor of

Philosophy

May, 2019

School of Engineering

Newcastle University

United Kingdom

### Abstract

Hybrid electric vehicles (HEVs) and electric vehicles (EVs) are gaining in popularity mainly due to the fact that unlike combustion-powered vehicles, they do not pollute with greenhouse gases and toxic particles. Most HEVs and EVs are powered by lithium-ion battery packs which have high power density and longer cycle lives compared to other battery types. Each pack is made out of many battery cells in series connected and due to manufacturing tolerances and chemical processes in individual cells each cell has its own electric characteristics. In order to achieve a balanced voltage across all cells, a battery management system (BMS) must be employed to actively monitor and balance the cells voltage. On-board battery chargers are installed in HEVs/EVs to charge the lithium-ion battery pack from the grid. This charger converts AC grid voltage into a controllable DC output voltage, but it adds weight to the vehicle, reducing the overall efficiency of an HEV/EV and also increasing its cost.

The aim of researches in multi-functional power electronics is to design systems which perform several different functions at the same time. These systems promise cost and weight reductions since only one circuit is used to conduct different functions. An example is the electric drive in an HEV/EV. On one hand, it propels the car forward when driving, while on the other hand the battery can be charged via a modified electric motor and inverter topology. Thus, no additional on-board charger is required.

This thesis describes a new multi-functional circuit for HEVs/EVs which combines the functions of voltage equalisation with grid charging. Compared to a drive system, the proposed circuit does not rely on an electric motor to charge the battery. Various battery chargers and equalisation circuits are first compared. Then, the design of the proposed circuit is described and simulation results are presented for charging and voltage balancing. An experimental test rig was built and practical results have been captured and compared with simulation results for validation. The advantages and disadvantages of the proposed circuit are discussed at the end of the thesis.

**Keywords**- Multi-functional system, Battery charging, Voltage equalisation, Lithiumion battery.

### Acknowledgement

Working towards this point over the past four years has been an amazing experience for me. I've learned and gained more than I ever thought I could. Here I would like to say thanks to a few people without whom I would never made it here.

First and Foremost, I would like to express my deep thanks and sincere gratitude to my supervisors, Prof. Volker Pickert, and Dr. Simon Lambert. I am very grateful for their guidance and supports and encouragements to me about this work and more. Also, their expertise, patience, and enthusiasm have inspired me a lot in my future pursuits.

I had the good fortune to undertake my research in the UG lab with lovely people in EP group. I am grateful for all the supports I've received from academics and technical staff including electric and mechanical workshop teams.

I would like to express my appreciation to Dr. Haimeng Wu, Dr. Bing Ji for their valuable advice and assistance during my study. I am also grateful to Xiang Lu, Xu Deng, Boru Jia, Weichi Zhang, and all lovely friends and their families, for the company and all the wonderful memories in Newcastle.

My most profound thanks is to my parents, Xuedao Zhan and Huiping Li, for their full understanding and supports during my education in UK. Undertaking a PhD is a lot of work not only for me but also for them. The hard work and sacrifices of my parents made it possible for me to be here. For their great emotional and financial support, I am eternally grateful.

### **Table of Contents**

| Abst | rac   | t     | i                                                    |

|------|-------|-------|------------------------------------------------------|

| Ackr | างพ   | ledg  | ementii                                              |

| Tabl | e of  | Co    | ntentsiii                                            |

| List | of F  | igur  | esvi                                                 |

| List | of T  | able  | sxii                                                 |

| Sym  | bol   | 3     | xiii                                                 |

| Abb  | revi  | atior | ۱۶XV                                                 |

| Cha  | pter  | l In  | troduction1                                          |

| 1.   | 1     | Bac   | kground1                                             |

| 1.   | 2     | Batt  | tery systems in EVs2                                 |

| 1.   | 3     | Volt  | age equalisation circuits3                           |

| 1.   | 4     | Pre   | vious work on multi-functional design in EVs4        |

| 1.   | 5     | Obj   | ectives6                                             |

| 1.   | 6     | Cor   | tribution to knowledge7                              |

| 1.   | 7     | The   | sis overview8                                        |

| Cha  | pter  | II C  | harging and Equalisation for Lithium-ion Batteries   |

| 2.   | -     |       | arging strategies for lithium-ion batteries10        |

| 2.   | 2     |       | Battery chargers                                     |

|      | 2.2.1 |       | Charger power levels and infrastructure              |

|      | 2.2.2 |       | Power flow in EV chargers                            |

|      | 2.2.3 |       | Structure of EV charging system                      |

|      | 2.2.4 | ŀ     | Power factor correction (PFC) converters             |

| 2.   | 3     | Volt  | age equalisation for battery packs17                 |

|      | 2.3.1 | _     | Unbalanced cells voltage                             |

|      | 2.3.2 |       | Necessity of equalisation circuits for battery packs |

| 2.   |       |       | erview of voltage equalisation circuits20            |

| 2.4.2   | 1 Energy flow path                                                          | 21         |

|---------|-----------------------------------------------------------------------------|------------|

| 2.4.2   | 2 Energy transfer sequence                                                  | 22         |

| 2.4.3   | 3 Energy transfer mode                                                      | 22         |

| 2.5     | Description of existing schemes                                             |            |

| 2.5.1   | 1 Switched capacitor equalisation scheme                                    | 24         |

| 2.5.2   | 2 Flying capacitor equalisation scheme                                      | 25         |

| 2.5.3   | 3 Buck-boost converter equalisation scheme                                  | 26         |

| 2.5.4   | 4 Cuk converter equalisation scheme                                         | 28         |

| 2.5.5   | 5 Multi-secondary winding transformer equalisation scheme                   |            |

| 2.5.6   | 6 Multi-primary winding transformer equalisation scheme                     | 32         |

| 2.5.7   | 7 Switched transformer equalisation scheme                                  | 33         |

| 2.6     | Summary                                                                     |            |

| Chapter | <sup>r</sup> III Development of Battery Charging System Incorporating an Eq | ualisation |

| Circuit |                                                                             |            |

| 3.1     | Design motivation                                                           |            |

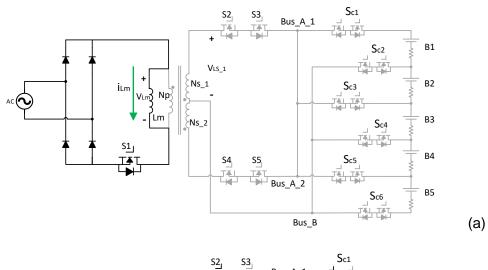

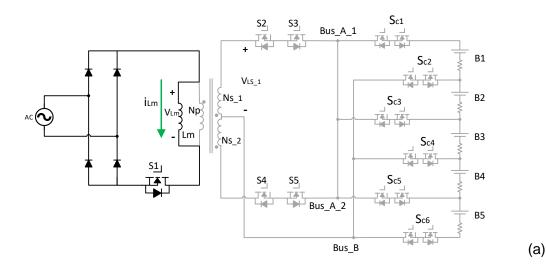

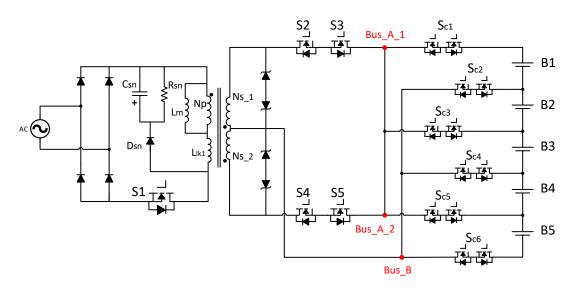

| 3.2     | Proposed circuit topology                                                   |            |

| 3.2.1   | 1 Rectifier                                                                 |            |

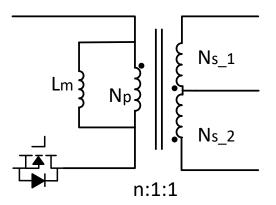

| 3.2.2   | 2 Isolated converter                                                        | 40         |

| 3.2.3   | 3 Winding selector                                                          | 41         |

| 3.2.4   | 4 Cell selector                                                             | 43         |

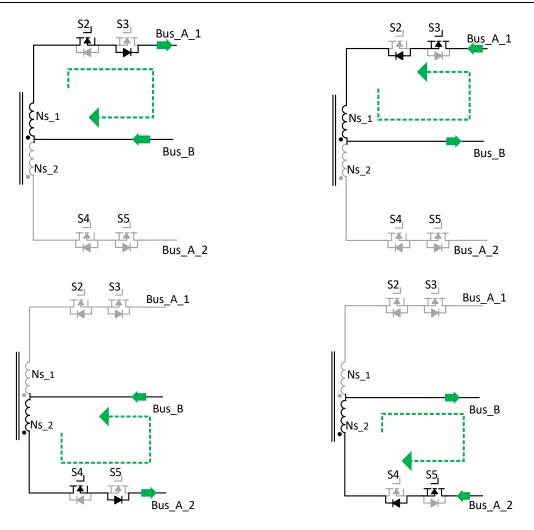

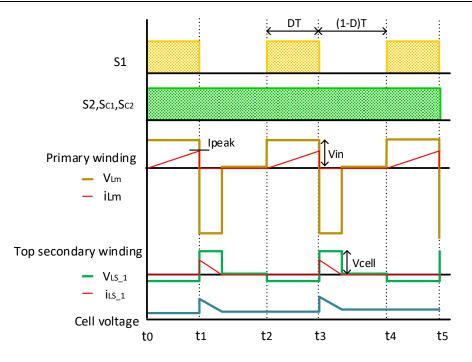

| 3.3     | Operating principles of the proposed circuit                                |            |

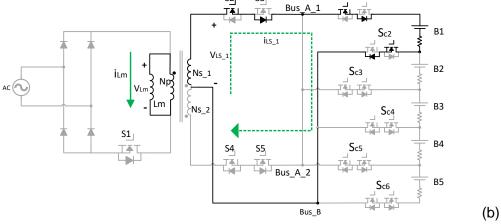

| 3.3.1   | 1 Mode 1: grid charging for odd numbered cells                              | 47         |

| 3.3.2   | 2 Mode 2: grid charging for even numbered cells                             | 51         |

| 3.3.3   | 3 Mode 3: equalisation from odd cells to odd cells                          | 53         |

| 3.3.4   | 4 Mode 4: equalisation from even cells to even cells                        |            |

| 3.3.5   | 5 Mode 5: equalisation between odd cells and even cells                     | 61         |

| 3.4     | RCD snubber circuit design for flyback converter                            | 65         |

| 3.5     | Development of the simulation model                                         | 69         |

| 3.6     | Verification of simulations under open loop control                         | 72         |

| 3.6.2   | 1 Simulation of grid charging of battery cells                              | 72         |

| 3.6.2   | 2 Simulations of battery voltage equalisation                               | 74         |

| 3.7     | Summary                                                                     | 80         |

| Chapter | VIV PFC & CC-CV Controller                                                  |            |

| 4.1     | Power factor (PF)                                       |     |

|---------|---------------------------------------------------------|-----|

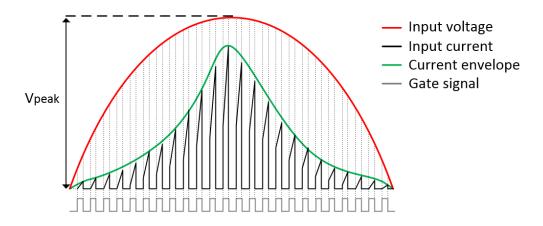

| 4.2     | PFC control for the proposed circuit                    | 85  |

| 4.2.    | 1 PFC control circuit                                   | 85  |

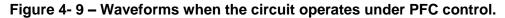

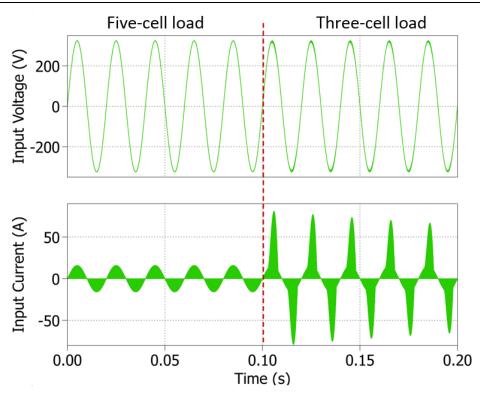

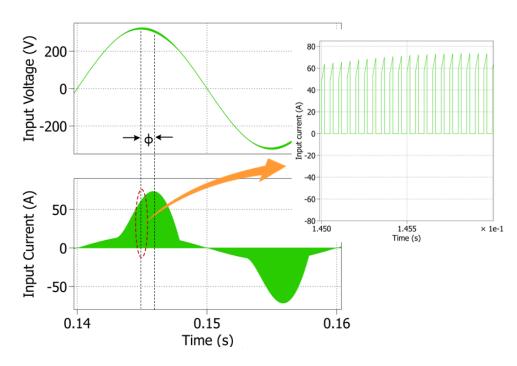

| 4.2.2   | 2 Circuit simulation with PFC controller                | 89  |

| 4.3     | PFC and CC-CV control                                   | 94  |

| 4.4     | Summary                                                 | 101 |

| Chapte  | r V Experimental Implementation, Results and Discussion | 103 |

| 5.1 D   | esign and implementation of test system                 | 103 |

| 5.1.    | 1 Hardware implementation                               | 103 |

| 5.1.2   | 2 Software implementation                               | 109 |

| 5.2 E   | xperimental results                                     | 112 |

| 5.2.    | 1 Battery charging                                      | 112 |

| 5.2.2   | 2 Equalisation B1-B3                                    | 120 |

| 5.2.3   | 3 Equalisation B1-B2                                    | 125 |

| 5.3 S   | ummary                                                  | 128 |

| Chapte  | r VI Conclusion and Future Work                         | 130 |

| Referer | 1ce                                                     | 134 |

| Append  | lix A                                                   | 142 |

| Append  | lix B                                                   | 148 |

| Append  | lix C                                                   |     |

## List of Figures

| Figure 1-1 – Diagram of a typical battery system in an EV.                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1- 2 – Photographs of: (a) a damaged lithium-ion battery; (b) a damaged EV caused by battery failure                         |

| Figure 1-3 – Bidirectional charger topology [26]                                                                                    |

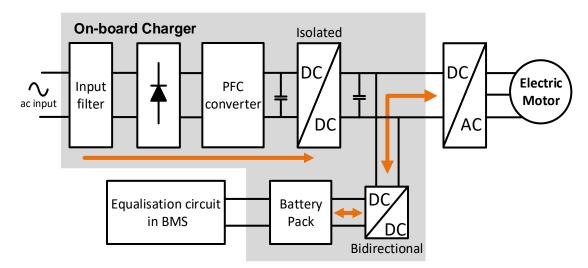

| Figure 1-4 – Non-dissipative battery charger equalizer topology [28]                                                                |

| Figure 2-1 – CC-CV charging method for battery cells                                                                                |

| Figure 2-2 – Electric vehicle supply equipment (EVSE) for three levels of chargers.                                                 |

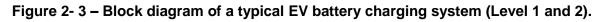

| Figure 2- 3 – Block diagram of a typical EV battery charging system (Level 1 and 2).                                                |

| Figure 2-4 – Typical Levels 1 and 2 charging circuit for an on-board EV charger 16                                                  |

| Figure 2- 5 – Typical two-stage boost PFC converter                                                                                 |

| Figure 2-6 – Principles of an isolated single-stage PFC converter                                                                   |

| Figure 2-7 – An example of degradation curve for a Lithium-ion battery (3.2V,1100mAh)                                               |

| [16]                                                                                                                                |

| Figure 2-8 – (a) Decreasing capacity with cycles and temperature; (b) increasing internal resistance with time and temperature [58] |

| Figure 2-9 – Dissipative voltage equalisation circuit                                                                               |

| Figure 2-10 – Energy flow paths: (a) neighbour flow; (b) global flow                                                                |

| Figure 2- 11 – Energy transfer modes: (a) one-to-one equalisation; (b) one-to-all equalisation; (c) all-to-all equalisation         |

| Figure 2-12 – Taxonomy of equalisation circuit categories                                                                           |

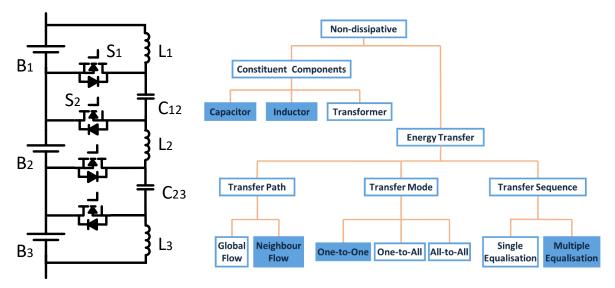

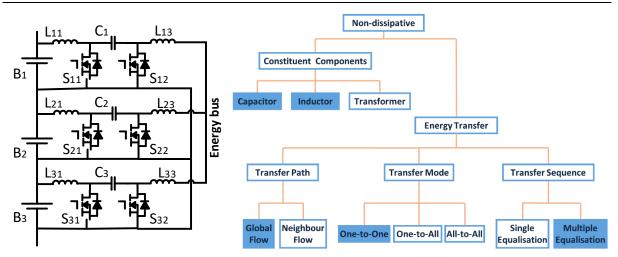

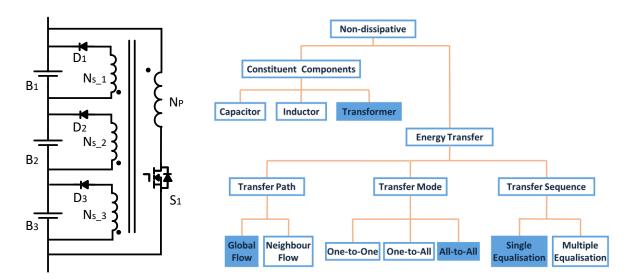

| Figure 2-13 – Switched capacitor equalisation circuit and taxonomic category 24                                                     |

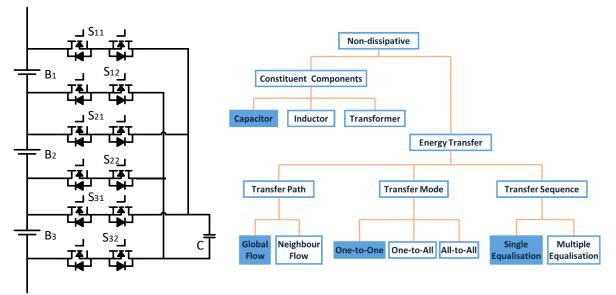

| Figure 2-14 – Flying capacitor equalisation circuit and taxonomic category 25                                                       |

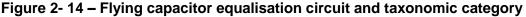

| Figure 2-15 – Buck-boost converter equalisation circuit and taxonomic category 26                                                   |

| Figure 2-16 – Successive buck-boost converter equalisation circuit and taxonomic                                                    |

| category                                                                                                                            |

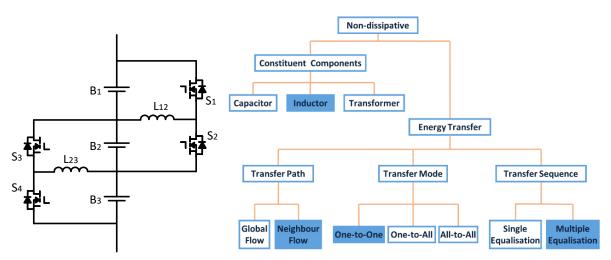

| Figure 2-17 – Cuk converter equalisation circuit and taxonomic category29                                                      |

|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-18 – Bus-based isolated Cuk converter equalisation circuit with taxonomic category                                    |

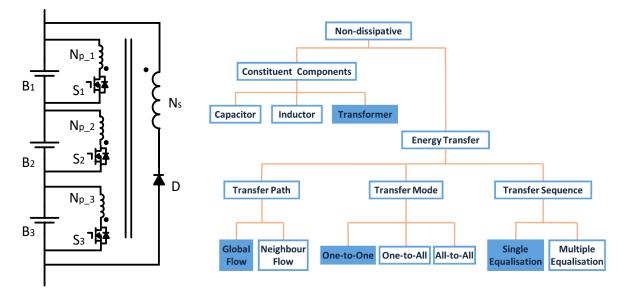

| Figure 2- 19 – Multi-secondary windings transformer equalisation scheme and taxonomic category                                 |

| Figure 2- 20 – Voltage equalisation with multi-secondary winding transformer circuit.                                          |

|                                                                                                                                |

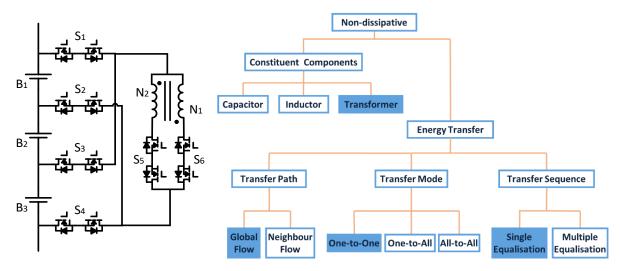

| Figure 2- 21 - Multi-primary windings transformer equalisation scheme and taxonomic category                                   |

| Figure 2-22 – Switched transformer equalisation scheme and taxonomic category. 34                                              |

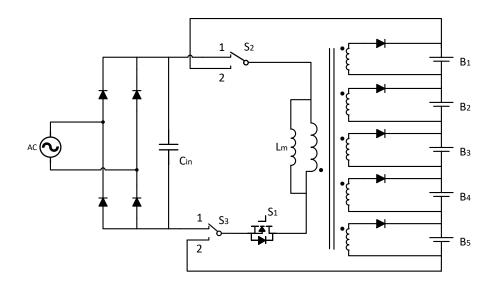

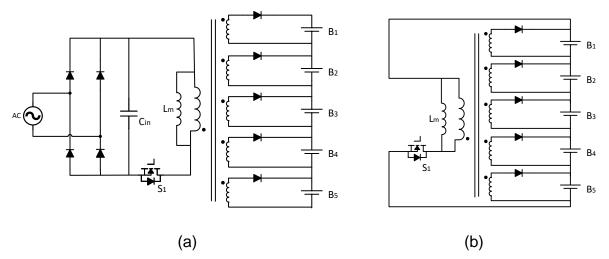

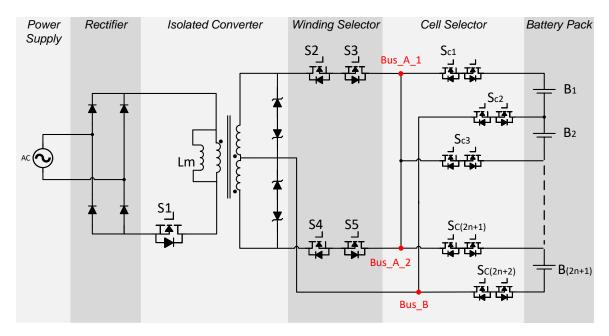

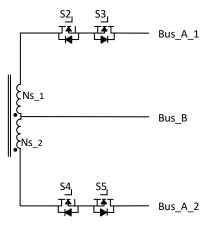

| Figure 3-1 – Principal circuit of a voltage balancing circuit based on multi-winding transformer with grid charging capability |

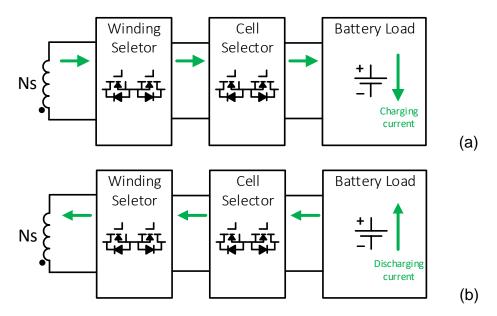

| Figure 3- 2 – Equivalent circuit of Figure 3-1 when operating for: (a) grid charging; (b) voltage balancing                    |

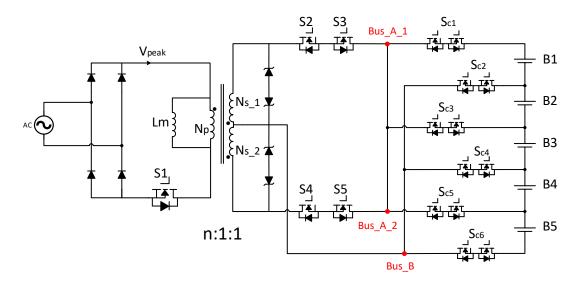

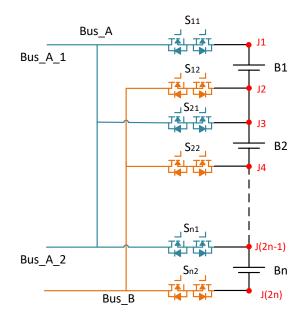

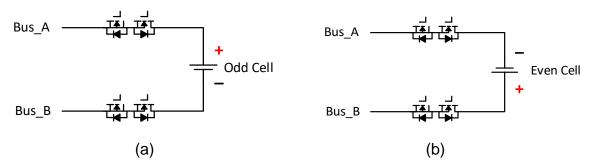

| Figure 3- 3 – Proposed multi-functional battery charger integrated with voltage equalisation in (2N+1) battery cells           |

| Figure 3- 4 – Proposed circuit with five cells                                                                                 |

| Figure 3- 5 – Schematic of transformer utilised in the proposed circuit40                                                      |

| Figure 3- 6 – Block diagrams of the circuit with current directions when battery cell is: (a) charging; (b) discharging41      |

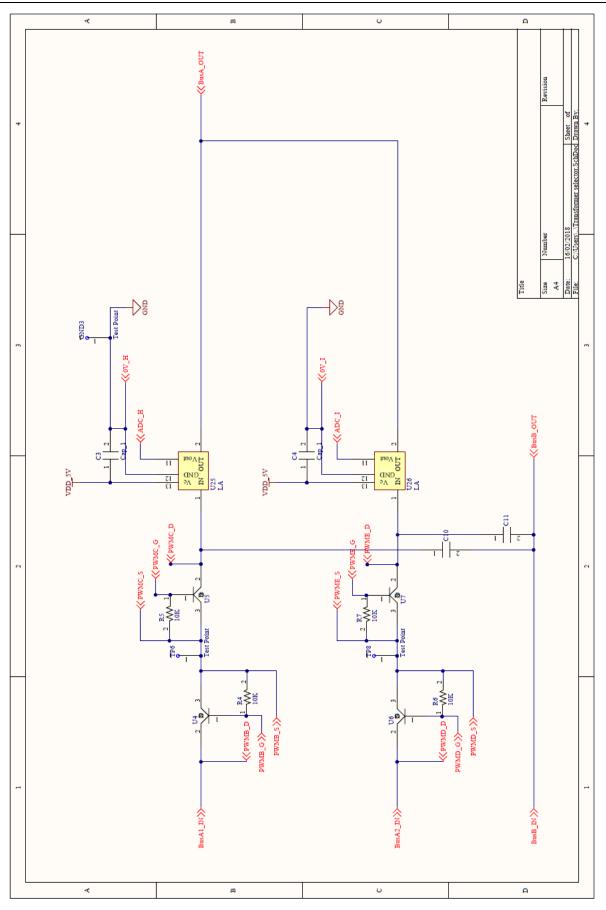

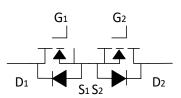

| Figure 3-7 – Secondary windings in the winding selector42                                                                      |

| Figure 3-8 – Bi-directional switch (gate, drain and source indicated)42                                                        |

| Figure 3-9 – Four current flow modes in the winding selector                                                                   |

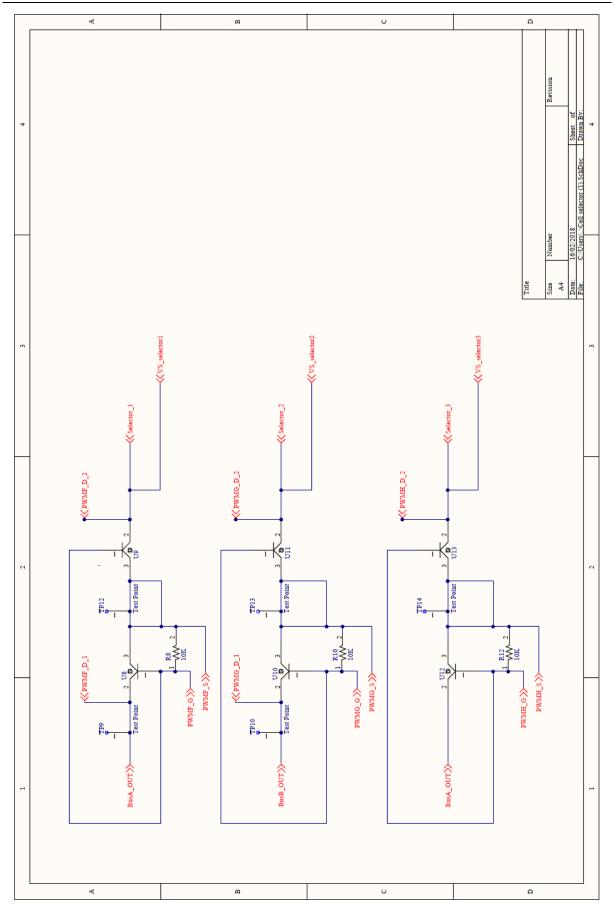

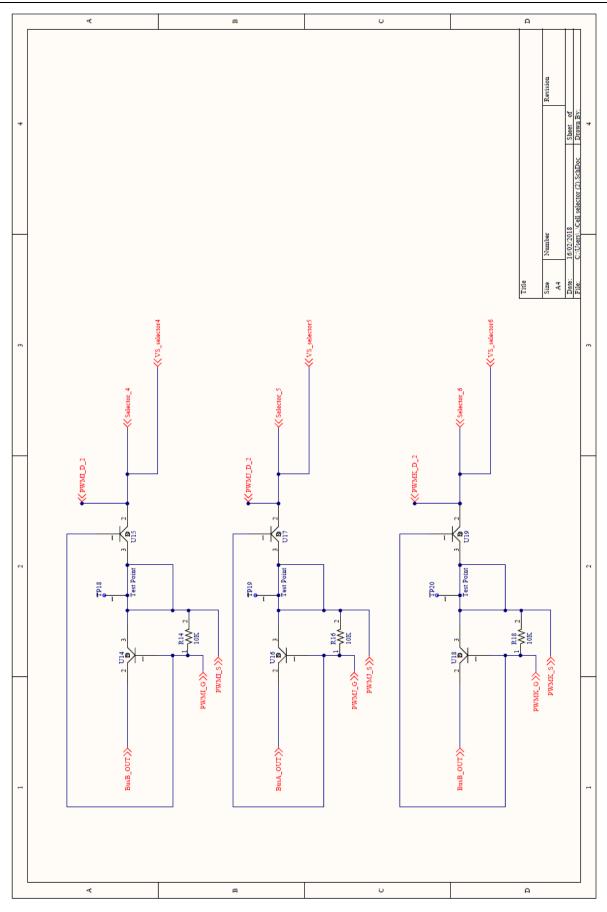

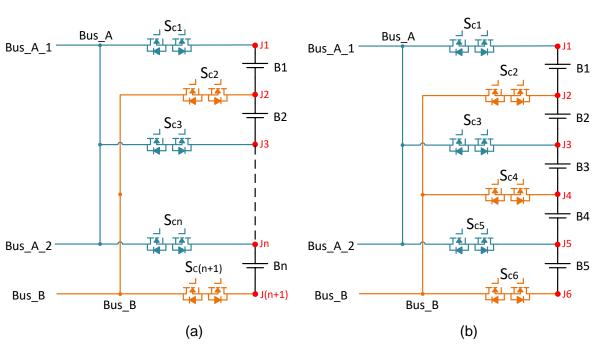

| Figure 3- 10 – Cell selector with N cells                                                                                      |

| Figure 3- 11 – Modified cell selector with: (a) N cells; (b) five cells45                                                      |

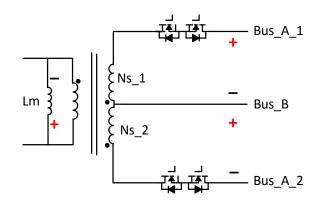

| Figure 3-12 – Polarity for transformer windings in the demagnetising period48                                                  |

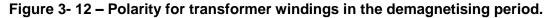

| Figure 3- 13 – Polarity of a cell connected to the winding selector for: (a) odd cell; (b) even cell                           |

| Figure 3- 14 – Equivalent circuits for charging B1 for: (a) magnetising period; (b) demagnetising period                |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 3-15 – Predicted waveforms for the circuit when charging B150                                                    |

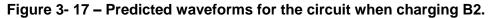

| Figure 3- 16 – Equivalent circuit for charging B2 for: (a) magnetising period; (b) demagnetising period                 |

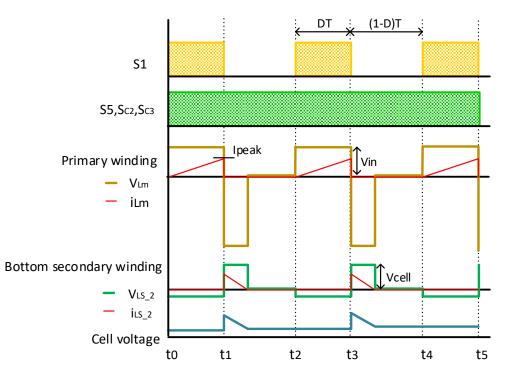

| Figure 3-17 – Predicted waveforms for the circuit when charging B2                                                      |

| Figure 3- 18 – Equivalent circuits for equalisation from B1 to B3 for: (a) magnetising period; (b) demagnetising period |

| Figure 3- 19 – Predicted waveforms for the circuit when equalisation from B1 to B3.                                     |

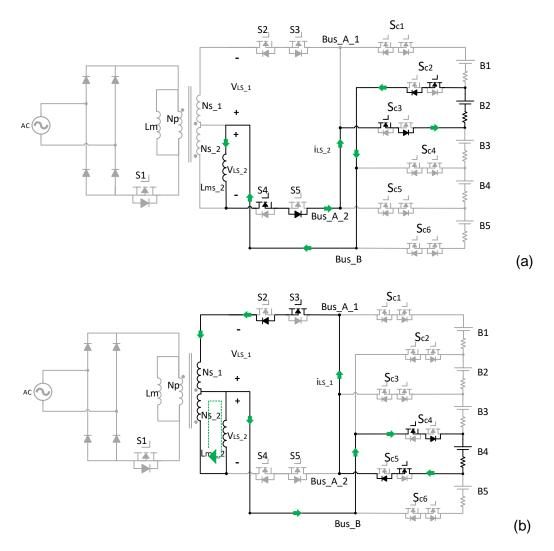

| Figure 3- 20 – Equivalent circuits for equalisation from B2 to B4 for: (a) magnetising period; (b) demagnetising period |

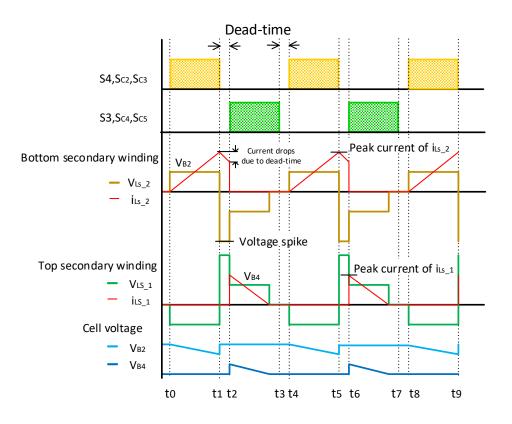

| Figure 3- 21 – Predicted waveforms for the circuit when equalisation from B2 to B4.                                     |

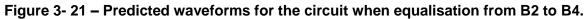

| Figure 3- 22 – Equivalent circuits for equalisation from B1 to B2 for: (a) magnetising period; (b) demagnetising period |

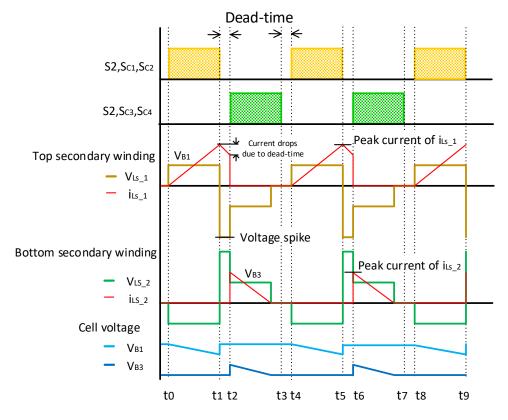

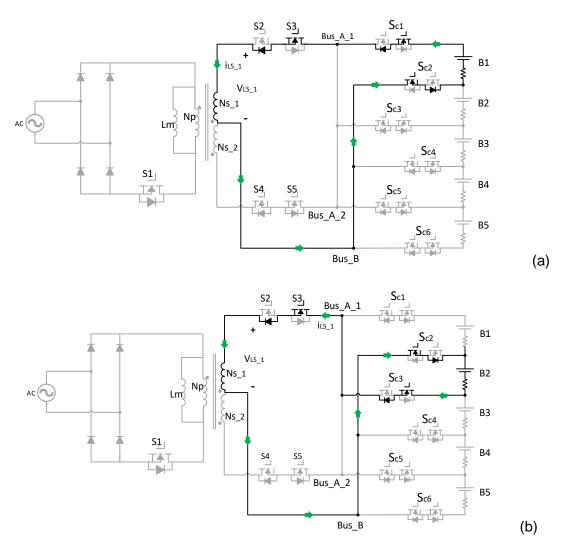

| Figure 3- 23 – Predicted waveforms for the circuit when equalisation from B1 to B2.                                     |

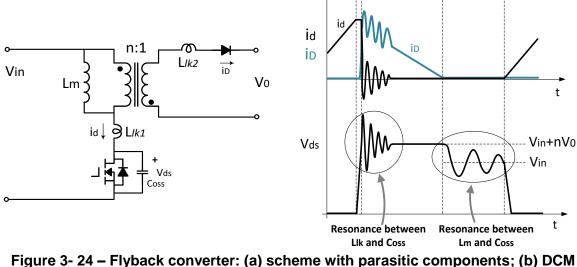

| Figure 3- 24 – Flyback converter: (a) scheme with parasitic components; (b) DCM operation                               |

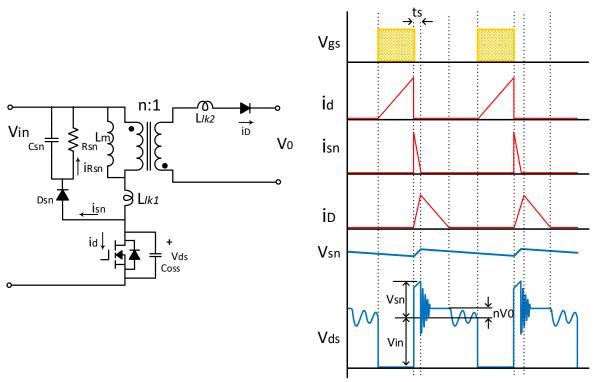

| Figure 3- 25 – Flyback converter assembled with RCD snubber: (a) scheme with parasitic components; (b) DCM operation    |

| Figure 3- 26 – Proposed battery charging and equalisation circuit enhanced with RCD snubber                             |

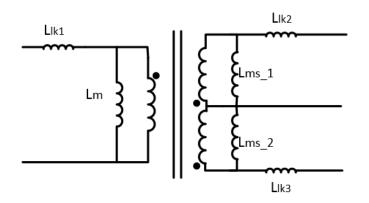

| Figure 3- 27 – The transformer model 69                                                                                 |

| Table 3- 7 – Parameters of the transformer model    70                                                                  |

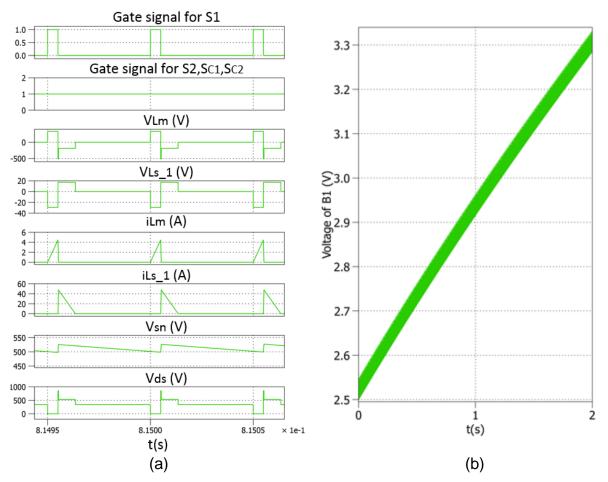

| Figure 3- 28 – Simulation waveforms for the proposed circuit when charging B172                                         |

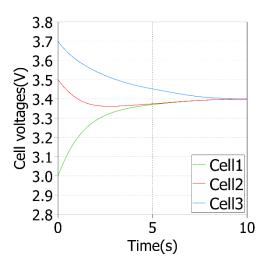

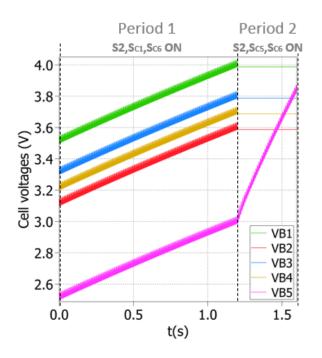

| Figure 3- 29 – Cell voltages for B1-B5 when charging five cells in two steps74                                          |

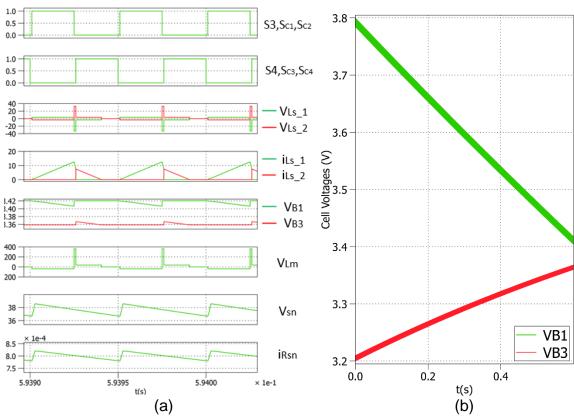

| Figure 3- 30 – Simulation waveforms for the proposed circuit when equalisation from B1 to B3                            |

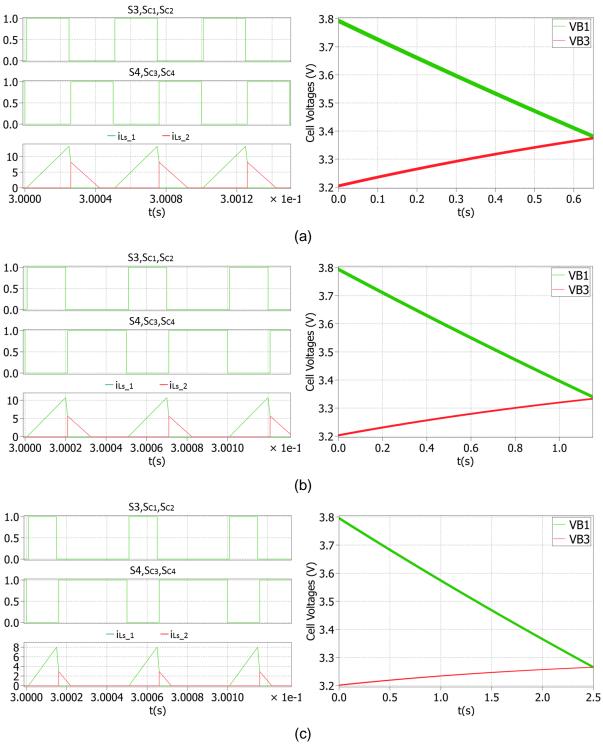

| Figure 3- 31 – Equalisation from B1 to B3 with different duty cycles: (a) D=0.5; (b) D=0.4; (c) D=0.3                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

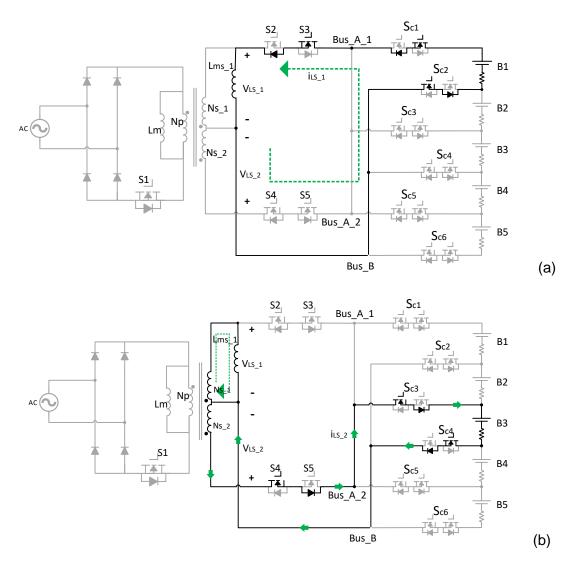

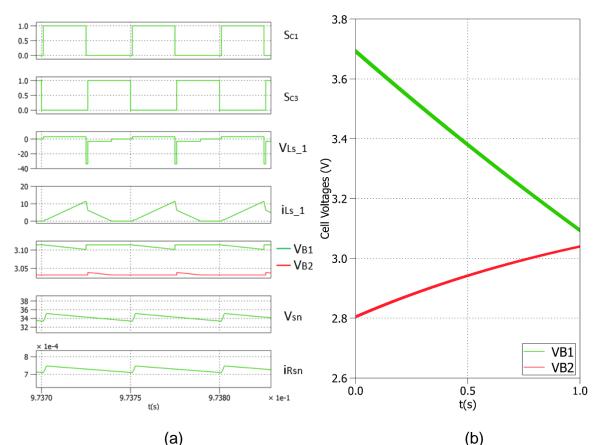

| Figure 3- 32 – Simulation waveforms for the proposed circuit when equalisation from B1 to B2                                                                  |

| Figure 3- 33 – Equalisation from B1 to B2 with different dead-times: (a) dead-time = 0.5us; (b) dead-time = 1us; (c) dead-time = 1.5us; (d) dead-time = 2us80 |

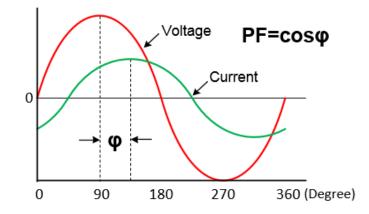

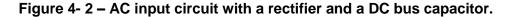

| Figure 4-1 – AC voltage and current with a lagging power factor in a linear system.                                                                           |

|                                                                                                                                                               |

| Figure 4- 2 – AC input circuit with a rectifier and a DC bus capacitor                                                                                        |

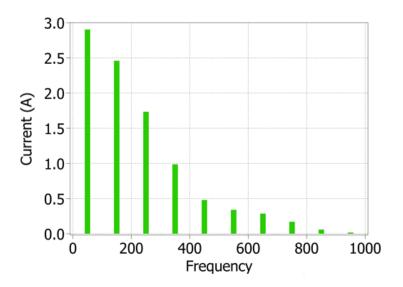

| Figure 4-3 – Input characteristics of an AC input circuit without PFC                                                                                         |

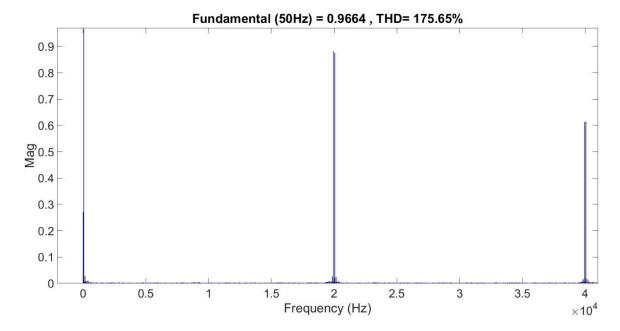

| Figure 4-4 – Harmonic content of the current waveform in figure 4-3                                                                                           |

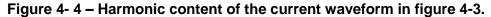

| Figure 4-5 – Proposed charging circuit with PFC85                                                                                                             |

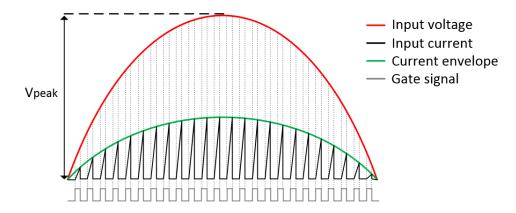

| Figure 4- 6 – Waveforms when the circuit operates at a constant D within the range in equation (4.10)                                                         |

|                                                                                                                                                               |

| Figure 4-7 – Waveforms when the circuit operates at a constant D exceeding the range in equation (4.10)                                                       |

|                                                                                                                                                               |

| in equation (4.10)                                                                                                                                            |

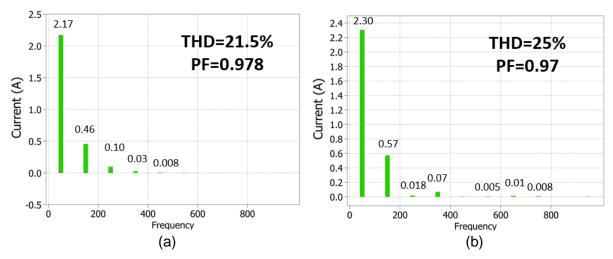

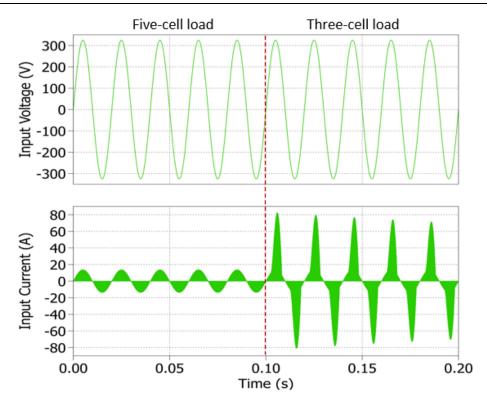

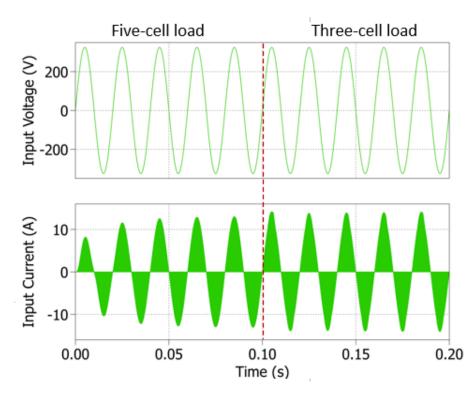

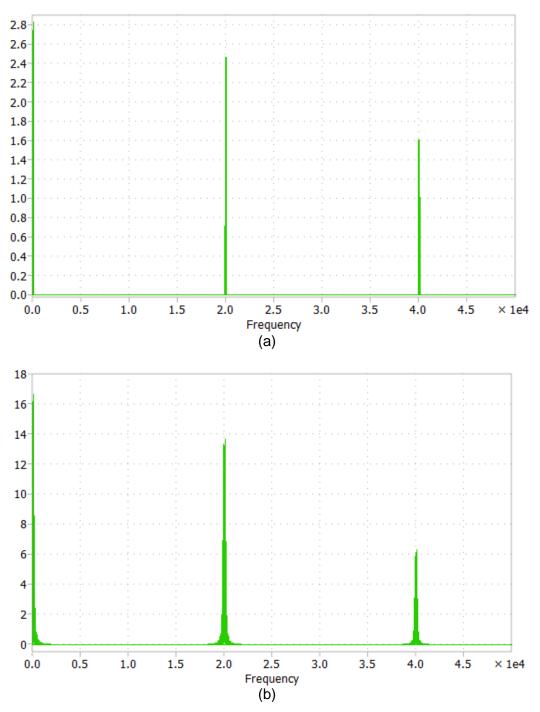

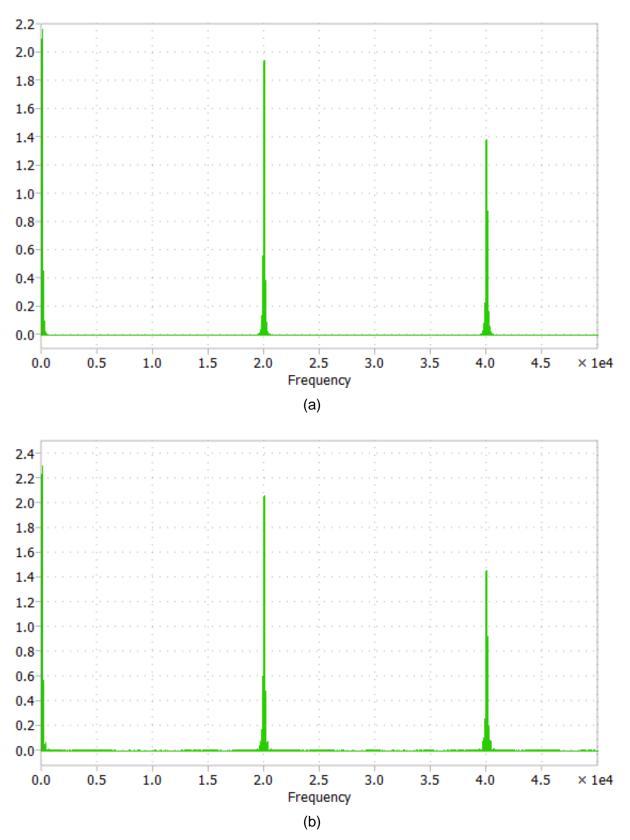

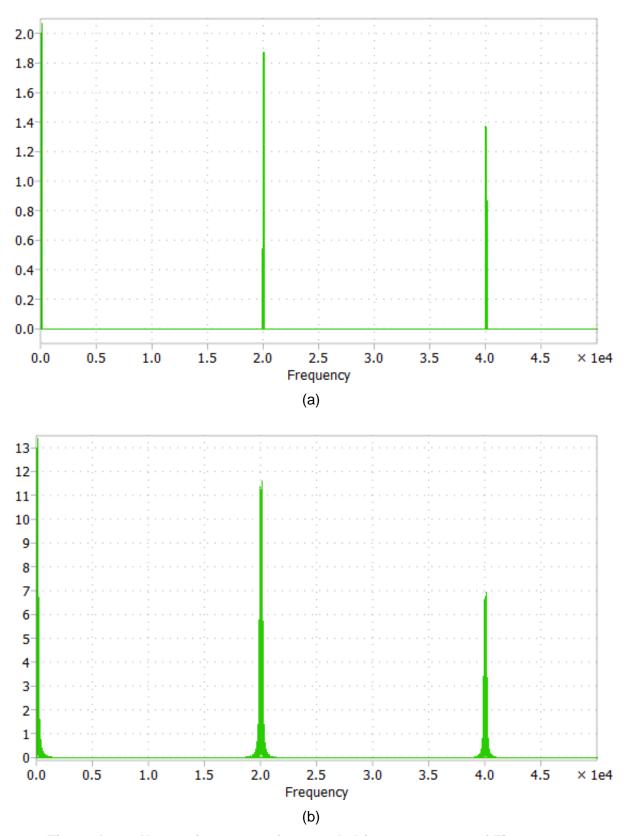

| Figure 4- 17 – Harmonic content of the current waveforms in Figure 4-16 with the load of: (a) 5 cells; (b) 3 cells                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

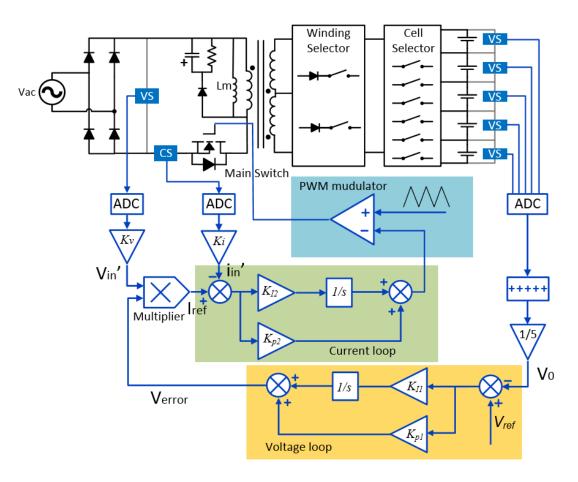

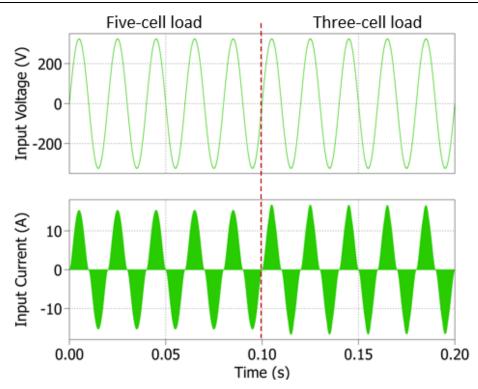

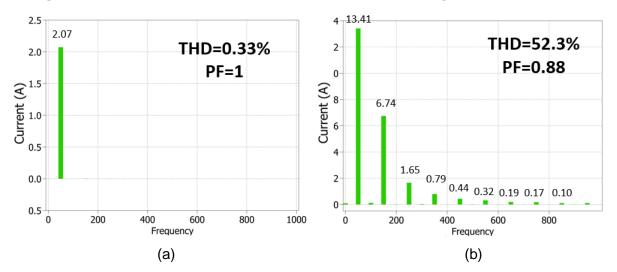

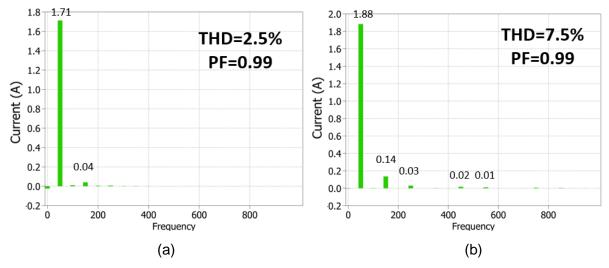

| Figure 4-18 – Simulation waveforms of input voltage and current PFC and CC control for two loads                                                    |

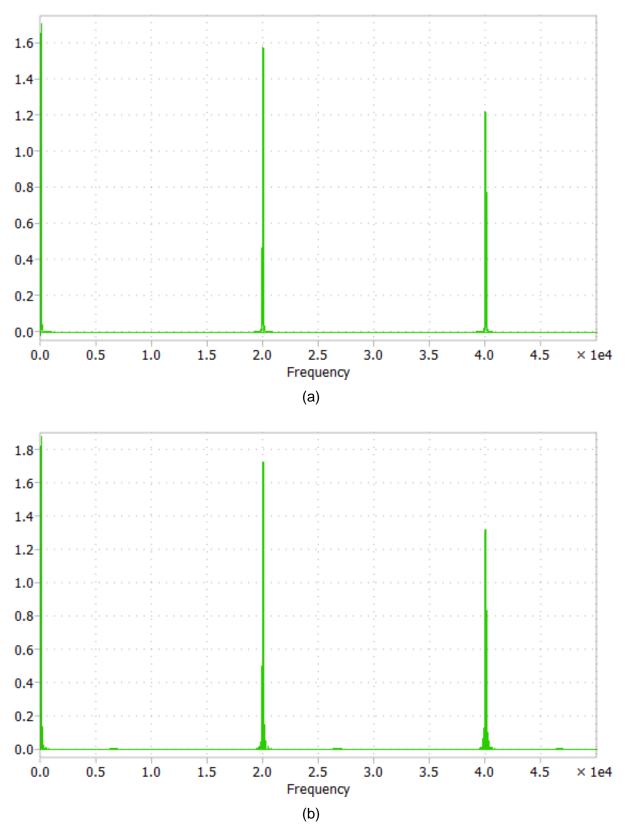

| Figure 4- 19 – Harmonic content of the current waveforms in Figure 4-18 with load of: (a) 5 cells; (b) 3 cells                                      |

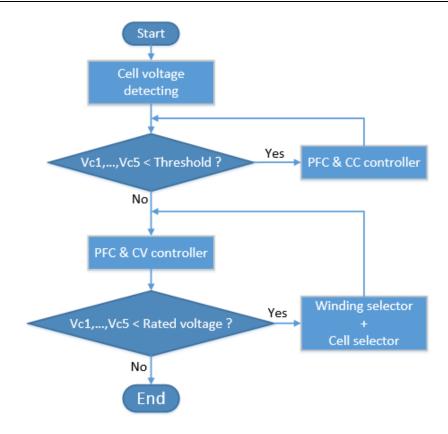

| Figure 4- 20 – Flow chart of proposed PFC and CC-CV controller                                                                                      |

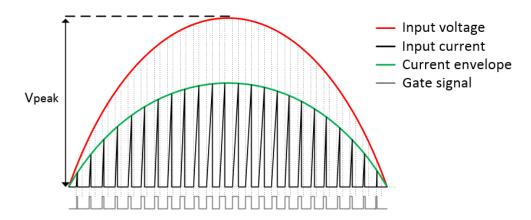

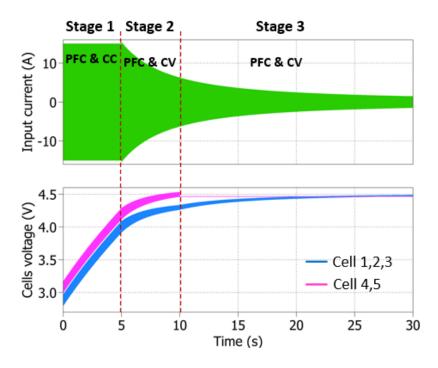

| Figure 4- 21 – Waveforms for PFC and CC-CV control by charging from CC to CV.                                                                       |

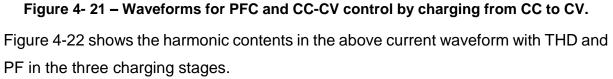

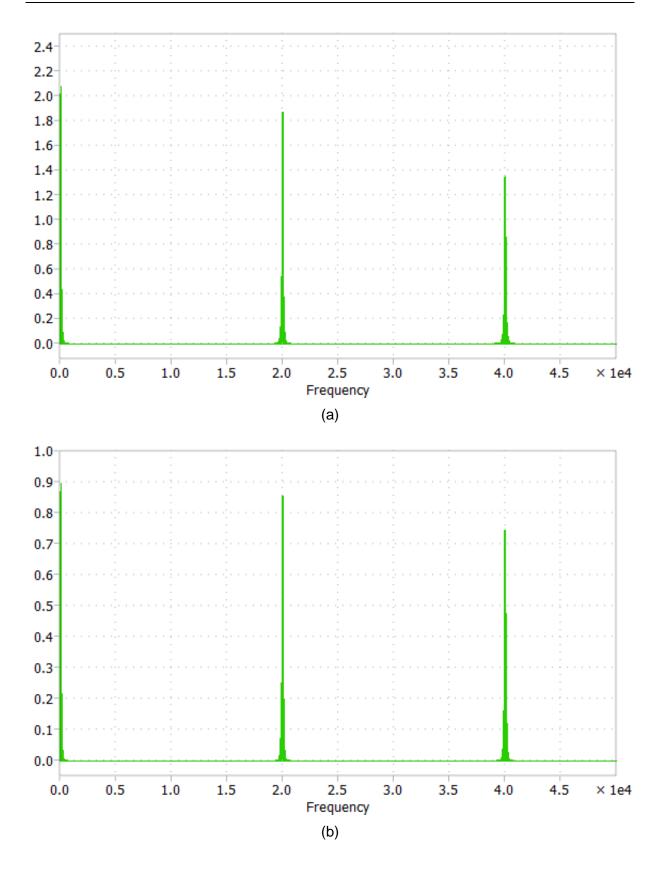

| Figure 4- 22 – Harmonic content of the current waveforms in Figure 4-21: (a) stage 1, $t = 2.5s$ ; (b) stage 2, $t = 7.5s$ ; (c) stage 3, $t = 15s$ |

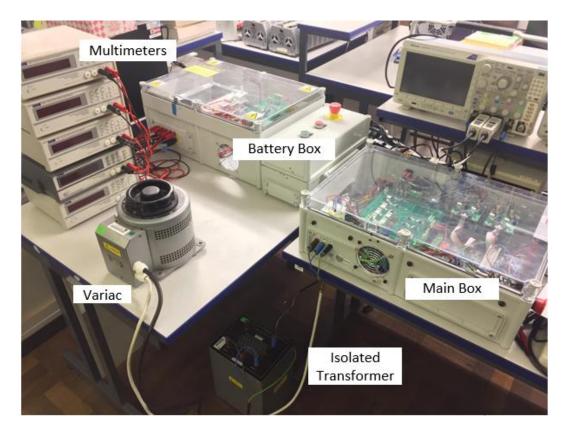

| Figure 5-1 – Photograph of the testing prototype                                                                                                    |

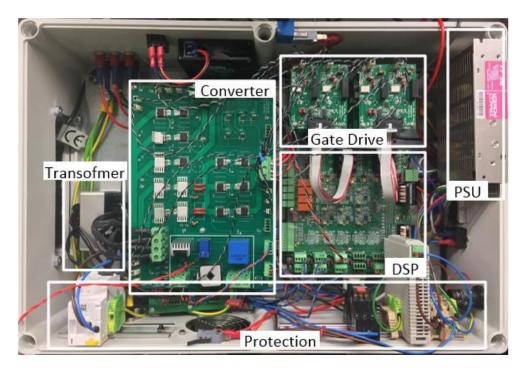

| Figure 5- 2 – Photograph of the main box 104                                                                                                        |

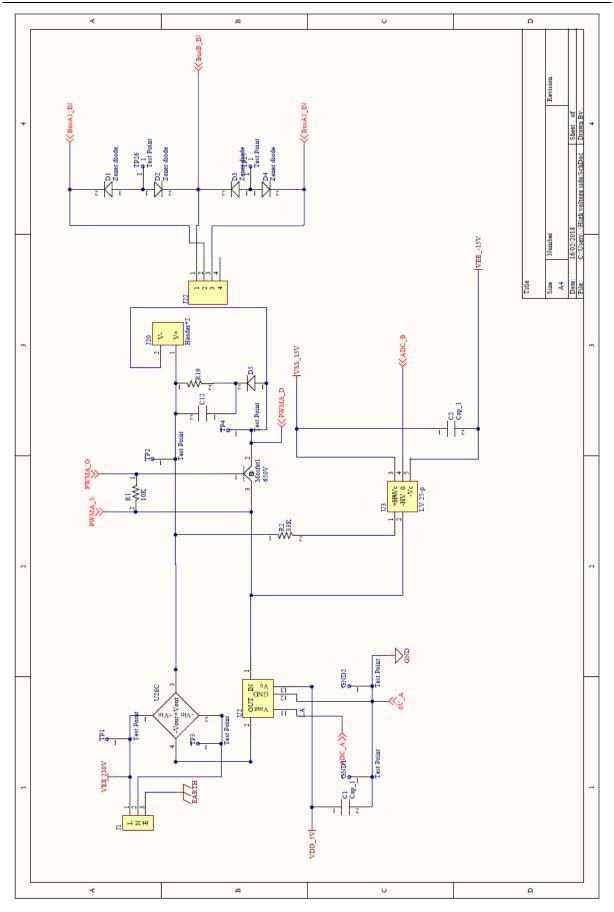

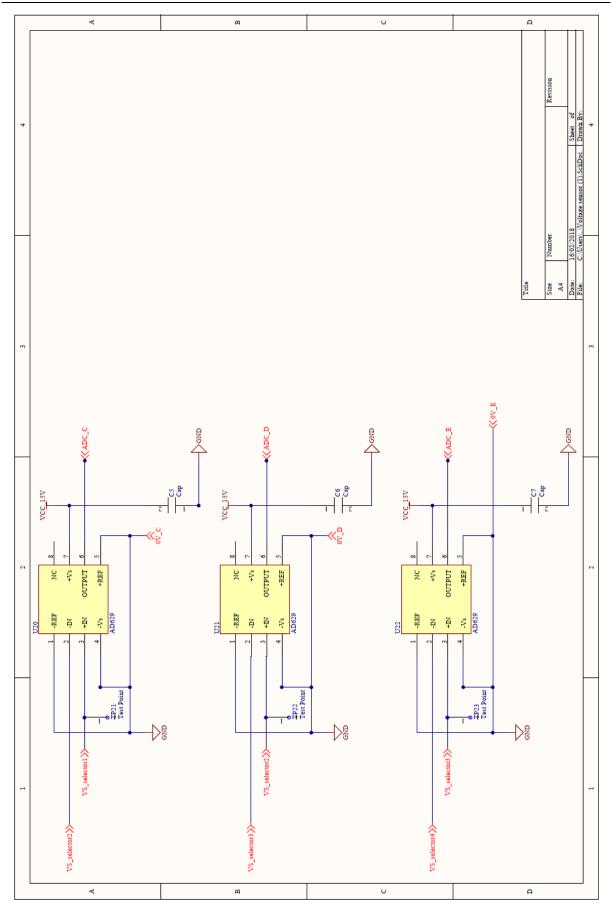

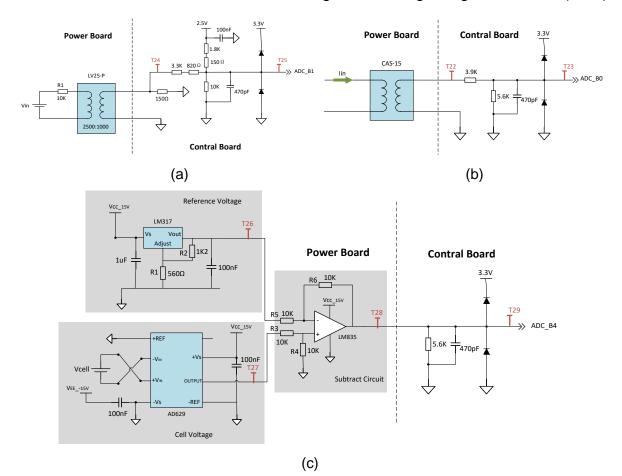

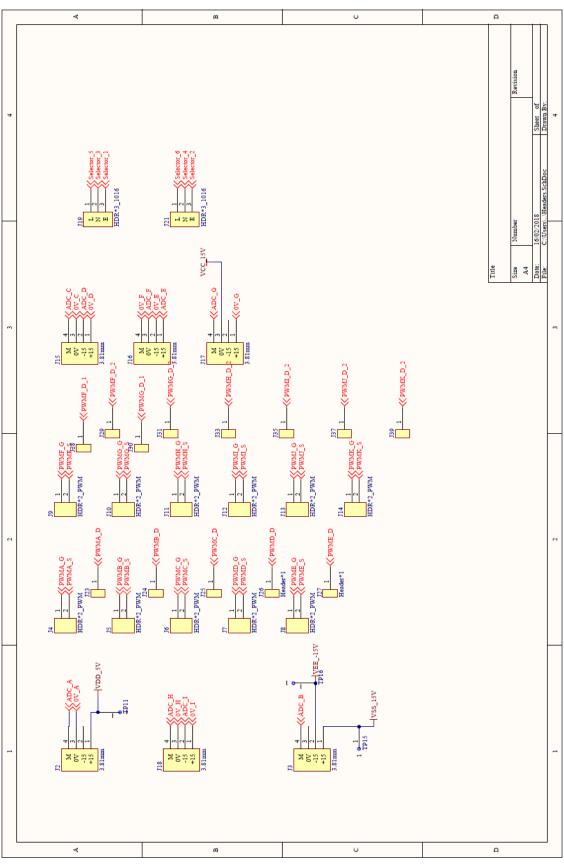

| Figure 5-3 – Signal regulation circuits for (a) Hall voltage sensor LV 25-P; (b) Hall current sensor CAS-6NP; (c) Differential amplifier AD629      |

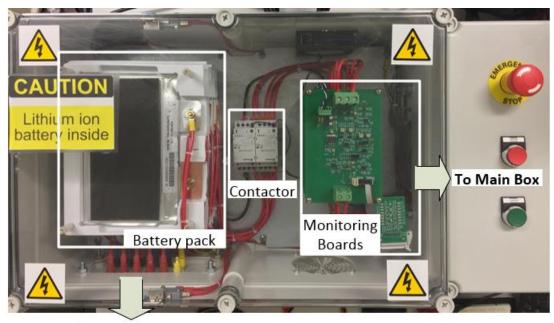

| Figure 5- 4 – Photograph of the battery box 107                                                                                                     |

| Figure 5-5 – Photograph of the research grade potentiostat system                                                                                   |

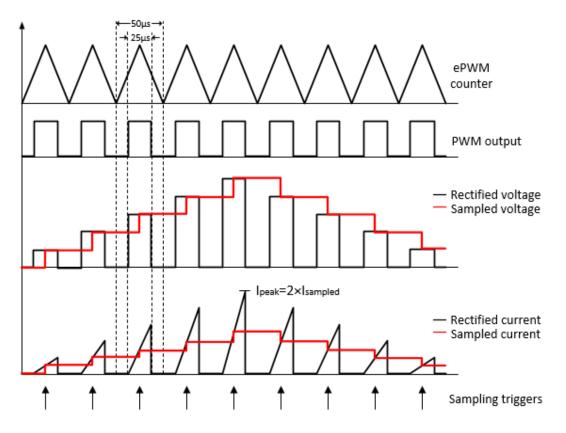

| Figure 5-6 – Diagram of the sampling of voltage and current signals in the ADC module.                                                              |

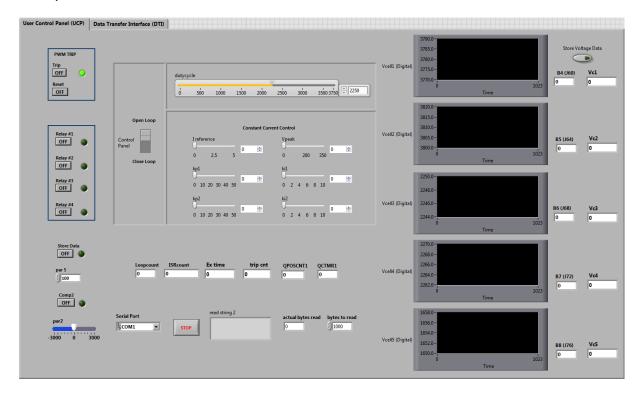

| Figure 5-7 – Part of the user's control panel in Labview.                                                                                           |

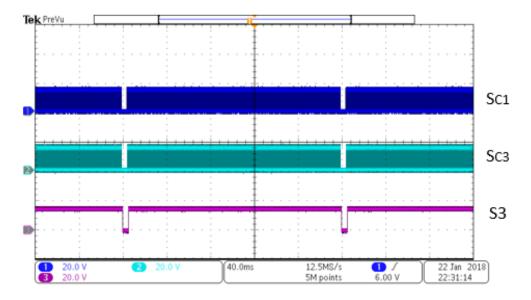

| Figure 5-8 – Switching signals for MOSFETs with pauses every 200ms 112                                                                              |

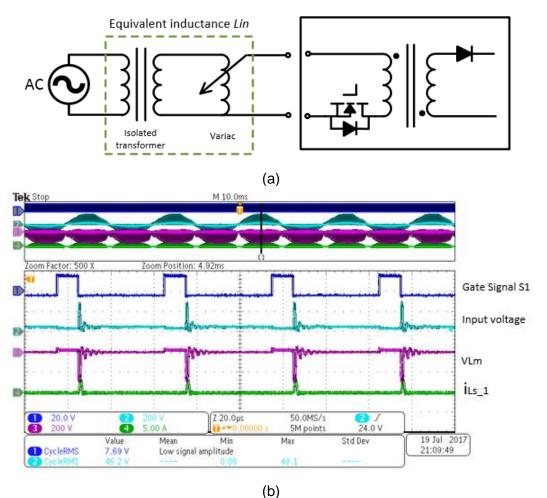

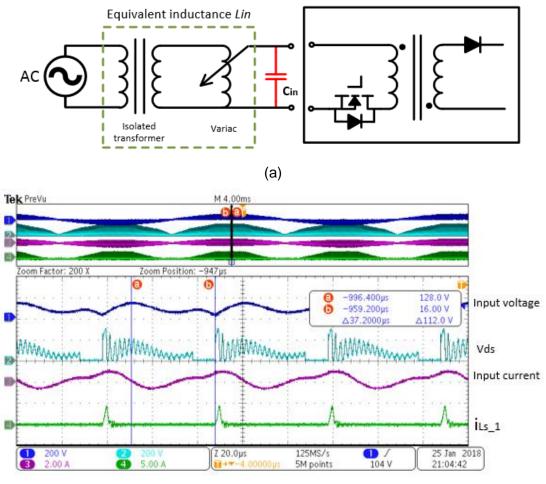

| Figure 5-9 – Isolated transformer and variac: (a) diagram of the input circuit; (b) waveforms with the input circuit                                |

| Figure 5- 10 – Input capacitor: (a) diagram of the input circuit; (b) waveforms with the input circuit                                              |

| Figure 5-11 – The AC power supply in the system                                                                                                     |

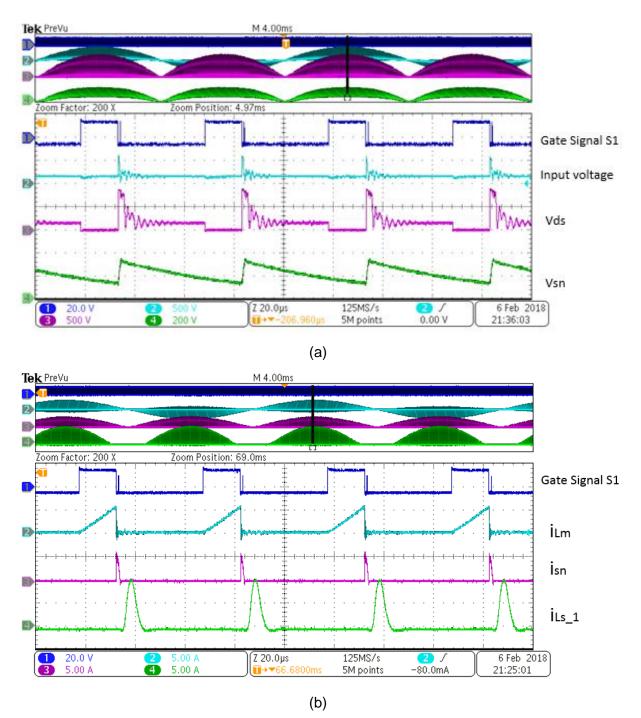

| Figure 5- 12 – Experimental results when charging five cells with fixed duty cycle: (a) voltage waveforms; (b) current waveforms                    |

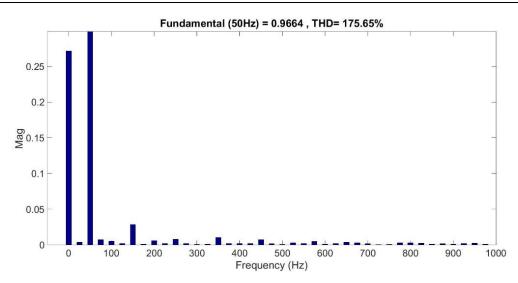

| Figure 5-13 – Harmonic contents in the input current in Figure 5-12                                                                                 |

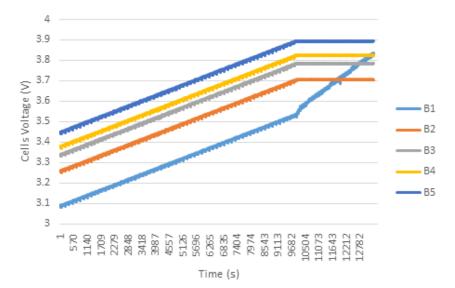

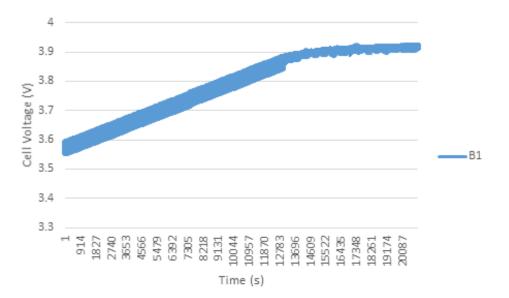

| Figure 5-14 – Cell voltages when charging B1-B5 in two steps117                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5- 15 – Voltage of B1 under CC-CV control                                                                                      |

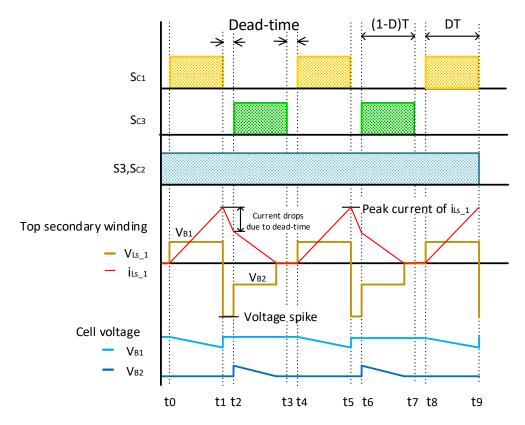

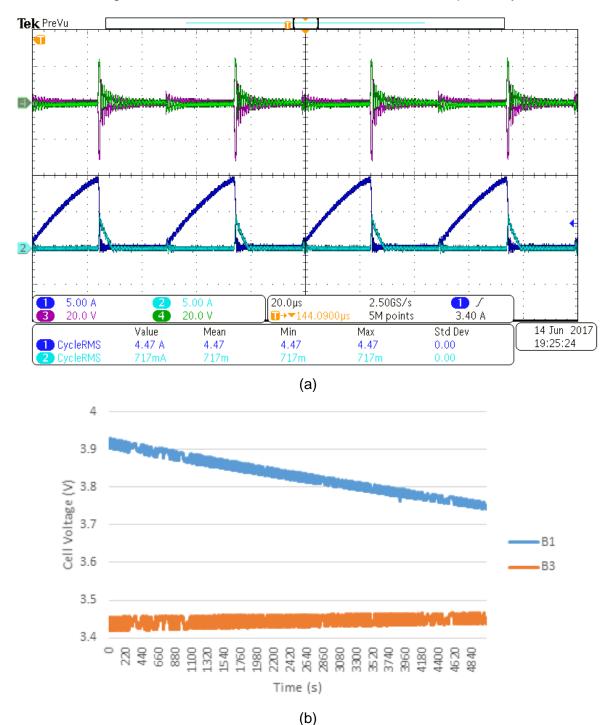

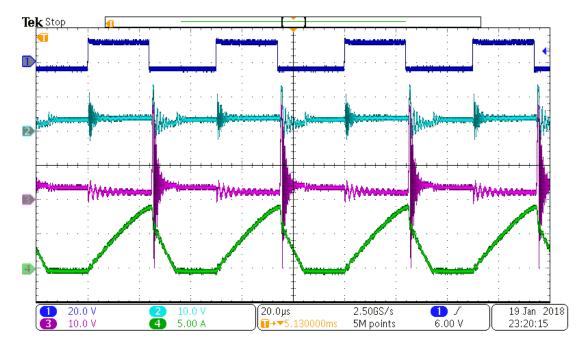

| Figure 5- 16 – Waveforms of equalisation from B1 to B3 @ Lms_1=4.2uH, f=20kHz: (a) voltage and current in windings; (b) cell voltages |

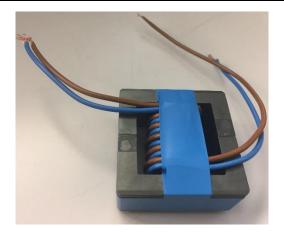

| Figure 5-17 – Photograph of the new transformer in the comparative test                                                               |

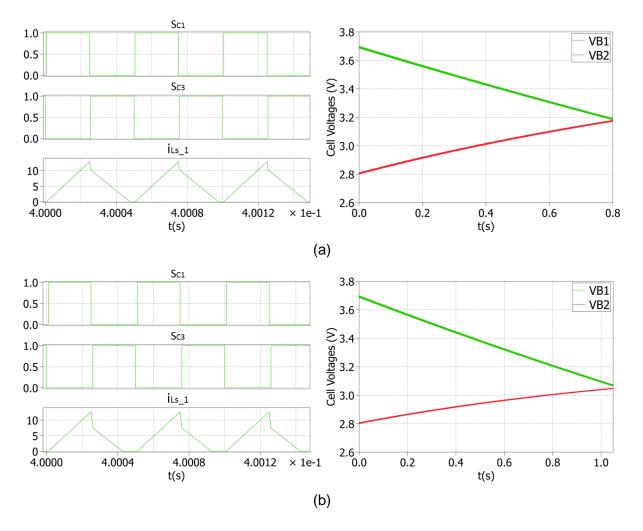

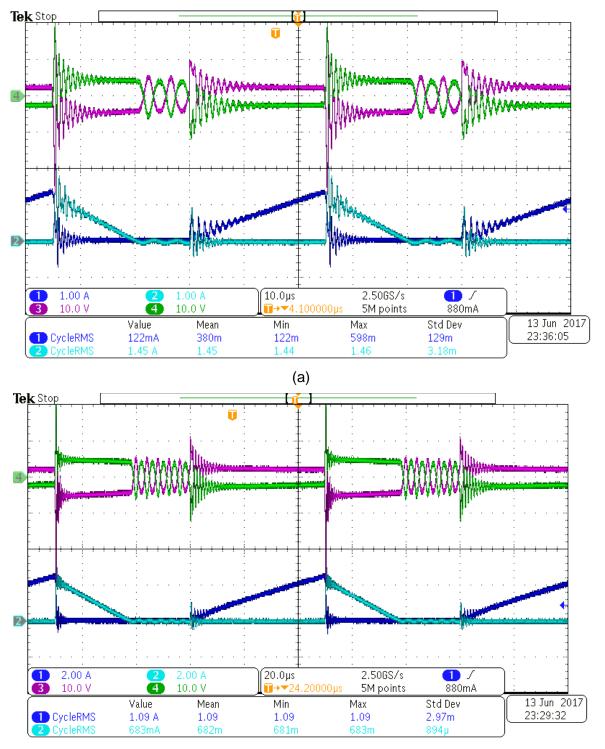

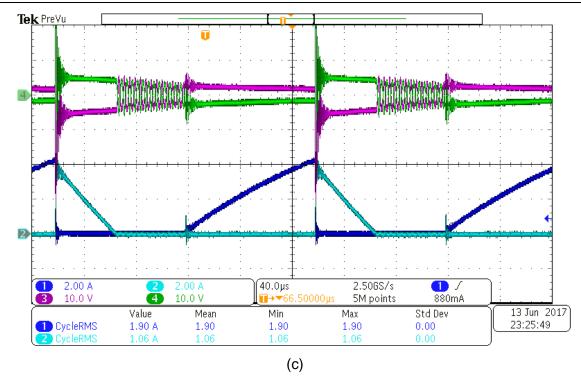

| Figure 5- 18 – Waveforms of equalisation from B1 to B3 @ Lms_1=54uH, (a) f=20kHz,<br>(b) f=10kHz, (c) f=5kHz                          |

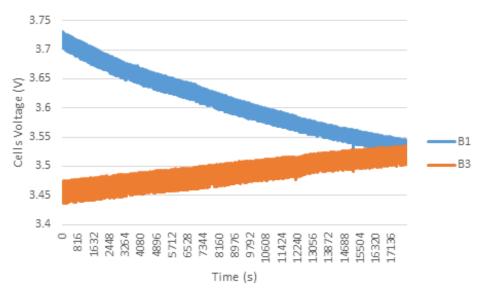

| Figure 5- 19 – Cell voltages in equalisation between B1 and B3 in comparative test.                                                   |

| Figure 5- 20 – Waveforms of equalisation from B1 to B2 @ Lms_1=4.2uH, f=20kHz, dead-time=1us                                          |

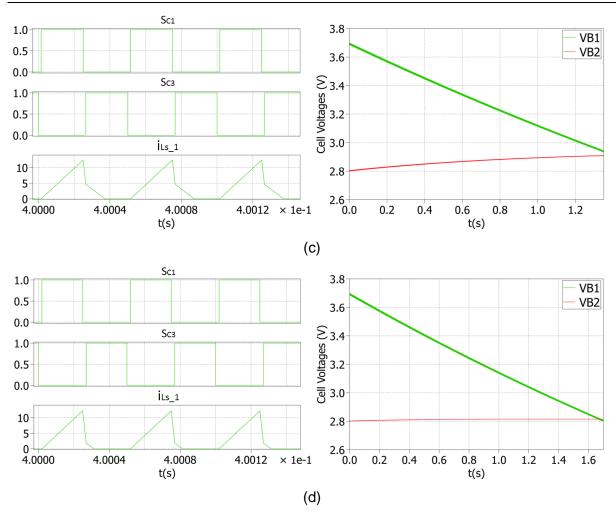

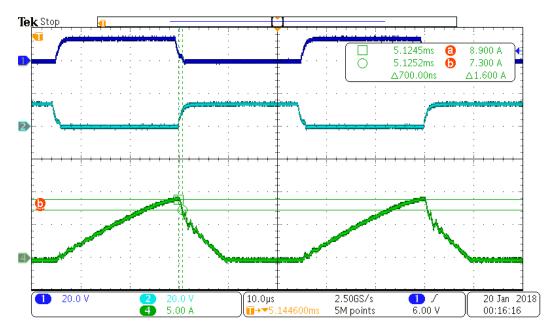

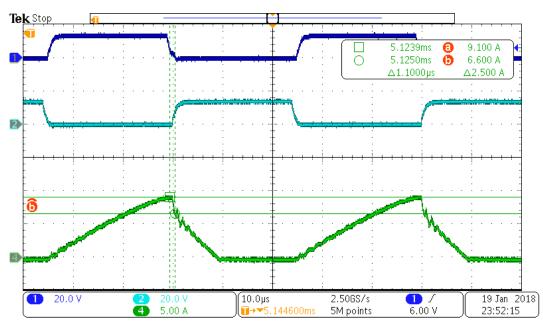

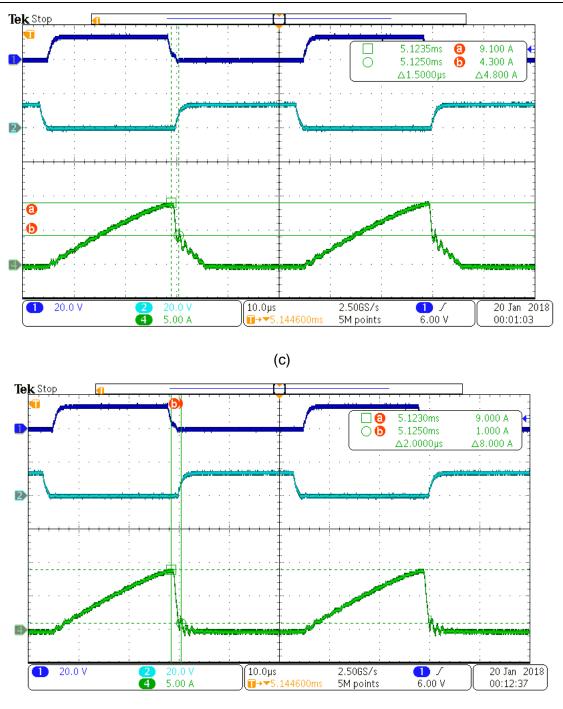

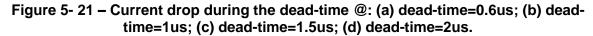

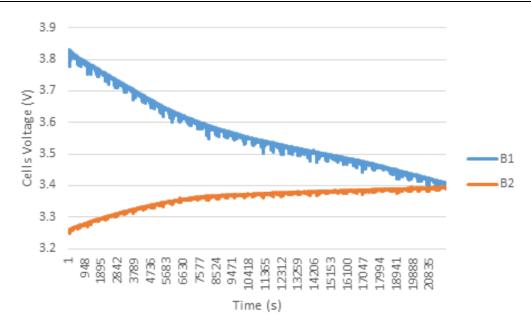

| Figure 5- 21 – Current drop during the dead-time @: (a) dead-time=0.6us; (b) dead-time=1us; (c) dead-time=1.5us; (d) dead-time=2us    |

| Figure 5- 22 – Cells voltage in equalisation from B1 to B2                                                                            |

| Figure A-1 – Harmonic contents in extended frequency span of Figure 4-12142                                                           |

| Figure A- 2 – Harmonic contents in extended frequency span of Figure 4-14143                                                          |

| Figure A- 3 – Harmonic contents in extended frequency span of Figure 4-17144                                                          |

| Figure A- 4 – Harmonic contents in extended frequency span of Figure 4-19145                                                          |

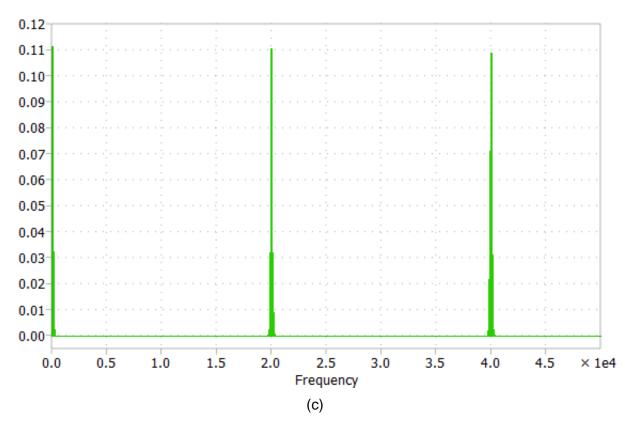

| Figure A- 5 – Harmonic contents in extended frequency span of Figure 4-22147                                                          |

| Figure A- 6 – Harmonic contents in extended frequency span of Figure 5-12147                                                          |

## List of Tables

| Table 2- 1 – Summary of equalisation schemes35                                                          |

|---------------------------------------------------------------------------------------------------------|

| Table 3-1 – Look-up table for switching states in a cell selector of five cells                         |

| Table 3-2 – MOSFET states for all cell-combinations when charging odd cells 50                          |

| Table 3-3 – MOSFET states for all cell-combinations when charging even cells 53                         |

| Table 3- 4 – MOSFET states for all cell-combinations for equalisation between odd         cells         |

| Table 3- 5 – MOSFETs states for all cell-combinations when equalisation betweeneven cells               |

| Table 3- 6 – MOSFETs states for all cell-combinations when equalisation between oddcells and even cells |

| Table 3- 8 – Parameters of the proposed circuit in the simulation model                                 |

| Table 4- 1 – Simulation parameters in the PFC controller       92                                       |

| Table 4- 2 – Simulation parameters in PFC and CC controller       97                                    |

| Table 4-3 – Simulation parameters in PFC and CC-CV controller                                           |

| Table 5-1 – Specifications of battery module                                                            |

## Symbols

| В                    | Battery cell                            |

|----------------------|-----------------------------------------|

| С                    | Capacitor                               |

| L                    | Inductor                                |

| Lm                   | Magnetic inductance                     |

| S                    | Switch                                  |

| Νρ                   | Primary winding                         |

| Ns                   | Secondary winding                       |

| Bus                  | Bus in winding selector                 |

| Rcell                | Resistance in battery model             |

| $V_{Lm}$             | Voltage across primary winding          |

| $V_{LS_{-1}}$        | Voltage across top secondary winding    |

| $V_{LS_2}$           | Voltage across bottom secondary winding |

| i <sub>Lm</sub>      | Current in primary winding              |

| I <sub>peak</sub>    | Peak current in primary winding         |

| i <sub>LS</sub>      | Current in secondary winding            |

| I <sub>LS_peak</sub> | Peak current in secondary winding       |

| т                    | Switching period                        |

| D                    | Duty cycle                              |

| Dc                   | Critical duty cycle                     |

| Vin                  | Input voltage                           |

| VBn                  | Cell voltage                            |

| Lik                  | Leakage inductance                      |

| Coss                   | Output capacitance of S1                      |

|------------------------|-----------------------------------------------|

| VDS                    | Rated voltage of S1                           |

| Vds                    | Voltage across S1                             |

| Csn                    | Snubber capacitor                             |

| Rsn                    | Snubber resistor                              |

| Dsn                    | Snubber diode                                 |

| id                     | Current through S1                            |

| isn                    | Current through Dsn                           |

| iD                     | Current through secondary winding             |

| Vsn                    | Clamped voltage of snubber circuit            |

| Psn                    | Power dissipated in snubber circuit           |

| $\Delta V_{sn}$        | Voltage ripple in Vsn                         |

| V <sub>ds_clamp</sub>  | Clamped voltage across S1                     |

| P <sub>dead-time</sub> | Power loss in dead-time                       |

| դ                      | Circuit efficiency                            |

| arphi                  | Phase angle between input voltage and current |

| $\cos \varphi$         | Phase factor in PF                            |

| $\cos 	heta$           | Distortion factor in PF                       |

| $K_{v}$                | Gain of input voltage                         |

| K <sub>i</sub>         | Gain of input current                         |

| K <sub>p</sub>         | Gain of proportional                          |

| K <sub>I</sub>         | Gain of integral                              |

| V <sub>ref</sub>       | Reference voltage                             |

### Abbreviations

| AC              | Alternating current               |

|-----------------|-----------------------------------|

| ADC             | Analogue to digital converter     |

| BMS             | Battery management system         |

| CC              | Constant current                  |

| CCS             | Code composer studio              |

| CCS/Combo       | Combined charging system          |

| CC-CV           | Constant-current-constant-voltage |

| CO <sub>2</sub> | Carbon dioxide                    |

| СТС             | Constant trickle current          |

| CV              | Constant voltage                  |

| DC              | Direct current                    |

| DCM             | Discontinuous conduction mode     |

| DSC             | Digital signal controller         |

| DSP             | Digital signal processor          |

| EPRI            | Electric Power Research Institute |

| ePWM            | Enhanced pulse width modulator    |

| ETM             | Energy transmission medium        |

| EV              | Electric vehicle                  |

| EVSE            | Electric vehicle supply equipment |

| FFT             | Fast Fourier transform            |

| GPIO            | General purpose input and output  |

| HEV             | Hybrid electric vehicle           |

| ICE             | Internal combustion engine        |

| IEEE   | Institute of Electrical and Electronics Engineers |

|--------|---------------------------------------------------|

| ISR    | Interrupt service routine                         |

| IMF    | Induced Magnetomotive Force                       |

| MMF    | Magnetomotive force                               |

| MOSFET | Metal oxide surface field effect transistor       |

| PF     | Power factor                                      |

| PFC    | Power factor correction                           |

| PI     | Proportional-integral                             |

| PSU    | Power supply unit                                 |

| PWM    | Pulse width modulation                            |

| RCD    | Resistor-capacitor-diode                          |

| SAE    | Society of Automotive Engineers                   |

| SOC    | State of charge                                   |

| SPDT   | Single-pole-double-throw                          |

| THD    | Total harmonic distortion                         |

| V2G    | Vehicle-to-grid                                   |

| 1P5S   | One-primary-five-secondary                        |

### **Chapter I Introduction**

#### 1.1 Background

Global warming due to the greenhouse effect has received more and more attention in recent years. Emissions of greenhouse gases, of which about eighty per cent is carbon dioxide (CO<sub>2</sub>), are the leading cause of the greenhouse effect [1]. In the UK, CO<sub>2</sub> emissions from the transport sector accounted for 32 per cent of all carbon dioxide emissions in 2016, which is a 0.9 per cent increased from 2015 [2].

Compared to conventional oil-fuelled vehicles with internal combustion engines (ICEs), hybrid electric vehicles (HEVs) and electric vehicles (EVs) have the potential to reduce CO<sub>2</sub> emissions [3-5].

There are several potential components which have been used as energy source for HEVs/EVs, such as the lithium-ion battery, fuel cell and supercapacitor. As a traditional energy storage component, lithium-ion batteries have been used as energy sources for portable devices such as mobile phones and laptops for a long time. Compared to novel components such as supercapacitors, lithium-ion batteries have the main advantages of high energy density, good high-temperature performance and good safety performance [6-10]. They also benefit from their advanced recharge cycle and relatively low manufacturing cost. Supercapacitors may have considerably higher power density and charging/discharging speeds than lithium-ion batteries; however, their energy density is still low and their cost is high [6, 11, 12]. Fuel cells generate electricity from hydrogen applied to the anode and the air applied to the cathode. The advantages of fuel cells include high conversion efficiency, quiet operation, and very low emissions [6, 13]. However, fuel cells have some major issues including high price and on-board hydrogen storage which needs improved energy density and safety [14]. Above all, owing to their power and energy density and good cycle behaviour, lithiumion batteries are chosen by most EV and HEV manufacturers. As the penetration of Liion powered vehicles across the world increases the scale of production, thus means that lithium-ion batteries will benefit from the maturity of production technology and higher volumes resulting in lower manufacturing costs [15, 16].

#### 1.2 Battery systems in EVs

The voltage level for a single Lithium-ion battery cell is quite limited. For example, the nominal voltage of a Lithium-ion 19850 cell which is used by Tesla is only 3.8V. In most HEV/EV battery systems, the standard battery pack voltage is about 300V to 600V or higher [17, 18]. There is therefore a requirement for a large number of cells to be connected in series to form a battery pack with an adequate nominal voltage. With significant numbers of battery cells installed in a vehicle, a delicate charging system and battery management system (BMS) are required to guarantee the safety of both the vehicle and the passengers.

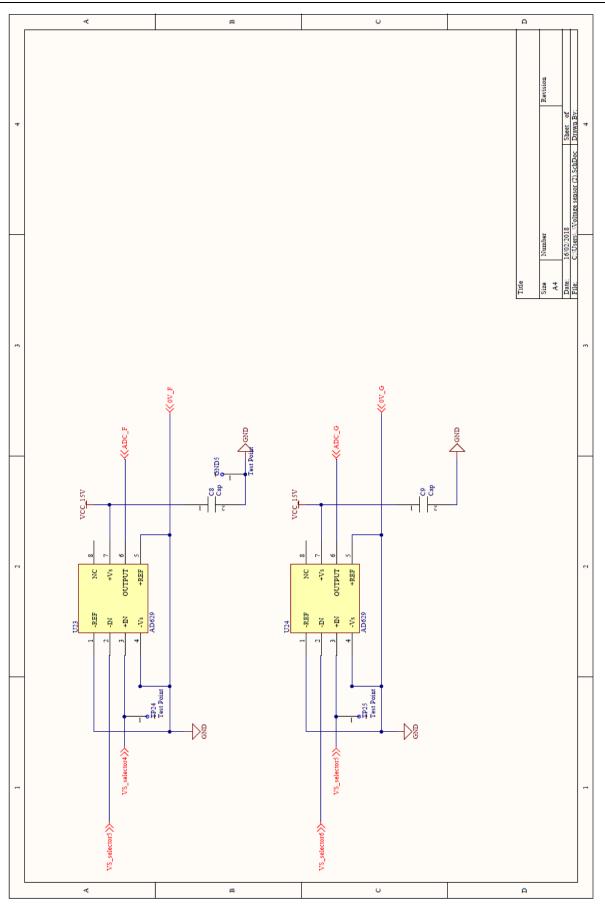

Figure 1-1 – Diagram of a typical battery system in an EV.

Figure 1-1 illustrates a typical battery system in an EV, including battery charging and battery management [19-22]. EV chargers provide a DC charging voltage from an AC source, whether from a common socket outlet or from a purpose-built DC charging station. Therefore, blocks including AC/DC conversion and power conditioning control are needed to convert AC power to DC power, and a DC/DC converter is required to regulate the DC power to a suitable voltage for battery charging. Another DC/AC converter is involved in converting the DC power to AC again to drive the electric motor, and it is usually a bi-directional converter to allow energy flow from the motor to the battery during braking.

Three different charging power levels have been defined: Level 1 (standard) charging, Level 2 (fast) charging, and Level 3 (rapid) charging. Level 1 and Level 2 chargers can deliver power up to 3kW and 22kW respectively, and both take AC power from the grid to charge the battery through an on-board charging system. Meanwhile Level 3 chargers supply very high power up to 120kW to achieve shorter charging times. With the very high power level, the charging circuit becomes very large and very expensive, and requiring heavy duty components. Hence, for Level 3 chargers, the functions of AC/DC conversion and power conditioning control take place in charging stations, fulfilled by off-board chargers.

The BMS is another system which is tightly integrated with the battery in an EV. It is responsible for monitoring the battery's operating conditions of voltage, current and temperature and controlling the charging/discharging rate to prolong battery life and guarantee its safety [23]. A typical BMS contains several different circuits to achieve the above functions, including measurement circuitry, a state of charge (SOC) calculator, equalisation circuits, and the thermal management circuits [23-25].

#### 1.3 Voltage equalisation circuits

As a part of the BMS, the voltage equalisation circuit is a key element in maintaining the battery voltage within the normal range. Due to manufacturing tolerances and changes in battery chemistry due to ageing effects, each cell is unique in its electric performance. Therefore the charging and discharging profiles of all battery cells are not the same. When the series-connected cells are charged or discharged by the same current, each cell produces a different cell voltage across the stack due to their unique individual cell impedances. This is often termed an unbalanced state. The continued charging of mismatched cells in a pack can lead to the over-charging or over-discharging of cells, reducing the power-to-volume ratio of the battery system and, in the worst case, placing the whole system at risk of a catastrophic fault. Figure 1-2 shows a damaged lithium-ion battery and a damaged EV caused by a failure of a lithium-ion battery. Therefore, a method for voltage equalisation is necessary to guarantee safety and improve efficiency.

Figure 1- 2 – Photographs of: (a) a damaged lithium-ion battery; (b) a damaged EV caused by battery failure.

A number of different circuits have been proposed in the literature to accomplish voltage equalisation [2-9] [26-31]. Based on different methods to deal with the management of energy in a battery pack, balancing circuits can be divided into two categories: dissipative and non-dissipative methods. In dissipative equalisation circuits, an energy absorbing unit such as a resistive load is switched into a parallel connection with the cell controlled by a micro-processor. This has the effect of discharging the cell's energy into the load and dissipating it as heat. This equalisation method has been widely used in low-power systems, due to the simple circuit structure and circuit control and its low cost. However, these circuits obviously exhibit low efficiency, since the energy extorted from higher voltage cells is wasted. Besides this, when the cell's stored energy is transformed into heat, the temperature in the battery pack must be carefully managed to avoid significant increases in temperature which could also lead to safety issues with the pack. Non-dissipative equalisation circuits have better performance in terms of energy efficiency. With the employment of an energy transfer medium such as converters and transformers, the energy in cells within a pack can be rearranged with less waste. Plenty of non-dissipative equalisation circuits have been proposed, and each circuit has its own advantages and drawbacks. Therefore, the choice of the equalisation circuit is often driven by the cost and specifications of applications.

#### 1.4 Previous work on multi-functional design in EVs

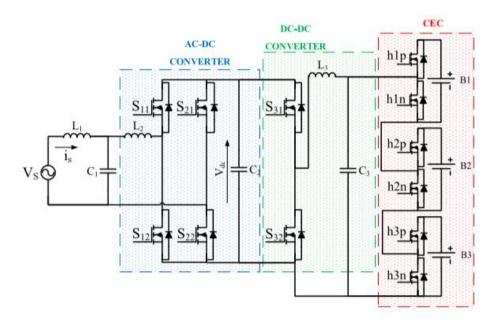

Any non-dissipative equalisation circuit adds cost compared to a dissipative circuit. In order to attempt to reduce costs the concept of multi-functional design is explored in this thesis. The idea is that the power electronics associated with voltage balancing could be modified in such a way as to be not only used for balancing the cell voltage but also for charging each cell directly from the grid. This way, the BMS will replace the AC/DC battery charger of an EV as shown in Figure 1-1. Thus a complete subsystem can be eliminated, reducing the weight and cost of an EV.

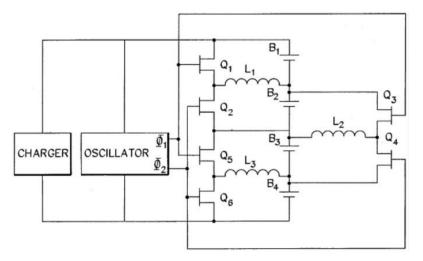

Figure 1-3 – Bidirectional charger topology [26].

A few attempts have been proposed to combine an additional function with the BMS. [32, 33] suggested a bi-directional battery charger with a modular integrated equalisation circuit in which the battery cells are connected to the grid via a full-bridge rectifier, a DC/DC converter and a group of switches. The circuit charges the cells by selecting those which have lower voltage and stops the charging of those which have reached the maximum cell voltage. Thus, rather than charging all cells with one current, each cell is charged individually from the grid. The proposed circuit is, however, only

able to balance the cell voltages when connected to the grid. Once the BMS is unplugged, the circuit is unable to achieve a balanced voltage across the cells. Another study proposes a battery charger that includes a voltage source and a non-dissipative shunt arrangement that can be customised to charge any number of batteries [34]. This non-dissipative shunt circuit includes a pair of transistors and an inductor for each pair of batteries, and they are connected as a buck-boost converter. Therefore, the circuit can be used to charge the battery as an EV charger when it is connected to the grid; meanwhile, it is capable of balancing cell voltages through the shunted buckboost converters when the circuit is unplugged. However, the components involved in the proposed circuit are exactly the same as those when the charging circuit and the equalisation circuit are separate. In other words, this circuit does not achieve the aim of reducing the number of devices in the system.

#### 1.5 Objectives

In a conventional EV, the battery charging and equalisation circuits are separate. Most chargers provide a charging voltage up to 600V, and components include the rectifier, power factor correction (PFC) circuit and isolated DC/DC. All of these components need to be designed to withstand this high voltage, which makes the battery charger bulky and costly. In order to achieve balanced voltage among a large number of battery cells, the size of the required equalisation circuit increases with the number of cells, as does the cost. Therefore, designing one circuit that combines both functions of charging and equalisation would save on number of components, weight and cost, which are important targets in the automotive industry.

The work in this thesis focuses on the design of a Level 1 battery charger incorporating a battery cell equalisation circuit for EVs. It aims to accomplish all of the functions of both battery charging and voltage equalisation using fewer devices. When the vehicle is static and connected to the grid, the proposed circuit is able to charge the traction battery just like conventional chargers do. When the vehicle is not connected to the grid, or is even on the road, the circuit operates like a conventional voltage equaliser. The design of such a circuit must therefore provide AC/DC conversion, grid power conditioning, isolation between the grid and the battery, and voltage equalisation.

To add a charging circuit to the voltage balancing circuit, the transformer-based balancing circuits are preferred, since the transformer structure can also provide the

isolation. The transformer-based balancing circuits can be divided into two types, one is based on flyback converter topology, while the other one is based on forward converter topology. Comparing these two types, the flyback converter topology has advantages such as smaller size and easier control. Besides, the flyback converter is more suitable for circuits with multiple outputs. However, the power of flyback converters are limited. The power level of a flyback converter is up to 200W, and it normally be used in low-power applications. As to the structure of the transformer, since in flyback converters, in order to prevent magnetic saturation, the core of the transformer needs to add an air-gap. It will increase the leakage inductance, reduce the circuit efficiency, and put more stress on the switching device. Besides, since the output voltage and current are pulsed, flyback converters are suitable for applications which highly require constant outputs.

#### **1.6 Contribution to knowledge**

The main original contributions of this research work are as follows:

- A detailed overview of published equalisation schemes is presented in this thesis, and a unique method is also firstly suggested for categorising these schemes to families based on different aspects including constituent components and energy transfer path, mode and sequence.

- An EV battery charger integrated with a multi-secondary windings transformer equalisation circuit is proposed in this thesis. The circuit has two standalone operational modes of grid charging or voltage balancing, which are alternated between using a pair of single-pole-double-throw (SPDT) switches.

- A multi-functional power electronic power converter is proposed for the first time which combines the full functions of grid battery charging with the full functions of battery equalisation with only one transformer in the circuit. Beside this, the proposed circuit is capable of achieving balanced voltage by selecting lower voltage cells during the charging process.

- A control strategy that includes PFC control and CC-CV charging control has been developed in this work. The control strategy demonstrates fast charging without compromising the PF when CC-CV charging is applied.

Some relevant outcomes from the research have been published in the following papers:

[1]. S. M. Lambert, V. Pickert, D. J. Atkinson and H. Zhan, "Transformer-Based Equalization Circuit Applied to n-Number of High Capacitance Cells," in *IEEE Transactions on Power Electronics*, vol. 31, no. 2, pp. 1334-1343, Feb. 2016.

The author of this thesis made contribution in this article mainly focusing on the introduction part, where the commonly used equalisation circuit been summarised, and their advantages and disadvantages been discussed. Besides, a part of the proposed circuit in this thesis is learned from the circuit in this article.

[2]. Huaxia Zhan, Xin Xiang, S. M. Lambert, V. Pickert, Haimeng Wu and Xiang Lu, "A cascaded transformer-based equalisation converter for series connected battery cells," 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), Glasgow, 2016, pp. 1-6.

The author of this thesis participated in the whole process of the work, including design, modelling and simulation of the circuit, and the writing up of the paper. Even though that this equalisation circuit is not utilised as a part of the circuit in this thesis in the final, the research process became a valuable experience for the author to have a deeper understanding of both the battery voltage equalisation and the flyback converter.

#### 1.7 Thesis overview

This thesis is divided into six chapters. Chapter I introduces the background of the project, including battery charging and battery voltage equalisation in EVs. The motivation and objectives of the study, and especially the design of a multi-functional battery system for an EV, as well as its contributions to knowledge.

In Chapter II a detailed overview is presented of both the battery charging system and the voltage equalisation circuit. It starts with the constant-current-constant-voltage (CC-CV) charging strategy for the lithium-ion battery. Then, EV chargers are introduced in terms of charging power levels with corresponding charging infrastructures, and different charging circuit schemes. This is followed by a thorough study of voltage equalisation circuits, including the factors which cause unbalanced voltage levels and the necessity for equalisation circuits for battery packs, and descriptions of existing equalisation schemes along with a summary of their advantages and limitations. Chapter III presents the development of the proposed battery charging system incorporating an equalisation circuit. Each block of the circuit is described separately, including its design and function. There are five operational modes for the proposed circuit, two for battery charging from the grid, and three for voltage equalisation. The five operational modes are studied successively, where each mode is explained using an example of a possible combination of cells. This chapter also introduces the simulation model for the proposed circuit, and the simulation results obtained when the circuit operates under different modes with open-loop control.

A closed-loop controller for the proposed circuit is described in Chapter IV. The controller is capable of both PFC and CC-CV charging. This controller actually consists of two controllers, a PFC and CC controller and a PFC and CV controller. The choice of controller depends on the cell voltages in the pack. Simulation results are presented when the circuit operates with the two controllers.

Chapter V describes the experimental testing of the circuit. It starts with the design and implementation of the test system, including hardware and software implementation. Then, experimental results for the circuit operating as a battery charger and a voltage equaliser are presented. The experimental results are compared with the simulation results, and they prove that the proposed circuit is capable of either charging the battery or achieving balanced voltage within a battery pack.

Chapter VI summarizes the research work that was carried out in the project and discusses the advantages and disadvantages of the proposed battery charging system integrated with an equalisation circuit. The chapter ends with recommendations for future work to enhance the proposed technique.

## Chapter II Charging and Equalisation for Lithium-ion Batteries

This chapter introduces background information concerning the development of a converter which achieves the aim of the project. Firstly, different charging strategies for lithium-ion batteries are explained. Then, battery charging systems which are currently used in EVs are described, including details of charging power levels and charging structures. Finally, an overview of existing battery equalisation circuits is presented covering their structure and operation, and a comparison based on the available literature.

#### 2.1 Charging strategies for lithium-ion batteries

In order to provide optimal charging in terms of efficiency and charging time, various battery charging strategies have been developed, such as constant trickle current (CTC) charging, constant current (CC) charging, constant voltage (CV) charging, and constant current and constant voltage (CC-CV) charging, as discussed in [35-41].

CTC charging provides the battery with a very low but constant current. Therefore, the charging process can be very stable but extremely slow. The long charging time is the biggest disadvantage of this method. However, when a battery is charged from a very low initial voltage, for example under the pre-charge voltage threshold, the battery should be CTC charged for safety and reliability reasons until its voltage has risen to the pre-charge threshold value. Above the threshold, other charging strategies can be applied.

CC charges the battery with a constant current at levels well above those in CTC. CC allows a battery to be charged at high speed. One drawback of this method is that the battery can be easily overcharged due to the high charging current.

The CV charge strategy charges the battery with a constant voltage. Since the current is determined by the voltage difference between the battery and the charging source, the charging current level is driven by Ohm's Law, and thus a higher current is applied to the battery at the beginning when the cell voltage is still low. Then the charging current declines slowly as the cell voltage increases. In the later stage of charging, the charging speed becomes dramatically slower until the voltage difference is not sufficient to drive any further charging current.

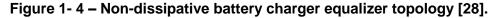

Charging based on the CC-CV strategy is a combination of the previous three charging methods. CC-CV aims to charge battery cells in a more efficient way and to guarantee safety at the same time. The principal charging process of the CC-CV method is shown in Figure 2-1.

Figure 2-1 – CC-CV charging method for battery cells.

At the beginning, the battery cell is charged in CTC mode by a small current when the cell voltage is under Threshold 1. After that, the charging process moves to CC mode during which the current is large enough to charge the battery at a higher speed and the cell voltage increases quickly. Once the cell voltage reaches Threshold 2, the charging switches to CV mode and thus the charging current starts to fall, as does the charging speed. The whole charging process ends when the cell voltage has reached its maximum value, which is normally defined by the manufacturer.

#### 2.2 EV Battery chargers

An EV battery charger is in principle a rectifier circuit that converts AC voltage to DC voltage. The DC level is controlled and adapted to the voltage of the battery pack in an EV. According to the charging method, battery chargers can be categorised as using conductive and inductive charging. Conductive chargers have hard-wire contacts between the power supply and the vehicle, while inductive chargers use a varying magnetic field to transfer energy to the battery without any physical contact. A detailed comparative study of these methods has previously been published [42]. Inductive chargers provide galvanic isolation between electric vehicles and the power supply,

which makes the method safe for high power applications (in excess of 50kW). It also makes it possible for vehicles to be charged during motion by building charging strips into highways. However, the efficiency of magnetic energy transfer in inductive chargers is relatively low due to the loose coupling of coils; besides, the infrastructure costs of inductive chargers are much higher compared to conductive chargers [43]. Hence, in this project, conductive chargers have been taken into consideration and are introduced in the next section.

#### 2.2.1 Charger power levels and infrastructure

The power level of a charger indicates its power, location, charging speed and infrastructure cost. According to the charging rate, conductive EV chargers can be classified into three categories, depending on the charging power level [44]. The categories are classified as Levels 1 to 3 and each level has its own electric vehicle supply equipment (EVSE).

EVSE is installed for the purpose of delivering energy from the grid to an EV, and consists of a residential or commercial charging stand, an attachment plug, a power outlet, a vehicle connector and some protection circuits [44]. Configurations of EVSEs vary depending on the power level, voltage, and frequency.

#### a) Level 1 Charging (Standard AC Charging)

The Level 1 category represent slow charger units found in both residential and commercial buildings with charging power up to 3kW. For this power level, EVs can receive power from a domestic single-phase socket outlet. Common EV plugs for Level 1 connected to power sockets are the three-pin NEMA 5-15P (US) or the three-pin BS1363 (UK), which are the same plugs as used on domestic appliances such as televisions and laptops. The other end of the EV cable connected to the vehicle possesses a connector which is either a five-pin SAE J1772 plug or a seven-pin IEC 62196 plug [45], as shown in Figure 2-2.

Level 1 charging requires approximately 6 hours to fully charge an EV such as the Nissan Leaf, for example, depending on the battery type and energy. Times between 6 to 8 hours are acceptable for EVs charged at home overnight, or in a car park during working hours. A Level 1 charger minimises the need to update the current power supply devices. The infrastructure cost per a residential Level 1 charger has been

estimated at approximately \$800 in the US [46], including labour, material and permit costs.

#### b) Level 2 Charging (Fast AC Charging)

Level 2 charging is the primary charging method for both private and public facilities and provides charging power up to 22kW. It employs dedicated equipment and connections for a charging unit to provide higher levels of safety. A residential fast charger is typically mounted on a garage wall, with a tethered J1722 plug or IEC 62196 plug [45], whichever is compatible with the vehicle. Meanwhile some standing fast charging points can be found at workplaces or on-street locations which possess seven-pin socket outlets.

Fast charging will take approximately two to six hours to fully charge a vehicle. According to the Electric Power Research Institute (EPRI), most EV owners prefer to charge at home overnight, and therefore, Levels 1 and 2 chargers are the primary options. However, despite their higher infrastructure costs, Level 2 chargers are more popular in public sites due to their faster charging and standardized vehicle-to-charger connections [18]. The installation fee for a residential Level 2 charger is reported to be approximately \$2,000 and about \$1,800 for a commercial facility charger.

#### c) Level 3 Charging (Rapid DC Charging)

Level 3 charging is for commercial and public applications which can be installed in highway stations and refuelling points similar to commercial petrol stations. The charging unit requires dedicated equipment to operate with a three-phase circuit at 480V or higher, and the power output is normally up to 50kW (the Tesla supercharger has a maximum power output of 120kW [47].) Level 3 chargers contain an off-board charger to provide regulated AC-DC conversion. Therefore, the connection to the vehicle is direct DC. Level 3 charger units are typically equipped with tethered CHAdeMO plugs to connect to EVs with the corresponding socket [45]. However, certain EVs possess the Combined Charging System (CCS or Combo) socket which is compatible with either the tethered rapid DC charger plug or the tethered fast AC charger plug [44, 46].

A Level 3 charger can fully charge an EV within an hour due to its significantly higher power output. The high power output and infrastructure costs mean that Level 3 chargers are rarely feasible for private use. It is reported that the infrastructure costs for a Level 3 charger are between \$30,000 and \$160,000, with extra costs for maintaining the charging station [44].

Figure 2-2 illustrates the charging equipment for all three levels of chargers, including the cords, plugs, and sockets mentioned above.

### Figure 2- 2 – Electric vehicle supply equipment (EVSE) for three levels of chargers. 2.2.2 Power flow in EV chargers

There are two types of power flow in EV chargers: unidirectional and bidirectional power flow. In a unidirectional charger, energy can only flow from the grid to the vehicle, but cannot be injected back from the battery to the grid. These chargers typically use a diode bridge rectifier in conjunction with an input filter and a power factor correction circuit. EVs with bidirectional chargers can not only charge battery cells but also inject energy from the battery pack into the grid, which is referred to as the vehicle-to-grid (V2G) operation mode [48-52]. A typical bidirectional EV charger has two stages: an active bidirectional AC-DC converter connected to the grid which controls input power factor, followed by a bidirectional DC-DC converter to regulate the output voltage and current. While many studies have focused on bidirectional power chargers, their successful implementation requires extensive safety measures and more complicated controllers, since the power flowing in both directions need power factor corrections, and also the same phase angle is needed when injecting power into the grid [18, 44, 48, 52]. So far, all commercially available Level 1, 2 and 3 chargers are unidirectional. It is expected that only Level 2 chargers will become bidirectional, since the cost-

benefit ratio of a bidirectional Level 1 charger is too large and rapid charging (Level 3) only makes sense if the user wants to charge an EV battery as quickly as possible rather than extending the charging time by transferring energy back into the grid.

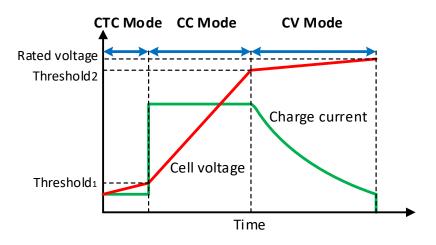

#### 2.2.3 Structure of EV charging system

EV battery chargers can also be categorized as on-board or off-board chargers [18]. For Level 1 and Level 2 charging, since the power rating is limited, the system can be designed to be small and light enough to be installed on vehicles as on-board chargers. Meanwhile off-board chargers are less constrained by weight and space, and therefore Level 3 chargers are typically designed to be off-board [46].

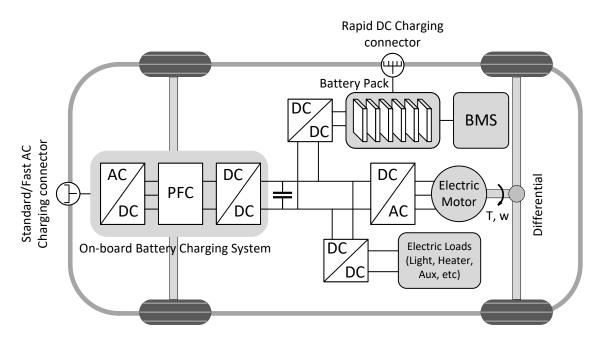

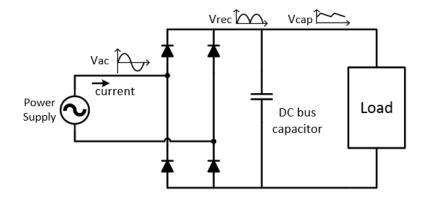

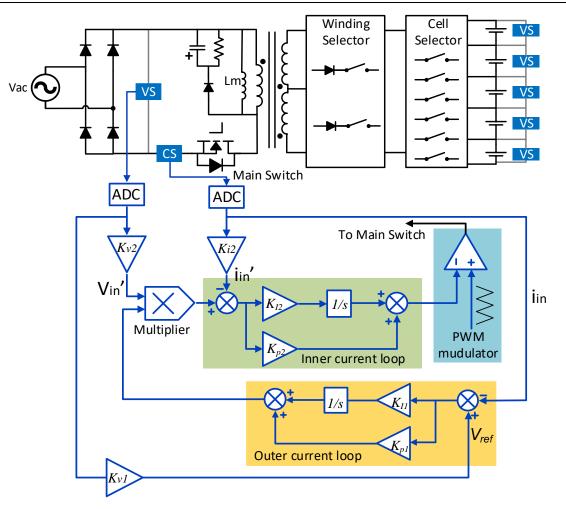

Figure 2-3 presents a block diagram of a typical EV charging system for Level 1 and Level 2 charging [44]. The on-board charger mainly consists of an input filter, a rectifier, a PFC converter and an isolated DC-DC converter. The circuit is shown in detail in Figure 2-4. The input filter is to block interference signals from the grid to the system, which is necessary for most electric equipment connected to the grid. The rectifier converts AC input to DC, which is then regulated by the PFC converter which is responsible for achieving a good power factor. The isolated DC-DC converter provides galvanic isolation and control of the charging power. Isolation is required as the vehicle chassis ground and neutral of the grid should be kept separate.

Figure 2- 4 – Typical Levels 1 and 2 charging circuit for an on-board EV charger.

#### 2.2.4 Power factor correction (PFC) converters

According to IEEE and SAE standards, in EV chargers it must be ensured that the current is drawn with low distortion to minimize any impact of power quality, and with a high power factor to maximize the real power [44]. Thus, in order to improve the power factor in battery charging circuits, PFC circuits are embedded in most EV chargers. Although PFC can be implemented using different topologies, such as buck, buck-boost or Cuk converters, the boost converter is most commonly used in the PFC topologies employed in EV charging [53].

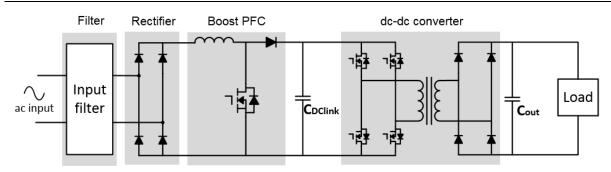

For applications such as EV battery chargers which require an isolated output along with input PFC, a two-stage conversion process typically includes a boost PFC followed by an isolated DC/DC converter, as depicted in Figure 2-5. Operation of the boost PFC converter helps to eliminate the distortion in the input current by compensating for the input voltage when it is lower than the voltage of capacitor *CB*.

Figure 2-5 – Typical two-stage boost PFC converter.

The two-stage PFC performs well in terms of achieving a high input power factor and low-frequency ripple in the output voltage, and therefore it suits many applications beyond EV charging. However, the two-stage structure has low power density, and the overall efficiency of the two-stage topology is also low since power has to flow through two cascaded stages and each stage has to be designed at full output power, which means that the size and cost of the system increase [54]. In addition, each stage has its own controller, which makes the overall control of the charging more complicated.

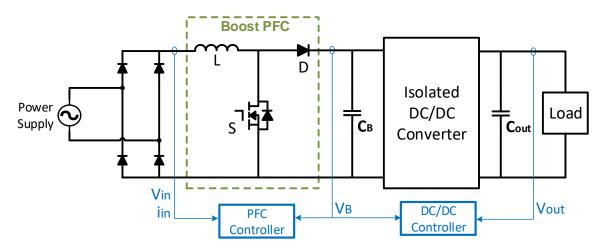

By applying new circuit topologies which allow the merger of the PFC converter and the isolated DC/DC converter into one single conversion system, isolated single-stage PFC converters can be developed. In principle, these converters provide better efficiency and power density. The principles of this circuit are shown in Figure 2-6.

Figure 2- 6 – Principles of an isolated single-stage PFC converter.

Isolated single-stage PFC converters utilise auxiliary magnetic components and power switches to achieve PF correction. Extra power switches have been employed, but this increases the cost and control complexity of the circuit [55]. Other circuits have been developed with one forward converter to deliver the main output to the load, and another auxiliary flyback converter which regulates the output voltage and current [56, 57]. Single-stage PFC circuits with a flyback topology have also been proposed [54, 58, 59] in which extra devices such as inductors and transformer windings are needed as well.

#### 2.3 Voltage equalisation for battery packs

Typically, the terminal voltage and energy capacity of a single lithium-ion battery cell are limited to about 4.2V and 3600mAh respectively [60]. Therefore, multiple cells are connected in series and parallel in EV traction batteries to meet the voltage and energy demands. In an EV battery system, the required bus voltage is in the range of 300-

600V, and the stored energy in the battery system determines the maximum endurance of the vehicle, where typical values are between 24kW to 66kW [17]. Hence, hundreds of batteries are usually assembled into one battery pack.

#### 2.3.1 Unbalanced cells voltage

When a number of batteries are connected in series, they are charged and discharged at the same current rate. Ideally, the terminal voltage of each cell should be the same if they received the same initial voltage and charging/discharging speed. However, due to limitations in manufacturing technology, every single cell is unique. This means that in a battery pack, the internal characteristics of each cell are always slightly different from others even if they are produced in the same batch. Furthermore, cycling, elevated temperature and ageing decrease the performance of the battery cell over time.

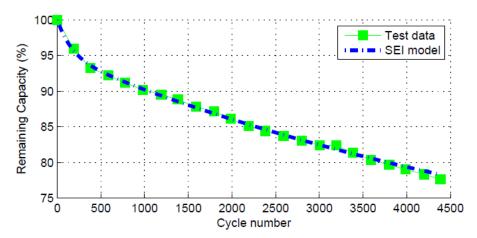

The performance of a lithium-ion battery depends on ion movement between the positive and negative electrodes [61]. The ageing process begins at the moment the cell was produced, and results in declining cell capacity and increasing cell internal resistance [62, 63]. Figure 2-7 shows the degradation curve of a lithium-ion battery. Over 4500 cycles, the remaining capacity of the battery cell decreases from 100% to less than 80%.

Figure 2- 7 – An example of degradation curve for a Lithium-ion battery (3.2V,1100mAh) [16].

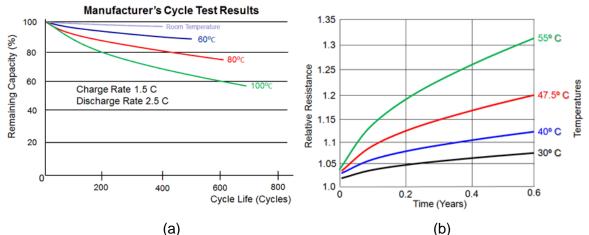

Figure 2- 8 – (a) Decreasing capacity with cycles and temperature; (b) increasing internal resistance with time and temperature [64].

Most batteries perform best at room temperature [61]. Figure 2-8 shows the changes of the remaining capacity and relative resistance of a lithium-ion battery over cycles or time under different testing temperature. It indicates that the high operation temperature will speeds up the degradation of a battery, causing the decreasing of the capacity, and the increasing of the internal resistance.

#### 2.3.2 Necessity of equalisation circuits for battery packs

Due to the fact that each battery cell has its own unique characteristics as highlighted in section 2.3.1, each cell in a battery pack has a unique cell voltage. This unbalanced voltage causes two problems. Firstly, when the battery stack is being charged, the charging process stops once one cell has reached its maximum voltage level. This means that the battery stack carries less energy, since other cells with lower cell voltages have not been fully charged. Secondly, if a cell reaches a critical low voltage level that requires it to stop operating for safety reasons, the whole stack must halt its operation even though all other cells have higher cell voltages. Otherwise, there would be cells which over-charge or over-discharge in the stack. Repeatedly over-charging or over-discharging are extremely harmful to lithium-ion cells, as any damage is irreversible and will dramatically accelerate the ageing process of cells and can lead to their breakdown.

Furthermore, over-charging and over-discharging are not only dangerous to the cell but also to the battery pack. This is because the cell can short-circuit, which then causes a series of reactions via an avalanche effect in the battery pack, resulting in the failure of the whole system. To avoid this situation, it should be ensured the voltage across every single lithium-ion battery is equal. The aim of equalisation circuits is to keep the voltage balanced across each cell in a battery pack. This can be accomplished in two ways. Either energy stored in the cell is bled into a resistor until the cell voltage reaches a specific level, or the energy from one cell is transferred to another cell to achieve a balanced voltage.

## 2.4 Overview of voltage equalisation circuits

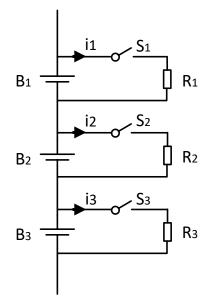

Based on the different ways to deal with extra energy in cells, voltage equalisation for multi-cell battery packs can be divided into two categories: dissipative and nondissipative methods. Typically a dissipative equalisation circuit uses an energy dissipating unit such as a resistor to absorb energy from a cell which has a higher voltage [65, 66]. A dissipative circuit is shown in Figure 2-9 and as shown, resistors will shunt to cells that have higher voltages by activating switches. Thus, these resistors consume energy from the battery cells by converting electric energy into heat until all cells have the same voltage. This method is also known as passive equalisation and it has been widely used typically in low power systems. Benefits include simple circuit structure and controlling and low manufacturing costs. However, passive equalisers show low energy efficiency since energy is wasted in heat, which can produce a temperature rise in the battery pack. Thus passive equalisation requires additional cooling efforts to manage any excess heat. In addition, the amount of current drawn by the shunt elements is not regulated. As a result, the cell voltages are not fully regulated [67].

Figure 2-9 – Dissipative voltage equalisation circuit

Compared to dissipative equalisation, non-dissipative equalisation circuits enhance energy efficiency by using electronic circuits to transfer energy from higher voltage cells to lower voltage ones; therefore, it is also known as active equalisation. This method aims to make better use of the electrical energy stored in battery cells at the expense of greater circuit complexity and higher fabricating costs. Active voltage balancing gains much more popularity in systems with higher power ratios.

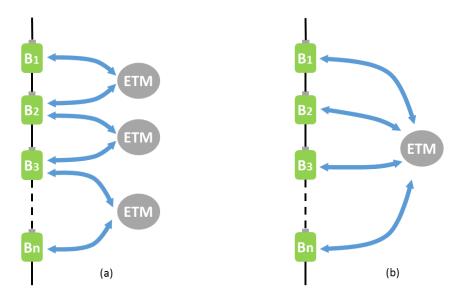

There are several types of non-dissipative equalisation circuits according to the energy transmission medium (ETM) used, and they belong to families grouped either by constituent components or energy transfer method. Categorising by constituent components indicates the physical properties of the circuit, such as size, weight, component count, and cost. Meanwhile, grouping by energy transfer method describes the equalisation rate, modularity, and flexibility. Energy transfer methods are considered below in terms of three aspects: energy flow path, energy transfer sequence, and energy transfer mode.

## 2.4.1 Energy flow path

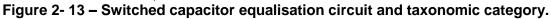

There are two types of energy flow path, which are illustrated in Figure 2-10. Assuming that battery cell Bn has the highest voltage and requires discharging, then two possible energy flow paths appear. Energy can either go to the adjacent cells Bn-1 or Bn+1, or to any cells in the stack. These two energy flow paths are referred to as energy neighbour flow (Figure 2-10(a)) and energy global flow (Figure 2-10(b)).

Figure 2-10 – Energy flow paths: (a) neighbour flow; (b) global flow

The energy neighbour flow scheme is modular and the circuitry required is relatively easy to design. Also, due to its modularity, this scheme can be easily adapted for battery packs with no matter how many cells in. However, energy neighbour flow scheme become less attractive for applications with many cells. This is due to the poor efficiency caused by all of the conversion stages that are required to move energy from *Bn* to a target cell, in the worst case, from the top to the bottom. Also, energy rippling through the different stages results in a slow distribution speed.

Energy global flow schemes are considered to be a more desirable solution for applications with large battery stacks, since they transfer energy from Bn to a target cell far away using only one conversion step. This scheme is therefore more efficient.

## 2.4.2 Energy transfer sequence

Based on energy transfer sequence, equalisation circuits can be divided into two types: single and multiple equalisation schemes. This property is relevant to the equalisation rate and flexibility of circuits. Single equalisation schemes operate on the basis that only one equalisation event takes place in one time period. This is usually the case for energy global flow schemes. Multiple equalisation schemes offer the possibility that several equalisation processes can take place simultaneously. Normally, circuits based on the energy neighbour flow scheme operate as multiple equalisers, since equalisations in these schemes happen independently with isolated energy flow paths.

## 2.4.3 Energy transfer mode

There are three types of energy transfer mode: all-to-all, one-to-one, and one-to-all equalisation, as indicated in Figure 2-11. The choice is determined by the energy transmission medium that is used in the equalisation circuit. Usually, circuits using inductors or capacitors form one-to-one equalisation circuits and circuits with multi-winding transformers form one-to-all or all-to-all equalisation circuits.

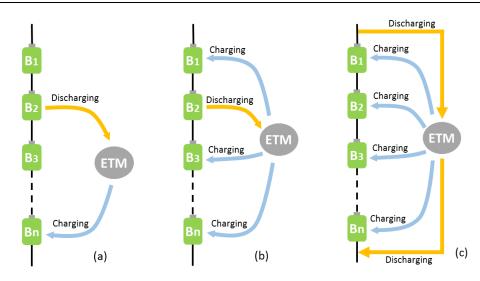

Figure 2- 11 – Energy transfer modes: (a) one-to-one equalisation; (b) one-to-all equalisation; (c) all-to-all equalisation.

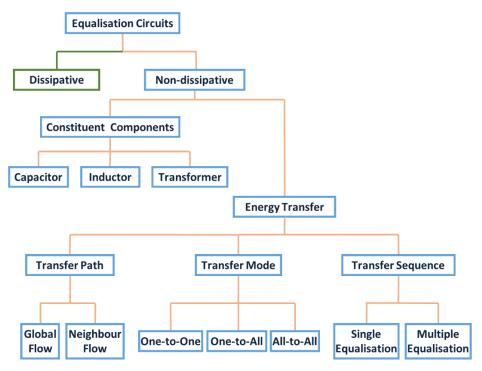

Figure 2-12 – Taxonomy of equalisation circuit categories.

Figure 2-12 presents a taxonomy of equalisation circuits based on the discussion above. Details of each equalisation circuit scheme given in the next section are based on these categories.

## 2.5 Description of existing schemes

This section provides an overview of existing equalisation circuits from the point of view of their operational principles, taxonomic categories, and their advantages and disadvantages.

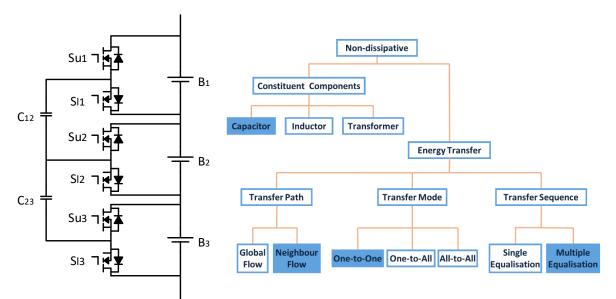

## 2.5.1 Switched capacitor equalisation scheme

It has been proposed in [68, 69] that voltage equalisation can be achieved using an auxiliary stack of capacitors paralleling battery cells via transistors. This scheme is shown in Figure 2-13. In this method, there are twice as many transistors as battery cells. They are grouped into upper switches *Sun* and lower switches *Sln* which are switched alternatively. The paralleled capacitor Cn(n+1) can be shunted to either the upper cell *Bn* or lower cell *Bn+1* according to the state of the switches.