## ADVANCED MODELLING AND DESIGN CONSIDERATIONS FOR INTERCONNECTS IN ULTRA-LOW POWER DIGITAL SYSTEMS

Mohammed Al-Daloo

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical Engineering

Faculty of Science, Agriculture and Engineering

2021

Mohammed Al-Daloo: Advanced Modelling and Design Considerations For Interconnects in Ultra-Low Power Digital Systems ©2021

## **DECLARATION**

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

| Newcastle upon Tyne 2021 |                   |

|--------------------------|-------------------|

|                          |                   |

|                          |                   |

|                          | Mohammed Al-Daloo |

## CERTIFICATE OF APPROVAL

I confirm that, to the best of my knowledge, this thesis is from the student's own work and effort, and all other sources of information used have been acknowledged. This thesis has been submitted with my approval.

ALEX YAKOVLEV

To my greatest supporters that is my wonderful father who is my role model

To my wonderful mother

To my beloved wife

To my lovely kids Maryam, Abdu Allah and Abdu Alrahman

To my family

— Mohammed

I would like to express my deep gratitude to my supervisor Prof. Alex Yakovlev for his support and guidance through my Ph.D. journey. He has always been a source of motivation and my inspirational model as a researcher.

I am grateful to my sponsor Iraqi Ministry of Higher Education and Scientific Research for funding my Ph.D. study their scholarship programme and also would like to express my sincere gratitude to the Iraqi Cultural Attaché in London.

I would like also to express my gratefulness and appreciation to my colleagues and friends in the School of Electrical and Electronic Engineering, especially those in Microelectronic Systems research (MSD) group, at Newcastle University for their guidance and assistance through my study.

I would like to offer my special regards to all the staff of the school of Electrical and Electronic Engineering in Newcastle university, especially Dr. Ahmed Soltan for his supporting through continues discussions and advices.

Last but not least, I would like to thank my wonderful family for their continuous support and motivation throughout my Ph.D. journey. As Very Large Scale Integration (VLSI) is progressing in very Deep submicron (DSM) regime without decreasing chip area, the importance of global interconnects increases but at the cost of performance and power consumption for advanced System-on-Chip (SoC)s. However, the growing complexity of interconnects behaviour presents a challenge for their adequate modelling, whereby conventional circuit theoretic approaches cannot provide sufficient accuracy. During the last decades, fractional differential calculus has been successfully applied to modelling certain classes of dynamical systems while keeping complexity of the models under acceptable bounds. For example, fractional calculus can help capturing inherent physical effects in electrical networks in a compact form, without following conventional assumptions about linearization of non-linear interconnect components.

This thesis tackles the problem of interconnect modelling in its generality to simulate a wide range of interconnection configurations, its capacity to emulate irregular circuit elements and its simplicity in the form of responsible approximation. This includes modelling and analysing interconnections considering their irregular components to add more flexibility and freedom for design. The aim is to achieve the simplest adaptable model with the highest possible accuracy. Thus, the proposed model can be used for fast computer simulation of interconnection behaviour. In addition, this thesis proposes a low power circuit for driving a global interconnect at voltages close to the noise level. As a result, the proposed circuit demonstrates a promising solution to address the energy and performance issues related to scaling effects on interconnects along with soft errors that can be caused by neutron particles.

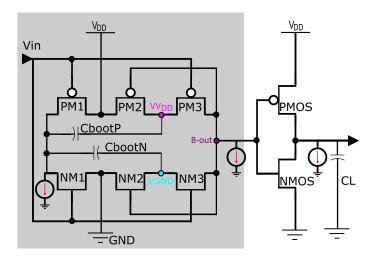

The major contributions of this thesis are twofold. Firstly, in order to address Ultra-Low Power (ULP) design limitations, a novel driver scheme has been configured. This scheme uses a bootstrap circuitry which boosts the driver's ability to drive a long interconnect with an important feedback feature in it. Hence,

this approach achieves two objectives: improving performance and mitigating power consumption. Those achievements are essential in designing ULP circuits along with occupying a smaller footprint and being immune to noise, observed in this design as well. These have been verified by comparing the proposed design to the previous and traditional circuits using a simulation tool. Additionally, the boosting based approach has been shown beneficial in mitigating the effects of single event upset (SEU)s, which are known to affect DSM circuits working under low voltages.

Secondly, the CMOS circuit driving a distributed RLC load has been brought in its analysis into the fractional order domain. This model will make the on-chip interconnect structure easy to adjust by including the effect of fractional orders on the interconnect timing, which has not been considered before. A second-order model for the transfer functions of the proposed general structure is derived, keeping the complexity associated with second-order models for this class of circuits at a minimum. The approach here attaches an important trait of robustness to the circuit design procedure; namely, by simply adjusting the fractional order we can avoid modifying the circuit components. This can also be used to optimise the estimation of the system's delay for a broad range of frequencies, particularly at the beginning of the design flow, when computational speed is of paramount importance.

## Journal publications:

- 1. **Mohammed Al-daloo**; Ahmed Soltan; and A. Yakovlev, *Advanced Interconnect Circuit Modelling Design Using Fractional-Order Elements*, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2019.

- 2. **Mohammed Al-daloo**; Mohamed A. Abufalgha; A. Yakovlev; and B. Halak, *Bootstrapped driver with the Single Event Upset effect*, IEEE Transactions on Circuits and Systems I, 2020.

## Conference publications:

- 1. **Mohammed Al-daloo**; A. Yakovlev; and B. Halak, *Energy efficient bootstrapped CMOS inverter for ultra-low power applications*, IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 516-519, 2016.

- 2. **Mohammed Al-daloo**; Ahmed Soltan; and A. Yakovlev, *Overview Study in On-chip Interconnect Modelling approaches and its trend*, In 2018 7th International Conference on Modern Circuits and Systems Technologies (MOCAST), pp. 1-5, IEEE, 2018.

## CONTENTS

| I | Th   | esis Chapters                                      | 1          |

|---|------|----------------------------------------------------|------------|

| 1 | INTE | RODUCTION                                          | 2          |

|   | 1.1  | Motivation                                         | 2          |

|   |      | 1.1.1 Interconnect power consumption               | 4          |

|   |      | 1.1.2 On-chip interconnect model                   | 5          |

|   | 1.2  | Thesis scope and contributions                     | 7          |

|   | 1.3  | Thesis organization and key findings               | 9          |

| 2 | BAC  | KGROUND AND LITERATURE REVIEW                      | 11         |

|   | 2.1  | Introduction                                       | 11         |

|   | 2.2  | Basics of on-chip interconnectivity circuit        | 12         |

|   |      | 2.2.1 Analytic Modelling                           | 12         |

|   |      | 2.2.2 Electrical level modelling                   | <b>17</b>  |

|   |      | 2.2.3 Importance of Transmission Line (TL) effect  | 19         |

|   | 2.3  | Interconnect system limitations                    | <b>22</b>  |

|   |      | 2.3.1 Fundamental limits                           | <b>22</b>  |

|   |      | 2.3.2 Limitations of the device                    | <b>2</b> 3 |

|   |      | 2.3.3 Limitations of the circuit                   | <b>25</b>  |

|   | 2.4  | Power in CMOS circuits                             | <b>27</b>  |

|   |      | 2.4.1 Ultra-Low-Power (ULP) techniques for driving |            |

|   |      | on-chip interconnect                               | <b>2</b> 9 |

|   | 2.5  | Overview and analyses for on-chip modelling tech-  |            |

|   |      | niques                                             | 32         |

|   | 2.6  | The main interconnects modelling approaches        | 33         |

|   |      | 2.6.1 Approach based on integer-order elements .   | 34         |

|   |      | 2.6.2 Approach based on fractional order elements  | 42         |

|   | 2.7  | Discussion and case study                          | 45         |

|   |      | 2.7.1 Case study                                   | 46         |

|   | 2.8  | Summary                                            | 49         |

| 3 | FRA  | CTIONAL MODELLING FOR INTERCONNECT SYSTEM          | 51         |

|   | 3.1  | Introduction                                       | 51         |

|   | 3.2  | Background                                         | 54         |

|   |      | 3.2.1 Basic definitions                            | 54         |

|   |      | 3.2.2 Basic properties                             | 55         |

|    |      | 3.2.3 Relevant approaches                                       |             |

|----|------|-----------------------------------------------------------------|-------------|

|    | 3.3  | 3.3 The generalising model of the interconnecting system        |             |

|    |      | 3.3.1 Procedure of TL parameters extraction                     | 61          |

|    |      | 3.3.2 Characteristic impedance and complex prop-                |             |

|    |      | agation constant in fractional domain                           | 62          |

|    |      | 3.3.3 $^{\text{TL}}$ transfer function with fractional elements | 69          |

|    |      | 3.3.4 Modelling the system transfer function $\dots$            | <b>7</b> 0  |

|    | 3.4  | Results and discussion                                          | <b>75</b>   |

|    |      | 3.4.1 System simulation                                         | <b>75</b>   |

|    |      | 3.4.2 Model simulation                                          | <b>7</b> 8  |

|    | 3.5  | Conclusion                                                      | 85          |

| 4  | ULTI | RA-LOW POWER DRIVER SCHEME INCORPORATING A                      |             |

|    | вос  | TSTRAP CONFIGURATION                                            | 86          |

|    | 4.1  | Introduction                                                    | 86          |

|    | 4.2  | Background                                                      | 88          |

|    |      | 4.2.1 Sub-threshold mode circuits                               | 88          |

|    |      | 4.2.2 The charge pumping principle                              | 90          |

|    |      | 4.2.3 Single event upsets (SEU)                                 | 91          |

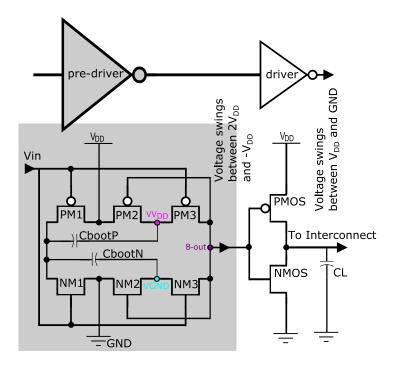

|    | 4.3  | Proposed CMOS inverter                                          | 93          |

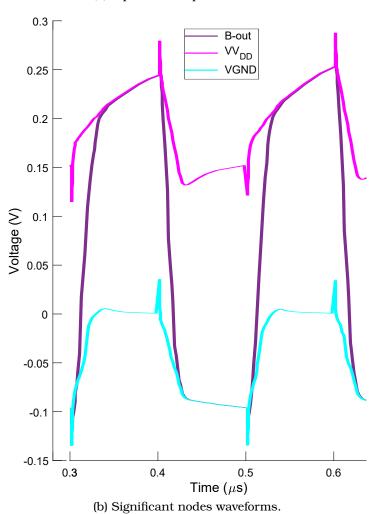

|    |      | 4.3.1 Circuit operation                                         | 94          |

|    |      | 4.3.2 Boosting efficiency                                       | 96          |

|    | 4.4  | Implementation and results                                      | 98          |

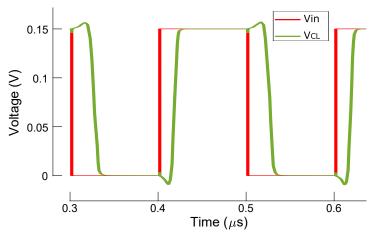

|    |      | 4.4.1 Circuit implementation and results                        | 98          |

|    |      | 4.4.2 Measurement and modelling of an SEU                       | 105         |

|    | 4.5  | Conclusion                                                      | 109         |

| 5  | CON  | CLUSIONS AND FUTURE WORK                                        | 110         |

|    | 5.1  | Summary and Conclusion                                          | 110         |

|    | 5.2  | Future work                                                     | 112         |

| Ш  | Th   | esis Appendices                                                 | 115         |

| A  | DEV  | ICES                                                            | 116         |

| В  | EXP  | ERIMENTAL OF PARAMETERS AND TECHNOLOGY SCA                      | ſ. <b>-</b> |

| _  | ING  |                                                                 | 117         |

|    | 1110 |                                                                 |             |

| Ш  | Th   | esis Bibliography                                               | 120         |

| вп | BLIO | GRAPHY                                                          | 121         |

## LIST OF FIGURES

| Figure 1.1  | Trend of limitations for power consumption      |           |

|-------------|-------------------------------------------------|-----------|

|             | based on Internet of Things (IoT) data in [99]. | 3         |

| Figure 1.2  | Thesis organization                             | 10        |

| Figure 2.1  | Cross sectional dimensions of a conductor.      | 13        |

| Figure 2.2  | Structure of a conductor                        | 15        |

| Figure 2.3  | Lumped element approximations for propa-        |           |

|             | gation classes: (a) RLGC propagation, (b) RC    |           |

|             | propagation, (c) LC propagation, (d) track-     |           |

|             | ing propagation, (e) and (f) propagation of     |           |

|             | resistive substrate                             | 18        |

| Figure 2.4  | A simple interconnect structure                 | 22        |

| Figure 2.5  | global interconnect effect with new genera-     |           |

|             | tions                                           | 24        |

| Figure 2.6  | RC interconnect model with resistive source     |           |

|             | and capacitive load                             | <b>25</b> |

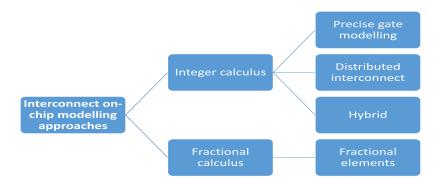

| Figure 2.7  | The interconnect on-chip modelling approaches   | s. 33     |

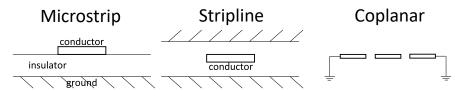

| Figure 2.8  | Some of interconnects structures                | 34        |

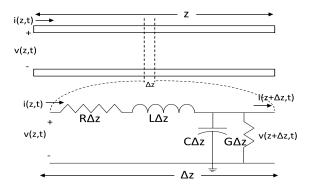

| Figure 2.9  | The RLGC unit of the transmission line equiv-   |           |

|             | alent                                           | 35        |

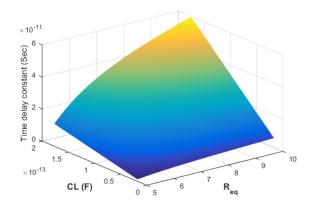

| Figure 2.10 | Time delay constant of first approach with      |           |

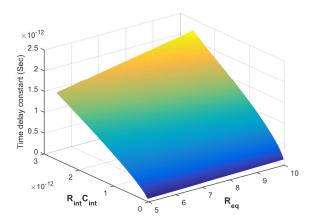

|             | $C_L$ and $R_{eq}$                              | 38        |

| Figure 2.11 | Time delay constant of second approach with     |           |

|             | $R_{int}C_{int}$ and $R_{eq}$                   | 40        |

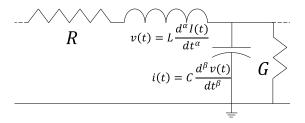

| Figure 2.12 | Fractional order model of the transmission      |           |

|             | line segment                                    | 44        |

| Figure 2.13 | Propagation constant in the fractional ap-      |           |

|             | proach with $\alpha$ and $\beta$                | 45        |

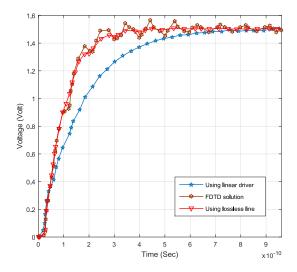

| Figure 2.14 | Time domain responses of the RLGC inter-        |           |

|             | connects                                        | 47        |

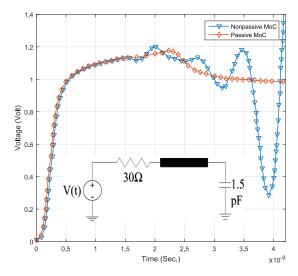

| Figure 2.15 | Far end transient response of passive and       |           |

|             | nonpassive Method of Characteristic ( $MoC$ )   | 47        |

| Figure 2.16 | Transient response of different approaches.     | 48        |

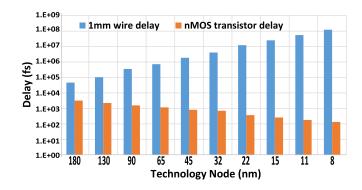

| Figure 3.1  | Wire delay to transistor delay ratio increases  |           |

|             | exponentially [15]                              | <b>52</b> |

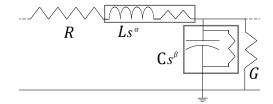

| Figure 3.2  | A transmission line segment with impedance                |

|-------------|-----------------------------------------------------------|

|             | and admittance of fractional order elements. 59           |

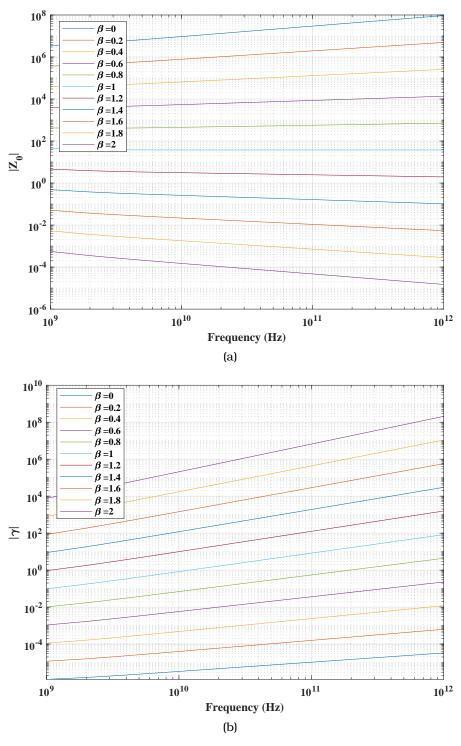

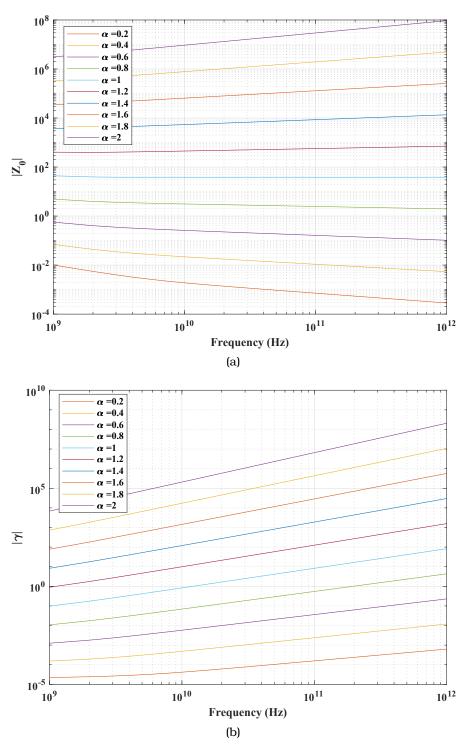

| Figure 3.3  | The magnitude of $Z_0$ and $\gamma$ with respect to       |

|             | frequency at $\alpha = 1$ and $\beta = 0:2$ 64            |

| Figure 3.4  | The magnitude of $Z_0$ and $\gamma$ with respect to       |

|             | frequency at $\alpha = 0:2$ and $\beta = 1.$ 65           |

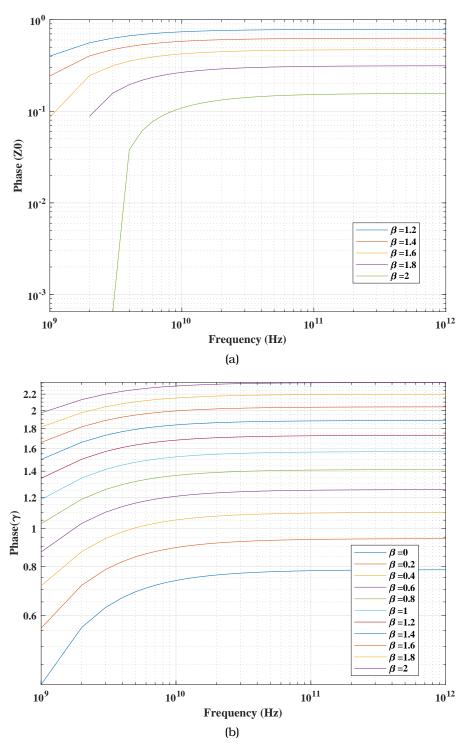

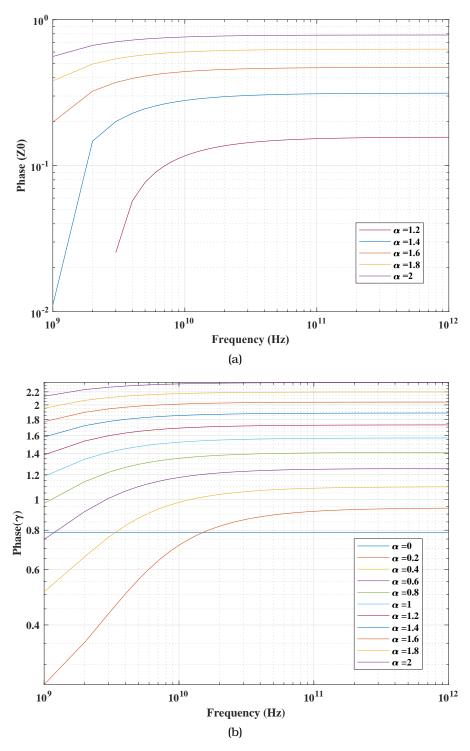

| Figure 3.5  | The phase angles of $Z_0$ and $\gamma$ , in radians,      |

|             | with respect to frequency at $\alpha=1$ and $\beta=0:267$ |

| Figure 3.6  | The phase angles of $Z_0$ and $\gamma$ , in radians,      |

|             | with respect to frequency at $\alpha = 0:2$ and           |

|             | $\beta = 1$                                               |

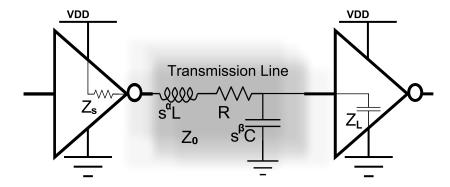

| Figure 3.7  | The model of a complementary metal-oxide-                 |

|             | semiconductor (CMOS) inverter driving a frac-             |

|             | tional distributed RLC load                               |

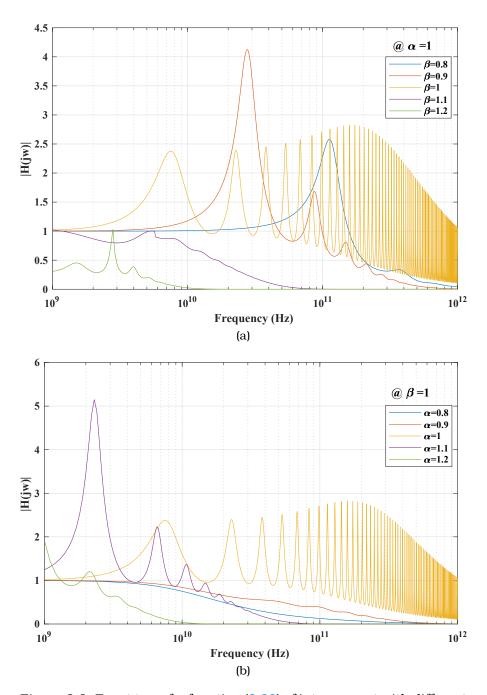

| Figure 3.8  | Exact transfer function (3.39) of interconnect            |

|             | with different values of $\alpha$ and $\beta$ 76          |

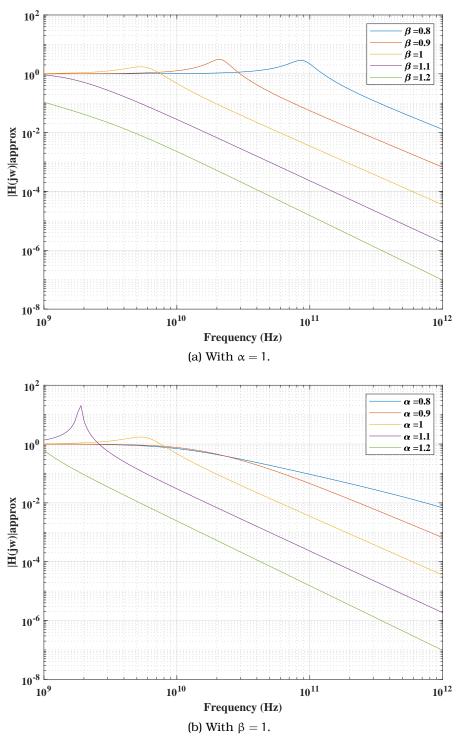

| Figure 3.9  | The fractional approximate transfer function              |

| _           | (3.40) of an RLC interconnect with different              |

|             | values of $\alpha$ and $\beta$                            |

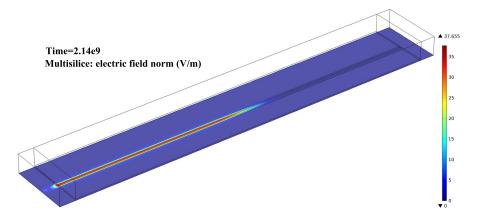

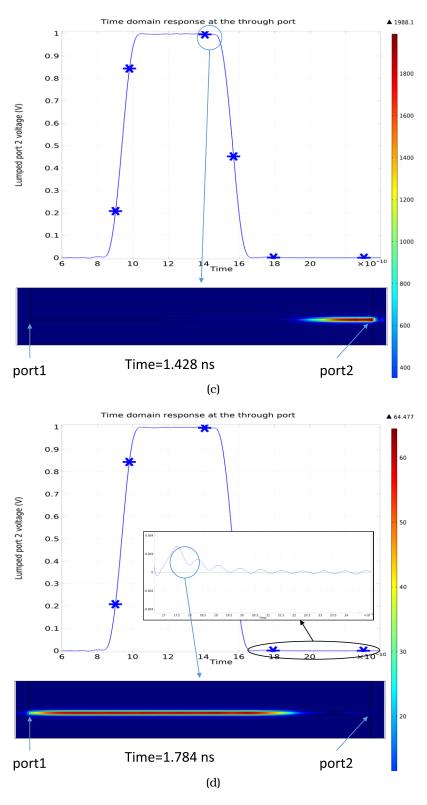

| Figure 3.10 | A microstrip line with a ground plane 79                  |

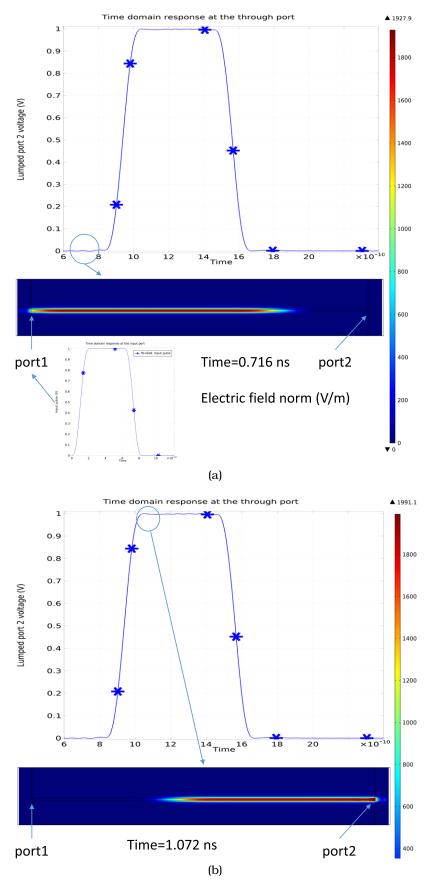

| Figure 3.11 | The process of the signal travelling across               |

|             | the interconnect; (a) The pules signal leave              |

|             | the first port, (b) The pules signal arrive at            |

|             | the far-end                                               |

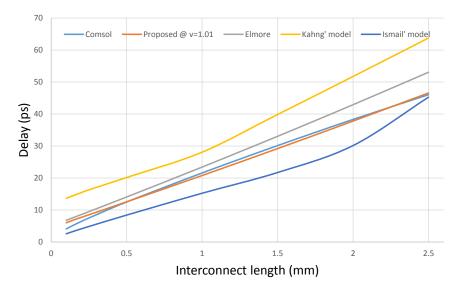

| Figure 3.12 | Delay time results of different models for a              |

| _           | gate driving an RLC transmission line 84                  |

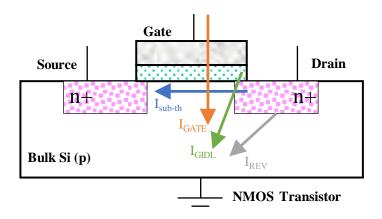

| Figure 4.1  | MOS device's leakage current sources 89                   |

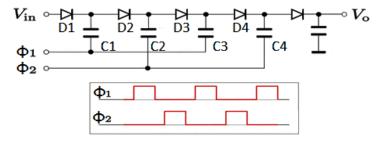

| Figure 4.2  | Four-stages Dickson charge pump [46] 91                   |

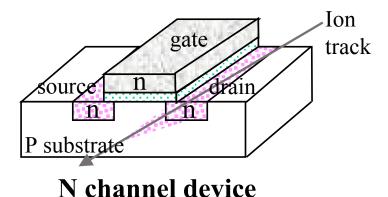

| Figure 4.3  | Particle strikes an NMOS device 92                        |

| Figure 4.4  | Circuit of the proposed driver 94                         |

| Figure 4.5  | Signal waveforms of the circuit 95                        |

| Figure 4.6  | Interaction between discharge current and                 |

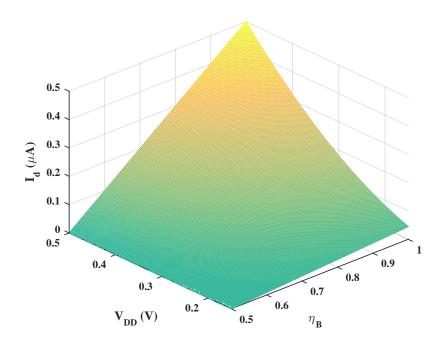

| _           | $V_{DD}$ with efficiency 97                               |

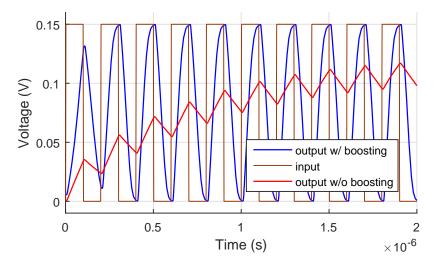

| Figure 4.7  | Transient response waveforms of drivers at                |

| _           | the CL with the same transistors size and                 |

|             | conditions                                                |

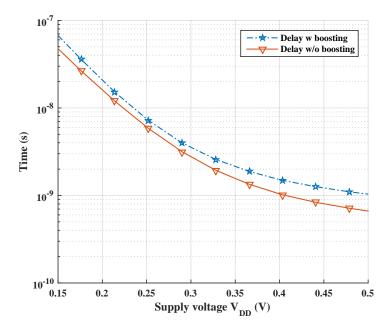

| Figure 4.8  | Drivers with/without boosting delay with                  |

| _           | 200fF load and 5MHz frequency 103                         |

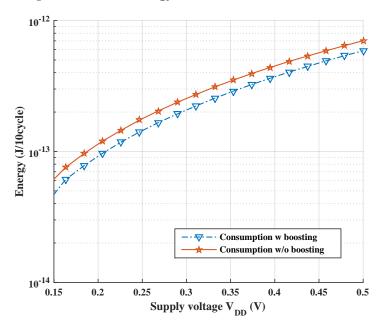

| Figure 4.9  | Energy consumption of buffers under scaling               |

|             | of supply voltage                                         |

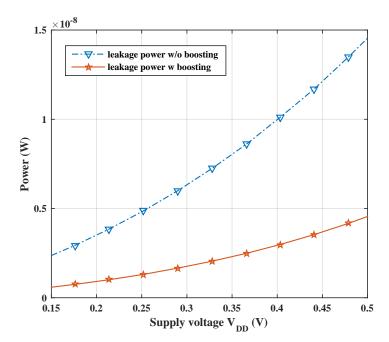

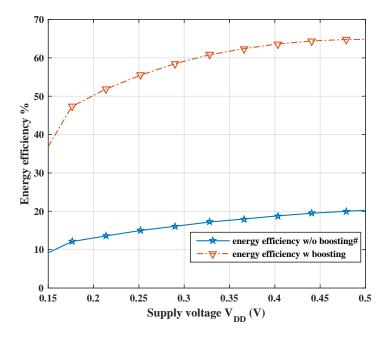

| Figure 4.10 | Power leakage of the drivers 104                 | 4 |

|-------------|--------------------------------------------------|---|

| Figure 4.11 | Energy efficiency of the drivers 10              | 5 |

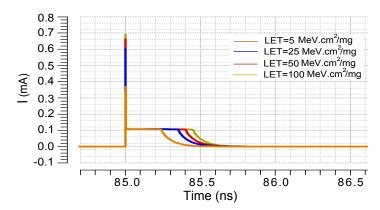

| Figure 4.12 | Transient current pulses generated at $V_{DD} =$ |   |

|             | 1V and different Linear Energy Transfer (LET)    |   |

|             | values                                           | 7 |

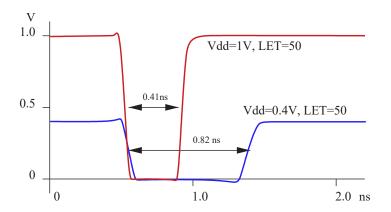

| Figure 4.13 | Responses of the inverter to a transient cur-    |   |

|             | rent pulse                                       | 7 |

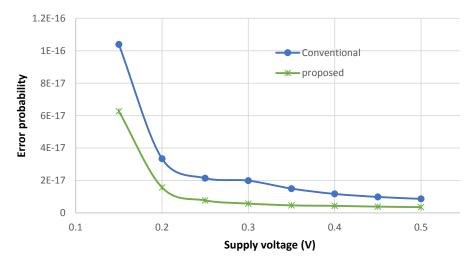

| Figure 4.14 | Circuit implementation of SEU analysis 108       | 8 |

| Figure 4.15 | Comparison of error probability at different     |   |

|             | voltages                                         | 8 |

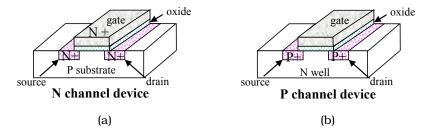

| Figure A.1  | MOSFET devices: (a) N-type MOSFET and            |   |

|             | (b) P-type MOSFET                                | 6 |

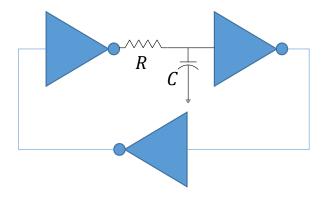

| Figure B.1  | Ring oscillator schematic                        | 8 |

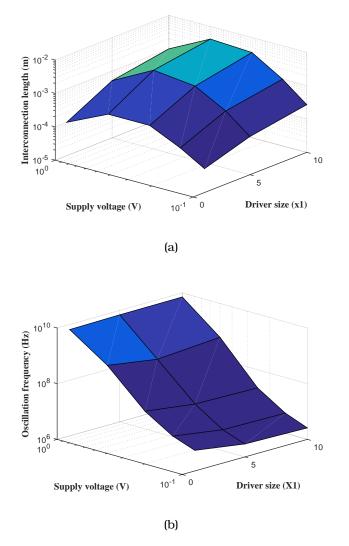

| Figure B.2  | Impact of the supply voltage, driver size and    |   |

|             | interconnection length on the interconnect       |   |

|             | circuits performance                             | 9 |

| LIST OF T   |                                                  | _ |

| Table 2.1   | On-chip interconnects modelling approaches       |   |

|             | summary                                          | O |

| Table 3.1   | Simulation results for different line lengths,   |   |

|             | considering a pulse input and 1 V supply 83      |   |

| Table 4.1   | Devices' sizes                                   | O |

| Table 4.2   | Comparison summary 100                           |   |

| Table 4.3   | Summary of comparison results 109                | 2 |

|             |                                                  |   |

| ACRONYM     |                                                  |   |

|             | S                                                |   |

$\textbf{BIBO} \ \ bounded\text{-}input \ bounded\text{-}output$

IGFET Insulated-gate field effect transistor

${f KVL}$  Kirchhoff's voltage law

KCL Kirchhoff's current law

sio<sub>2</sub> Silicon dioxide

Si Silicon

**MoC** Method of Characteristic

LTI linear time-invariant

**TEM** Transverse electromagnetic

TL Transmission Line

**TLM** Transmission line modelling

**IoT** Internet of Things

**IoE** Internet of Everything

NoC Networks-on-Chip

integrated circuit

**cmos** complementary metal-oxide-semiconductor

**MOSFET** metal-oxide-semiconductor field-effect transistor

**MOS** metal-oxide-semiconductor

**NMOS** N-type metal-oxide-semiconductor

**PMOS** P-type metal-oxide-semiconductor

**SEU** single event upset

LET Linear Energy Transfer

**SET** Single Event Transient

**DSM** Deep submicron

**NoC** network-on-chip

$\mathbf{R}_{q}$  sheet resistance

SoC System-on-Chip

**PV** Parameter Vector

**ULP** Ultra-Low Power

vLSI Very Large Scale Integration

## Part I

# Thesis Chapters

The motivation for the work, a summary of the technical contributions made by the author, and the structure outline of the thesis are stated in this chapter.

#### 1.1 MOTIVATION

Generations of constant improvements in complementary metal-oxide-semiconductor (CMOS) technologies design and fabrication have been catalysed by the demand for lower cost, higher density and more energy-efficient integrated circuit (IC). Such technology trend has led to a relentless shrinking of electronic systems, which has approached the realm of a very deep submicron scale. On the other hand, the reduction in the cost per transistor keeps following an exponential trend, which somehow depends on Moore's law, and will continue despite the end of this law [10]. At the same time, the projection of energy consumption promises a reduction by two orders of magnitude according to the Koomey's and Gene's laws [117]. Thus, based on those trends, it will be increasingly possible to see systems that are small, very inexpensive and extremely low power and pervasive in space.

The demand and supply effect of those technological applications and trends is coming together and creating a novel paradigm, under the so-called Internet of Things (IoT). This new paradigm is swiftly gaining ground owing to the promises of creating huge value and delivering unprecedented benefits to society [17]. The concept of IoT firstly appeared in a presentation in 1999 in the context of a large-scale network of a variety of things or objects such as mobile phones, sensors, tags and actuators [14]. In the general term, the IoT locates at the intersection of the pervasive networking (the Internet), cloud and its significant data, the unprecedented form of mostly real-time aggregated data from the physical world and many other infrastructures. This is occurring through the introduction of ubiquitous, distributed sensors and nodes of an extremely miniaturized integrated system with

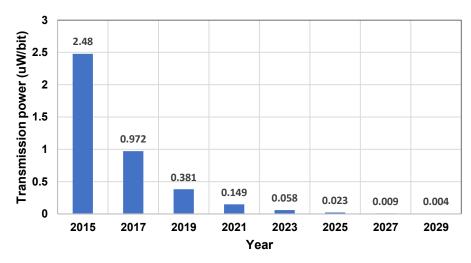

Figure 1.1: Trend of limitations for power consumption based on IoT data in [99].

a very long lifetime and low power consumption [66, 9]. Based on this general term, LoT has already become a reality due to the number of computing devices connected to a global network which surpassed the worldwide population [66].

Regardless of the wide claims regarding LoT in the community of chip design, it is still in their technological infancy and there are many challenges that should be addressed. For instance, the challenges of energy efficiency to maintain power source, cost and reliability, among others need to be tackled [10]. Specifically, in terms of low power requirements for emerging LoT applications, the overriding concern is power where such applications mostly require to consume a certain amount of power [99], as predicted in Figure 1.1. Hence, it is important to work in the direction of locating new solutions which are expected to run at very low voltages [103].

Deep submicron (DSM) technology has created considerable possibilities for digital system design, but has also added a new type of design problems. In the 22nm technology node and beyond, the circuit performance has become more sensitive to the parasitics of interconnect and, thus, more sensitive to interconnect variability [28]. Accordingly, the precision of interconnects fabrication processes has great importance as a direct consequence of the reduction in devices feature size [152]. Additionally, as the feature size and power supply reduce, the sensitivity of the integrated circuits to process variability and single event upset (SEU) has increased. These issues should be considered

in driver circuits design as it noticeably affects the testability, reliability and yield [5].

#### 1.1.1 Interconnect power consumption

Given the increasing use of portable devices which depend on batteries as a power source, saving energy has become one of most important criterion in Very Large Scale Integration (VLSI) design. The recent emerging improvements in semiconductor technology accompanied by a reduction in size and cost of fabrication, have urged such a trend of energy-constrained and IoT-oriented applications [183, 10]. This is to meet the requirements of energy-efficient architectures associated with the delivery of fast-growing IoT services.

The fact of the huge dimensions of interconnects compared to those of transistors, which is caused by aggressive technology scaling, leads the load capacitance to be dominated from the power consumption point of view [184, 55]. Hence, the interconnects appear to represent a puzzle in terms of achieving a high-performing digital system with good power efficiency, where its driver accounts for a large percentage (approximately 50%) of the whole system's power dissipation [183]. However, to be exact, it ought to be known which parts of the system are involved when referring to energy and power. Benini et al. [24] defined it as "the minimum power dissipation per bus transition for only their low power encoder and decoder". This would be correct in ideal cases, but actually some messages are dropped because of noise, and in this case retransmission or redundant bits are needed. Meanwhile, the term "energy per transmitted word" is used by Worm et al. [204], that is to include the energy of successful transmission and retransmission processes together. At the circuit level, power consumption P practically takes place when the capacitance of the interconnection is pulled up to supply voltage  $V_{DD}$  and then pulled down to the ground, wherein  $P \propto fV_{\rm DD}^2$  [150] and f is the frequency of this event. Thus, the energy dissipation depends on basic system features as shown [212]:

$$E = \alpha_a C_{eff} V_{DD}^2 \tag{1.1}$$

where E is the energy consumption of a wire,  $\alpha_{\alpha}$  is an activity factor and  $C_{eff}$  is the effective wire capacitance. Overall, it is clear that equation 1.1 and power expression identify the system components that are involved in power dissipation and guide researchers in designing approaches to mitigate the power dissipated in logic circuits. The issues of wires have been exacerbated with technology scaling due to the increase in the parasitic capacitance of interconnects which results from decreased space between wires and the wire to ground. Moreover, increases in clock speed and energy densities and reduced supply voltage make the system more vulnerable to noise [49]. Also, with the advantages of the semiconductor technology scaling, the microelectronic circuit's susceptibility to radiation-induced soft errors has raised. Consequently, the reliability issue of these circuits becomes another concern to IC's designers [162].

In order to overcome such challenges, many techniques have been proposed; for instance, reducing the swing voltage or the activity over links using coding, implementing circuits with scaled supply voltage, or a bootstrap technique [55].

#### 1.1.2 On-chip interconnect model

Circuits for advanced applications should be premeditated effectively with a high awareness of the interconnect circuits as a crucial part of the chip structure. Estimating the influence of the interconnect on the circuit performance is necessary for the circuit and interconnect joint optimisation. This is because the IC is fundamentally a combination of semiconductor devices and interconnections.

In recent years, most research has not only been interested in transistors and ways to employ them optimally but also in interconnection between devices, which received a comparable interest [29, 55]. Interconnections are simply wires, made of poly-silicon or metal, which link an enormous number of components to transfer data and signals inside a chip, with lengths reaching more than 10 mm in some large chips [56]. In general, the interconnect model can be represented as a set of values of inductance, capacitance and resistance within high frequency nano-scale systems [96]. This is because the simplest form of interconnect is a strip of metal in parallel with a ground plane,

and therefore just a capacitor could be a representative of the wire [183].

At the present time, SPICE like [136] simulators represent the gold standard for the IC designers to simulate the circuit performance. These simulators can accept nearly any circuit, regardless of whether it is linear or nonlinear, and define the voltage waveform on all nodes. However, the process of simulating complete systems using such simulators is very costy. In addition, it is effective to hundreds of nodes [130, 202].

Hence, economical alternatives are used for these simulators. Among these alternatives; Relaxation and iteration simulation methods, solving Maxwell's Equations for interconnections, delay models based on RC tree and transmission line model analysis [197]. These delay models are primarily based on either numerical or analytical techniques. Accurate interconnect models, such as RLC transmission lines and efficient solutions to analyse on-chip interconnects are required in IC design process [197, 163].

With the continuous decrease of on-chip clock periods, the timing characteristics of on-chip signals need to be precisely controlled and determined. Accordingly, accurate interconnect model is important to the process of IC design. However, the attainment of an accurate model for the on-chip line requires a realistic consideration of its parameters. Achieving this is difficult due to the variance of the parameters. For instance, the distributed RLC model is a good approximation to a transmission line model, but it is accurate only up to a certain frequency [159], depending on the number of sections per wavelength.

Currently, designs at a very high-frequency region with considerably improved cut-off frequency near 300GHz at recent technology nodes have become possible due to the advance scaling of CMOS technology [179]. Therefore, frequency dependent components, in particular inductive and capacitive elements, are crucial especially when there is a very high operating frequency [95]. Hence, this draws the attention to the effects that have been discarded in the early assumptions to model interconnections. Thus, this effect should be considered during modelling this important component of IC circuits.

Fractional order calculus has the ability to represent systems with complex nonlinear phenomena high-order dynamics using fewer parameters [149, 80]. This is because its arbitrary order

of the derivatives provides an additional degree of freedom to fit a specific behaviour [75, 80]. Based on that, fractional elements modelling can be used effectively for a non-uniform transmission line with a distributed parameter system. Thus, adding such parameters, i.e. that relate to the fractional-orders elements, would extend the interconnect model representation and have a higher degree of control on its characteristics.

#### 1.2 THESIS SCOPE AND CONTRIBUTIONS

This thesis opens a new research direction in the development of on-chip interconnections modelling. The scope of this thesis is to study interconnect design techniques that are suitable for DSM System-on-Chip (SoC) in the lot realm. This includes a study to seek to extend existing classical interconnects models in the context of generalising architectures, i.e., that use fractional calculus. Though present fractional approaches have discussed the transmission lines, they have not covered the interconnection structure. The objective, here, is to add more flexibility and freedom for design to achieve the simplest adaptable model with acceptable accuracy. As a result, the suggested model can be applied for computer simulation of interconnection management. Additionally, to address Ultra-Low Power (ULP) design limitations, the thesis proposes a low power driving circuit design by running the global interconnect under the transistor voltage threshold and resolves their circuit level challenges. Accordingly, the proposed implementation achieves reduction in energy consumption compared with conventional designs with enhancing performance and improving tolerance to soft errors. Specifically, errors are caused by the radiation impact, for instance the strikes of neutron and alpha-particle.

The major contributions of this thesis can be summarized as follows:

• Several techniques related to the interconnect structure analysis and modelling are outlined in this work. The models are categorized into two main classes; the integer order models and the fractional order models. All major modelling issues and challenges are discussed for different approaches, where a comparison is made for a number of them. From that perspective, this research proposes a

fractional on-chip interconnect modelling approach that has the ability to supersede models using the classic approaches in the DSM regime. Additionally, this research can be the basis for any research intending to take advantages of using these methods and to address their challenges.

- With regard to tackling ULP design challenges, a new design of an interconnect driver has been developed and analysed. This design uses a bootstrap circuitry which boosts the low input voltage of the driving circuit, while this boosted circuit itself feeds the voltage pumping components simultaneously. Hence, this approach has achieved a number of goals; improving performance, decreasing the power consumption, reducing the size and being immune to noise. For ULP circuits design, these improvements are essential and they have been validated by comparing the proposed design with previous and traditional circuits using Cadence simulation tool. On the other hand, the results revealed that the developed design mitigates the effects of single event upsets such as those caused by neutron particle strikes.

- We proposed a new general formula for RLC interconnect circuit model in CMOS technology using fractional-order elements approach. The study is based on approximating an infinite transfer function of the CMOS circuit with a non-integer distributed RLC load to a finite number of poles. It shows better accuracy compared to the results of integral order modelling as demonstrated by performing simulations.

As such, delay calculations employing our analytical model are within 0.4ps absolute error of COMSOL-computed delay across a range of interconnect lengths. Furthermore, although the model has only been designed based on RLC segments, the effect of conductivity G has been implicitly taken into account due to utilising fractional order element in the shunt admittance.

A number of analyses were carried out at different levels of the design to evaluate its effectiveness. First, we demonstrated the significant effects of generalising parameters gained by modelling the fractional order impedance and propagation constant of the transmission line for a range of frequencies. The most important effects are increased flexibility and freedom to design the system. Second, using Matlab we assessed the potential of the proposed approximated model besides the exact one, which shows similarity in the fundamental features of the system such as stability and resonance. Third, the proposed approach showed that with a very small tuning for the generalising parameters we can achieve improvement in the model accuracy. We believe that the proposed approach can be used with already existing simulation tools with a minimal loss in time.

#### 1.3 THESIS ORGANIZATION AND KEY FINDINGS

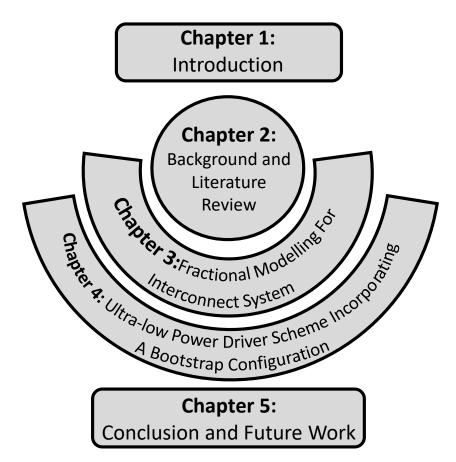

This thesis is organized into five chapters, as shown in Figure (1.2).

Chapter 1 "Introduction": introduces the motivations, objectives, contributions and structure of this thesis.

Chapter 2 "Background and Literature Review": provides background information and presents a brief literature review on topics relevant to this thesis. Discussing the limitation of on-chip interconnect circuits is introduced. Also, a coherent overview of recently reported works regarding the essential on-chip modelling approaches is stated which can be used for any research intending to take advantages of using these emerging methods and to address their challenges. Furthermore, a device-level comparison of different types of these techniques is provided.

Chapter 3 "Fractional Modelling For Interconnect System": presents a new introduction for interconnect delay time in the fractional order domain as well as a general expression for RLC interconnect network model in CMOS technology based on a second order approximate transfer function.

Chapter 4 "Ultra-Low Power Driver Scheme Incorporating a Bootstrap Configuration": proposes low power driver based on a bootstrap technique that has been implemented to produce circuit design where simulation results of this circuit are compared with conventional one from point of view energy and power consumption.

Chapter 5 "Conclusions and Future Work" outlines the conclusions of the study and explore the implications of the presented work and draw the horizon for prospective future research.

Figure 1.2: Thesis organization.

The information in this chapter is intended to present the reader with the basic concepts behind interconnect circuitry to understand the motivation and the choices made in the context of this work.

#### 2.1 INTRODUCTION

Internet of Things (IoT) as a multidisciplinary paradigm, where almost every object around us will be connected and networked through miniature computing systems, has evolved to Internet of Everything (IoE) which is shaping the society and creating multiple industries [99, 178]. This calls for unusual breakthroughs in a number of disciplines of the entire stack such as designing, modelling and other disciplines [28].

The industry of semiconductors will continue to be a key enabler of this paradigm mainly through miniature computing systems and sensors [99]. Many devices, including embedded devices, in the realm of IoT generally need an energy-efficient hardware due to the limitation of the energy budget. Hence, ultra-low-power System-on-Chip (SoC) is widely used to enable portable devices powered by batteries [178].

The modern digital system comprises sets of chips on boards, sets of circuit boards placed in framework and frameworks housed in a rack. At every single level of the structure, signals are transmitted and received on different types of interconnections. However, this communication is mostly implemented by traditional global interconnects through multiplexers and buffers for high-speed, which have a high-power consumption. Given low-power consumption is a major requirement, scaling down the supply voltage to the voltage of the transistor threshold serves reducing energy [154]. Yet, doing so causes significant interconnect delay because of the exponentially decreased current of drivers in sub-threshold [55]. On the other hand, upsizing the drivers does not assist much because the delay depends on the

transistor size linearly, but exponentially on the supply voltage in the sub-threshold [55, 154].

A good device model is essential in the analysis and design of interconnect circuits in deep submicron complementary metal-oxide-semiconductor (CMOS). Interconnect is a term used for the wiring utilised to connect the active components within the integrated circuit (IC). Its purpose is to convey clock and other signals and deliver power/ground to the circuit/system functions on a CMOS chip [61, 21]. According to the signal frequency and wires length, it is determined whether or not the wires should be treated as a transmission line [61].

The ideal wire refers to the interconnect that is treated as a lossless equipotential circuit, which is a reasonable assumption. The actual wire, however, representing a load to the signal driver needs time for the signal to deliver information and it drains power. The non-ideality, as an inherent property, of the wire introduces parasitics which depend on the wire's dimensions. Also, depending on the fall (rise) times of the signals with which they are gated along the wire properties, the electrical circuit model of the interconnect differs [116]. This will be discussed in Section 2.2.2 after underlining the basic concepts behind the analytical model. This chapter, also, introduces basics and fundamental concepts related to interconnect circuits. Section 2.6 reviews the the three main techniques of on-chip interconnect modelling; Section 2.7.1 implements a case study, in a comparison of selected cases, then a section for studying the impact of inserting fractional elements has been presented, after that, a section for introducing the modelling of the interconnect, while the final section is the conclusion.

#### 2.2 BASICS OF ON-CHIP INTERCONNECTIVITY CIRCUIT

#### 2.2.1 Analytic Modelling

Wires of on-chip interconnect structure are considered to be composed of four main parasitic components; resistance (R), capacitance (C), inductance (L) and conductance (G). These parts are used to model the wiring which is extremely useful in timing investigation, particularly in assessing the interconnect delay. The discussion, in this section, follows the description in [144].

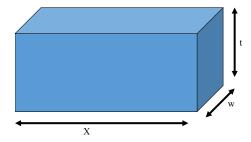

RESISTANCE: a conductor with rectangular cross-sectional, as shown in Figure 2.1, is a reasonably good approximation for an on-chip wire whose length is X. The resistance R of such a simple strip of material is obtained by [20]

$$R = \frac{\rho}{tw}X\tag{2.1}$$

where t and w are the thickness and the width of the interconnect, respectively, and  $\rho$  is the resistivity of the material. Since the thickness t is often one for each technology, it is usual to incorporate the resistivity and the thickness into a single constant named the sheet resistance ( $R_q$ ) of the material, given as.

$$R_{q} = \frac{\rho}{t} \tag{2.2}$$

Then the resistance is given by

$$R = \frac{R_q}{w} \tag{2.3}$$

The sheet resistance ( $R_q$ ) provides the resistance of a square cross-section of a specific material for a constant height. Several materials such as silver, aluminium and copper are used as conductors. Although silver has the lowest conductivity, its high cost implies that it is implemented only for special applications. On the other hand, the most regularly used is aluminium, which is economically the best, and copper which is more expensive but has better conductivity [20].

However, for higher complexity structures including combinations of round and square cross-sections, curves and corners, the resistance is assessed by using tools known as field solvers. Such tools are used to accurately extract parasitics by solving Maxwell's equations in 2 and 3 dimensions [63].

Figure 2.1: Cross sectional dimensions of a conductor.

Also, it is important to be aware that it is common to treat the resistor ideally but this is not always the case. In high frequencies, the current density with depth into the conductor is not uniform but drops away exponentially because of the skin effect phenomenon [61]. A cut-off frequency of this phenomenon can be determined, and an empirical approximation for it is given as [46]

$$f_{c} = \frac{\rho}{\pi \mu \delta_{c}^{2}} \tag{2.4}$$

where  $\mu$  refers to the permeability, and  $\delta_c$  to the skin depth. Less than this frequency, the current is supposed to be spread consistently across the whole cross-sectional area of the conductor leading to a frequency-independent resistance given in (2.3), whereas above the cut-off frequency the resistance increases with the square of the frequency.

CAPACITANCE: the capacitance is the ability of the metal conductor to store an energy in electric field form between its surface and another surface. The value of this capacitance is given by

$$C = \frac{Q}{V} = \frac{\iint_{s} \varepsilon \vec{E} d\vec{S}}{\int_{c} \vec{E} d\vec{I}}$$

(2.5)

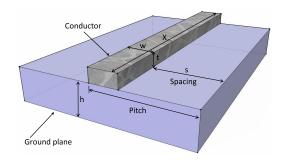

where the Q is the charge stored by the conductor, E the electric field and S is a closed surface. In an interconnection architecture, this appears between a metal part under interest and its surrounding such as the ground and power planes, other wires and substrates. Assuming the E field is entirely contained within the two surfaces, the capacitance of the microstrip line structure given in Figure 2.2 can be calculated as follows

$$C = \frac{w\varepsilon}{h}X\tag{2.6}$$

The equation (2.6) underestimates the parasitic capacitance of a wire if applied to the excessive aspect ratio (h/w) wires in DSM technologies. Also, it does not reflect how strong the function is between the parasitic capacitance and the geometry. Therefore, tools known as 3-D field solvers are required to take into account the fringe components of the E field to the capacitance and to obtain an accurate value [63]. However, over the years, empirical formulas have been developed with fair accuracy, and are very

Figure 2.2: Structure of a conductor.

important in understanding the consequence at system level [203]. For instance, an evaluation for the capacitance between the wire and ground plane  $C_g$  based on curve fitting approach is given in [175] as

$$C_g = \varepsilon [1.15(\frac{w}{h}) + 2.4(\frac{t}{h})^{0.222}]$$

(2.7)

This value in addition to mutual capacitance  $C_c$  is used to determine a total capacitance for a conductor surrounded by two adjacent conductors, as follows

$$C_T = C_g + 2C_c \tag{2.8}$$

The total capacitance obtained by this equation is in good agreement with that predicted by the field solver. But it is still inaccurate as the ratio (h/w) continues to decrease. Also, the individual components are not destined to provide the total decomposition into the ground and coupled components since the presence of the adjacent wires significantly affects the electric field around the middle conductor. Since then, formulas which better partitioned the components into coupling components and ground have been reported in [42, 122, 216]. They are in effect a modification of equations in [175] to render the decomposition more accurate, which can be suitably used for parasitic extraction of Deep submicron (DSM) geometries as reported in [83]. These equations have been reproduced in [83], as follows

$$C_f = \varepsilon[0.075(\frac{w}{h}) + 1.4(\frac{t}{h})^{0.222}]$$

(2.9)

$$C_f' = C_f[1 + (\frac{h}{s})^{\infty}]$$

(2.10)

$$C_{q} = C + C_{f}' + C_{f} {(2.11)}$$

where  $C_f$  and  $C_f^{'}$  refer to the fringing components with and without a surrounded conductor, respectively and  $\varpi$  is a curve fitting constant computed from a database of values produced by a field solver. The values of  $C_f^{'}$  and C are per unit length. These formulae 2.5, 2.11, 2.9 and 2.10 are deemed to be convincing where their accuracy is reported [144, 83] to be over 85% of the actual value when the following inequalities are satisfied

$$0.3 < \frac{w}{h} < 30$$

$0.3 < \frac{t}{h} < 10$   $0.3 < \frac{s}{h} < 10$  (2.12)

INDUCTANCE: the parasitic inductance is a measure of the distribution of the magnetic field created by the current passing through the conductor. The basic definition of the inductance is

$$L = \frac{\oint BdS}{I} \tag{2.13}$$

where B denotes the magnetic field induced from the current I. This parasitic depends on the global surrounded more than the parasitic capacitance. That is clear in the definition where this equation yields self-inductance if S is induced in the same circuit. Whereas it defines mutual inductance in case of S following another conducting track. The loop created by the signal wire and the return path, which is fundamentally in the power distribution network, can potentially extend to hundreds of micrometers away from the wire under study. Therefore, the extraction of parasitic inductance for a given wire is vastly complicated, as it depends not only on the features of that specific wire, but also probably on the features of thousands of other wires. Thus, it would appear that expensive 3-D numerical methods are required for good accuracy.

To overcome this problem, the concept of partial inductance approach is reported for the first time in [165]. This technique avoids the need to define the return loop by assuming the current

return at infinity. Hence, this causes the inductance to be only dependent on the geometry of the wire. Later, this approach was simplified and a close form solution had derived to the following [155]

$$L_{s} = \frac{\mu_{0}}{2\pi} \left[ X \ln(\frac{2X}{w+t}) + \frac{X}{2} + 0.2235(w+t) \right]$$

(2.14)

$$L_{m} = \frac{\mu_{0}}{2\pi} \left[ X \ln(\frac{2X}{d}) - 1 + d \right]$$

(2.15)

where  $L_m$  and  $L_s$  are mutual and self inductance, respectively,  $\mu_0$  is the permittivity of the dielectric and d is the distance between the centres of the two wires under study. However, the best precise evaluation can be achieved by field solvers such as FASTHENRY [187] and a 3-D inductance extraction tool which are popular and available for free.

#### 2.2.2 Electrical level modelling

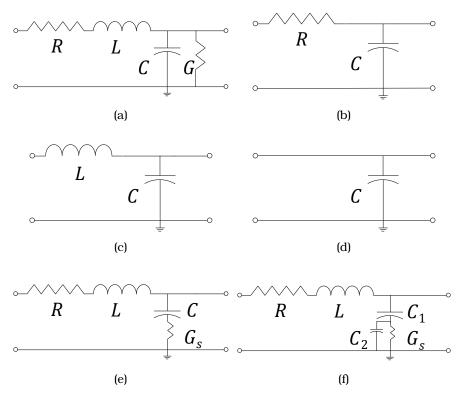

Equivalent lumped element circuit approximations can be used to illustrate the interconnection properties. Also, it can be assumed that those circuit elements are constant throughout all time and frequency, but such an assumption can not always apply. Figure 2.3a shows a lumped element circuit approximation of an RLGC interconnection. The propagation behaviour of a large number of these two-port circuits, that are chained together, can resemble the behaviour of its equivalent interconnection [130].

Generally, propagation along a general RLGC interconnection is described by partial differential equations [43] as follows

$$\frac{\frac{\partial \nu(x,t)}{\partial x} + L \frac{\partial i(x,t)}{\partial t} + Ri(x,t) = 0}{\frac{\partial i(x,t)}{\partial x} + C \frac{\partial \nu(x,t)}{\partial t} + Gi(x,t) = 0}$$

(2.16)

Conventionally, one or more of the terms in these equations (2.16) can be neglected, depending on the signal frequency and on values of interconnection parasitics R, L, G and C. Accordingly, different propagation models result, while the more prevalent models are listed in Figure 2.3.

Figure 2.3: Lumped element approximations for propagation classes: (a) RLGC propagation, (b) RC propagation, (c) LC propagation, (d) tracking propagation, (e) and (f) propagation of resistive substrate.

- RC propagation dominates over other propagation models particularly for silicon metal-oxide-semiconductor (MOS) technologies. This class is used in a case of very fine line width, which results in a large R, and closely situated to the ground line, which results in a large C and a small L. With the absence of G and L terms in (2.16), as shown in Figure 2.3b, the diffusion partial differential equation is applied [131].

- Transverse electromagnetic (TEM) propagation or LC propagation class includes the L and C terms, shown in Figure 2.3c, as wL >> R. This type of interconnection is a lossless transmission line. It is preferred over the RC class because of its faster, i.e., wave-like propagation. Therefore, efforts have been made to guarantee this class in Wafer Scale Integration circuitry, typically by elevating the interconnection over the ground plane. This class exists in Gallium-Arsenide technologies. However, decreasing the R term below wL with

typical switching speeds and dimensions of MOS technologies is not easy to achieve [131].

- However, it is satisfactory to consider the interconnection such a single node which propagates signal instantaneously if its time constant is much shorter than the one of the input signal. Figure 2.3d illustrates the class of tracking propagation where a single lumped capacitor is used to model the entire interconnection [167].

- There is a transition region, as one would expect, between the former two propagation classes when the inductive and resistive components have similar magnitudes. This class exhibits wave-like propagation but has considerable resistive component as lossy transmission lines. For instance, [214] investigated the signal propagation on metal strips on top of a highly resistive silicon substrate. Owning to the non-ideal ground plane, the transmission line model more resembles propagation classes in Figure 2.3e and 2.3f. In addition, [87] reported some speed advantages to a lossy substrate. Though, this is resulting in more challenging differential equations.

#### 2.2.3 Importance of Transmission Line (TL) effect

In the past, until 1990s, wavelength of digital signals was much more than the electrical lengths of on-chip interconnects. This is due to the on-chip digital performance being under 1GHz and that the run length was relatively short. Therefore, a lumped circuit of RC model was adequate to simulate the interconnect circuit [61]. Nevertheless, recently, this has altered because of significant improvements in the performance of IC, which affects not only digital circuits but also analog circuitry [178]. Mainly, these developments are in two directions; speed and dimension. Regarding the speed, faster circuits have been developed with multiple on-chip clocks global of a few Gigahertz and local of approximately 10GHz [61]. Larger chips of around 2cm have been constructed with fine lithography resulting in longer interconnects owing to cross-sectional measurements of less than a micron [61]. As a consequence for these changes, the RC modelling became applicable in some cases only [18]. In recent years, there has been a growing number of studies that consider the issue of whether inductance should be included in the interconnect model [21, 96, 98, 196]. Though their investigations were in different ways, the obtained expressions are for the most part equivalent. This discussion reconfirms the conclusions in [144]. From the signal timing point of view, to consider the circuit as the transmission line, it has to satisfy the inequalities, that is

$$\frac{t_r}{2\sqrt{lc}} < X < \frac{2}{r} \sqrt{\frac{l}{c}} \tag{2.17}$$

where  $t_r$  is input signal slew rate, l,c,r are per unit length parasitic of the wire with X length. Whereas the wire conductance to ground can be ignored for the most of Very Large Scale Integration (VLSI) circuit applications. Now from the standpoint of the qualitative sense, in the first inequality, the gating signal is quite slow for the combined capacitive and inductive reactance to compete with the resistance. If not, the link has to be sufficiently long for the delay at the speed of light in the medium to be comparable to the rise time. However, on the other side of the inequality, if the link is too long, the loss is quite enough to conceal the inductive effect. If not, and the reactance at the highest frequency of operation (determined by the driver's output rise time) is comparable with the series resistance, the inductance effects cannot be ignored.

The transmission line effect drew the attention of a vast number of researchers and this will be discussed concisely in the next section and more in Section 2.5.

#### 2.2.3.1 Importance of TL in fractional order domain

The effect of the transmission line has become more significant, especially in global interconnects, with increasing on-chip signal frequencies. Equations (2.16) describes this effect and were solved for the first time by Heaviside [85]. Fundamentally, this classical model considers that the magnetic effects are represented by the serial inductive elements, and likewise, parallel capacitive elements can be used to model capacitive phenomena. The energy losses during the transmission, which are commonly in the form of current leakage and voltage drop, are modelled by means of parallel conductive and serial resistive, respectively. The derived result of that is Telegrapher's equations which can

fully be fitted for plenty of practical applications [48].

Nevertheless, these equations may not be sufficient to handle certain effects, such as memory effects in magnetization and polarization processes and the effect of accumulation of electrical charge on the wire. Neglecting such effects was well understandable which is based on particular circumstances considering large-scale structures and signals with a low frequency. However, this must be re-considered when dealing with modern VLSI systems. For the purpose of addressing this, numerous models of transmission line have been developed recently. Many studies have utilized fractional elements rather than traditional elements. Accordingly, different generalization models have been developed-the most prevalent models are listed below.

- The time fractional Telegrapher's equations were considered in [140, 40] by means of numerical and analytical methods on bounded and unbounded domains, while the forcing term is presented in [107]. The time-fractional of this equation has been studied with only two different orders of fractional differentiation zero and two [16]. On the other hand, [38] considered multi-term time-fractional Telegrapher's equations to obtain the highest derivative in processes of diffusion type. In this study, a fractional differentiation with n order has been assumed, where n is an integer. Furthermore, [47] developed an analytical and numerical scheme for the one dimensional and two dimensional.

- The space fractional Telegrapher's equations have been considered in [141, 86]. [141] analysed and discussed the fundamental solution of the equation with fractional order between zero and two using Fourier transform. [86] introduced a procedure for applying the matrix to solve the equation in fractional domain in space and time, one at time, using the wavelet approach.

- The space and time fractional Telegrapher's equations were considered in [68, 34], where fractional Laplacian was used to solve the equation, which is assumed comprising of two fractional variables with two different orders of time-fractional derivatives. In [153], a similar assumption was examined using the method of the joint Laplace and Fourier transform. [33] and [207] used the same method

Figure 2.4: A simple interconnect structure.

but proposed the case of two different sequential orders of time-fractional derivatives with a non-symmetrical space fractional derivative.

#### 2.3 INTERCONNECT SYSTEM LIMITATIONS

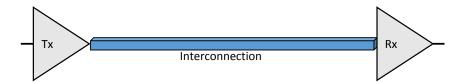

The circuit model is extremely valuable for designing and analysing a new circuit and estimate the performance of the present techniques. To understand design environment simply, it should probe the parameters of devices (transmitter and receiver) and wires (interconnection), as illustrated in Figure 2.4. For that, it would be convenient to study their inherent attributes separately and then combining the results together to have an integrated model.

#### 2.3.1 Fundamental limits

In this section, unchanged and immutable limits of interconnect are discussed which are fundamentally based on principles represent the physical world. These limits cannot be changed with the increase of device structure complexity, novel circuits techniques, or inventive architectures [49, 129].

The first fundamental limit is based on Shannon's communication theorem related to the capacity of the channel, where the equation below represents the maximum channel capacity  $C_{b/s}$  with effect of a white Gaussian thermal noise [180]

$$C_{b/s} \leqslant B_{r} \log_{2} \left( 1 + \frac{P_{s}}{kTB_{r}} \right) \tag{2.18}$$

where  $B_r$  is the bandwidth of the receiver,  $P_s$  is the average signal power of the input,  $kTB_r$  is the Johnson thermal noise power delivered to a matched load, k is the Boltzmann's constant  $(1.38*10^{-23}\text{J/K})$ , and T is the room temperature (300 K). It can

be concluded the minimum energy per bit  $E_{b(min)}$  by assuming  $E_b = P_s/C_{b/s}$  and based on (2.18) [49]:

$$\mathsf{E}_{\mathsf{b}(\min)} = \mathsf{ln}(2)\mathsf{kT} \tag{2.19}$$

This is the minimum energy transfer of a binary transmission on interconnect, less than that makes the transition undifferentiated from the white noise and whatever the encoding techniques to error correction used. This energy also governs the limitation of a lowest swinging on buses.

Secondly, the function of interconnect is to transmit signal swinging events which are normally generated by computational elements. Therefore, the essential limit on interconnect performance is established by the shortest delay between a switching event in a transmitter and a transition detected at a receiver, with the assumption that interconnect is lossless and noise free to find the shortest delay. The speed of transmission is generally known depending on the speed of an electromagnetic wave propagating in free space which is quantified by Maxwell's equation, Then Helmholtz derived an equation that describes the propagation of the electric field and formed free space wave travelling speed  $C_0$  to [102]

$$C_{o} = \frac{1}{\sqrt{\mu_0 \varepsilon_0}} \tag{2.20}$$

where  $\mu_0$  and  $\epsilon_0$  are the permeability and the permittivity of free space, respectively. Then the speed of the communication between the transmitter and the receiver should not exceed the latency  $\tau$  of the channel [183]. Hence,

$$\tau \geqslant \frac{X}{C_0} \tag{2.21}$$

This fundamentally means that the electromagnetic propagation in free space limits interconnects performance.

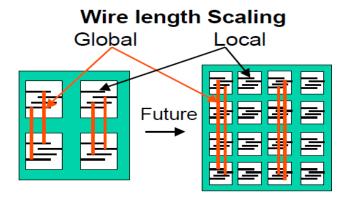

## 2.3.2 Limitations of the device

The basic MOS scaling principle started by Dennard [52], who predicts how IC operating ranges and layouts will alternate as inevitable enhancements in IC technology occur. The principle assumes a proportional scaling down in all dimensions; the

reduction amount is denoted by  $S_\tau > 1$ , where any dimension  $X \to X' = X/S_\tau$ . It additionally assumes retention of constant electrical fields, leading to a voltage reduction by  $\nu' = \nu/S_\tau$ . According to this scaling theory, we are able to predict interconnection propagation times for a scaled design. By recalled (2.1) and (2.6), the change in line resistance and capacitance can be calculated respectively as

$$R' = \rho \frac{X'}{t'w'} = S_r R \tag{2.22}$$

$$C' = \varepsilon \frac{w'X'}{h'} = \frac{C}{S_r}$$

(2.23)

Since R'C' = RC, the interconnection propagation times defined by the RC product remain firm. The scaling theory precisely predicts that interconnections will not gain in speed, MOS transistors do. Time delay constant  $\tau$  of a distributed RC is given by

$$\tau = rcX^2 \tag{2.24}$$

where X is interconnect length, r and c are the distributed resistance and capacitance per unit length, respectively. This equation clearly shows that the delay of an unbuffered long link is quadratic in its length. From these arguments, it can be concluded unquestionably that the latency value of interconnect will not change despite interconnect ideally minimized. In other words, the negative effect of the interconnect on performance would not mitigate in spite of a new emerged technologies as a result of not only its transistors numbers is increase but also die area as shown in Figure 2.5. Without changing this scenario, interconnection delay will remain dominant in the scaling process.

# 2.3.3 Limitations of the circuit

To this end, the interconnect issues have been listed separately. Hence, to have the understanding of interconnect circuit limitations, an assumed basic model with main involved parameters has been used. The approach, in this section, deals with a single

Figure 2.5: global interconnect effect with new generations.

interconnect. Also, it does not taken into consideration the noise impacts and accuracy was sacrificed for simplicity in order to deduce the main factors that affect the performance of such a system.

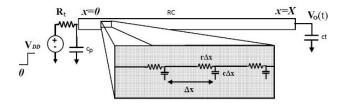

The model shown in Figure 2.6 consider a line with RC distributed parameter that is driven by a simple inverter has loaded with capacitor of  $c_t$  and an internal resistor of  $R_t$  with neglecting source capacitance  $c_p$  considering C compensates this parasitic. This model imitates a point-to-point interconnect on single-layer driven by a CMOS device and connected to the next gate. We have assumed this model because it is used over a wide range of VLSI design theories [20]. In addition, the effects of the line inductance has been deliberately ignored. Since, in the approach here, what is important is the impact of the line RC delay and not the characteristic impedance of signal lines in VLSI circuits [20]. At this point, as an intuitive prediction from the model, it is clearly elucidated from the structure that the transistor parameters have an impact on the line and the crosstalk issue.

For this interconnection, a differential equation can be given as:

Figure 2.6: RC interconnect model with resistive source and capacitive load.

$$\frac{\partial^2 V}{\partial x^2} = rc \frac{\partial V}{\partial x} \tag{2.25}$$

where r and c are the unit length resistance and capacitance of interconnect respectively. The far end voltage can be revealed in a form of an expanded series. This technique was presented in [171, 172] to describe the system in Figure 2.6 as follows

$$\frac{V_{o}(x,t)}{V_{DD}} = 1 - \exp\left(-\frac{\frac{T_{d}}{RC} - 0.1}{R_{T}C_{T} + R_{T} + C_{T} + 0.4}\right)$$

(2.26)

where  $T_d$  is the delay time,  $R_T = R_t/R$ , and  $C_T = c_t/C$ . Rearranging the (2.26) by solving  $T_d$  in term of V a formula can be obtained [172] for the delay time  $t_V$  from the initial (t=0) to the time when far end voltage reaches ( $V_o/V_{\rm DD}$ ). Hence,

$$t_V = RC[0.1 + ln(\frac{1}{1 - V_o/V_{DD}})(R_TC_T + R_T + C_T + 0.4)]$$

(2.27)

This form can be simplified by assuming a large interconnect. Thus, its capacitance C will be the most effective capacitance component (i.e.,  $c_t << C$ ) and transistor equivalent resistor will be the dominant (i.e.,  $R_t >> R$ ). Then, to find the approximation circuit delay, the RC distributed model has been combined in [176] and the time of transient voltage on interconnect model in [49] to produce

$$T_d = 2.3R_tC$$

(2.28)

From this equation, it can be concluded that there are main factors affecting the performance of the system. These factors are the line capacitor, which is proportional to the interconnection dimensions, and the transistor resistance, which is a function of its size. In simple words, it clearly illustrates the most effective components that govern the operating point for a particular wire length. These components can be classified into technology-dependent parameters, such as  $\epsilon$ , conductor width and hight from the ground, and the parameters of the operation point which are related to the relevant transistors.

#### 2.4 POWER IN CMOS CIRCUITS

CMOS can be in two different states; a dynamic state during the signals or clocks transitions and a static state during no transitions [20, 157]. Accordingly, power dissipation sources are divided in two major classes: dynamic and static. These two components have an essential difference that is the former proportional to the switching frequency and the activity in the network, whilst the latter is independent of both. Normally, dynamic power P<sub>d</sub> outweighs static power but, recently, leakage has emerged as a major power component, particularly, in subthreshold systems and nanometre technologies where the device size down-scaling has led to very thin gate oxides [209]. Therefore, both should now be treated alike. The model shown in Figure 2.6 will be proposed, since it includes the most effective system components [20], where the total power P<sub>T</sub> for that system is

$$P_{\mathsf{T}} = P_{\mathsf{d}} + P_{\mathsf{l}k} \tag{2.29}$$

where  $P_{lk}$  represents the leakage power, which can be presented as following [191]

$$P_{lk} = V_{DD}I_{lk} \tag{2.30}$$

where  $I_{lk}$  is typically a particular fabrication technology parameter, as it is originating in the substrate conduction and affected by the sub-threshold voltage [209]

$$I_{1k} = 1.5I_{off}W_t$$

(2.31)

where  $W_t$  is the transistor width and  $I_{\rm off}$  is the transistor current in off state which depends on  $V_{\rm DD}$  and the size of the devices [191]. Depending on these formulae, it is apparent that the solution to reduce the leakage power dissipation is scaling down the supply voltage, the main contributor to the leakage power. This is based on an ideal assumption that when the transistor is a turned-off switch, the current between drain and source is zero, while in fact, this is not the case. Whereas the weak-inversion current  $I_{\rm off}$ , occasionally called sub-threshold leakage, is proportional to  $V_{\rm gs}$ . In other words, the voltage scaling-down has to be within some trade-off according to the report in [157, 209],

which classify the reducing supply voltage as the major reason causing the drain-source leakage to increase exponentially, as provided approximately by:

$$I_{off} = I_0 \times 10^{(V_{gs} - V_{th}/S_{th})}$$

(2.32)

where  $I_0$  is the current when  $V_{gs} = V_{th}$ ,  $V_{th}$  is a threshold voltage and  $S_{th}$  is the sub-threshold swing where the drain current changes 10 times to  $V_{gs}$  change.

Secondly, power consumed during circuit switching activity is generally represented by [21]

$$P_{\rm d} = \alpha_{\rm g} C_{\rm eff} V_{\rm DD}^2 f \tag{2.33}$$

where  $\alpha_a$  represents activity factor that its value is 0.15 [21],  $C_{eff}$  is equivalent the circuit capacitance, in this case (C,  $c_p$  and  $c_t$ ), and f is the operating frequency.

Finally, it is often assumed that the N-type metal-oxide-semiconductor (NMOS) and P-type metal-oxide-semiconductor (PMOS) transistors of a CMOS gate do not become ON at the same time, but such an assumption is certainly not correct, as the finite slope of the input signal during transient produces a direct current path between supply voltage and ground for a short period of switching time  $T_{rise}$ . The power dissipation due to these short-circuit currents  $I_{sc}$  is proportional to the switching activity as well as the ratio between the slopes of the input and output signals as shown in following equation [157]

$$P_{sc} = \alpha_a T_{rise} V_{DD} I_{peak} f \qquad (2.34)$$

where  $I_{peak}$  is the peak current which depends highly on  $V_{DD}$  [191] unlike  $I_{off}$ . This part of power considerably impacts the receiver circuits among the interconnect components, since it is highly dependent on the input signal slope [188].

In conclusion, based on the study for driving circuits parameters, it is certain that the intrinsic circuit power dissipation can be effectively reduced by scaling down the supply voltage.

# 2.4.1 Ultra-Low-Power (ULP) techniques for driving on-chip interconnect

In the past, the power issue was neglected and designers concentrated on performance, cost, chip area and reliability. This has changed due to the demands on emerging applications for low power and not high performance, for example in portable devices, wireless sensor networks, self-powered devices and biomedical systems [56, 78]. These applications are required to be lower in weight with longer energy source life, and to have no cooling systems. Since reduced power consumption could achieve these aims, the trend to use circuits with Ultra-Low Power (ULP) budgets seems to be the solution [56]. In the same work, it is reported that sub-threshold design shows the ability to meet the needs of the ULP design. The sub-threshold system means designing the circuits to operate in a supply (V<sub>DD</sub>) no more than the transistor threshold voltage  $(V_{th})$  [56]. This approach has emerged as the best way to fulfil energy efficiency [115], because of the reduction in sub-threshold's current driving compares to superthreshold's current and the dynamic power strongly depends on  $V_{DD}$ , see equations (2.29) and (2.33).

However the sub-threshold circuit has a frequency limited to tens of MHz [115], while in the conventional circuits the switching is at hundreds of MHz [100, 188]. This subject has received great research attention recently as an essential part of IoT requirements [78, 31, 10]. Nevertheless, with new generations of scaled technology, challenges of design reliability and the tradeoff between having an energy-efficient system or one with low performance are among the major concerns in this subject [10].

There are many studies that have initiated utilising the low power consumption links as several industrial, standardization bodies are actually involved in the activity of development of solutions to fulfil the technological requirements [17]. The efforts regarding the LoT paradigm are varied and came from different scientific areas. Specifically, however, the approaches concerning on-chip interconnect circuits and the system's power dissipation can be classified into data link layer and higher techniques, physical layer techniques, and both [183]. The challenges in this field are varied, nevertheless what is important is the way to deal with these issues and the results would obtain. Designers

trying to cope with this issue have to deal not only with power dissipation, but also parasitic impedance, link delay, CMOS buffer design among other issues [56].

# 2.4.1.1 Link layer techniques

These techniques achieve power saving in network-on-chip (NoC) by using coding to modify the transmitted data, in a way, to minimize the data transition activity that takes place through interconnects. However, these techniques will not be discussed here as they are beyond the scope of this thesis.

# 2.4.1.2 Physical layer techniques

On the other hand, equation (1.1) gives designers an obvious platform for prospective schemes to satisfy the demand for an energy-efficient system, to:

- optimize the spacing and sizing of wires;

- adapt the repeaters, driving and driven circuits' design;

- reduce the supply voltage that provides the power for interconnects drivers and repeaters.

Low swing signalling is a powerful method to minimize the energy consumed due to that energy is directly related to  $V_{DD}$  and  $V_{swing}$ , but with trading off to raise the latency [183, 56, 78]. This has led many researchers [93, 198, 161] to explore this solution and have achieved roughly five-fold improvements in energy consumption for interconnect circuits with certain frequency [93].

However, using signals with low voltage swing requires a special receiver design to sense these small changes in voltage level [198]. Furthermore, other researchers have cleverly combined this technique and conventional methods [161] to design adaptive link voltage scaling systems. Through adaptive voltage scaling not only is the magnitude of voltage changed but also the operating frequency is altered to meet a varied performance to the same system. Jeong et al. [105] reported that their adaptive technique led to an improvement of 43% in power saving compared to traditional techniques.

Another group of developers [121, 73, 208, 54] have implemented a dual voltage buffer technique. Some of these [121, 73]

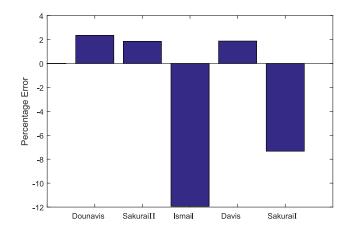

used two transistors with different threshold voltages in designing the buffer, reporting around a 40% improvement compared to a single threshold. This method is called dual  $V_{\rm th}$ . Others [208, 54] used a dual supply voltage (low and High  $V_{\rm DD}$ ) and achieved approximately 50% reduced power consumption by interconnects compared to single supply voltage methods. Ho et al. [210] introduced an interconnect driver that reduces the static leakage current by using a bootstrapped inverter and an active reduction technique.