$\mu$ Systems Group

School of Engineering

Newcastle University, UK

# Energy-Efficient Mixed-Signal Multiplier Design using Memristive Technologies

**Shengqi Yu**

Supervisors:

Dr. Rishad Shafik

Prof. Alex Yakovlev

A thesis submitted for the degree of

Doctor of Philosophy

24th March 2022

# Abstract

Energy efficiency and performance are two of the most important design considerations for computing applications, e.g., artificial intelligence at the edge and Internet of things empowered by limited energy supply from batteries or energy harvesters. For these applications, arithmetic computation is key, with multiplication and addition being the “must-have” core functionalities. Traditional approaches to these are primarily based on cascaded logic chains with long carry propagation circuits that contribute to high energy consumption and latencies. Additionally, these circuits exploit digital interfaces at both inputs and outputs, which require complex signal conversion circuits when designed using analogue methods. This thesis presents original research focused on developing low-energy and high-speed multiplication hardware. The core technology developed in this work is a novel digital-in/analogue-out mixed signal multiplication method based on a single-bit multiplication cell. The cell consists of a resistive memory bit controlled by a transistor switch. The single-bit memory cell is implemented using memristor devices, which provide non-volatile storage and avoid capacitive or inductive elements. This type of single-bit multiplication cell takes two single-bit input operands (multiplier and multiplicand). One (e.g., the multiplier) is encoded in the form of a Boolean voltage and the other (e.g., the multiplicand) is encoded in the memristor’s conductance, also set to Boolean values. The cell current then encodes the Boolean product following the Ohm’s Law. The single-bit multiplication cells are then assembled into multi-bit multipliers using a crossbar matrix structure, which directly implements the long-multiplication algorithm. Across the crossbar, Kirchhoff’s Current Law ensures that the cell currents are summed up to form the final overall product, forming a digital-in/analogue-out mixed signal design. The entire Ohm’s law-Kirchhoff’s Current Law operation is instantaneous in the absence of capacitive and inductive elements. With Kirchhoff’s Current Law,

this type of mixed-signal multiplier eliminates the need for passing carries to the left. This saves both time and energy compared with conventional digital amplifiers, which need costly and potentially long logic chains for carry handling. By using multiple memristors in an single-bit multiplication cell, costly current mirrors can be avoided from the crossbar. The core digital-in/analogue-out multiplication method can have direct applications in Internet of things nodes, like multiplying digital-to-analogue converters. One advantage of using the proposed multiplier in this application comes from the asymmetry between the two input operands. One of them, saved in memoristor conductances, is the best changed less frequently than the other, represented by voltages, precisely what an multiplying digital-to-analogue converter aims for. This digital-in/analogue-out multiplier is further developed into a digital-in/digital-out multiplier with reduced output precision, with the same bit width for both the operands and the product.

We envisage our design will be useful in applications where multiple multiply-and-add units are assembled into larger structures, such as in neural networks. With the same bit width for both inputs and outputs, multipliers of this design can be cascaded a straightforward manner for larger networks. The multiplier designs are implemented in 65 nm technology using Cadence Virtuoso based analogue simulations. The designs are shown to have significant speed and energy advantages over existing state of the art and the machine learning experiments demonstrate the correctness and usability of the reduced-precision multiplication scheme for artificial intelligence applications.

# Contents

|                                                                     |            |

|---------------------------------------------------------------------|------------|

| <b>Abstracts</b>                                                    | <b>i</b>   |

| <b>List of Figures</b>                                              | <b>vi</b>  |

| <b>List of Tables</b>                                               | <b>x</b>   |

| <b>List of Acronyms</b>                                             | <b>xiv</b> |

| <b>Acknowledgments</b>                                              | <b>i</b>   |

| <b>Publications</b>                                                 | <b>1</b>   |

| <b>1 Introduction</b>                                               | <b>1</b>   |

| 1.1 Challenges in Emerging Applications . . . . .                   | 1          |

| 1.2 Energy-efficient Multiplier Design . . . . .                    | 3          |

| 1.3 Research Questions and Contributions . . . . .                  | 5          |

| 1.4 Thesis Layout . . . . .                                         | 6          |

| <b>2 Background and Literature Review</b>                           | <b>8</b>   |

| 2.1 High Performance Arithmetic Circuit Design Techniques . . . . . | 8          |

| 2.1.1 Multiplication Circuit Design . . . . .                       | 8          |

| 2.2 High-speed Analogue-to-digital Converter . . . . .              | 10         |

| 2.2.1 Flash Analogue-to-digital Converter . . . . .                 | 10         |

| 2.2.2 Current Mirror . . . . .                                      | 11         |

| 2.2.3 Complementary Metal–Oxide–Semiconductor Current Comparator    | 13         |

| 2.2.4 Thermometer Code to Binary Encoder . . . . .                  | 14         |

| 2.3 Memristors . . . . .                                            | 15         |

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| 2.3.1    | Memristor Physical Models . . . . .                                     | 17        |

| 2.3.2    | The Voltage ThrEshold Adaptive Memristor Model . . . . .                | 21        |

| 2.3.3    | Transistor Memristor Cell Design . . . . .                              | 23        |

| 2.4      | Memristor-based Multiplier Design for Energy Efficiency . . . . .       | 23        |

| 2.5      | Current-mode Arithmetic . . . . .                                       | 25        |

| 2.6      | Multiplying Digital-to-analogue Converters . . . . .                    | 25        |

| 2.7      | Neural Networks . . . . .                                               | 26        |

| 2.8      | Summary . . . . .                                                       | 27        |

| <b>3</b> | <b>Transistor-memristor Crossbar Multiplier with Current Amplifiers</b> | <b>28</b> |

| 3.1      | Single Transistor Single Memristor Multiplier . . . . .                 | 30        |

| 3.1.1    | Algorithm for the Crossbar Multiplier . . . . .                         | 30        |

| 3.1.2    | Crossbar Multiplier Architecture . . . . .                              | 32        |

| 3.1.3    | Single Transistor Single Memristor Cell . . . . .                       | 36        |

| 3.1.4    | Current Amplification . . . . .                                         | 40        |

| 3.1.5    | 4-bit Crossbar Multiplier Implementation . . . . .                      | 41        |

| 3.2      | Simulation Results . . . . .                                            | 42        |

| 3.3      | Summary . . . . .                                                       | 49        |

| <b>4</b> | <b>Memristive Multiplier Design with In-cell Current Multiplication</b> | <b>51</b> |

| 4.1      | Number Representation and Encoding . . . . .                            | 53        |

| 4.2      | Single Transistor Multiple Memristors Multiplier . . . . .              | 58        |

| 4.2.1    | Baseline Design . . . . .                                               | 58        |

| 4.2.2    | Technology Improvements . . . . .                                       | 60        |

| 4.3      | Simulation Results . . . . .                                            | 62        |

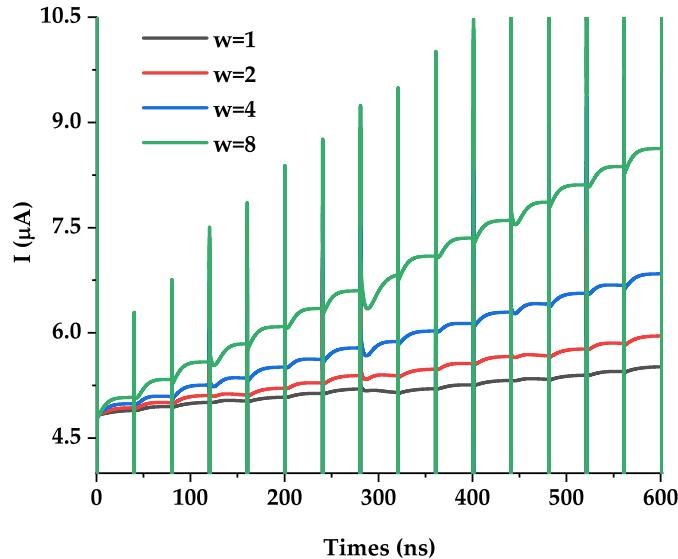

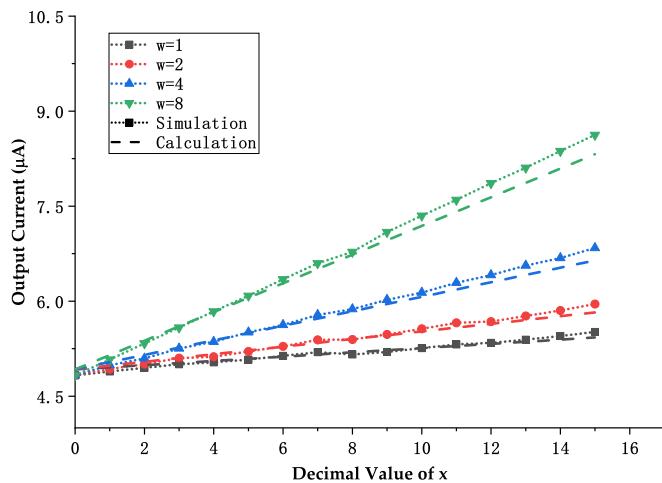

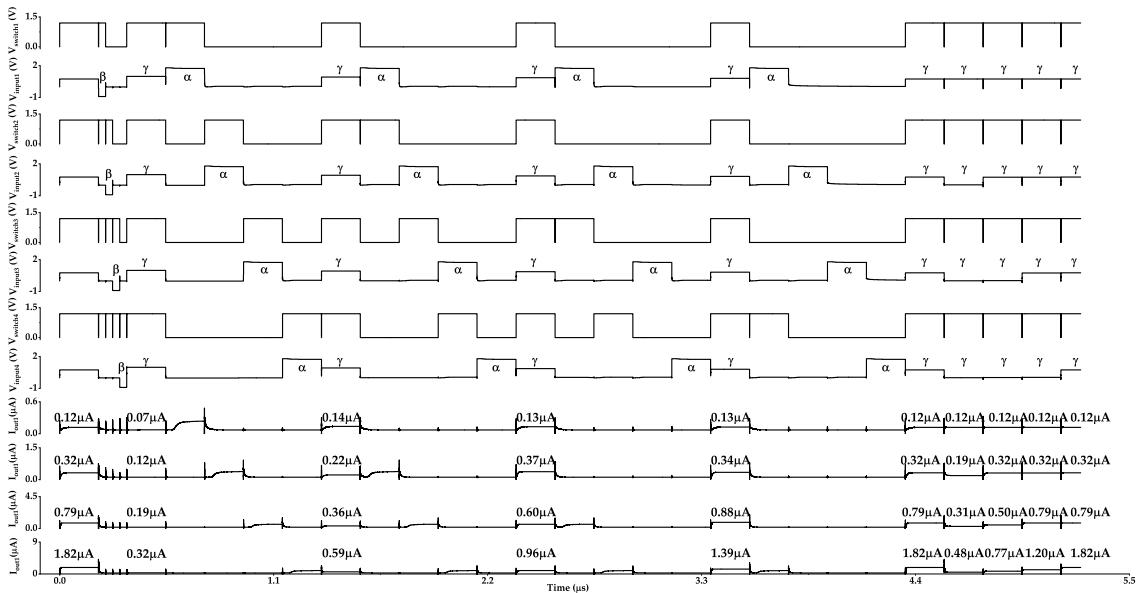

| 4.3.1    | Cell Performance on Crossbar . . . . .                                  | 66        |

| 4.3.2    | Case Experimental Study: 4-bit Multiplier . . . . .                     | 67        |

| 4.3.3    | Results and Comparisons . . . . .                                       | 68        |

| 4.4      | Summary . . . . .                                                       | 73        |

| <b>5</b> | <b>Memristive Multiply-accumulate Unit for Neural Networks</b>          | <b>75</b> |

| 5.1      | Multiple-transistor Multiple-memristor Multiplier . . . . .             | 78        |

|                     |                                                                                    |            |

|---------------------|------------------------------------------------------------------------------------|------------|

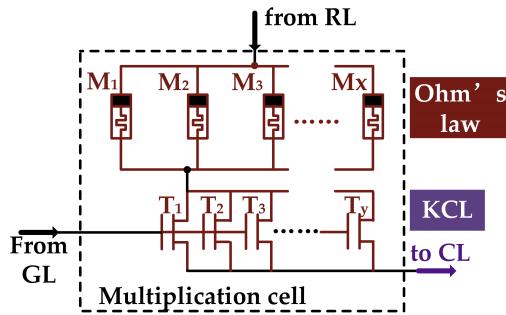

| 5.1.1               | Resistive Multiple Memristors Multiplication Cell . . . . .                        | 78         |

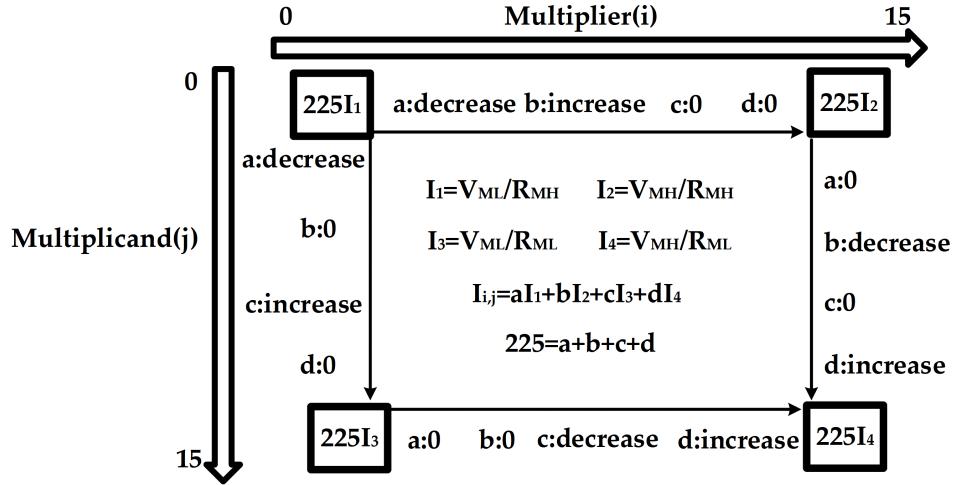

| 5.1.2               | Crossbar Multiplier Current Identification . . . . .                               | 80         |

| 5.2                 | Analogue-to-digital Conversion . . . . .                                           | 83         |

| 5.2.1               | Thermometer Code Generating Current Comparator . . . . .                           | 84         |

| 5.2.2               | Thermometer Code to Binary Encoder . . . . .                                       | 85         |

| 5.3                 | Neural Network Implementation . . . . .                                            | 85         |

| 5.3.1               | Quantization-aware Training Analysis . . . . .                                     | 86         |

| 5.4                 | Simulation Results . . . . .                                                       | 89         |

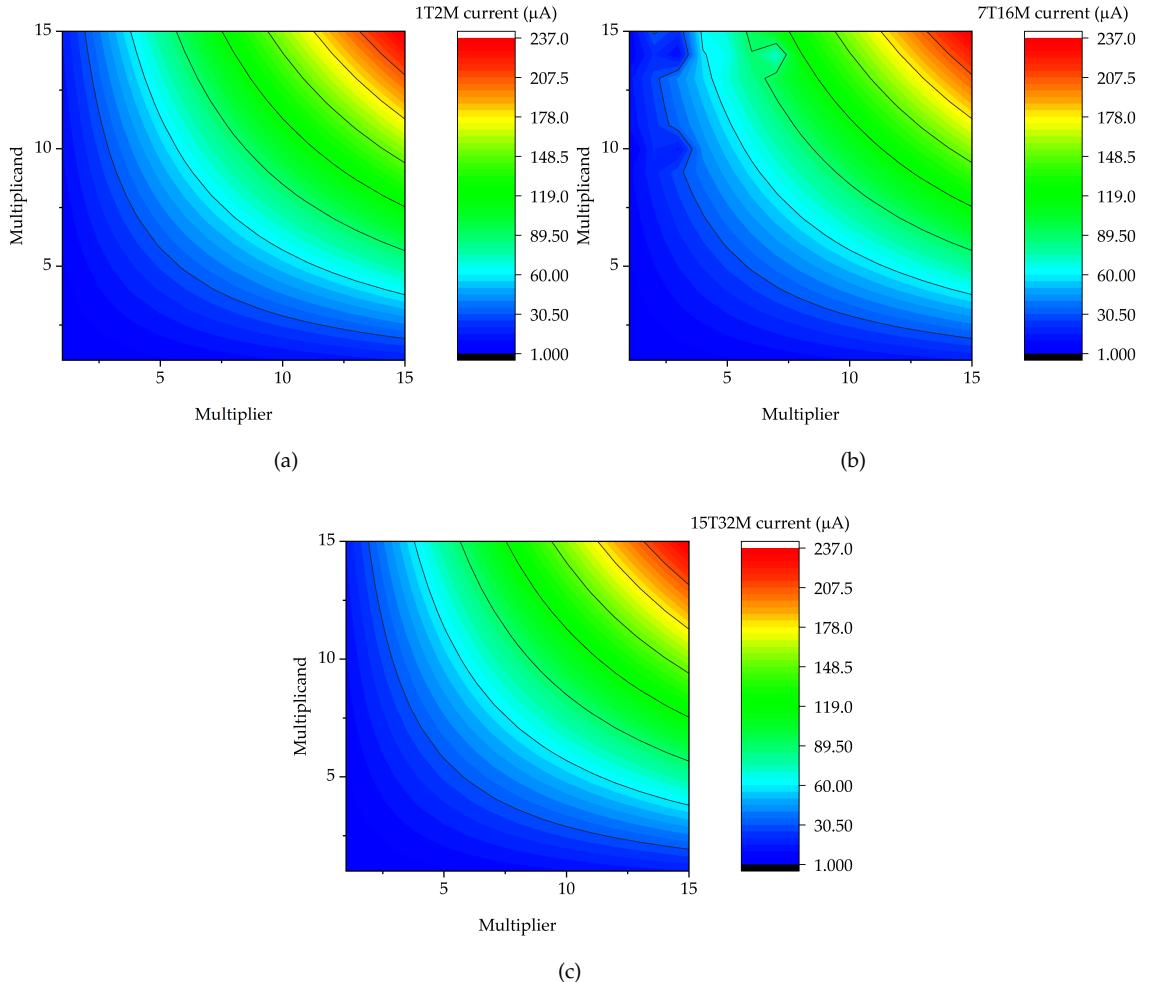

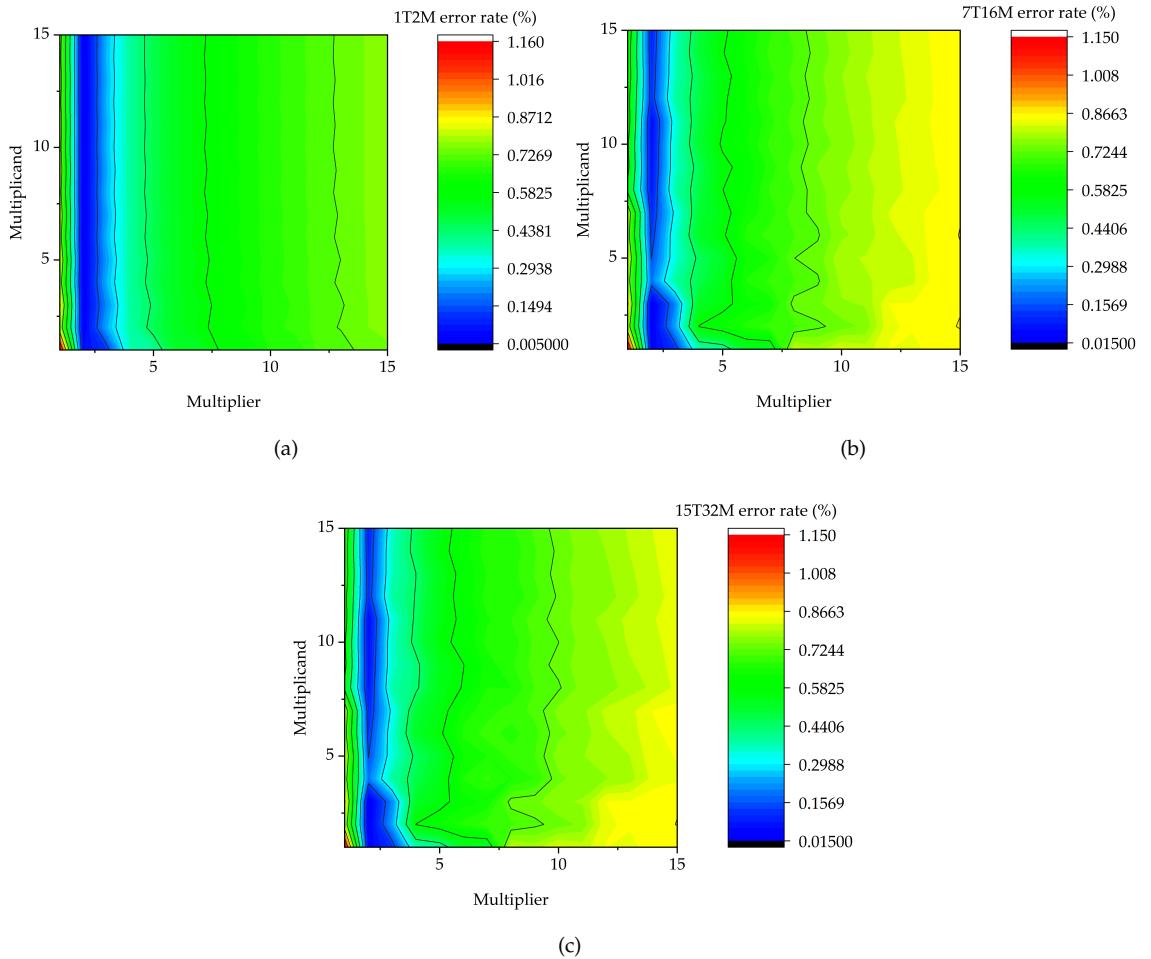

| 5.4.1               | Multiple Transistors Multiple Memristors Multiplication Cell Performance . . . . . | 89         |

| 5.4.2               | Crossbar Multiplier Performance . . . . .                                          | 90         |

| 5.4.3               | Energy Efficiency . . . . .                                                        | 93         |

| 5.4.4               | Neural Network Training and Results . . . . .                                      | 94         |

| 5.4.5               | Effects of Technology Parametric Variations . . . . .                              | 97         |

| 5.5                 | Summary . . . . .                                                                  | 100        |

| <b>6</b>            | <b>Conclusions and Future Work</b>                                                 | <b>102</b> |

| 6.1                 | Conclusions . . . . .                                                              | 102        |

| 6.1.1               | Contributions . . . . .                                                            | 102        |

| 6.1.2               | Limitations of the Research . . . . .                                              | 104        |

| 6.2                 | Future Work . . . . .                                                              | 105        |

| <b>Bibliography</b> |                                                                                    | <b>106</b> |

# List of Figures

|     |                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Block diagram of flash ADC. . . . .                                                                                                                                                                                                                                                                                                                                             | 11 |

| 2.2 | Circuit diagram of CM. . . . .                                                                                                                                                                                                                                                                                                                                                  | 11 |

| 2.3 | Circuit diagram of a current comparator thermometer code generator [35].                                                                                                                                                                                                                                                                                                        | 13 |

| 2.4 | Circuit diagram of ROM thermometer to binary encoder [35] [37] . . . . .                                                                                                                                                                                                                                                                                                        | 15 |

| 2.5 | Details of memristor internal state [38]. . . . .                                                                                                                                                                                                                                                                                                                               | 16 |

| 2.6 | TiO <sub>2</sub> memristor device architecture [38]. . . . .                                                                                                                                                                                                                                                                                                                    | 18 |

| 2.7 | Schematic of the fabricated Cu:ZnO memristor architecture [46]. . . . .                                                                                                                                                                                                                                                                                                         | 19 |

| 2.8 | Schematic of the transport mechanism of the forming free Al/Cu:ZnO/ITO/glass device [46]. . . . .                                                                                                                                                                                                                                                                               | 21 |

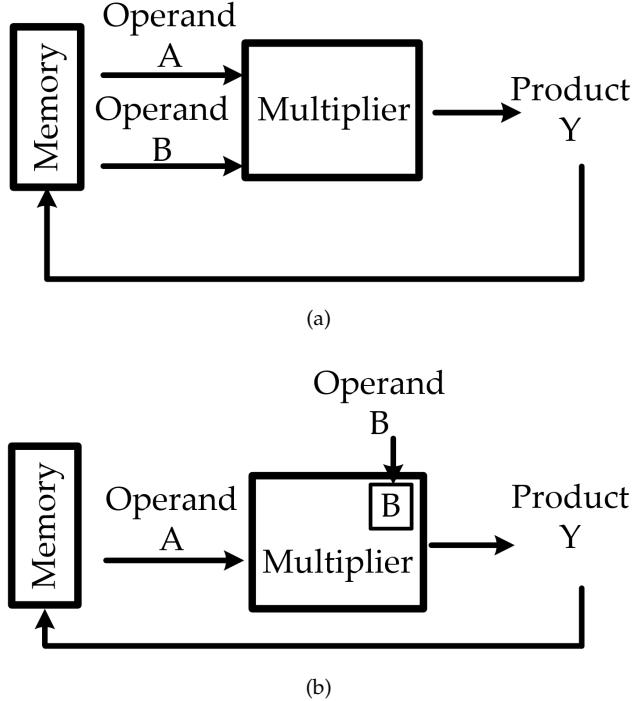

| 2.9 | Multiplication type. In (a), typical type. In (b), in-memory type. . . . .                                                                                                                                                                                                                                                                                                      | 24 |

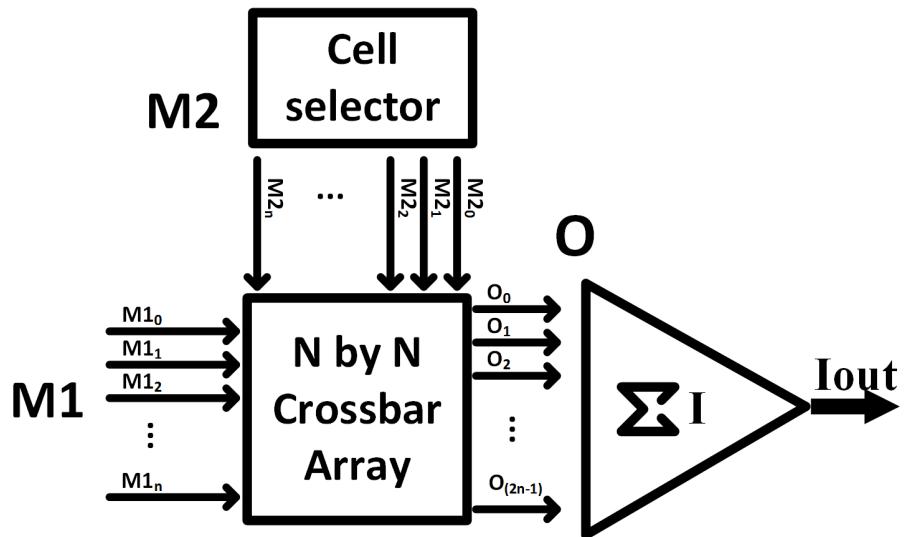

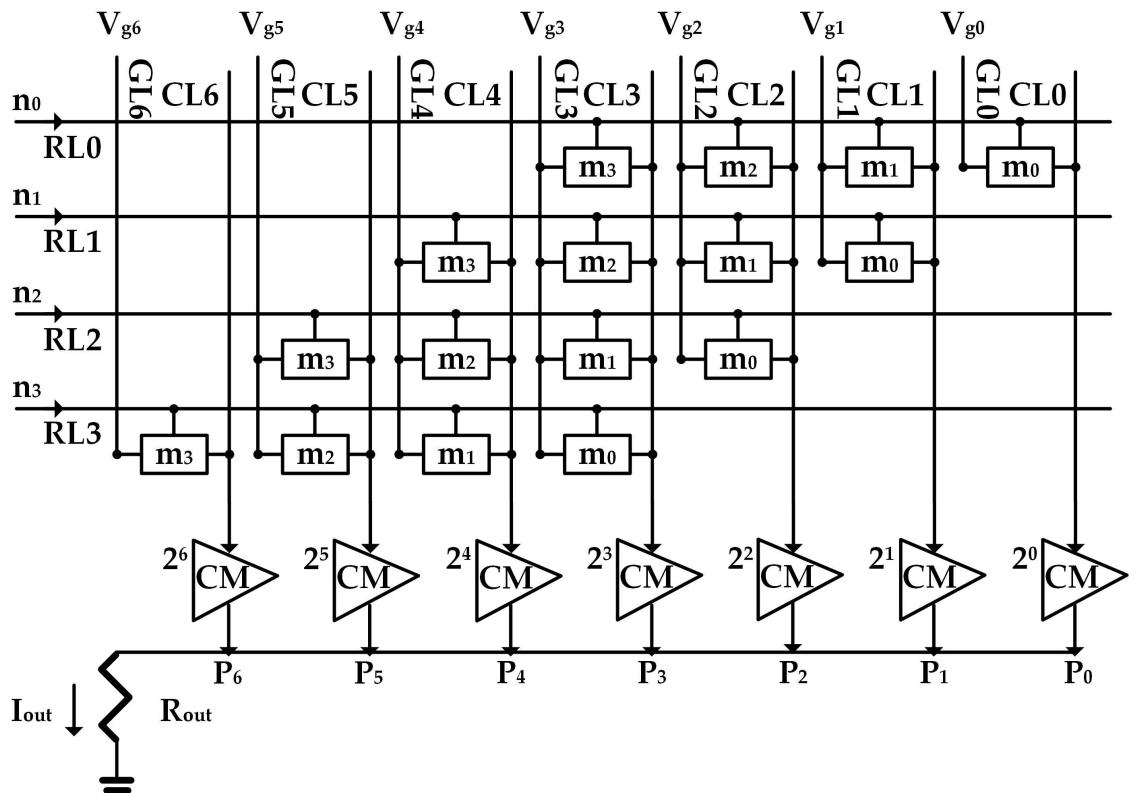

| 3.1 | Block diagram of the proposed mixed-signal carry-free current-mode multiplier. This diagram shows the connections between the different blocks of the proposed multiplier. The n-bit signals M and N generate a (2n-1)-bit result via multiplication; here, $M1_0$ means the first bit of M1, $M1_1$ means the second bit of M1, and the regulation also fits M2 and O. . . . . | 29 |

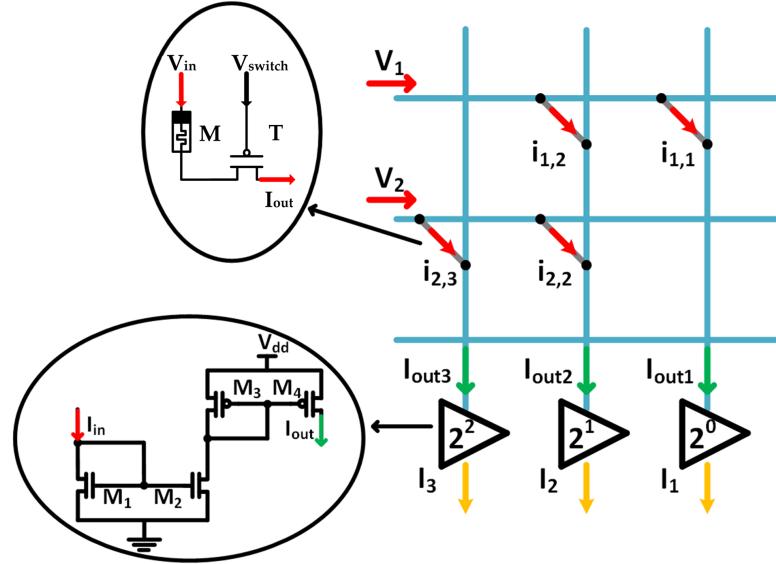

| 3.2 | Multiplier product generation and accumulation circuits. . . . .                                                                                                                                                                                                                                                                                                                | 33 |

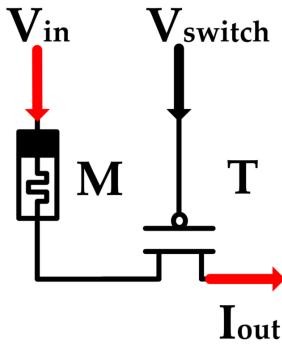

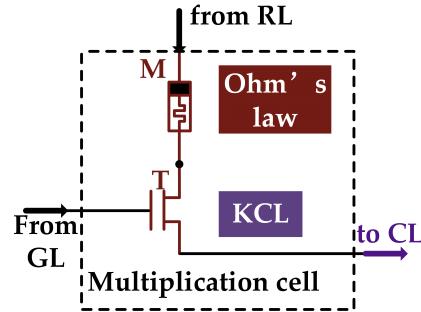

| 3.3 | 1T1M cell. This building block for the crossbar array consists of a memristor and a transistor. . . . .                                                                                                                                                                                                                                                                         | 36 |

| 3.4 | Responses of the memristor to writing biasing. In (a) and (b), under biasing by a DC voltage, the operations of writing logic 0 and logic 1, respectively, are shown. . . . .                                                                                                                                                                                                   | 38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4 Responses of the memristor to writing biasing. In (c), (d), (e), (f), and (g), the biasing pulses have the same amplitude but differ in their rise/ fall times, with voltage peak values of 3.5V/-3.5V. The pulse rise/fall time pairs are 10 ps/10 ps, 20 ps/20 ps, 30 ps/30 ps, 40 ps/40 ps, and 50 ps/50 ps, respectively. . . . .                                                                                                                                                      | 39 |

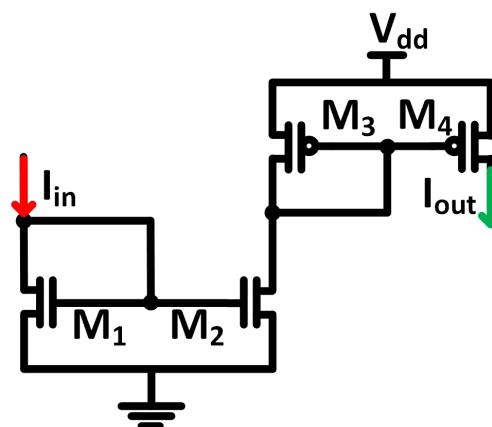

| 3.5 Multi-amplifier design for the current summer circuit. This design is built using an n-type CM that is series-connected to a p-type CM. . . . .                                                                                                                                                                                                                                                                                                                                            | 40 |

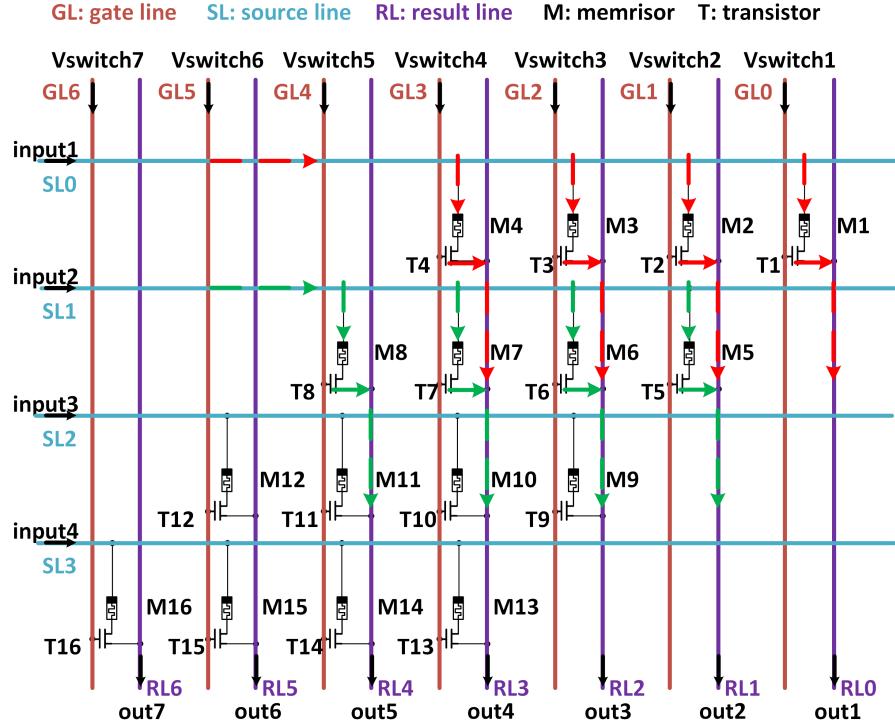

| 3.6 4 by 4 1T1M crossbar circuit with three line settings, one RL, and two parallel CLs that are defined to give the circuit the ability to select any cell within the circuit. . . . .                                                                                                                                                                                                                                                                                                        | 42 |

| 3.7 Multiplication performance for a 4-bit case. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

| 3.8 Writing and multiplying procedures of 1T1M crossbar multiplier. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                    | 45 |

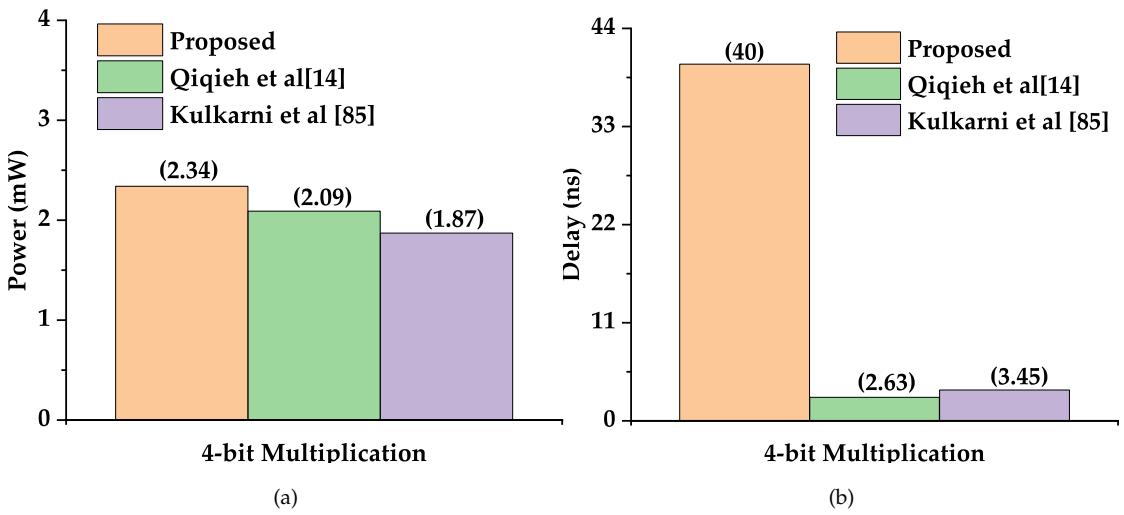

| 3.9 Comparative analyses of multiplier power, and delay. In (a), the power consumption of the proposed design is 2.45 mW, that of Qiqieh's approach [14] is 2.09 mW, and that of Kulkarni's approach [85] is 1.87 mW. In (b), the proposed multiplier shows a 40 ns delay, while Qiqieh's approach produces a delay of 2.673 ns, and Kulkarni's approach [85] shows a delay of 3.45 ns. . . . .                                                                                                | 47 |

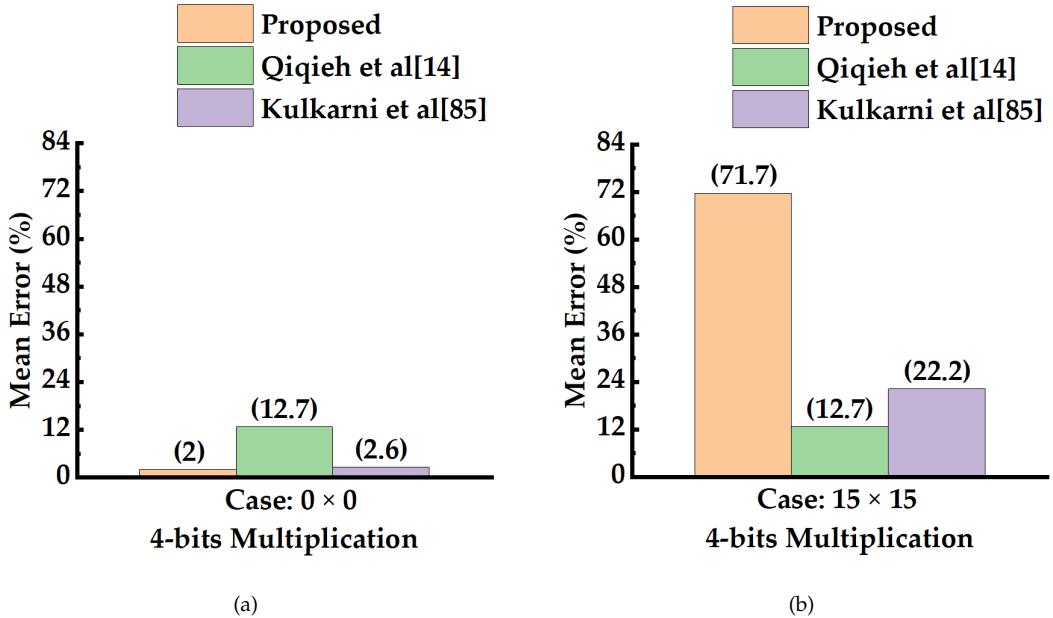

| 3.10 Comparative analysis of 4-bit multiplication accuracy. In (a), the low error level comparison results show that the proposed design has the lowest mean error (ME) at 2%, followed by that of Kulkarni at 2.6% with Qiqieh having the highest at 12.7%. In (b), the situation is reversed in the high error level comparison progress, with Qiqieh having the lowest ME at 12.7%, and Kulkarni still in the middle at 22.2%. The proposed multiplier shows the highest ME at 71%. . . . . | 48 |

| 4.1 The structure of 1T1M cell with updated details. Transistor is in n-type, memristor applied Cu:ZnO thin film. . . . .                                                                                                                                                                                                                                                                                                                                                                      | 52 |

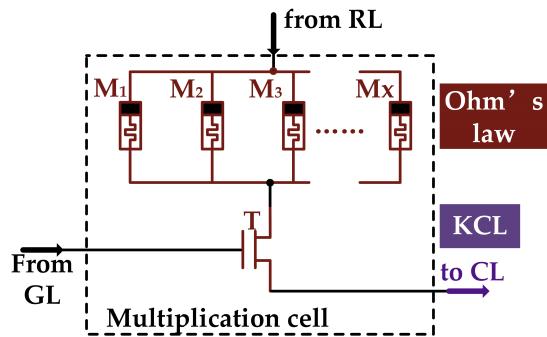

| 4.2 1TxM cell structure. For a cell along the current path for bit $i$ , $x = 2^{i-1}$ . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 52 |

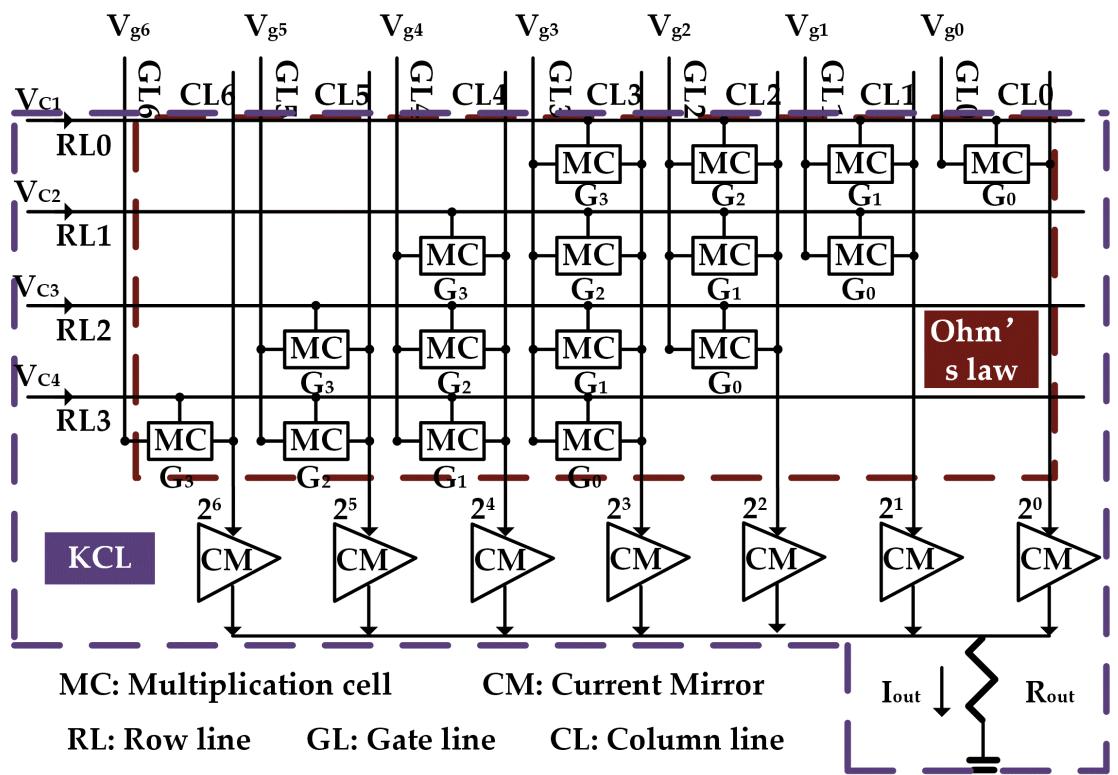

| 4.3 The architecture of 1T1M crossbar multiplier. The current amplification is implemented with CM. Each MC is a 1T1M cell described in Fig. 4.1, and a CM amplifier has one n-type CM and one p-type CM series connected. . .                                                                                                                                                                                                                                                                 | 55 |

|     |                                                                                                                                                                                                                                                                                                                                                                       |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4 | The mapping of numbers onto the crossbar structure with multiplication operands ( $M_1, M_2$ ) and final product ( $P$ ) . . . . .                                                                                                                                                                                                                                    | 56 |

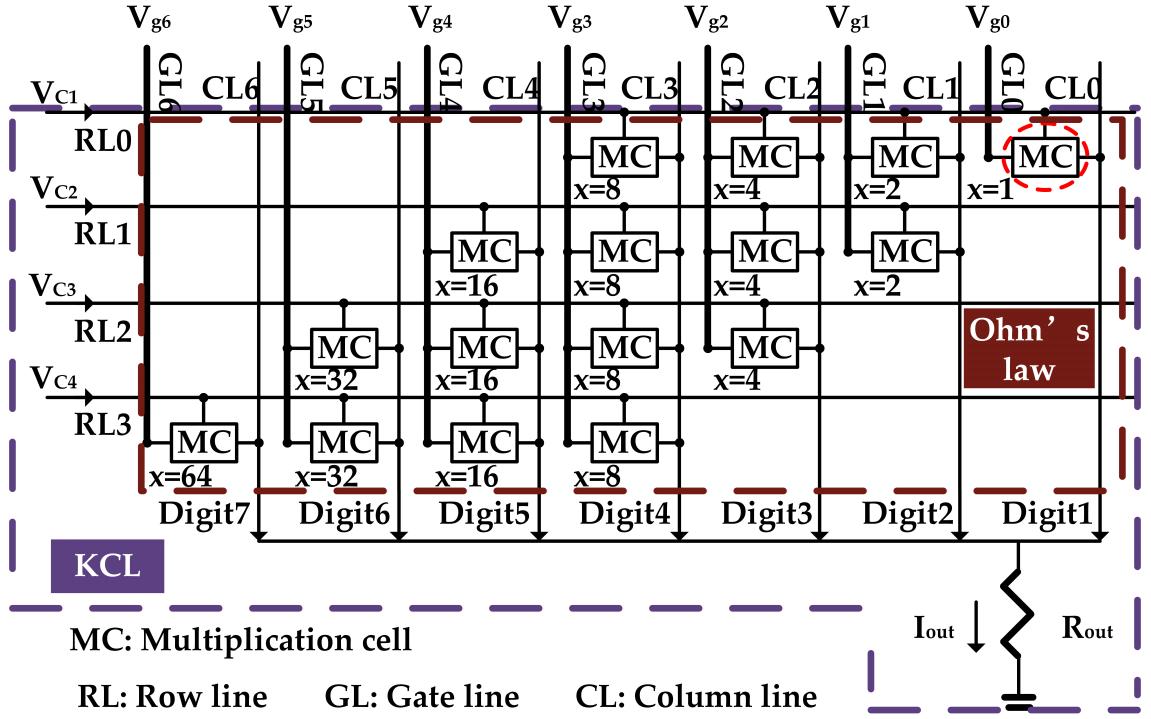

| 4.5 | The Architecture of 1TxM crossbar multiplier. The number of parallel memristors $x$ in a 1TxM cell is determined by its column location. . . . .                                                                                                                                                                                                                      | 59 |

| 4.6 | The 1TxM crossbar mapping with multiplication operands ( $M_1, M_2$ ) and final product ( $P$ ) . . . . .                                                                                                                                                                                                                                                             | 60 |

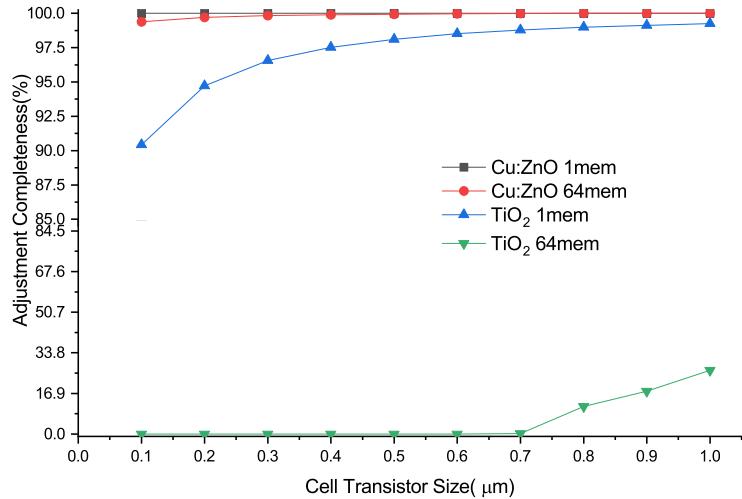

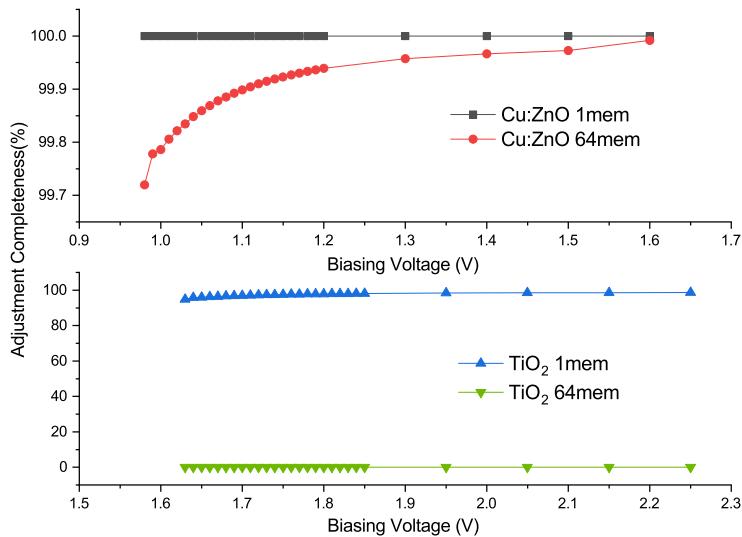

| 4.7 | The behaviour of the 1TxM cell. In (a), biasing voltages are set as $V_{TiO_2} = 1.85$ V and $V_{Cu:ZnO} = 1.2$ V, and length of transistor in cell is also fixed at 60 nm. In (b), transistor size is fixed at Width/Length = 500 nm/60 nm. For $TiO_2$ model and $Cu:ZnO$ model, the difference between biasing voltage and threshold voltage are the same. . . . . | 63 |

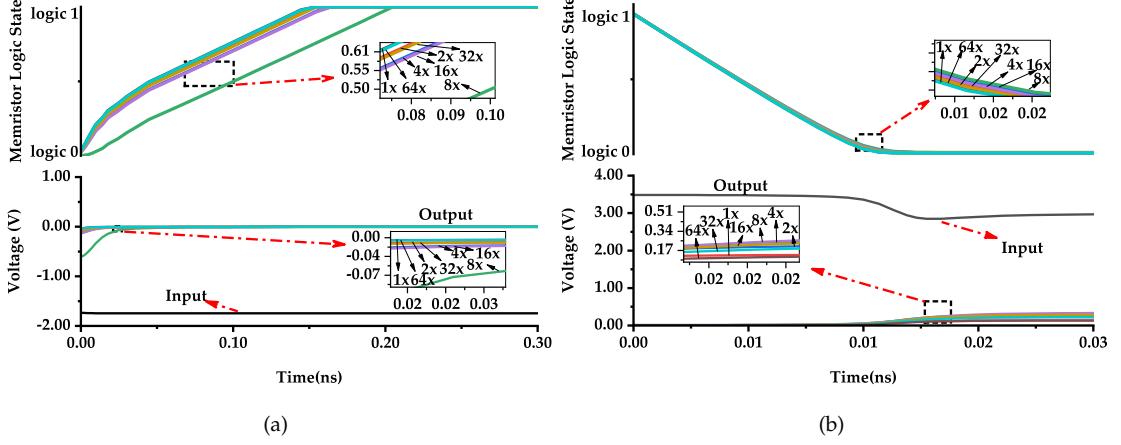

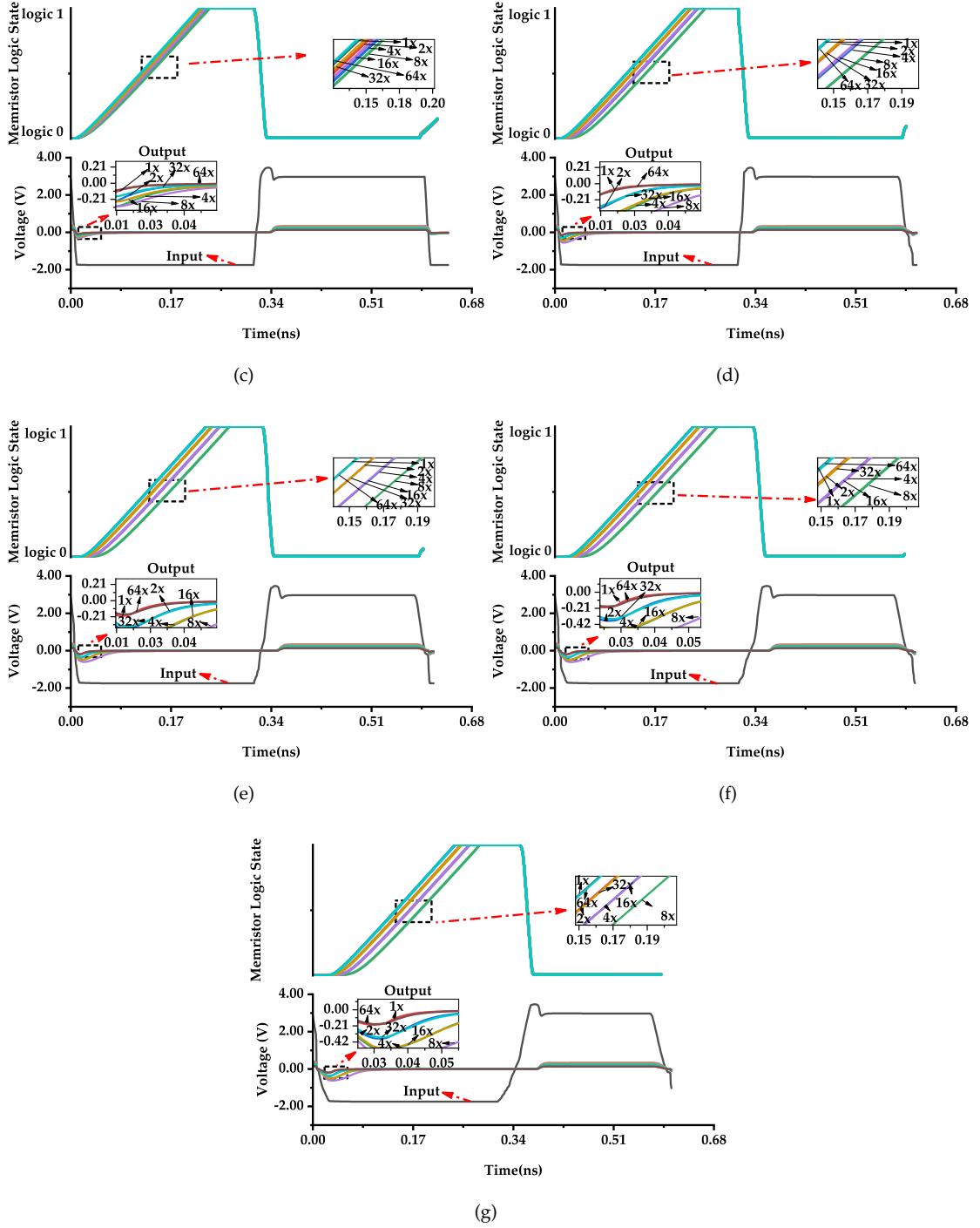

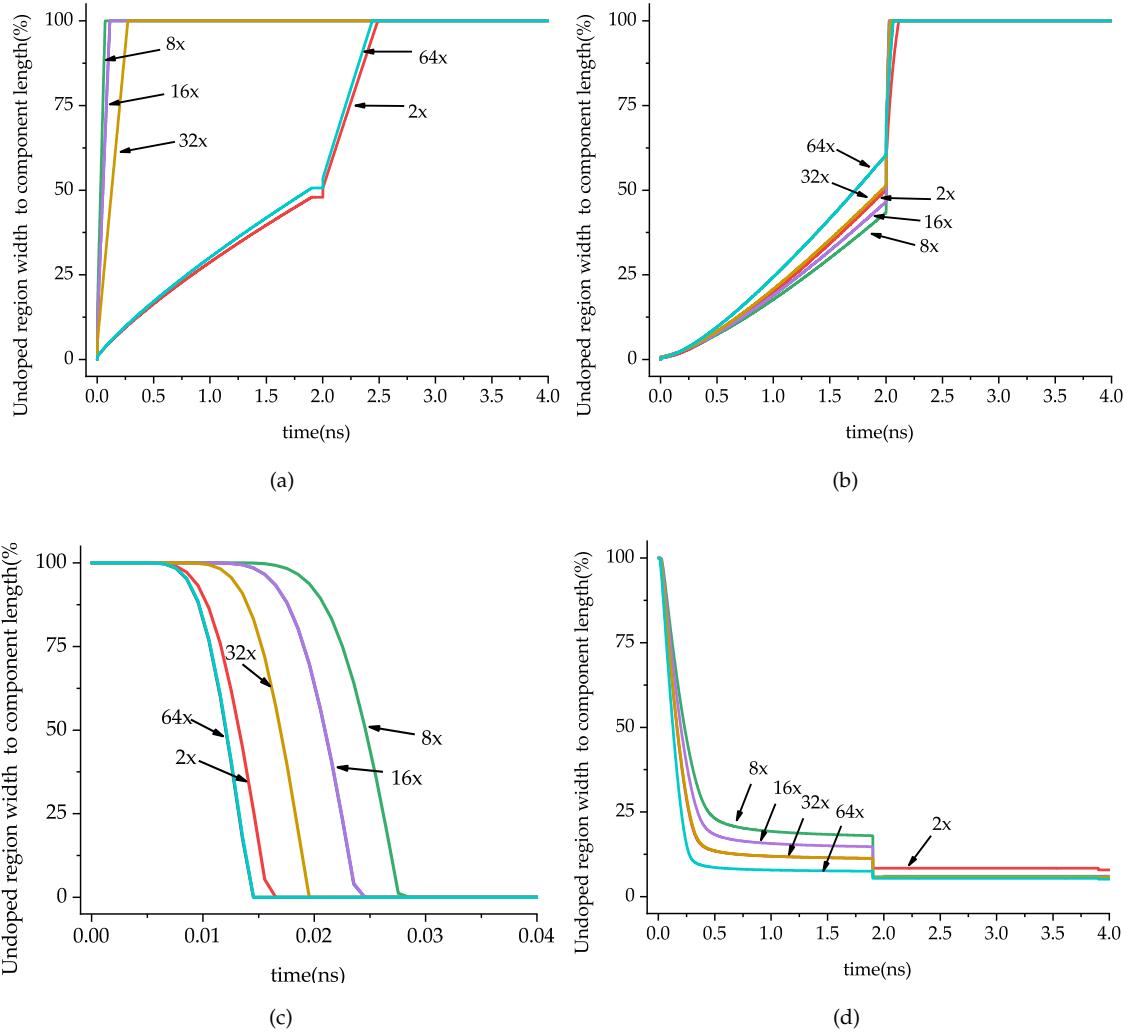

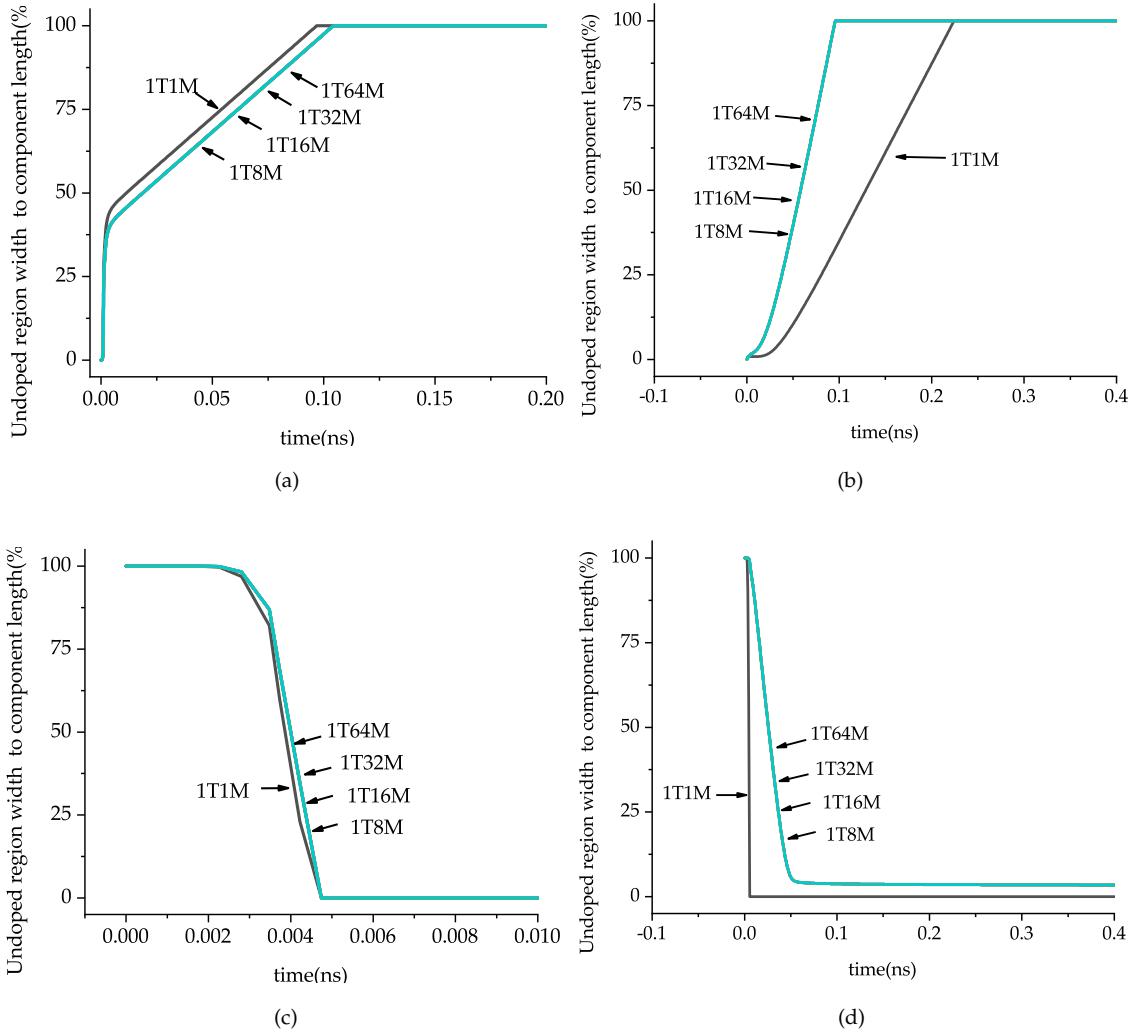

| 4.8 | The comparison of 1T1M crossbar writing operation. The writing has been presented in (a) to (d), and the amplification ratios are marked with number and "x". (a) presents $Cu:ZnO$ memristor writes 0, (b) presents $TiO_2$ writes 0, (c) presents $Cu:ZnO$ memristor writes 1, and (d) presents $TiO_2$ writes 1. . . . .                                           | 64 |

| 4.9 | The comparison of 1TxM crossbar writing operation. The writing has been presented in (a) to (d). (a) presents $Cu:ZnO$ memristor writes 0, and (b) presents $TiO_2$ writes 0, (c) presents $Cu:ZnO$ memristor writes 1, and (d) presents $TiO_2$ writes 1. . . . .                                                                                                    | 65 |

| 5.1 | The structure of MAC units. . . . .                                                                                                                                                                                                                                                                                                                                   | 77 |

| 5.2 | The structure of yTxM multiplication cell. . . . .                                                                                                                                                                                                                                                                                                                    | 79 |

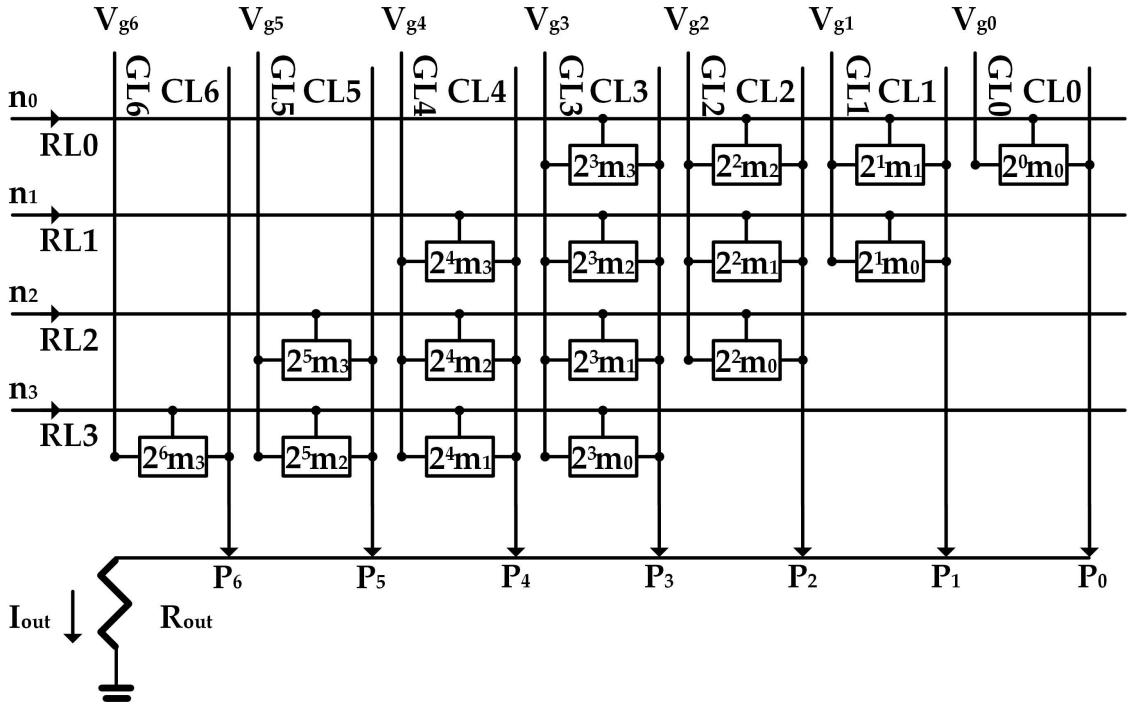

| 5.3 | The mapping of all multiplication output current. . . . .                                                                                                                                                                                                                                                                                                             | 82 |

| 5.4 | The yTxM MC output current mapping in all 4 by 4 multiplications. . . . .                                                                                                                                                                                                                                                                                             | 89 |

| 5.5 | The yTxM MC output current error rate mapping in all 4 by 4 multiplications. . . . .                                                                                                                                                                                                                                                                                  | 91 |

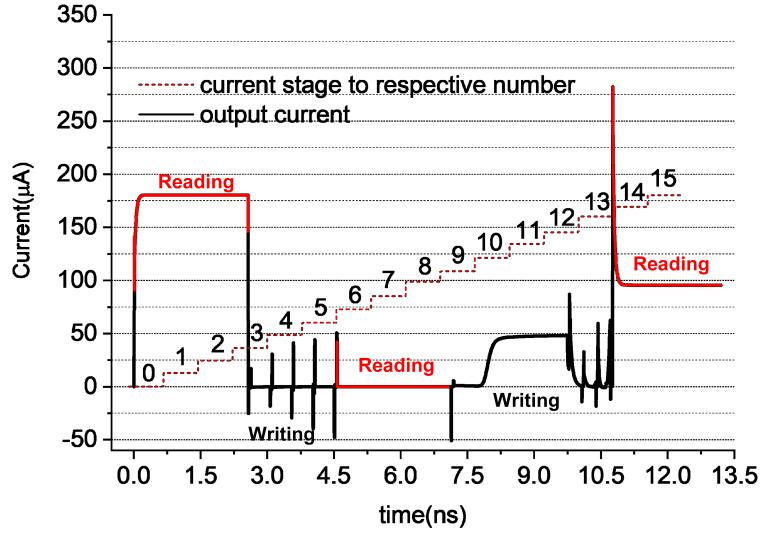

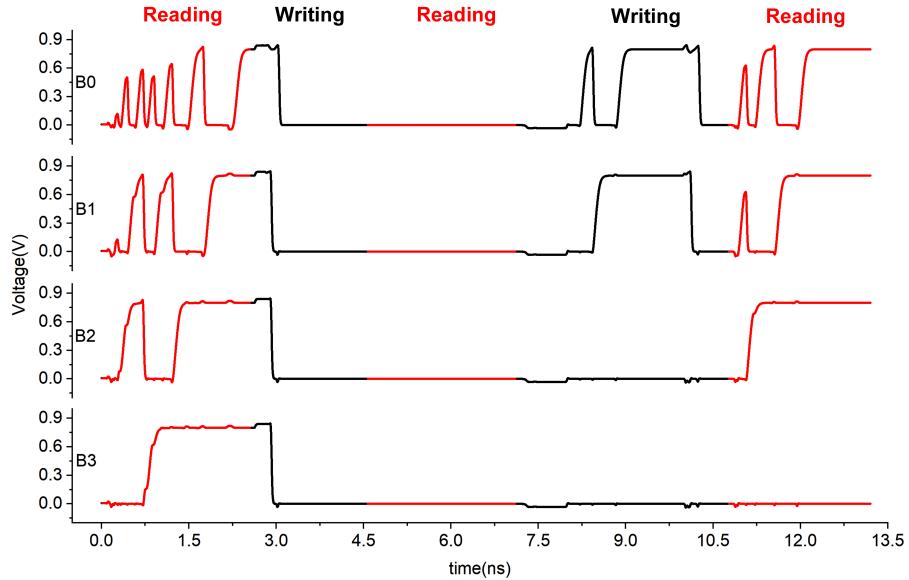

| 5.6 | The output current details of three multiplication cases. The red dash steps are the threshold for each digital output. 0-2.97 ns is $15 \times 15$ , 4.57 ns-7.13 ns is $0 \times 0$ , and 10.77 ns-13.2 ns is $9 \times 6$ . . . . .                                                                                                                                | 92 |

| 5.7 | The binary pulse output details of three multiplication cases. 0-2.97 ns is $15 \times 15$ , 4.57 ns-7.13 ns is $0 \times 0$ , and 10.77 ns-13.2 ns is $9 \times 6$ . . . . .                                                                                                                                                                                         | 93 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

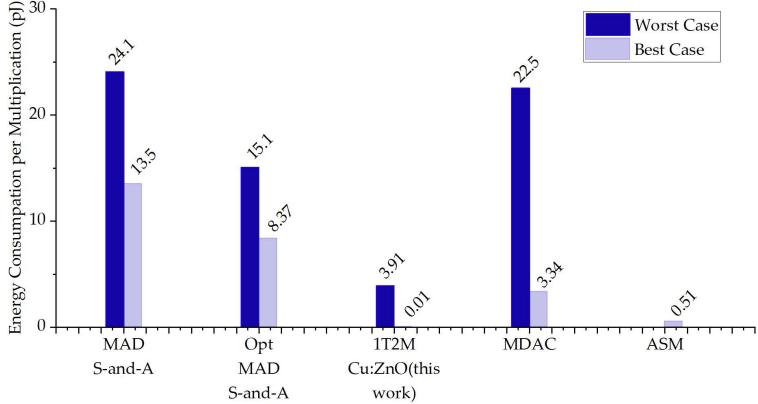

| 5.8 The comparison of energy consumption per multiplication with MAD Shift-and-Add multiplier, optimised MAD Shift-and-Add multiplier [86], MDAC [23], and alphabet set multiplier (ASM) [95]. This work consumes the least energy in both worst case and best case. When compared the memristive multiplier [86], the proposed design saves 83.7% and 74.1% energy in the worst case, and saves up to over 99% energy in the best case. When compared with MDAC [23], proposed design still has 82.6% energy cost reduction in worst case and up to over 99% energy saving in the best case. When compared with alphabet set multiplier, the proposed design has 98% energy efficiency advantage in the best case. . . . . | 95 |

| 5.9 The NN structure and training graph. (a) presents NN structure to demonstrate MNIST classification using the proposed MAC unit. It consists of three fully-connected layers, each of which (input/hidden/output) contains 800/500/10 neurons. The traditional MAC unit will be replaced by the proposed one. (b) presents the training graph of the NN. We added the MAC block (highlighted in blue) where the output of the dot-product will be subtracted by the non-ideal effect of our MAC unit following Eq. (5.23) and the multiplication errors in Table 5.2. This allows the NN to learn the loss regarding the proposed MAC unit. . . . .                                                                      | 97 |

# List of Tables

|     |                                                                                                              |    |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Digital-in/Analogue-out Multiplier Designs . . . . .                                                         | 4  |

| 2.1 | Voltage ThrEshold Adaptive Memristor Model Parameters . . . . .                                              | 22 |

| 3.1 | Binary Multiplication Algorithm with 4-bit Operands . . . . .                                                | 30 |

| 3.2 | Cell Values and Path Currents in Eq. (3.11)Ex. 1 and Ex. 2 . . . . .                                         | 35 |

| 3.3 | Voltage ThrEshold Adaptive Memristor Model Parameters taken from [52]                                        | 38 |

| 3.4 | Transistor Sizes for the Current Mirrors . . . . .                                                           | 43 |

| 4.1 | Single Transistor Multiple Memristors Cell Operations . . . . .                                              | 54 |

| 4.2 | Multiplier Operation Steps and Delay per Multiplication . . . . .                                            | 70 |

| 4.3 | Circuit Complexity of Memristor Based Multipliers . . . . .                                                  | 71 |

| 4.4 | Multiplier Peak Power per Phase . . . . .                                                                    | 72 |

| 4.5 | Energy per Multiplication Corner Cases . . . . .                                                             | 72 |

| 5.1 | Thermometer Code Generator Transistor Size . . . . .                                                         | 84 |

| 5.2 | Multiplication Errors of the Proposed Multiply Accumulate Unit . . . . .                                     | 88 |

| 5.3 | Multiplier Operation Design Details . . . . .                                                                | 92 |

| 5.4 | Modified National Institute of Standards and Technology (MNIST) Classification Accuracy Comparison . . . . . | 96 |

| 5.5 | QAT NN with MAC Component Variation Training. . . . .                                                        | 99 |

# List of Acronyms

**1T1M** - Single Transistor Single Memristor

**1TxM** - Single Transistor Multiple Memristors

**A2D** - Analogue to Digital

**ABM** - Analogue Behavioural Model

**ADC** - Analogue-to-Digital Converter

**AI** - Artificial Intelligence

**ASM** - Alphabet Set Multiplier

**CF** - Conductive Filament

**CL** - Column Line

**CLA** - Carry Look-Ahead

**CM** - Current Mirror

**CMA** - Current Accumulation

**CMOS** - Complementary Metal–Oxide–Semiconductor

**Cu:ZnO** - Copper doped:Zinc Oxide

**DAC** - Digital-to-Analogue Converter

**DC** - Direct Current

**DI/AO** - Digital-In/Analogue-Out

**DI/DO** - Digital-In/Digital-Out

**GL** - Gate Line

**HCS** - High Conductance State

**HRS** - High Resistance State

**HVS** - High Voltage State

**IMC** - In-Memory Computing

**IMP/IMPLY** - Material Implication

**I/O** - Input/Output

**IoT** - Internet of Things

**ITO** - Indium Tin Oxide

**I-V** - Current-Voltage

**KCL** - Kirchhoff's Current Law

**LC** - Logic Cell

**LCS** - Low Conductance State

**LRS** - Low Resistance State

**LSB** - Least Significant Bit

**LVS** - Low Voltage State

**MAC** - Multiply-Accumulate

**MAD** - Memristors-as- Drivers

**MDAC** - Multiplying Digital-to-Analogue Converter

**MIG** - Majority Inverter Graph

**MIM** - Metal-Insulator-Metal

**MLA** - Machine Learning Algorithm

**MLP** - Multi-Layer Perceptrons

**MNIST** - Modified National Institute of Standards and Technology

**MOSFET** - Metal-Oxide-Semiconductor Field-Effect Transistor

**MSB** - Most Significant Bit

**NMOS** - N-channel Metal-Oxide-Semiconductor

**NN** - Neural Network

**PMOS** - P-channel Metal-Oxide-Semiconductor

**PP** - Partial Product

**PTQ** - Post-Training Quantization

**QAT** - Quantization-Aware Training

**ReLU** - Rectified Linear Unit

**RL** - Row Line

**ROM** - Read Only Memory

**RRAM** - Resistive Random Access Memory

**RS** - Resistive Switch

**RSV** - Reset Voltage

**SBMC** - Single-Bit Multiplication Cell

**SBS** - Single Bar Source

**SL** - Source Line

**SV** - Set Voltage

**TEAM** - ThrEshold Adaptive Memristor

**TIA** - Trans-Impedance Amplifier

**TiO<sub>2</sub>** - Titanium Dioxide

**UT** - Unintended Tuning

**VMM** - Vector-Matrix Multiplication

**VTEAM** - Voltage ThrEshold Adaptive Memristor

**xM** - Multiple Memristors

**yT** - Multiple Transistors

**yTxM** - Multiple Transistors Multiple Memristors

# Acknowledgments

I would like to express my gratitude to Dr. Rishad Shafik, my supervisor, for his passion, knowledge, and guidance throughout my study in Newcastle. Especially the mental support in my toughest period. He educated me to become a better researcher, furthermore, a better man for my family. I would also like to thank my second supervisor, Prof. Alex Yakovlev, for his wisdom and encouragement in improving my research skills. I am also grateful to Petros Missailidis, who supervised me during my MSc studies; he introduced me to the exciting microsystem group.

I also extend my thanks to Dr. Fei Xia, Dr. Ahmed Soltan, and Dr. Thanasin Bunnam, who acted as my unofficial supervisors. Dr. Fei Xia helped me in improving my publications' quality and provided me with invaluable guidance during my postgraduate research. Dr. Ahmed Soltan shared his huge experience in the field of analog circuit design. Dr. Thanasin Bunnam closely collaborated with me, validating the proposed design in Chapter 5. I would like to thank Dr. Kaiyuan Gao and Dr. Yuqing Xu, who gave me support while EDA tool training.

I am thankful to my wife, Dr. Xue Han, for all her love, strength, patience, and support throughout my Ph.D. She gave birth to and raised our first child during my absence, which is an invaluable gift in my tough period. She supported me in any difficulty; also, she shared me with all happiness. I am grateful to my family for their concern and support. My thanks also to all my friends, especially to Dr. Adrian Wheeldon, who made my Ph.D. journey a much more fun journey with various social activities.

This research was supported by EPSRC IAA project Whisperable AI Power Management (ref: NU-007755, Newcastle University, UK) and Northern Accelerator grant on Low-Power AI Circuits (NU-009397, Newcastle University). I am grateful for their support.

# Publications

The following is a list of publications related to this thesis.

S. Yu, A. Soltan, R. Shafik, T. Bunnam, F. Xia, D. Balsamo and A. Yakovlev, "Current-Mode Carry-Free Multiplier Design using a Memristor-Transistor Crossbar Architecture," 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2020, pp. 638-641, doi: 10.23919/DAT48585.2020.9116417.

This paper presents the titanium oxide (i.e.,  $TiO_2$ ) 1T1M multiplication cell and crossbar multiplier design using the UMC 65 nm library. It is the first publication to introduce a current-mode multiplication with memristive cells. This work appears in Section 3.1.

S. Yu, R. Shafik, T. Bunnam, K. Chen and A. Yakovlev, "Self-Amplifying Current-Mode Multiplier Design using a Multi-Memristor Crossbar Cell Structure," 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2020, pp. 1-4, doi: 10.1109/ICECS49266.2020.9294797.

This paper extend the titanium oxide (i.e.,  $TiO_2$ ) 1T1M multiplication cell to 1TxM multiplication cell. Meanwhile, apply it in a CM eliminated crossbar multiplier design using the UMC 65 nm library. Moreover, this work discusses the performance development by multiplication cell structure variation in Section 4.2.

S. Yu, R. Shafik, T. Bunnam, K. Chen and A. Yakovlev, "Optimized Multi-Memristor Model based Low Energy and Resilient Current-Mode Multiplier Design," 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2021, pp. 1230-1233, doi: 10.23919/DAT51398.2021.9473926.

This paper compares crossbar multiplier based on the titanium oxide (i.e.,  $TiO_2$ ) 1TxM multiplication cell and doped zinc oxide (i.e., ferroelectric Cu:ZnO) 1TxM

multiplication cell with other multipliers in performance and energy efficiency. The results show the favorable energy efficiency of the 1TxM crossbar multiplier over other designs and motivate the 1TxM crossbar multiplier design in Section 4.2.

S. Yu, F. Xia, R. Shafik, D. Balsamo, and A. Yakovlev, Approximate Digital-In Analog-Out Multiplier with Asymmetric Nonvolatility and Low Energy Consumption. In: Integration.

This paper compares crossbar multiplier based on the titanium oxide (i.e.,  $TiO_2$ ) 1TxM multiplication cell and doped zinc oxide (i.e., ferroelectric Cu:ZnO) 1TxM multiplication cell with other multiplication circuits in latency, performance, and energy efficiency. High memristance 1TxM crossbar multiplier stands out in latency and energy efficiency to other designs. Moreover, the transistor memristor crossbar multipliers are summarized in Chapter 4.

Yu, S., T. Bunnam, S. Triamlumlerd, M. Pracha, F. Xia, R. Shafik and A. Yakovlev, Energy-Efficient Neural Network Design using Memristive MAC Unit. In: Frontiers in Electronics, 28.

This paper presents a MAC unit based on doped zinc oxide (i.e., ferroelectric Cu:ZnO) yTxM multiplication cell crossbar multiplier. Apply this MAC unit in an NN applications and compare the MNIST classification accuracy. The pure fully-connected layer is acceptable for MNIST classification motivates the MAC unit design in Section 5.4.

The rest papers are not presented in this thesis which I was involved as a contributor:

T. Lan, F. Xia, G. Mao, S. Yu, R. Shafik and A. Yakovlev, "Editable asynchronous control logic for SAR ADCs," 2022 IEEE International Symposium on Circuits and Systems (ISCAS), (in progress).

G. Mao, F. Xia, T. Lan, S. Yu, R. Shafik and A. Yakovlev, "Automated Mapping of Asynchronous Circuits on FPGA under Timing Constraints," In 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI) (pp. 104-109). IEEE.

T. Lan, G. Mao, F. Xia, R. Shafik, A. Yakovlev and S. Yu, "An Asynchronous Tsetlin Automaton Architecture with Integrated Non-volatile Memory," In 2022 International Symposium on the Tsetlin Machine (ISTM) (pp. 37-40). IEEE.

O. Ghazal, S. Singh, T. Rahman, S. Yu, Y. Zheng, D. Balsamo, S. Patkar, F. Merchant, F. Xia, A. Yakovlev, and R. Shafik, "IMBUE: In-Memory Boolean-to-CURRENT Inference ArchitecturE for Tsetlin Machines," In ACM/IEEE International Symposium on Low Power Electronics and Design 2023 (ISLPED 2023).

# <sup>1</sup> Chapter 1

## <sup>2</sup> Introduction

### <sup>3</sup> 1.1 Challenges in Emerging Applications

<sup>4</sup> Over the past half-century, the requirement of high energy efficiency and performance

<sup>5</sup> in computing has been sustained by the down-scaling of metal-oxide-semiconductor

<sup>6</sup> field-effect transistors (MOSFET). This method enabled complementary metal-oxide-

<sup>7</sup> semiconductor (CMOS) systems to maintain an exponential increase of the device's

<sup>8</sup> density in per unit area at each technology generation [1]. In the recent nano-scale

<sup>9</sup> generation, the energy efficiency has stopped commensurately growing with circuit

<sup>10</sup> performance. It is partly because the thermal power density from a large number

<sup>11</sup> of devices in the unit area leads to device performance degradation. This is further

<sup>12</sup> exacerbated by the performance gap between the central processing unit (i.e., data

<sup>13</sup> processing part) and the computer memory (i.e., data storing part) increases as the data

<sup>14</sup> volume increases. These issues leads to difficulties when trying to meet performance

<sup>15</sup> and energy efficiency requirements of emerging electronic applications such as artificial

<sup>16</sup> intelligence (AI) and Internet of things (IoT) AI applications usually based on neuron

<sup>17</sup> networks (NNs) [2,3].

<sup>18</sup> Machine learning using NNs and other AI methods involves multiple iterations of

<sup>19</sup> arithmetic operations, with data flow between processing elements and memory, and is

<sup>20</sup> a significant bottleneck for conventional computers [2–4], this phenomenon is known as

21 the "memory wall" [5, 6]. In order to address the memory wall challenge, researchers

22 have proposed a shift from traditional Von Neumann computing architectures to non-

23 Von Neumann computing architectures. In-memory computing (IMC) is an example of

24 non-Von Neumann computing architectures.

25 IMC using non-volatile memory technologies, provide ways of reducing the amounts

26 of data flow required for AI applications, including NNs [4, 7], by locating the computa-

27 tion close to or at the memory. Using non-volatile memory, IMC can further reduce

28 the number of data movements. Moreover, non-volatile data storage helps sustain the

29 continuity of computing flow through power cuts or interruptions in edge devices,

30 which are powered by unreliable supplies, such as energy harvester.

31 As a result, non-Von Neumann architectures have been a popular area of research

32 aimed at improving energy efficiency and performance. An example area of such

33 research is related to the use of resistive memory such as memristors, which has

34 shown promises of significantly improving key performance metrics such as operating

35 frequency (increasing by 15% relative to the scaled supply voltage), energy efficiency

36 (increasing by 35% for a given per switching performance), footprint area cost (reducing

37 by 35% on chip), and scaled die cost (reducing by 20% while no more than 30% increase

38 of wafer cost ) [8–10].

39 Another application area that is seeing a similar rapid development as AI is the

40 Internet of Things (IoT), devices communicate end-to-end to build the machine-to-

41 machine interaction [11].

42 Arithmetic operations are central to modern AI applications and IoT [12, 13]. In these

43 operations, multiplication plays a crucial role with significant impact on performance

44 and energy efficiency, especially because traditional multiplier circuits feature complex

45 partial product generation and carry propagation logic chains [14]. As such, reducing

46 the energy consumption of multipliers, is an ongoing design challenge.

47 For low-complexity multiplication, reducing precision is a promising method. For

48 this, pruning the carry chains to a minimum proportion while also maintaining an ac-

49 ceptable precision has been proposed by numerous approximate and speculative circuit

50 designs [15]. These designs require careful synergy of operating voltages and frequencies

51 to balance energy and performance trade-offs [16]. Moreover, the accumulation of

52 imprecision and errors in cascaded workloads needs mitigation strategies which adds

53 more complexity to the logic chains [17]. Consequently, the usability of voltage-mode

54 proportional carry pruning schemes is still limited.

55 Many IoT applications, such as neuromorphic, signal processing and control, require

56 the multiplier output in an analogue form with digital input interfaces [18, 19]. This

57 is conventionally satisfied by attaching a digital-to-analogue converter (DAC) device to

58 the output of a digital circuit [20]. Meanwhile, the increase of real-time data produced

59 by relative sensors in edge devices and the number of edge devices set a much higher

60 requirement for the processing speed in IoT applications. However, DAC circuits

61 add to the energy and performance costs that depend on the precision of the digital

62 multipliers. Therefore, resistive switch (RS) emerging devices bring analogue domain

63 data processing in hardware back to the forefront [8, 9, 21].

## 64 **1.2 Energy-efficient Multiplier Design**

65 Since pure digital multiplier design needs positive related scale of DACs, the digital mul-

66 tiplier will be costly in high density analogue to digital (A2D) conversion applications.

67 Therefore, the inevitable A2D conversion in IoT edge devices and the higher requirement

68 of processing speed and energy efficiency makes a limited space for pure digital design

69 in IoT.

70 Multiplication with mixed-signal arithmetic circuits is a potential alternative for

71 achieving low-cost analogue output directly [22] and has a successful academic and

72 commercial history. An example is the multiplying digital-to-analogue converter

73 (MDAC) circuit, which multiplies a digital number by a usually analogue reference

74 signal to produce an analogue output [23–25]. Digital-in/analogue-out (DI/AO), where

75 both operands are digital, but the product is analogue, has remained under explored.

76 One of the main areas of contribution by this thesis is in this area.

77 Table 1.1 lists different types of multipliers (including MDACs) by the digital and

78 analogue nature of their input and output signals. In digital design of DI/AO,

79 both multiplication operands are in digital, and product is initially in digital. Thus

80 DAC is needed for the analogue product. Conversely, analogue design has analogue

Table 1.1: Digital-in/Analogue-out Multiplier Designs

| Design                                  | Multiplier           | Multiplicand             | Product               | Non-volatility |

|-----------------------------------------|----------------------|--------------------------|-----------------------|----------------|

| Digital                                 | Digital              | Digital                  | Digital+DAC [20]      | Symmetric      |

| Analogue [22]                           | Analogue             | Analogue                 | Analogue              | Symmetric      |

| MDAC [23]                               | Digital              | Analogue (Ref.)          | Analogue              | Symmetric      |

| <b>This Work<br/>(Chapters 3&amp;4)</b> | Digital<br>(Voltage) | Digital<br>(Memductance) | Analogue<br>(Current) | Asymmetric     |

81 multiplication operands and analogue product. The MDAC design has digital multiplier,

82 analogue multiplicand and analogue product. The proposed work in Chapter. 3 and 4

83 have digital multiplication operands and analogue product.

84 The proposed designs have the both operands in digital form which removes the

85 need for maintaining an analogue reference or other type of analogue input. These

86 analogue signals will be costly in edge computing including IoT applications. Research

87 in pure-digital input, pure-analogue output is, therefore, relevant for serving one of the

88 important needs in the rapidly developing edge computing area.

89 This thesis presents a design approach for mixed-signal DI/AO multipliers. These

90 multipliers are based on transistor-memristor cells located at the nodes of a crossbar

91 for fast and efficient operation. With one of the operands (inputs) held in non-volatile

92 memory, such a multiplier is suitable for use in applications for which one of the

93 operands has a relatively stable value, for instance a reference input. Such a multiplier

94 can be used as a replacement for or an improvement on an MDAC.

95 For AI applications such as NNs, on the other hand, the input and the output of a

96 multiply-accumulate (MAC) unit should all be of the same format, e.g., digital, because

97 the output of the multiplication usually is re-used as input for other MAC units in

98 the NN [2, 3]. In order to extend the multipliers (presented in Chapters 3 and 4) for

99 use in NNs, the analogue output needs to be converted to digital format. One strong

100 reason for adapting these DI/AO multipliers is that they are based on the transistor-

101 memristor crossbar structure. In such multipliers, one of the operands is represented

102 by memductance (memristor conductance), which is non-volatile. This is a good match

103 for such applications as NNs and reference-based arithmetic, where one of the operands

104 (e.g., the weight or the reference) tends to be relatively stable and requires only sporadic

105 change [2–4,7]. Having that operand in non-volatile storage help reducing system energy

106 consumption and operating latency.

### 107 **1.3 Research Questions and Contributions**

108 The energy-efficient multiplier design has set several fundamental requirements. How-

109 ever, implementations of multiplier demands more than the basics.

110 The arithmetic requirements from IoT nodes and NN cells on the edge pose the

111 following research questions:

112 Research Question (RQ): Can a method be found for designing hardware multipliers

113 that satisfy the following:

- 114 1. Both the operands (inputs) are digital and the product is analogue (DI/AO).

- 115 2. Operands and product are all digital, and have the same bit-width (DI/DO).

- 116 3. One of the operands is maintained in non-volatile memory (asymmetric non-

117 volatility).

- 118 4. Low latency and low energy operations.

- 119 5. High precision and high bit resolution is not an important concern.

120 Note that for both of these application areas, high precision and high bit resolution

121 (bit-width) are not a major concern [23–26], and lower precision can be traded for

122 complexity, energy and speed gains.

123 This thesis seeks to answer these research questions and presents methods for making

124 use of memristors to improve performance metrics including speed and energy efficiency

125 of multipliers. The specific contributions of this thesis are as follows:

- A new, mixed-signal multiplier design method for multiplying two digital numbers and directly obtaining an analogue product without carry-chain and DAC complexities. (Addressing RQ. 1, 4 and 5)

- Comparative analysis of energy / performance against state of the art existing work, demonstrating the advantages of this work through extensive theoretical and experimental investigations. (Addressing RQ. 1, 3, and 4)

- Optimisation methods such as the elimination of current mirror (CM) by changing the topologies of memristor cells and investigating different memristor technologies resulting in an order of magnitude improvements in accuracy, speed and energy for lower complexity design when compared with the high complexity structure with CM. (Addressing RQ. 3 and 4 )

- A high energy efficiency end-to-end multiplication accumulation unit based on the transistor-memristor crossbar multiplier with mode transition for such applications as classification NNs. (Addressing RQ. 3, 4 and 5)

- Validation of the MAC design using it as a perception in a non-Von Neumann NN implementation with quantization-aware training (QAT) solving a machine learning problem of non-trivial size (MNIST hand-writing classification). (Addressing RQ. 2, 3, 4, and 5)

## 1.4 Thesis Layout

This thesis is organised as follows:

**Chapter 1 - Introduction.** This chapter briefly presents the motivation for the thesis and summarises its contributions.

**Chapter 2 - Background and Literature Review.** This chapter gives background theory of the technologies used in the designs in this thesis. These include amplification implementations, the theoretical base of CMs, methods of high energy efficiency AI hardware design, as well as the properties of the memristor.

**Chapter 3 - Transistor-memristor Crossbar Multiplier with Current Amplifiers.** In this chapter, a design of crossbar array multiplier based on one transistor one memristor

<sub>154</sub> (1T1M) is presented. The performance and characteristics are investigated. (Addressing

<sub>155</sub> RQ. 1, 3, and 4)

<sub>156</sub> **Chapter 4 - Memristive Multiplier Design with In-cell Current Multiplication.**

<sub>157</sub> This chapter presents a multiplication cell which amplifies current in cell without CM

<sub>158</sub> circuit, and its use in multipliers. The performance and characteristics are investigated.

<sub>159</sub> (Addressing RQ. 1, 3, and 4)

<sub>160</sub> **Chapter 5 - Memristive Multiply-accumulate Unit Applied for Neural Network.**

<sub>161</sub> The multiplier presented in the previous chapter is further developed into a MAC unit

<sub>162</sub> and an NN is constructed using such MAC units as perceptrons. The use of these

<sub>163</sub> types of NNs is investigated with real-world example machine learning applications.

<sub>164</sub> (Addressing RQ. 2, 3, 4, and 5)

<sub>165</sub> **Chapter 6 - Conclusions and Future Work.** The contributions of this thesis are

<sub>166</sub> summarised, and future research areas for the development of memristor-based design

<sub>167</sub> solutions for computing performance in AI applications are suggested.

<sup>168</sup> **Chapter 2**

<sup>169</sup> **Background and Literature Review**

<sup>170</sup> In this chapter, the technology baseline and related work are discussed, and appropriate

<sup>171</sup> literature survey is also carried out.

<sup>172</sup> **2.1 High Performance Arithmetic Circuit Design Techniques**

<sup>173</sup> **2.1.1 Multiplication Circuit Design**

<sup>174</sup> Multipliers have been a computational building block or programming element in

<sup>175</sup> different computing and signal processing applications. These include filters, NNs,

<sup>176</sup> communication mixers, and communication modulators.

<sup>177</sup> Multiplication is traditionally implemented through a sequence of logic AND, ad-

<sup>178</sup> dition, subtraction, and shift operations. In other words, multiplication is a series of

<sup>179</sup> repeated additions [27]. The multiplicand is the number in addition, and the multiplier

<sup>180</sup> is the number of addition repetitions. Usually, multiplication is divided into several

<sup>181</sup> steps: partial product generation, partial product addition for two rows final addend and

<sup>182</sup> augend, and final product generation by adding row final addend and augend. Besides

<sup>183</sup> initial partial product generation procedure, each step of addition also generates a partial

<sup>184</sup> product. Carry propagation is along with the entire addition procedures [28]. The

<sup>185</sup> partial products addition procedure usually performed by digital adders. These circuits

186 generate delay and consume energy in the carry propagating procedure. Therefore,

187 reducing the delay caused by carry propagation has been set as high-priority task about

188 multiplication optimisation and widely investigated.

189 Partial products are conventionally generated by adders in various logic operations.

190 For instance, in radix b notation, integer  $x = (\dots x_2 x_1 x_0)_b$  and  $y = (\dots y_2 y_1 y_0)_b$ , sum

191 with them will generate two integers,  $p_{xy} = (\dots p_2 p_1 p_0)$  and  $c_{xy} = (\dots c_2 c_1 c_0)$ , and

192 these two new integers has the relation as Eq. (2.1) [29] shows:

$$0 \leq s_i = x_i + y_i - b_{c_{i+1}} < b \quad (i \geq 0) \quad (2.1)$$

193 In Eq. (2.1),  $c_{xy}$  are the "carry" digits with  $c_0 = 0$  as the least significant bit (LSB)

194 cannot get carry from a lower significant bit. As the speed of addition be affected

195 by carry propagating time, a single sum usually is operated in a single adder with

196 additional circuits running the carry propagating procedure. In a multiplier, the scale

197 of the additional circuit, which contributes hugely to logic complexity, will increase with

198 the bit-width and this increase not be proportional.

199 One way of reducing the carry propagation overhead is to reduce the number of

200 addends and augends. In addition, Bedrij proposed a carry identification adder [30].

201 This design generates two sub-sums for each addition with repeating sub-addends and

202 sub-augends addition twice in the same addition sequence. One is forced with carry

203 digits in these two sub-sums, and the other is not. Therefore, the selection of addition

204 results can be directly forwarded without heavy back-propagation [30]. Therefore, the

205 multiplier can be much faster with this light carry propagation.

206 These conventional multipliers built with different adders show respective advan-

207 tages for faster partial product generation. High-performance multiplier design needs

208 to consider simplifying the number of addition operands, accelerating the generation

209 of addition operands, and adding up all operators faster [31]. Wilkes tried to iterate

210 the multiplication process for cutting down the number of addition operands [32]. This

211 method is able to approximate the multiplication operands and shorten the digits for a

212 quicker result than a full multiplication. As addition operands have the same amount

213 as multiplier digits do, all addition operands need to be generated simultaneously. The

214 efficient recording needs to be local operation with digit-shifted multiplicand. By doing

215 this, the number of addition operands will be halved. Normally, an addition operation is

216 performed by a single adder that can only generate a single sum. Carry propagation

217 grows when the number of bits increases, usually not in proportion. And the logic

218 complexity also grows disproportionately with the increase of the number of bits. One

219 way of mitigating this is to use carry-save schemes which reduce the horizontal passing

220 of carry bits by delaying their resolution.

221 Carries must exist in digital multiplication because a single bit cannot represent a

222 numerical value higher than 1, but adding two such bits produce a higher than 1.

223 Furthermore, time and energy costs are inevitably caused by carry processing. Thus,

224 digital no-carry/carry-mitigation/carry-optimisation schemes are ultimately incapable

225 of completely removing the complexity of dealing with carries in digital multiplication.

226 On the other hand, analogue arithmetic does not need to deal with carries because

227 an analogue signal is able to represent a range of values large enough to contain all

228 possible arithmetic results at that digit position. The current in each column may be

229 amplified according to the column's bit significance. For instance, a current value stands

230 for LSB can be amplified to the digit with respective significance. Simultaneously, KCL

231 circuit adds up all currents and generates one current stands for the final calculation

232 result. And this result naturally contains all carries. This will be discussed in detail in

233 subsequent chapters (Chapter 3 and Chapter 4) as the multipliers presented in this thesis

234 take advantage of this principle to eliminate carry processing.

## 235 **2.2 High-speed Analogue-to-digital Converter**

### 236 **2.2.1 Flash Analogue-to-digital Converter**

237 In Chapter 5 of this thesis, there is a requirement for high-performance low-energy

238 analogue to digital (A2D) conversion. Small size is also an important requirement as

239 the analogue-to-digital converter (ADC) represents a significant part of the hardware

240 design.

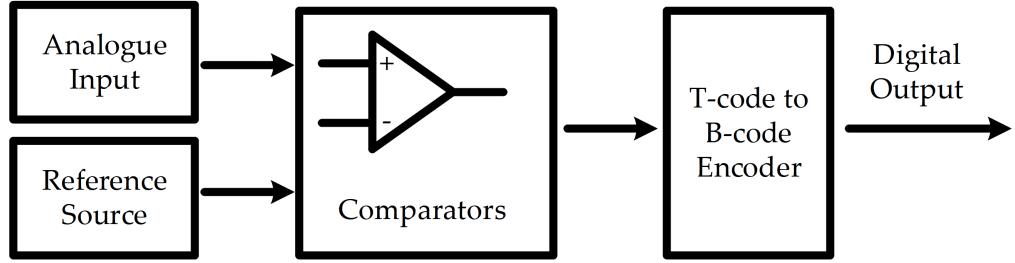

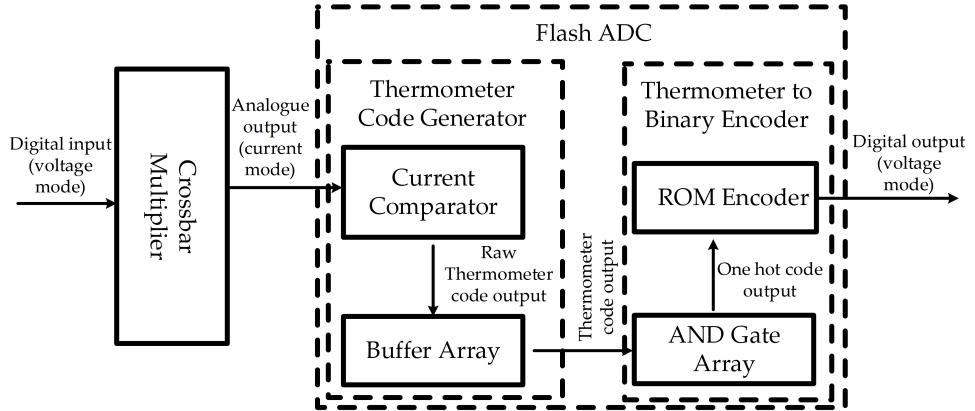

241 A Flash ADC structure is presented in Fig. 2.1. With very high-speed architecture,

242 flash ADC has its performance dominated by matching issues [33]. Also, the flash ADC

243 is a good fit for these requirements. Meanwhile, parallelism exists in both the current

244 comparison and encoding operation by inputting the current into multiple comparisons

245 while encoding multiple comparison results in one shot. This parallelism makes the flash

246 ADC one of the fastest ADC schemes.

Figure 2.1: Block diagram of flash ADC.

### 247 2.2.2 Current Mirror

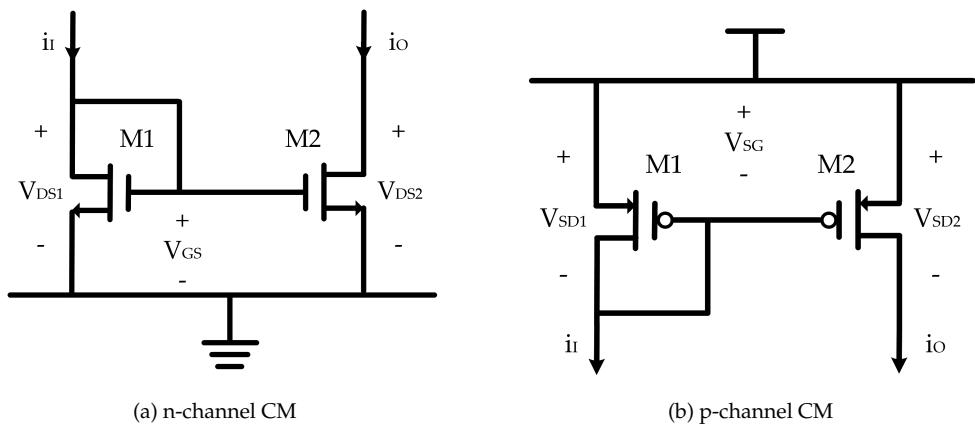

248 The CM was originally named after the equal channel current, which was generated by

249 two identical MOS transistors with the same gate-source potentials [34]. Fig. 2.2 shows

250 two CM structures, in them, (a) is n-channel CM structure, and (b) is p-channel CM

251 structure.

Figure 2.2: Circuit diagram of CM.

252 In Fig. 2.2,  $i_I$  is defined by an input current source, and  $i_O$  is the output with the name

253 "mirrored current". In the n-channel CM, transistor M1 has the drain connected with

254 the gate. Therefore,  $V_{DS1}=V_{GS}$  which means M1 is working in saturation. Similarly, M2

255 also needs to be set in saturation by  $V_{DS2}+V_{T2}\geq V_{GS}$ . In this way, the ratio of  $i_O$  to  $i_I$

256 can be written as Eq. (2.2). In the following equations,  $i_I$  and  $i_O$  are the input current

257 and output current,  $L_1$  and  $L_2$  are channel length of  $M_1$  and  $M_2$ ,  $W_1$  and  $W_2$  are channel

258 width of  $M_1$  and  $M_2$ ,  $V_{GS}$  is the gate-source voltage on transistor,  $V_{T1}$  and  $V_{T2}$  are the

259 threshold voltage of  $M_1$  and  $M_2$ ,  $V_{DS1}$  and  $V_{DS2}$  are drain-source voltage of  $M_1$  and  $M_2$ ,

260  $K'_1$  and  $K'_2$  are the process transconductance parameter of  $M_1$  and  $M_2$ ,  $\lambda$  is the device

261 parameter of transistor.

$$\frac{i_O}{i_I} = \left( \frac{L_1 W_2}{W_1 L_2} \right) \left( \frac{V_{GS} - V_{T2}}{V_{GS} - V_{T1}} \right)^2 \left[ \frac{1 + \lambda v_{DS2}}{1 + \lambda v_{DS1}} \left( \frac{K'_2}{K'_1} \right) \right] \quad (2.2)$$

262 Normally, the same physical parameters of MOS components in the same integrated

263 circuit are identical. These include gate threshold voltage  $V_T$  and process transconduc-

264 tance  $K'$ . Therefore, Eq. (2.2) simplifies to Eq. (2.3).

$$\frac{i_O}{i_I} = \left( \frac{L_1 W_2}{W_1 L_2} \right) \left( \frac{1 + \lambda v_{DS2}}{1 + \lambda v_{DS1}} \right) \quad (2.3)$$

265 In other words, the value of  $i_O$  is proportional to the value of  $i_I$ , achieving pure uni-

266 directional current amplification. In other words, putting a CM on an input current to

267 generate a proportional output current does not modify the former.

268 Similarly, in the p-channel CM, transistor M1 has the drain connected with the gate.

269 Therefore,  $V_{SD1} = V_{SG}$  which means M1 is working in saturation. Similarly, M2 also

270 needs to be set in saturation by  $V_{SD2} + V_{T2} \geq V_{SG}$ . In this way, the ratio of  $i_O$  to  $i_I$  can be

271 written as Eq. (2.4).

$$\frac{i_O}{i_I} = \left( \frac{L_1 W_2}{W_1 L_2} \right) \left( \frac{V_{SG} - V_{T2}}{V_{SG} - V_{T1}} \right)^2 \left[ \frac{1 + \lambda v_{SD2}}{1 + \lambda v_{SD1}} \left( \frac{K'_2}{K'_1} \right) \right] \quad (2.4)$$

272 It is reasonable to assume that the physical parameters, including the gate threshold

273 voltage  $V_T$ , and process transconductance  $K'$ , are the same for the same p-type transistor.

274 Then Eq. (2.4) simplifies to Eq. (2.5).

$$\frac{i_O}{i_I} = \left( \frac{L_1 W_2}{W_1 L_2} \right) \left( \frac{1 + \lambda v_{SD2}}{1 + \lambda v_{SD1}} \right) \quad (2.5)$$

275 If  $V_{DS1} = V_{DS2}$  ( $V_{SD1} = V_{SD2}$ ), then the ratio of  $i_O/i_I$  becomes Eq. (2.6).

$$\frac{i_O}{i_I} = \left( \frac{L_1 W_2}{W_1 L_2} \right) \quad (2.6)$$

To increase the current, the size ratio of the CM transistor can be adjusted [34]. According to Eq. (2.6), a much larger multiplying transistor (M2) with W/L ratio greater than that of the reference transistor (M1) can be used in the CM to amplify current. This technique can also be applied to a p-type CM for current amplification.

280 CMs and other purely transistor-based methods are not the only ways in which

281 current can be tuned. In low-energy and high-speed applications, the latency and energy

282 consumption of charging and discharging transistors are need to be avoided. In some of

283 the multipliers presented in this thesis CMs are not used for this reason.

### 2.2.3 Complementary Metal–Oxide–Semiconductor Current Comparator

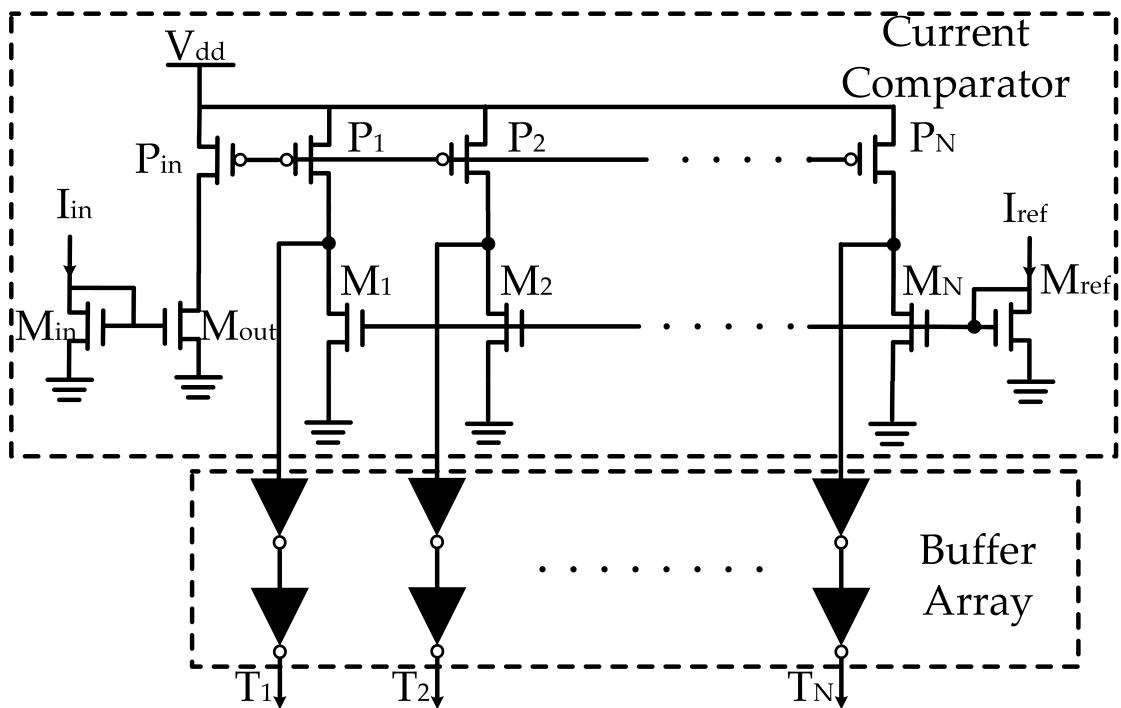

Figure 2.3: Circuit diagram of a current comparator thermometer code generator [35].

285 In ADC designs, comparing an analogue input signal with threshold features is a

286 prominent operation. When the input signals are in the form of voltages, this comparison

287 requires a respective circuit structure to build a feedback path to sources such as source-

288 coupled pairs and complementary device pairs of common-gate and common-drain. In

289 comparison, if the input analogue signals are in the form of currents, the comparison can

290 be implemented in a much more straightforward manner, resulting in faster responses

291 in some cases [36].

292 The current comparator incorporates CM circuits, which are shown in Fig. 2.3. The

293 input is on the left, and the reference is on the right. In this design, p-MOSFETs ( $P_1$

294 to  $P_N$ ) function as current sources, while n-MOSFETs ( $M_1$  to  $M_N$ ) act as current sinks.

295 The p-MOSFET source current is mirrored from the input, while the n-MOSFET sink

296 current is mirrored from the reference source. As a result, the voltage at the junction

297 point between the p-MOSFET source and the n-MOSFET sink increases to  $V_{dd}$  when

298 the p-MOSFET source current is greater than the n-MOSFET sink current. Conversely,

299 if the n-MOSFET sink current is greater than the p-MOSFET source current, the junction

300 point voltage drops to ground. The comparison of currents is therefore represented in

301 voltages.

302 To detect a small reference current, the sink can be constructed with multiple same

303 channel length n-MOSFETs connected in series. When the differences between the input

304 and reference currents are minimal, the output may not be resolved to logic levels. To

305 address this, dual series-connected inverters in the buffer array amplify the comparator

306 output to standard logic levels. With this setup, the gain inverter array produces a

307 thermometer code where the boundary between 0 and 1 indicates the input current

308 value.

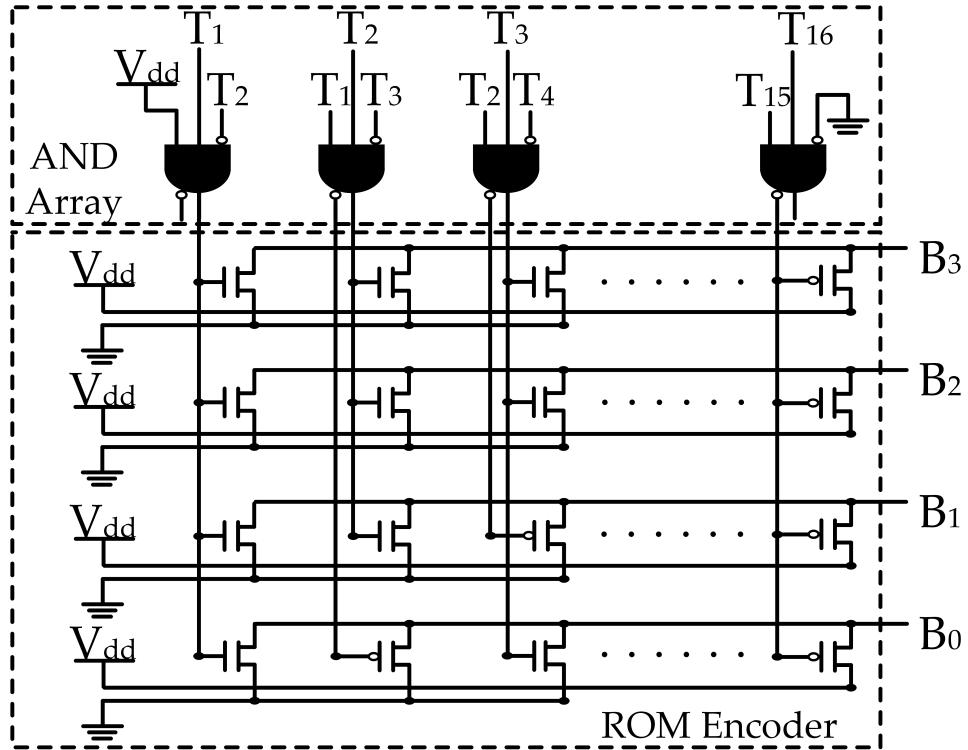

### 309 **2.2.4 Thermometer Code to Binary Encoder**

310 After the current comparator generates its output in a thermometer code, the encoder

311 needs to translate the thermometer code to binary code for output. The thermometer

312 code to binary encoding consists of 2 procedures. First, it generates a one-hot code

313 from the thermometer code. Second, it converts one-hot code to binary code. A 16-

314 bit thermometer code to 4-bit binary code encoder is illustrated in Fig. 2.4. As can be

315 seen, the one-hot code is generated by the AND gates. Then, the one-hot code is input

316 into a binary encoded ROM pattern. Finally, the binary output is buffered and sent out.

Figure 2.4: Circuit diagram of ROM thermometer to binary encoder [35] [37]

317 During this procedure, the output of binary encoder generation needs to scan from

318 the LSB to the most significant bit (MSB). LSB will keep swinging until all significant bits

319 are encoded until the higher significant bits are set.

## 320 2.3 Memristors

321 In 1971, Leon Chua related the fundamental circuit variables charge ( $q$ ) and flux

322 linkage ( $\phi$ ) with a mathematical description of a component. Because this relationship

323 includes non-volatility in the adjustable resistance state, it was called "Memristor",

324 short for "memory resistor" [19, 38, 39]. The memristor was proposed as the fourth

325 element in the charge and flux taxonomy [19, 39] and had a number of promising

Figure 2.5: Details of memristor internal state [38].

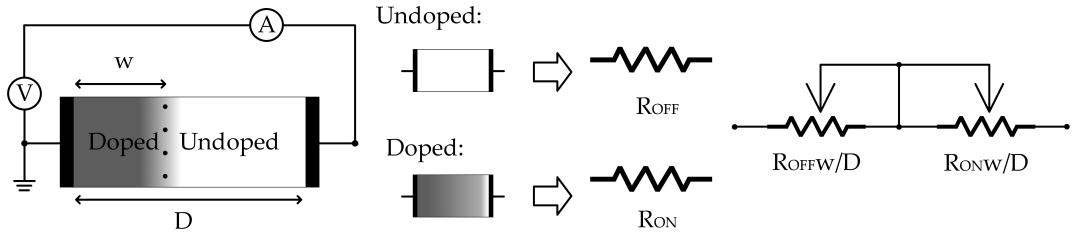

characteristics. One of these is its potential in replacing semiconductor components in processing circuits. That is because, as a switchable device, a memristor can perform similar ON-OFF operations to a transistor, and this became more significant when practical memristor implementations appeared [38, 40]. The RS devices which come from emerging memory technologies are also known as resistive random access memory (RRAM) [41]. A memristor is an RRAM device, typically based on a metal-insulator-metal (MIM) structure. The proper voltage to the top electrode will generate conductive filament (CF) between the top and bottom electrodes. Thus the high density of CF makes the device in low resistance state (LRS). Figure. 2.5 shows in detail how memristor resistance state relates to doped region width ( $w$ ) and device length ( $D$ ). If the electric potential on the left side terminal of the doped region is higher than that on the right side terminal of the undoped region and over a threshold value, the doped region width will increase, and the memristor resistance will decrease, and vice versa [38,39].

Conversely, the rupture of CF by application of proper voltage to the bottom electrode will make the device in high resistance state (HRS) [42,43]. This kind of processing, called IMC, is a design for computing within the memory, thus eliminating the energy-intensive and time-consuming data movement. In this thesis, the design strategy applies the best memristor component with a transistor as individual functional cells.

As a nonvolatile component, memristor has been used in memory device design, which is now called "resistive memory" [44]. At the same time, the possibilities for performing arithmetic with memristors have also been explored, with multiplication being viewed as especially promising [45].

The multiplier solutions presented in this thesis are centred around the use of

349 memristors in novel ways. Fundamentally, the methods presented by using any resistive

350 non-volatile memory. Memristors are chosen for this work because of their support for

351 integration into normal CMOS circuits, the existence of memristor devices with suitable

352 properties and the availability of reliable and trustworthy models for investigating the

353 performance of implemented hardware.

354 **2.3.1 Memristor Physical Models**

355 **Titanium-dioxide Thin-film Memristor**

356 Inspired by Chua's theoretical work, HP lab presented the first Titanium Dioxide ( $TiO_2$ )

357 thin-film memristor device. Strukov and colleagues built a physical model of a two-

358 terminal electrical device that behaves like a perfect memristor [38]. In detail, the device

359 state variable  $w$  specifies the distribution of dopants in the device. It is bounded between

360 zero and  $D$  (maximum device length).  $R$  is the general resistance that depends on the

361 device's internal state, which has the highest value  $R_{OFF}$  and the lowest value  $R_{ON}$ .

362 The external bias  $v(t)$  across the device will move the boundary between the high-

363 dopant region and low-dopant region by causing the drifting of charged dopants and

364 generate respective current  $i(t)$ . With average ion mobility  $\mu_v$ , the simplest case of Ohmic

365 electronic conduction and linear ionic drift in a uniform field can give us the following

366 relations.

$$v(t) = \left( R_{ON} \frac{w(t)}{D} + R_{OFF} \left( 1 - \frac{w(t)}{D} \right) \right) i(t) \quad (2.7)$$

$$\frac{dw(t)}{dt} = \mu_v \frac{R_{ON}}{D} i(t) \quad (2.8)$$

367 From Eq. (2.8), the formula for  $w(t)$  is generated as:

$$w(t) = \mu_v \frac{R_{ON}}{D} q(t) \quad (2.9)$$

368 Then the memristance of this system can be derived by inserting Eq. (2.9) into Eq. (2.7)

369 with simplification from  $R_{ON} \ll R_{OFF}$ ,

$$M(q) = R_{OFF} \left( 1 - \frac{\mu_V R_{ON}}{D^2} \right) q(t) \quad (2.10)$$

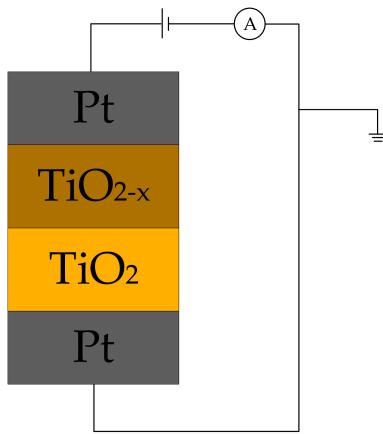

370  $\text{TiO}_x$  devices have similar current-voltage (I-V) relations; meanwhile, I-V character-

371 istic from a metal/oxide/metal cross-point device. This device applies the nanometer

372 scale thick oxide film, which initially contained one layer of insulating  $\text{TiO}_2$  and one

373 layer of oxygen-poor  $\text{TiO}_{2-x}$ . This structure generates the boundary condition on the

374 state variable of the device. A detailed model of  $\text{TiO}_2$  memristor is presented in Fig. 2.6.

Figure 2.6:  $\text{TiO}_2$  memristor device architecture [38].

375 As can be seen, the oxygen vacancies are drifting in the applied electric field as mobile

376 +2-charged dopants. Also, they shift the actual boundary between  $\text{TiO}_2$  and  $\text{TiO}_{2-x}$

377 layers. This shifting performs the switching characteristic on the state variable of device.

378 Meanwhile, this model's ON/OFF memristance ratio ranged from 160 to 380. As will

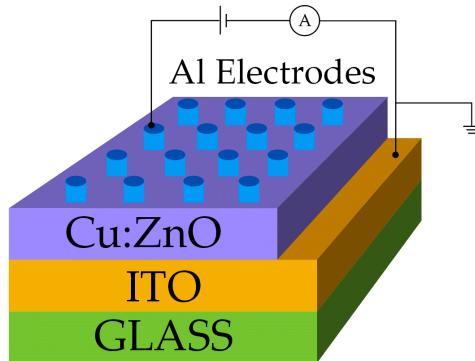

379 be discussed in later chapters, this type of digital-in/analogue-out multiplier does not

380 represent Boolean 0 in the operands with true 0 values of physical parameters – the high

381 resistive state (HRS) of a memristor cannot have a conductance of true 0 and the low

382 resistive state (LHS) of a memristor cannot have a conductance of infinity. This means

383 that  $I_{i,j}$  cannot be 0 amps even when it represents a Boolean value of 0. Consequently,

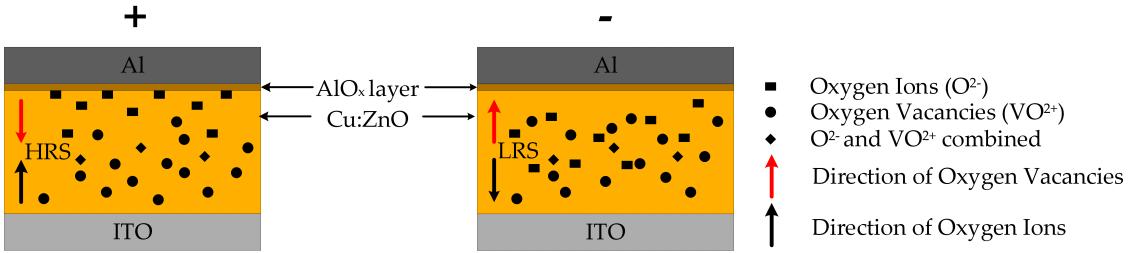

384 when multiple Boolean 0's are added together to produce an overall product  $P$  of 0, the