# Research on the topology of switched capacitor multilevel inverter

PHD thesis

Name: Ze Shan

Student number: 180102549

Supervisor: Matthew Armstrong

Date: 06.01.2024

#### **Abstract**

With the gradual depletion of fossil energy and the deterioration of the global climate caused by greenhouse gas emissions, renewable energy power generation has become a hot research topic today. Multi-level inverter is an important equipment in renewable energy power generation system. The switched capacitor inverter, which evolved on the basis of the multi-level inverter, has attracted widespread attention in recent years due to its advantages of self-boosting, self-balancing of capacitor voltage, and suitability for medium and high power.

This thesis conducts a comprehensive analysis and research on various multilevel inverters, and then proposes a 13-level switched capacitor inverter topology and a 17level switched capacitor inverter topology. For the 13-level switched capacitor inverter, there are one DC source input and 3 times voltage gain of the output voltage. The number of the switch is 13 and the number of the diode is 2. The utilization of the ttype structure makes the output voltage step reduced to 1/2Vdc and the utilization of the crossing structure gives the topology the capability of inherent output voltage polarity shift. Redesigned series/parallel switched capacitor unit makes the inverter has the capability of flexible extension to output variable number of output voltage level and output voltage gain. Compared with diode-clamped multilevel inverter, when output the 13-voltage levels, the number of the switches utilize in the circuit is 24 and the number of diodes is 66. So the 13-level switched capacitor inverter proposed in this thesis, the number of the switch is approximately 1.85 times lower than that of the diode clamped multilevel inverter. The number of the diode is 33 times fewer than that of the diode clamped multilevel inverter. The flying capacitor inverter requires relatively more components for the same number of output voltage levels. Compared to the proposed 13-level switched capacitor inverter in this thesis, the flying capacitor inverter has 1.85 times the number of switches and 3 times the number of capacitors. Additionally, the flying capacitor multilevel inverter suffers from capacitor voltage imbalance, whereas the inverter proposed in this thesis has the capability of selfbalancing capacitor voltages.

The 17-level switched capacitor inverter proposed in this thesis is an optimization of the 13-level switched capacitor inverter. By repositioning the DC power sources and adding two necessary switches and one essential diode, the design achieves a higher number of output voltage levels and a 4 times output voltage gain. Based on the switched capacitor inverters with the same number of output levels designed by other scholars in recent years, the typical number of switches used is 20-24, the number of capacitors used is 5-8, and the achieved voltage gain is 2-3 times. Therefore, the 17level switched capacitor inverter proposed in this thesis reduces the number of switches by 25%, the number of capacitors by 33.3%, and improves the voltage gain by 33.3%. Both of these two proposed topologies are controlled by the phase disposition pulse width modulation (PDPWM) strategy and MATLAB/Simulink is utilized to conduct simulation studies on the two proposed topologies, with a detailed comparative analysis. The results indicate that the device cost of the proposed 17-level switched capacitor inverter is reduced by 34% compared to that of the 13-level switched capacitor inverter, implying a lower component count for the 17-level inverter. Additionally, the Peak Voltage Stress of the 17-level switched capacitor inverter is reduced by 25% compared to the 13-level inverter. In subsequent hardware experiments, the control logic for the 17-level switched capacitor inverter is implemented using FPGA, and detailed experiments are carried out to evaluate its output performance under various load conditions. The results demonstrate the good performance of the proposed 17-level switched capacitor inverter.

## **ACKNOWLEDGEMENT**

I wish to express my profound gratitude to my supervisor, Matthew Armstrong, for his invaluable guidance and unwavering support during my academic pursuits. His expertise, empathy, and patience have greatly enriched my graduate experience. His astute mentorship has been instrumental in the fruition of this research, and his steady encouragement has been the driving force behind my dedication to this project.

Furthermore, my heartfelt thanks go to my family, whose steadfast support and encouragement have been my anchor throughout my studies. The journey of researching and writing this thesis was one accompanied and uplifted by their belief in me. Their role in this accomplishment is immeasurable and deeply appreciated.

## List of abbreviations

DCMLI Diode-clamped multilevel inverter

FCMLI Flying-capacitor multilevel inverter

CHBMLI Cascaded H-bridge multilevel inverter

SCMLI Switched capacitor multilevel inverter

PV Photovoltaics

EMI Electromagnetic interference

PWM Pulse width modulation

SPWM Sinusoidal pulse width modulation

PSPWM Phase shifted carrier pulse width modulation

LSPWM Level shifted pulse width modulation

PDPWM Phase disposition pulse width modulation

PODPWM Phase opposition disposition pulse width modulation

APODPWM Alternative phase opposition disposition pulse width modulation

THD Total harmonic distortion

BF Boost factor

TSV Total standing voltage

PVS Peak voltage stress

CF Cost factor

DSP Digital signal processor

FPGA Field programmable logic gate array

RTL Register-Transfer Level

PLL Phase-locked loop

# **Table of contents**

| Chapter 1: Introduction                                                     | 12        |

|-----------------------------------------------------------------------------|-----------|

| 1.1 Background                                                              | 12        |

| 1.2 Research gap and motivation                                             | 16        |

| 1.3 Scope of the project                                                    | 17        |

| 1.4 Contribution                                                            | 18        |

| 1.5 Thesis summary                                                          | 18        |

| Chapter 2: Review of Multilevel inverters                                   | 20        |

| 2.1 Introduction                                                            |           |

| 2.2.1 DIODE-CLAMPED MULTILEVEL INVERTERS                                    |           |

| 2.2.2 FLYING-CAPACITOR MULTILEVEL INVERTER                                  |           |

| 2.2.3 CASCADED MULTILEVEL INVERTER                                          | 29        |

| 2.2.4 SWITCHED CAPACITOR MULTILEVEL INVERTER                                |           |

| 2.1 Chapter conclusion                                                      | 40        |

| Chapter 3: Methodology                                                      | 42        |

| 3.1 Chapter introduction                                                    | 42        |

| 3.2 Pulse-width modulation strategy (PWM)                                   | 42        |

| 3.3 Multicarrier PWM                                                        |           |

| 3.3.1 Phase shifted carrier PWM (PSPWM)                                     | 47        |

| 3.3.2 LEVEL SHIFTED PWM (LSPWM)                                             | 47        |

| 3.4 MATLAB/Simulink model implement                                         | 50        |

| 3.5 Capacitance calculation for switched capacitor multilevel inverter      | 54        |

| 3.5.1 CAPACITOR VOLTAGE RIPPLE                                              | 54        |

| 3.5.2 CAPACITANCE CALCULATION                                               | 55        |

| 3.5.3 Chapter conclusion                                                    | 56        |

| Chapter 4: Modelling and simulation analysis of a 13-level switched capacit |           |

| multilevel inverter.                                                        | 58        |

| 4.1 Chapter introduction                                                    | 58        |

| 4.2 Configuration of a novel 13-level switched capacitor inverter           |           |

| 4.3 Operation principle                                                     | <i>61</i> |

| 4.4 Modulation strategy                                                     | 65        |

| 4.5 Capacitance calculation                                                 |           |

| 4.6 Simulation setup                                                        | 72        |

| 4.7 Simulation results                                                      |           |

| 4.8 Simulation result of the extension topology                             |           |

| 4.9 Configuration of a novel 17-level switched capacitor inverter           |           |

| 4.10 Operation principle                                                    |           |

| 4.11 Modulation strategy                                                    |           |

| 4.12 Capacitance calculation                                                |           |

| 4 13 Simulation Setun                                                       | 94        |

| 4.14 Simulation result                                            | 95  |

|-------------------------------------------------------------------|-----|

| 4.15 Comparative analysis                                         | 103 |

| 4.16 Chapter conclusion                                           | 105 |

| Chapter 5: Hardware Implement and Experiment Results              | 106 |

| 5.1 Introduction                                                  | 106 |

| 5.2 FPGA-based PDPWM implementation                               | 106 |

| 5.3 Gate drive of the MOSFETs                                     | 111 |

| 5.4 17-level SCMLI prototype implementation and experiment result | 117 |

| 5.5 Chapter conclusion                                            | 125 |

| Chapter 6: Conclusion and future work                             | 126 |

| 6.1 Conclusion                                                    | 126 |

| 6.2 Future work                                                   | 127 |

| Reference                                                         | 129 |

# List of figures

| Fig 1.1 Distribution diagram of global power generation by different power gene methods from 2000 to 2023[8]  |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| Fig 1.2 Distribution diagram of Europe power generation by different power gene methods from 2000 to 2022 [8] |     |

| Fig 2.1 Topology of a standard three-level DCMLI                                                              | 22  |

| Fig 2.2 Topology of a reduced number of clamping diode five-level DCMLI                                       | 23  |

| Fig 2.4 Topology of a novel DCMLI to eliminate the capacitor voltage imbalance                                | e24 |

| Fig 2.5 Topology of a three-level FCMLI                                                                       | 26  |

| Fig 2.6 Topology of a five-level FCMLI                                                                        | 27  |

| Fig 2.7 Topology of a novel five-level inverter proposed                                                      | 29  |

| Fig 2.8 topology of a three-level H-bridge inverter                                                           | 30  |

| Fig 2.9 Topology of a cascade five-level H-bridge inverter                                                    | 31  |

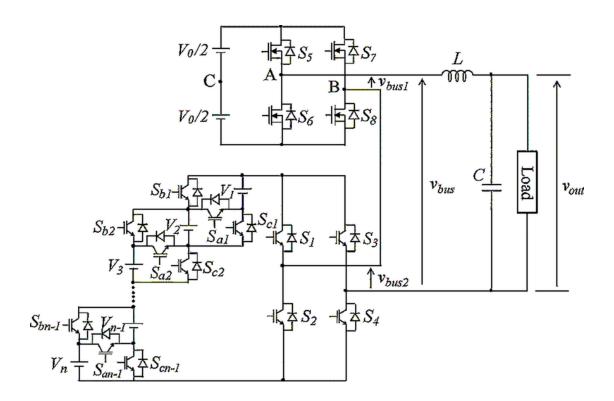

| Fig 2.10 Topology of a hybrid 5-level cascaded inverter                                                       | 33  |

| Fig 2.11 Basic cascaded unit proposed in [52]                                                                 | 34  |

| Fig 2.12 Cascaded multilevel inverter proposed in [52]                                                        | 35  |

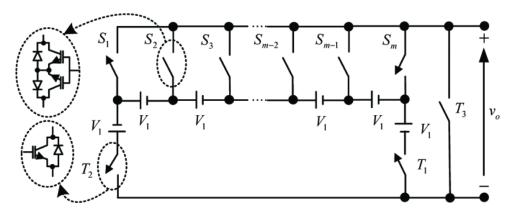

| Fig 2.13 Basic unit circuit of a switched capacitor                                                           | 37  |

| Fig 2.14 Topology by connecting several basic units                                                           | 37  |

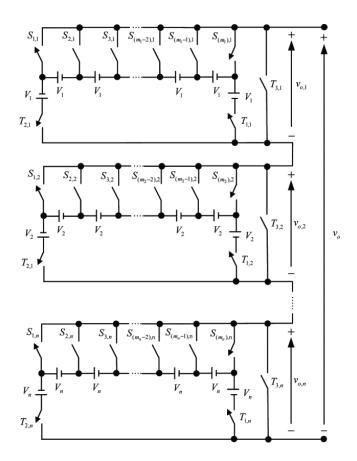

| Fig 2.15 Cascaded switched capacitor multilevel inverter with the basic unit                                  | 38  |

| Fig 2.16 Nine-level switched capacitor inverter with H-bridge                                                 | 39  |

| Fig 2.17 Switched capacitor multilevel inverter without H-bridge                                              | 39  |

| Fig 3.1 Standard H-bridge inverter                                                                            | 44  |

| Fig 3.2 Waveforms of unipolar SPWM method                                                                     | 44  |

| Fig 3.3 Waveforms of bipolar SPWM method                                                                      | 45  |

| Fig 3.4 Waveforms of unipolar SPWM method                                                                     | 46  |

| Fig 3.5 Waveform arrangements of the PSPWM                                                                    | 47  |

| Fig 3.6 Waveform arrangements of the PDPWM                                                                    | 49  |

| Fig 3.7 Waveform arrangements of the PODPWM                                                                   | 49  |

| Fig 3.8 Waveform arrangements of the APODPWM                                                                  | 50  |

| Fig 3.9 Simulink model of 5-level cascaded H-bridge inverter                                                  | 51  |

| Fig 3.10 Logic schematic of PSPWM                                                                             | 52  |

| Fig 3.11 Logic schematic of PDPWM                                                                             | 52  |

| Fig 3.12 Logic schematic of PODPWM                                                                                                           | 53  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig 3.13 Logic schematic of APODPWM                                                                                                          | 53  |

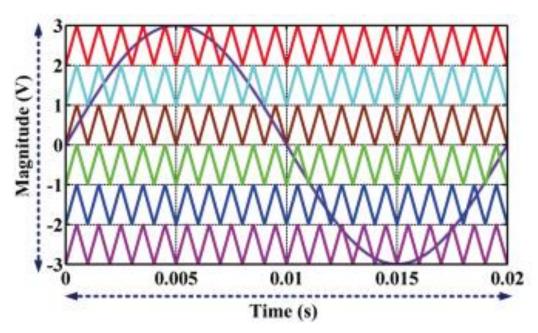

| Fig 3.14 The waveforms of the PDPWM                                                                                                          | .56 |

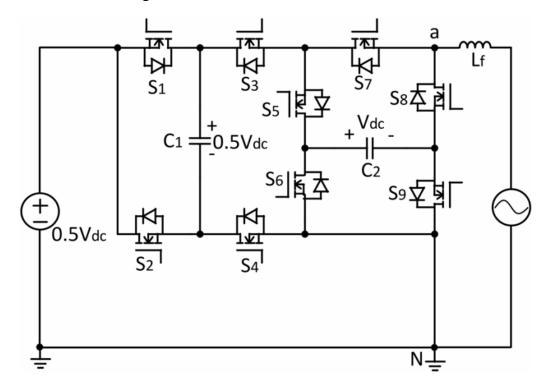

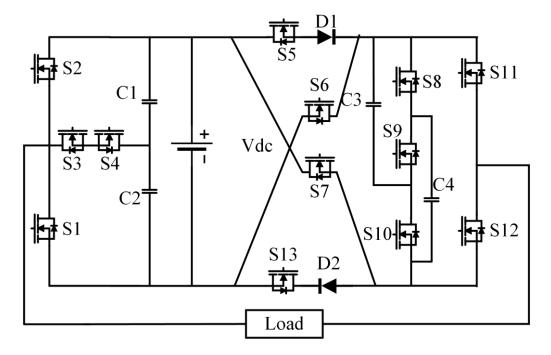

| Fig 4.1 Topology of 13-level switched capacitor inverter                                                                                     | 59  |

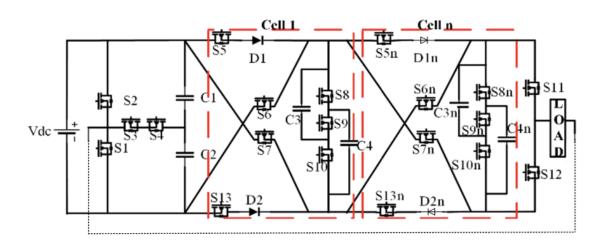

| Fig4.2. Extension of the proposed 13-level SCMLI                                                                                             | .60 |

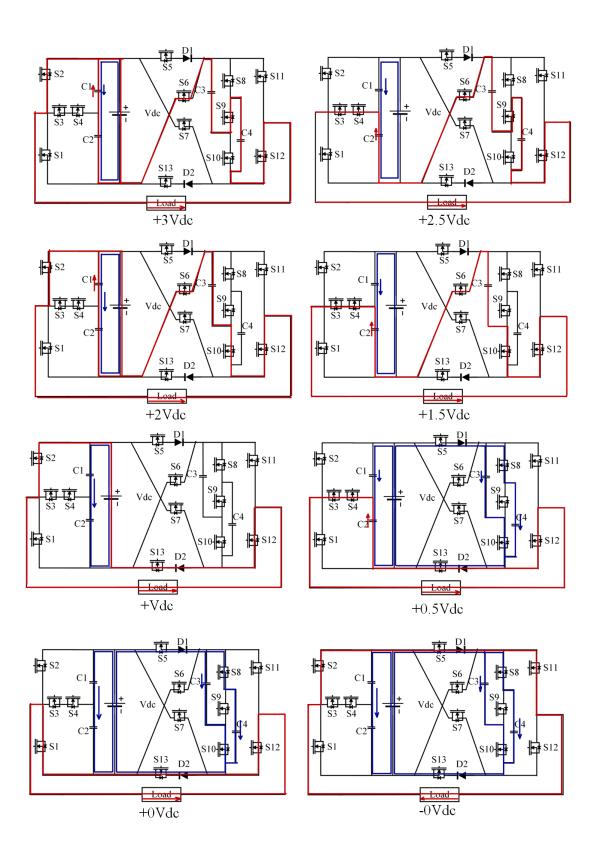

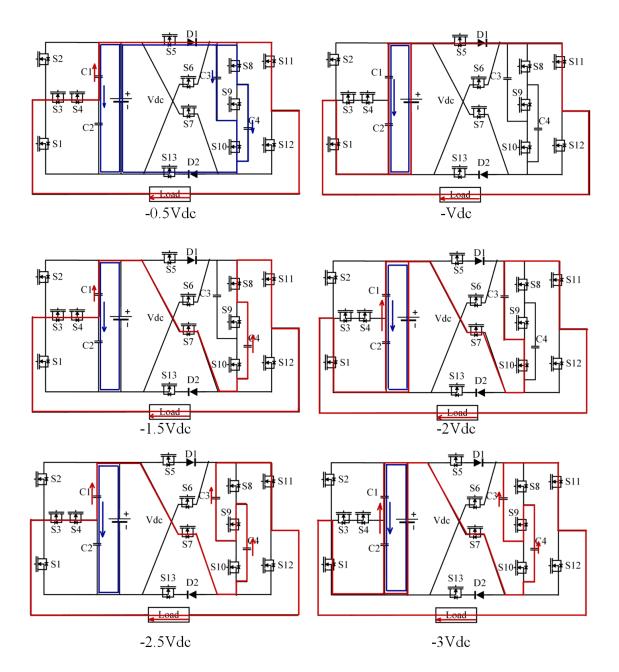

| Fig 4.3 Operating circuit of each mode                                                                                                       | 63  |

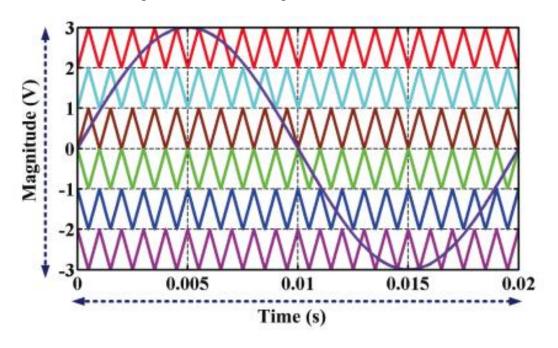

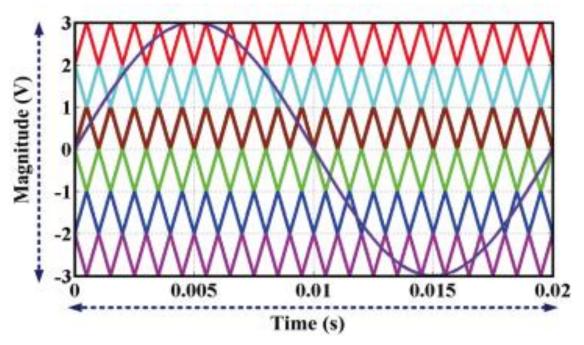

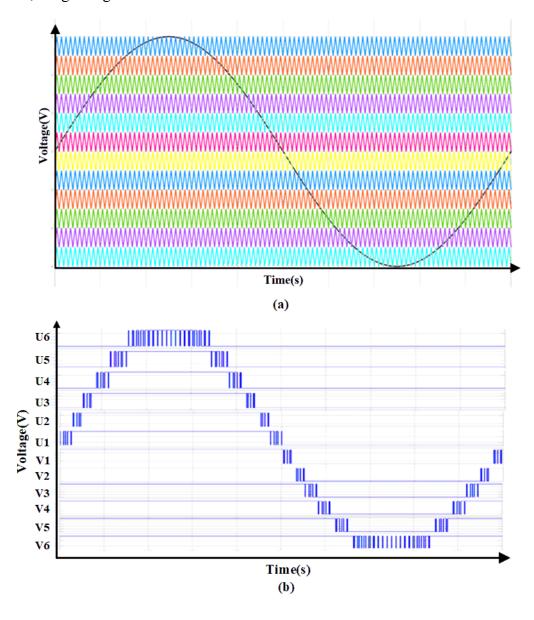

| Fig 4.4 Principle of PDPWM (a) Waveform arrangement                                                                                          | .66 |

| (b) Waveform of $U1 - U6$ , $V1 - V6$                                                                                                        | 66  |

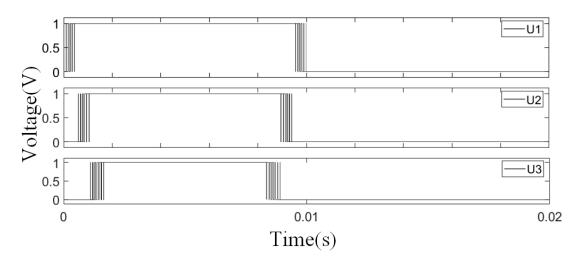

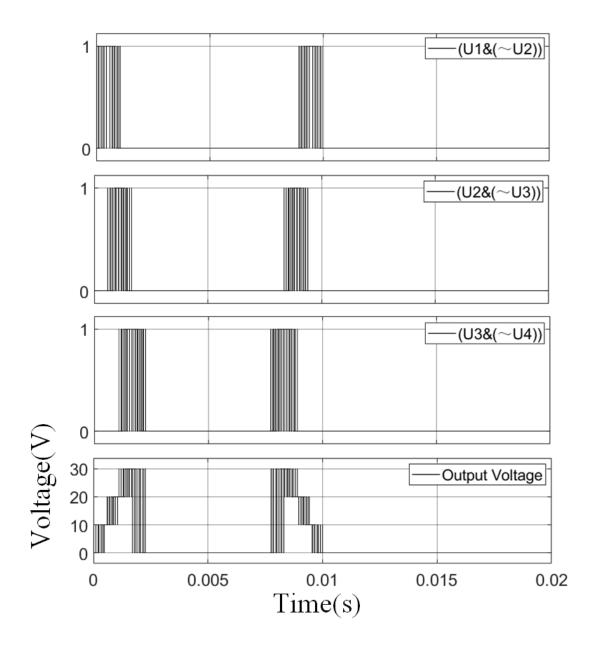

| Fig 4.5 Waveforms of signal U1-U3                                                                                                            | 67  |

| Fig 4.6 Logic signal and corresponding output voltage level                                                                                  | 68  |

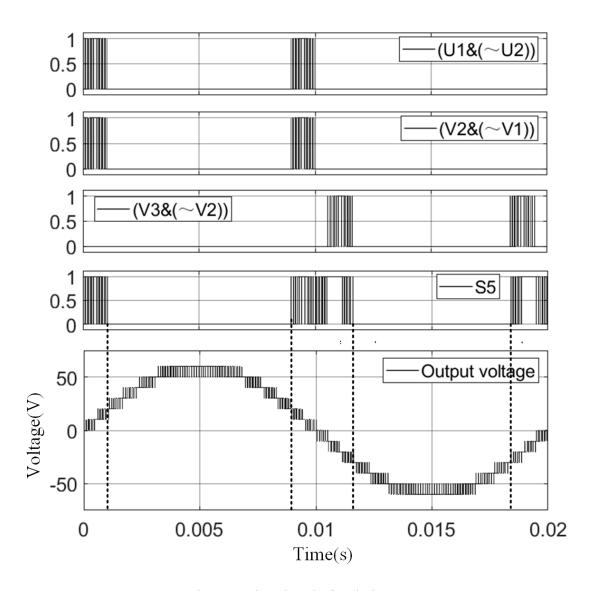

| Fig 4.7 Drive signal of switch S5                                                                                                            | 69  |

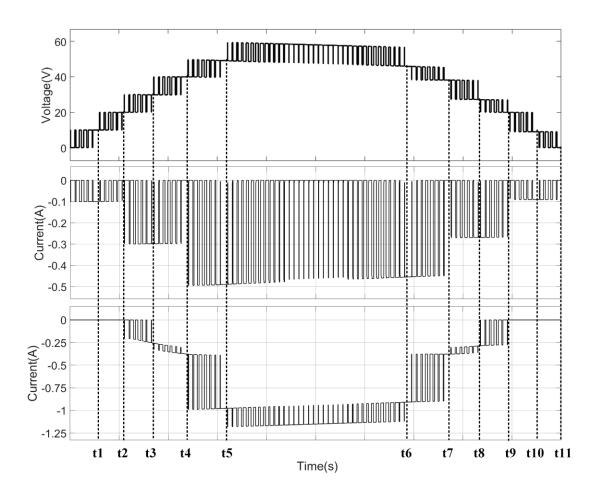

| Fig 4.8 Positive half-cycle of the output voltage and discharge current of the capacitor C2 and C3                                           |     |

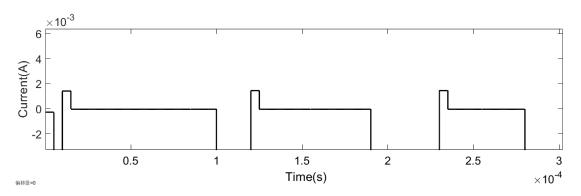

| Fig 4.9 Current waveform close-up view of capacitor C2                                                                                       | 72  |

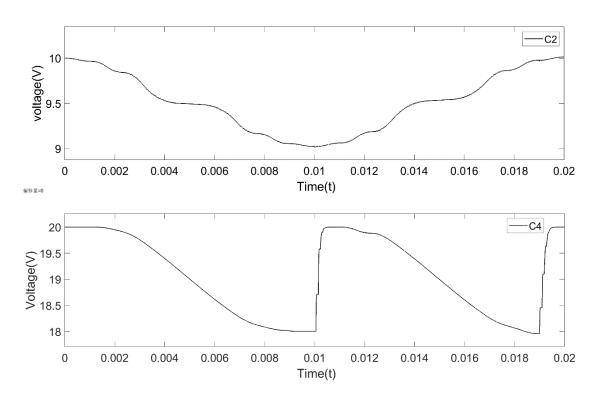

| Fig 4.10 Voltage of capacitors C2 and C4                                                                                                     | 72  |

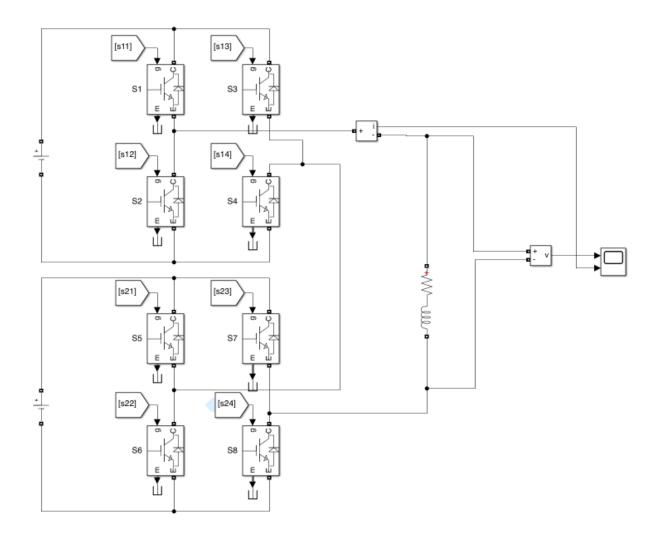

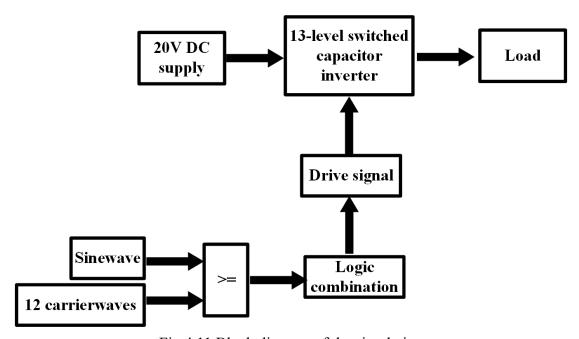

| Fig 4.11 Block diagram of the simulation                                                                                                     | 73  |

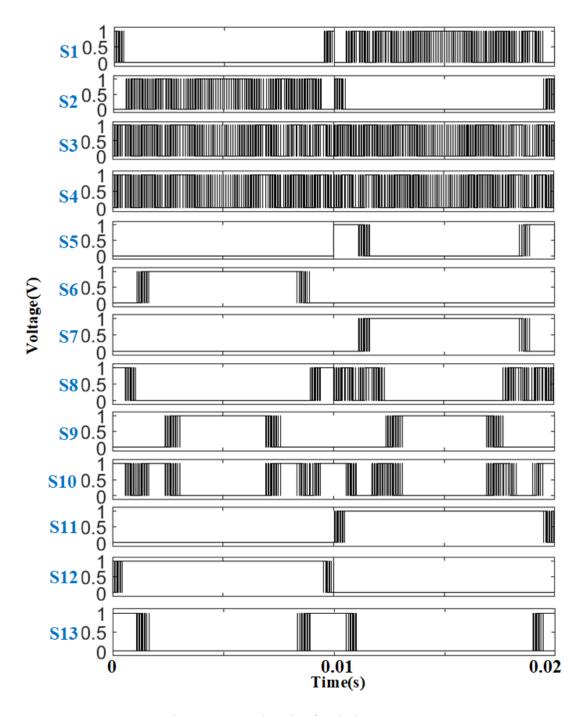

| Fig 4.12 Gate signals of switches S1-S13                                                                                                     | 75  |

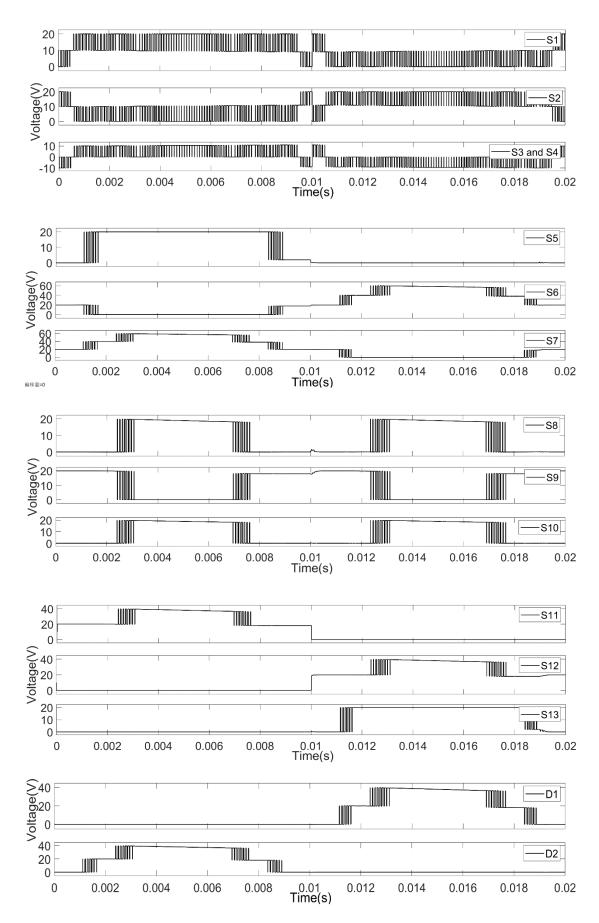

| Fig 4.13 Voltage stress of the switches and diodes                                                                                           | 76  |

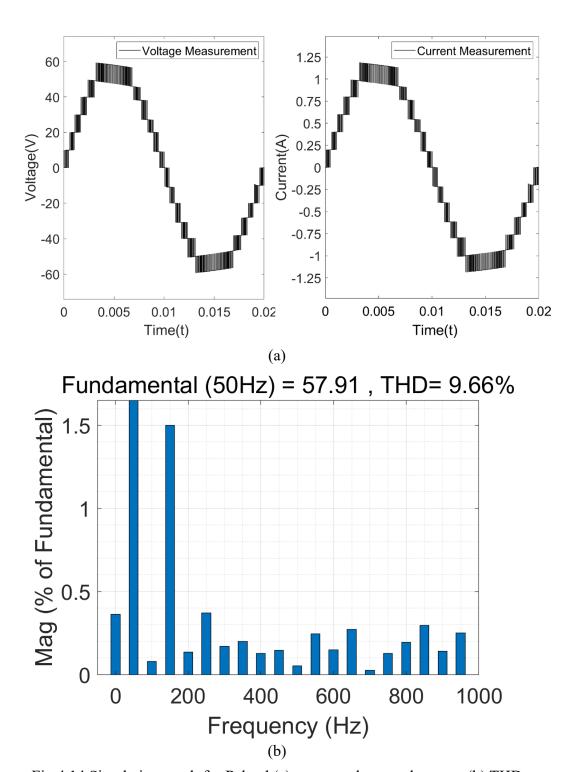

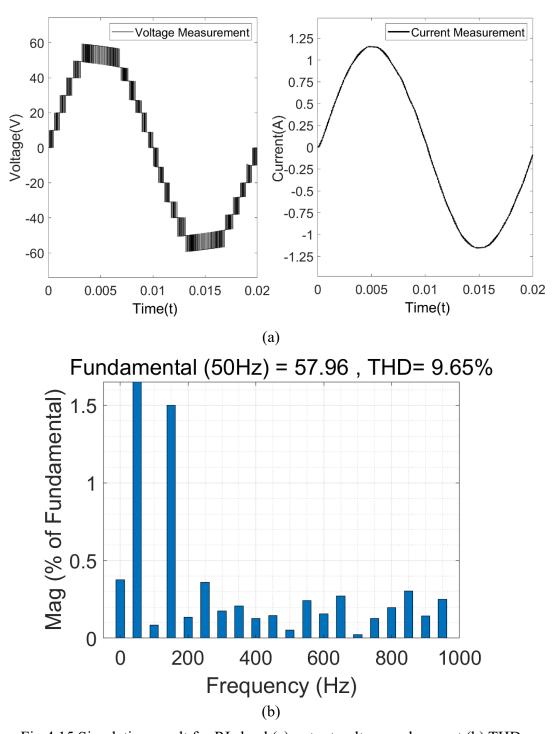

| Fig 4.14 Simulation result for R-load (a) output voltage and current (b) THD                                                                 | 77  |

| Fig 4.15 Simulation result for RL-load (a) output voltage and current (b) THD                                                                | 78  |

| Fig 4.16 Topology of extended 21-level switched capacitor inverter                                                                           | 79  |

| Fig 4.17 Simulation result of the extended topology under 50 $\Omega$ load. (a) Output volt and current (b) Total harmonic distortion        | _   |

| Fig 4.18 Simulation result of the extended topology under 50 $\Omega$ and 5mH load. Output voltage and current (b) Total harmonic distortion |     |

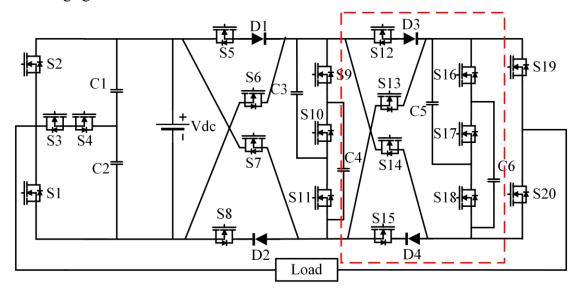

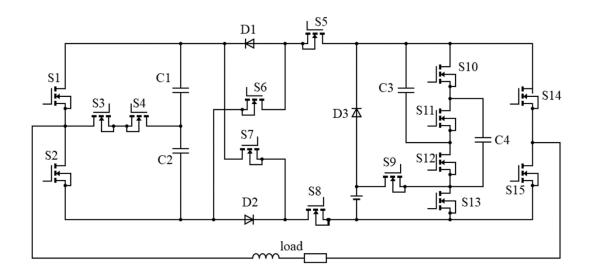

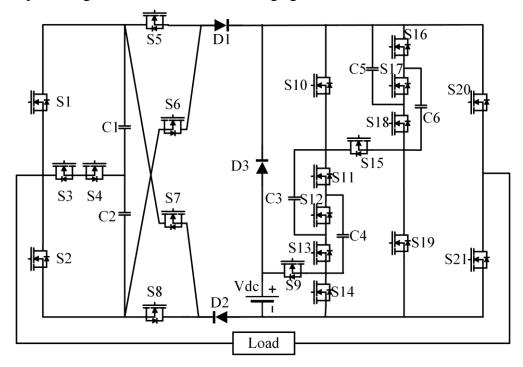

| Fig 4.19 Topology of the 17-level SCMLI                                                                                                      | 81  |

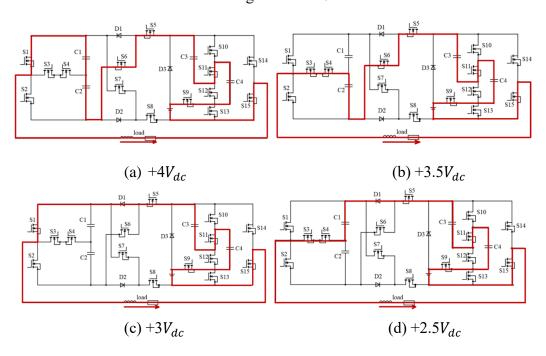

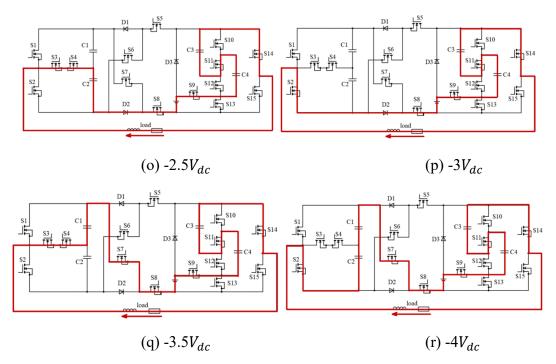

| Fig 4.20 Operating modes of 17-level SCMLI                                                                                                   | 85  |

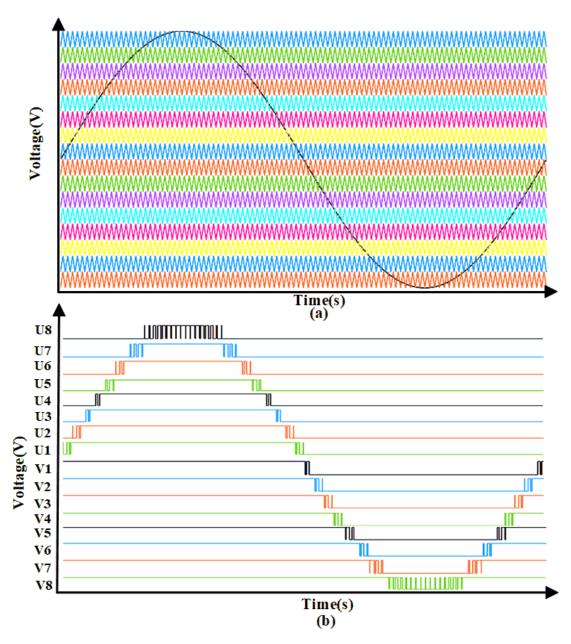

| Fig 4.21 Principle of PDPWM (a) Waveform arrangement                                                                                         | 90  |

| (b) Waveform of $U1 - U6$ , $V1 - V6$                                                                                                        | 90  |

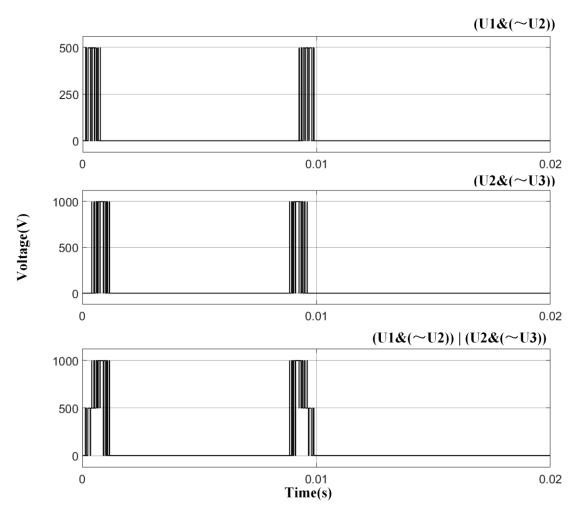

| Fig 4.22 Output voltage levels of specific control signal                                                                                    | 91  |

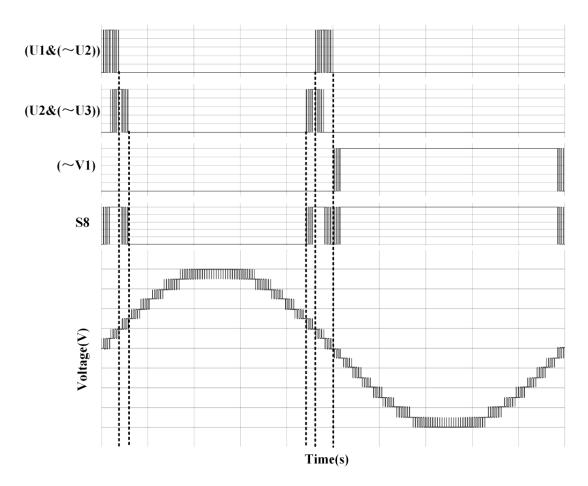

| Fig 4.23 Switching signal of S8                                                                                                              | 92  |

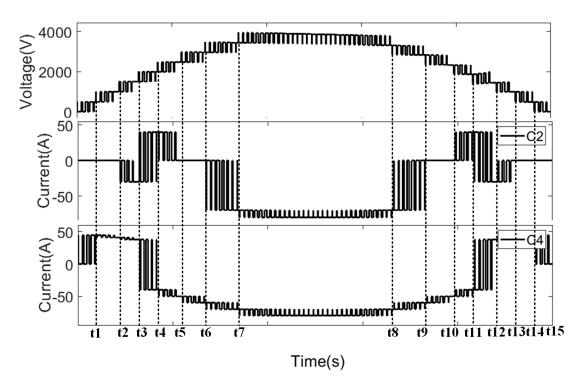

| Fig 4.24 Positive half-cycle of the output voltage and discharge current of the capac C2 and C3                                              |     |

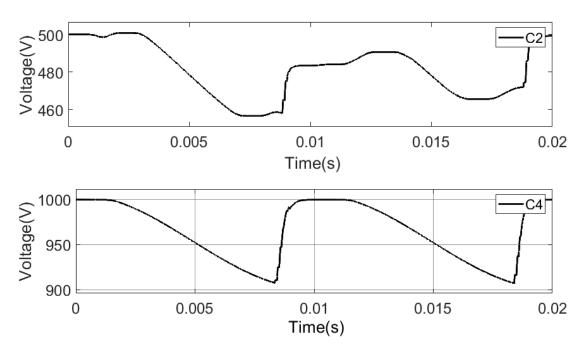

| Fig 4.25 Voltage of capacitors C2 and C4                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

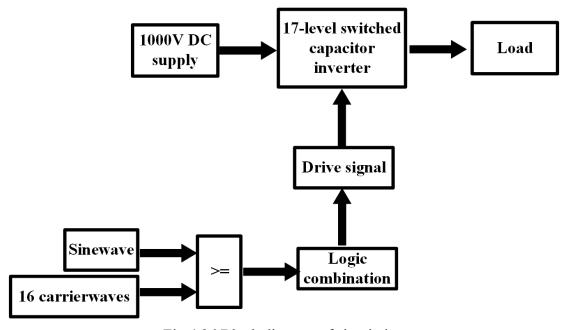

| Fig 4.26 Block diagram of simulation                                                                                                        |

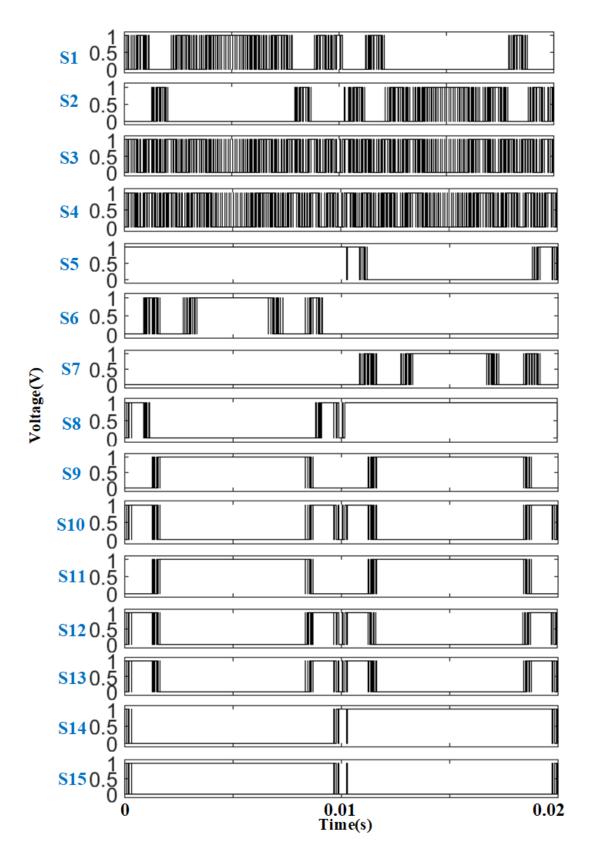

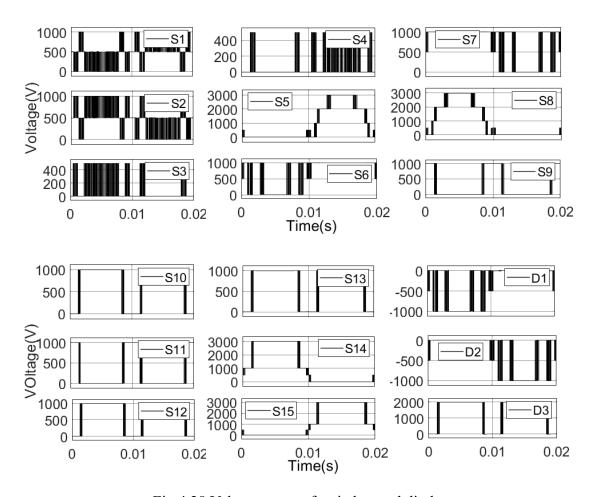

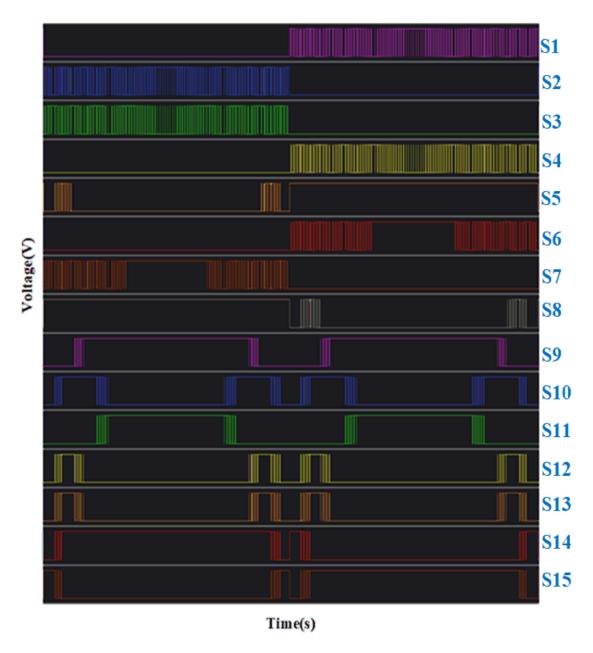

| Fig 4.27 Gate signals of switched S1-S1596                                                                                                  |

| Fig 4.28 Voltage stress of switches and diodes                                                                                              |

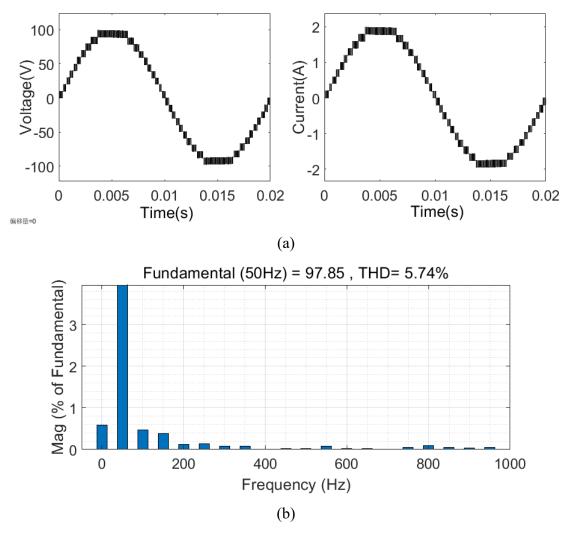

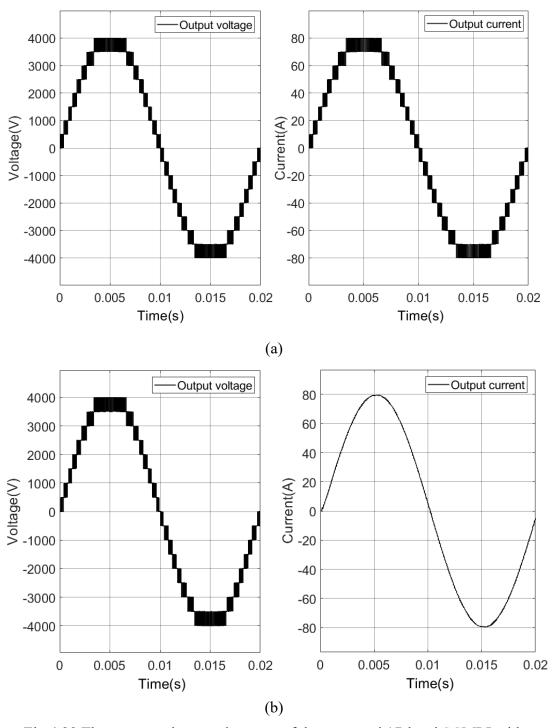

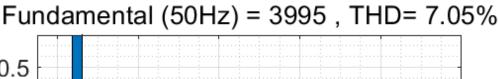

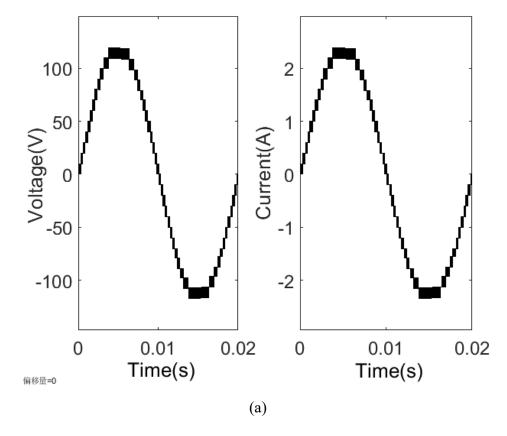

| Fig 4.29 The output voltage and current of the proposed 17-level SCMLI with different load. (a) Resistive load (b) Resistive-inductive load |

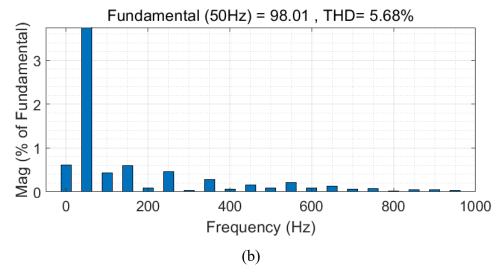

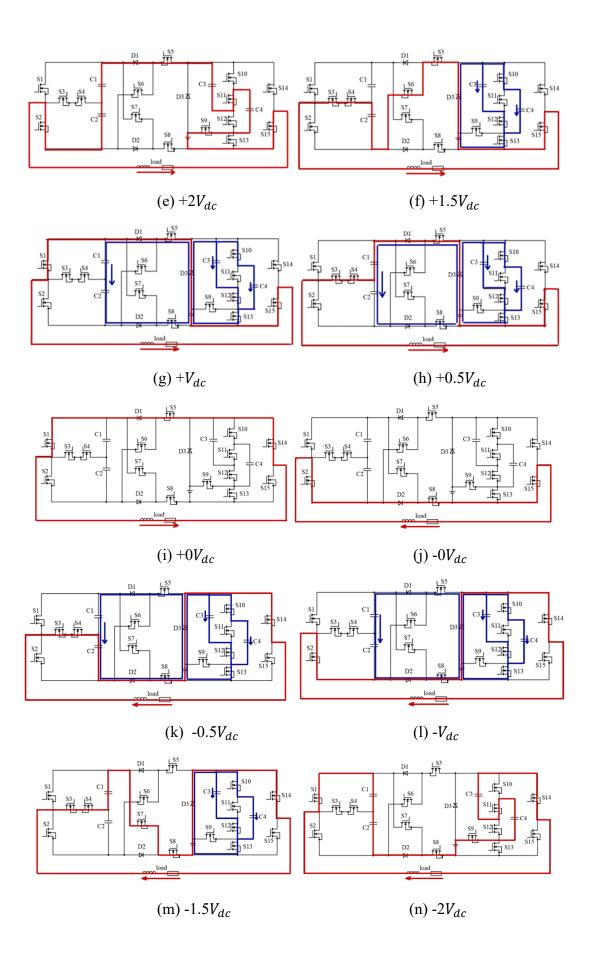

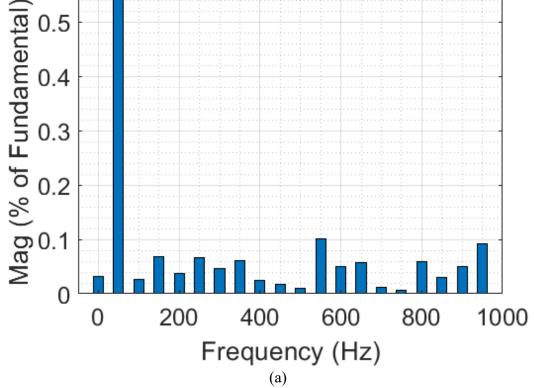

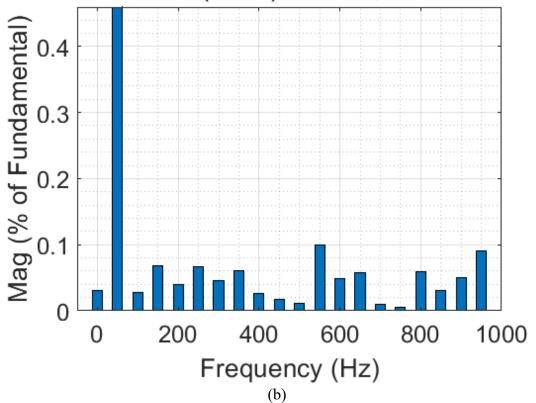

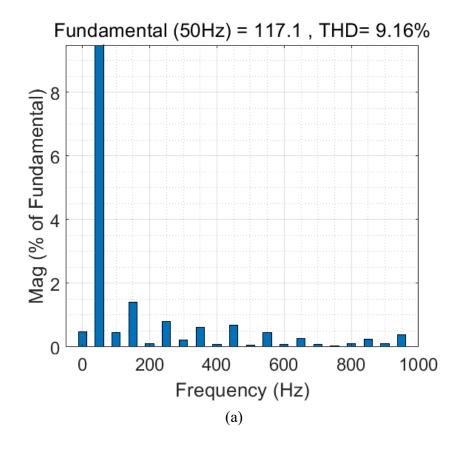

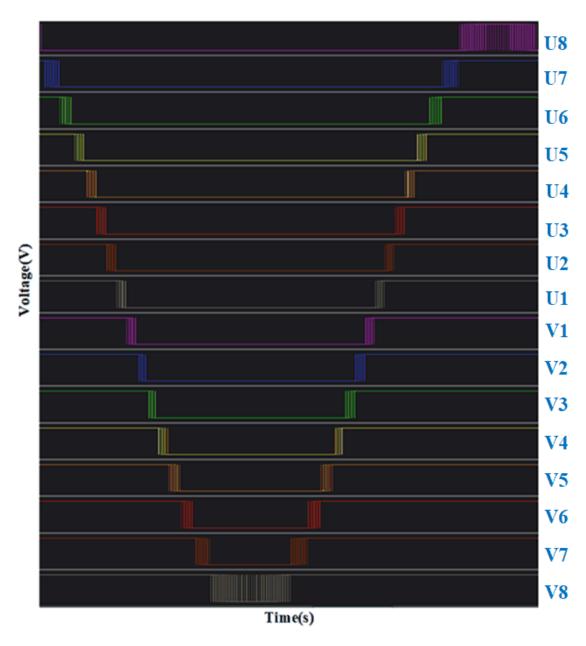

| Fig 4.30 Total harmonic distortion of output voltage of proposed 17-level SCMLI99                                                           |

| Fig 4.31 Topology of extended 25-level switched capacitor inverter100                                                                       |

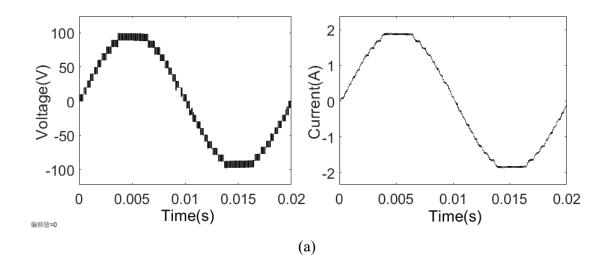

| Fig 4.32 Waveform of output voltage and current of proposed 25-level SCMLI with different load. (a) $50~\Omega$ (b) $50\Omega+5$ mH         |

| Fig 4.33 Total harmonic distortion of output voltage of proposed 25-level SCMLI with different load. (a) $50~\Omega$ (b) $50\Omega+5$ mH    |

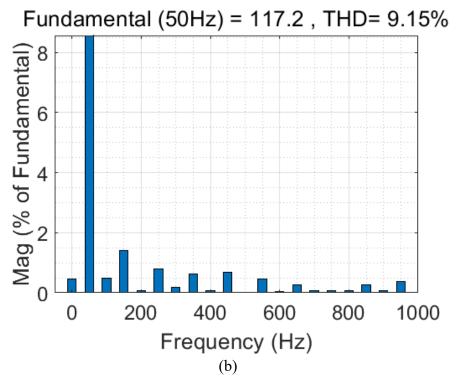

| Fig 5.1 RTL diagram of proposed PDPWM                                                                                                       |

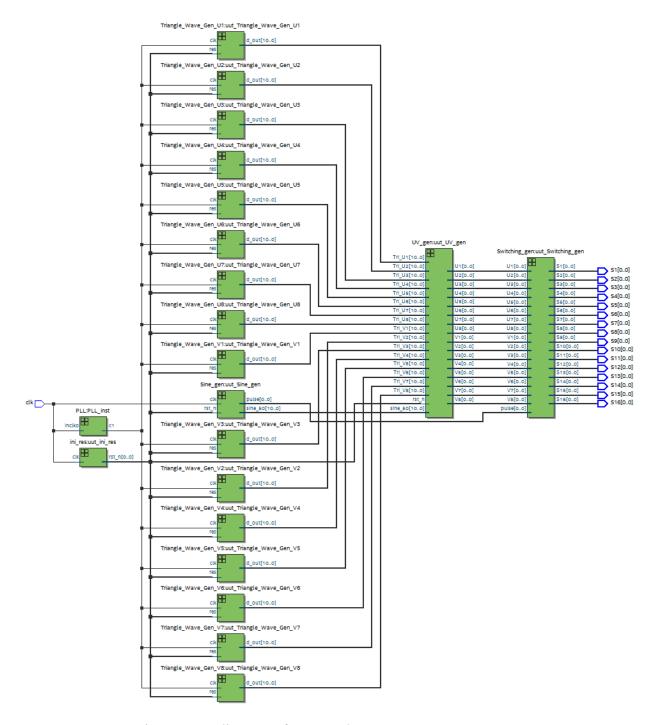

| Fig 5.2 The output signal of U1-U8 and V1-V8                                                                                                |

| Fig 5.3 Switching signal of S1-S15                                                                                                          |

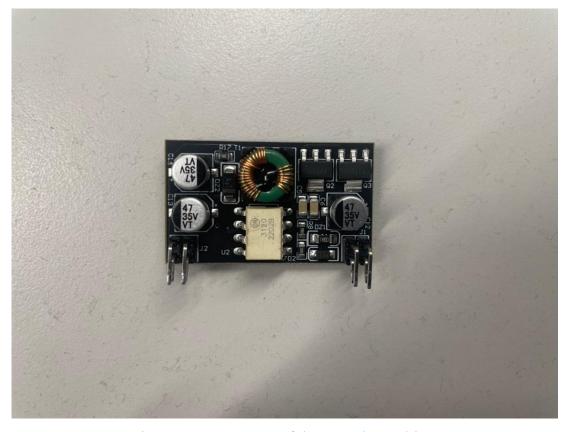

| Fig 5.4 PCB prototype of the first gate driver                                                                                              |

| Fig 5.5 PCB prototype of the second gate driver                                                                                             |

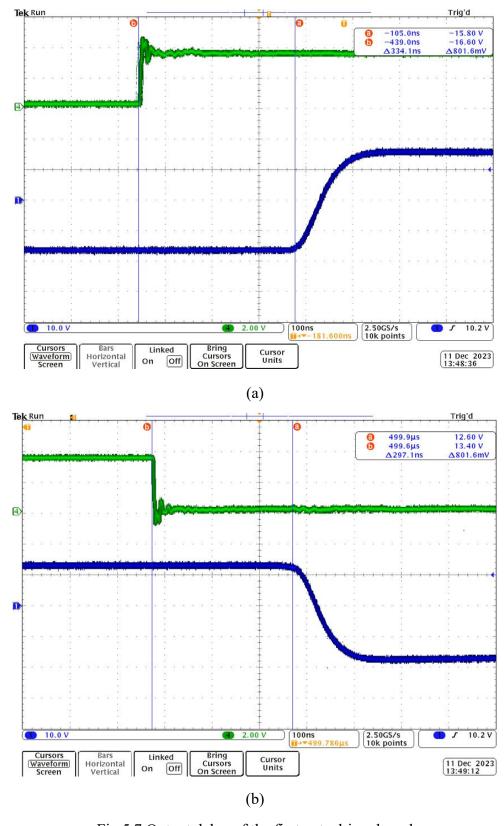

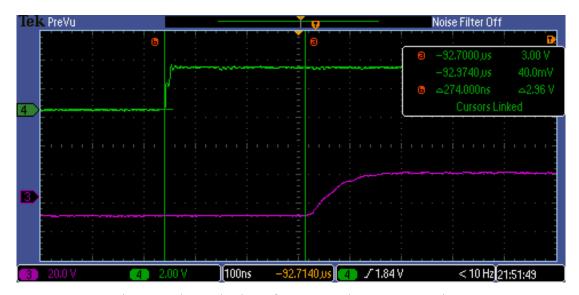

| Fig 5.6 Test bench of the gate driver output delay test                                                                                     |

| Fig 5.7 Output delay of the first gate driver board                                                                                         |

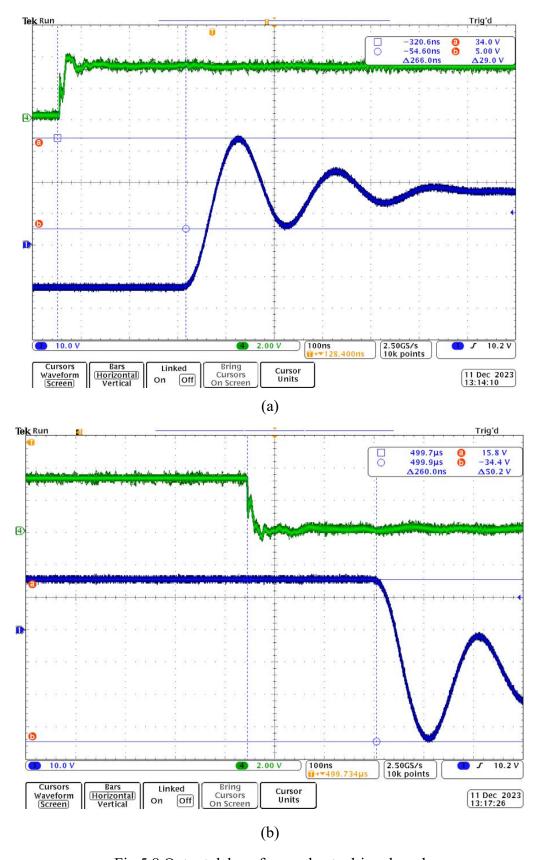

| Fig 5.8 Output delay of second gate driver board                                                                                            |

| Fig 5.9 Voltage ringing after connecting gate on resistor                                                                                   |

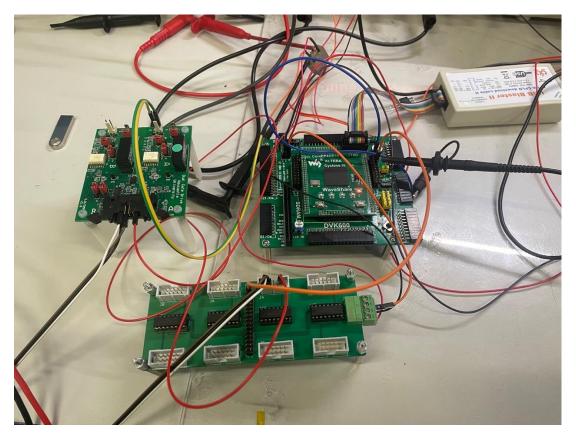

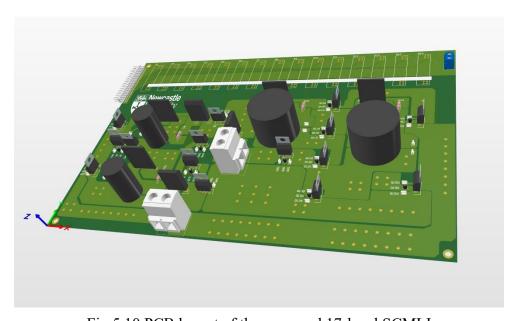

| Fig 5.10 PCB layout of the proposed 17-level SCMLI                                                                                          |

| Fig 5.11 Test bench of the inverter system                                                                                                  |

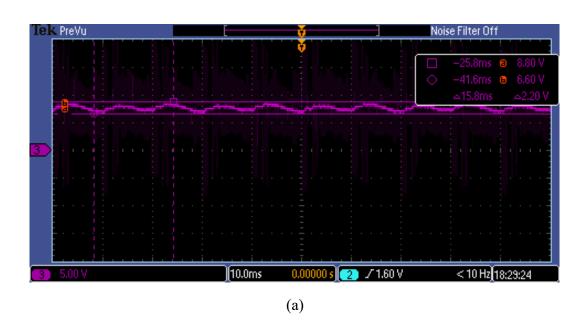

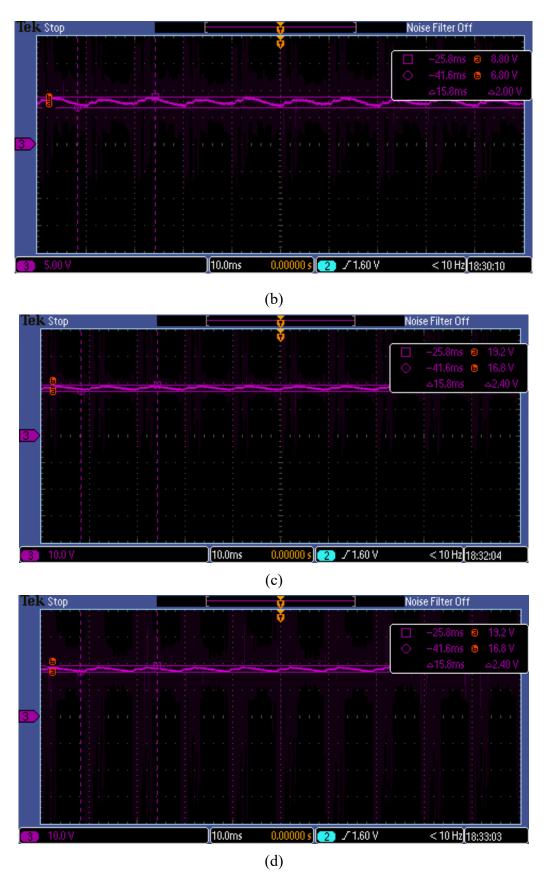

| Fig 5.12 Charging and discharging voltage of capacitors(a)capacitor C1(b)capacitor C2(c)Capacitor C3(d)capacitor C4                         |

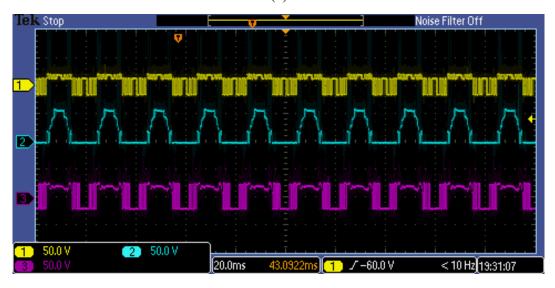

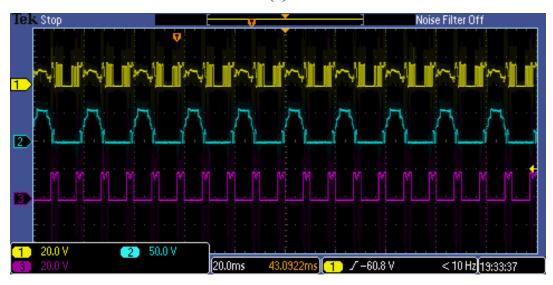

| Fig 5.13 Voltage stress of MOSFETs(a)S1-S3(b)S4-S6(c)S7-S9(d)S10-S12(e)S13-S15                                                              |

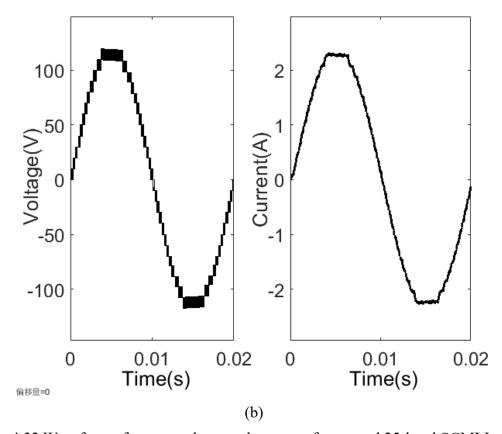

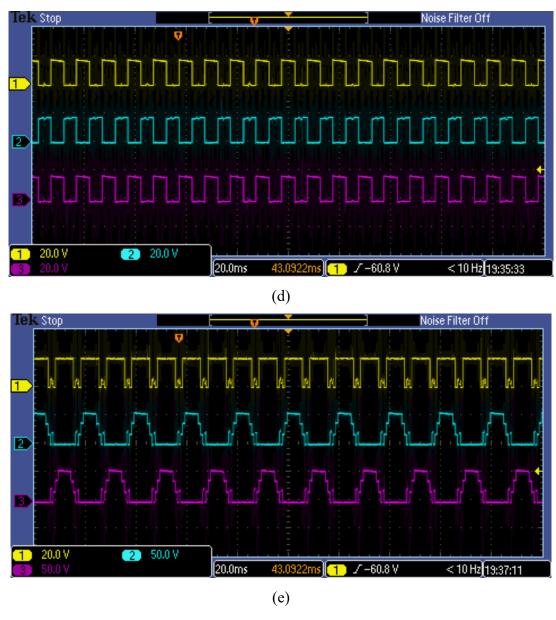

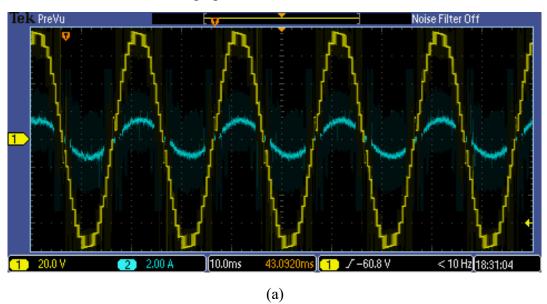

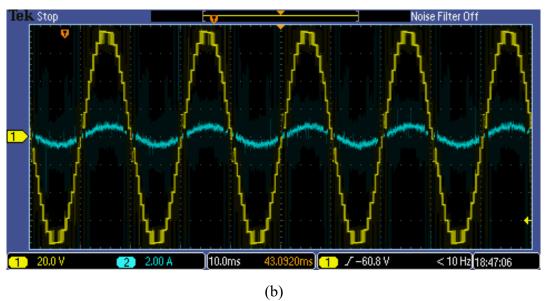

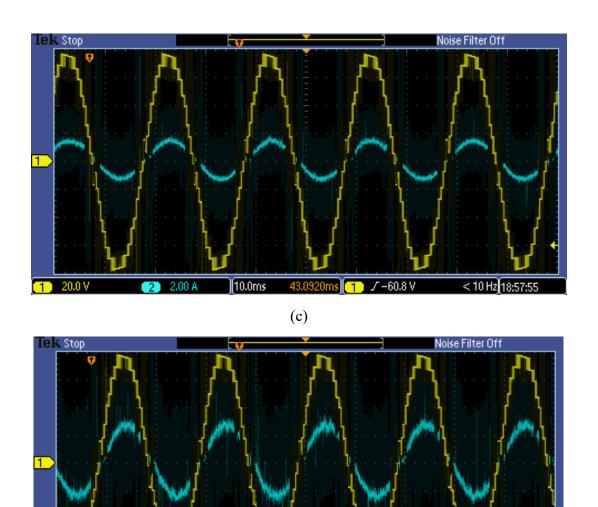

| Fig 5.14 the output voltage and current with different loads(a)50 $\Omega$ (b)100 $\Omega$ (c)50 $\Omega$ +1.5mH                            |

| $(d)50\Omega + 10 \text{mH}$                                                                                                                |

# List of tables

| Table 2.1 Switching states of a three-level flying capacitor inverter          | 26       |

|--------------------------------------------------------------------------------|----------|

| Table 2.2 Switching states of a 5-level FCMLI                                  | 28       |

| Table 2.3 Switching state of the cascaded five-level H-bridge inverter         | 31       |

| Table 2.4 Operation principles of topology proposed in [51]                    | 34       |

| Table 4.1 Switching states of proposed 13-level SCMLI                          | 61       |

| Table 4.2 Simulation model parameters                                          | 73       |

| Table 4.3 Simulation model parameters                                          | 79       |

| Table 4.4 Switching states of 17-level SCMLI                                   | 83       |

| Table 4.5 Simulation parameters                                                | 95       |

| Table 4.6 Simulation model parameters                                          | 101      |

| Table 4.7 Comparison of different topology                                     | 104      |

| Table 4.8 The number of devices per voltage gain per level of different topolo | gies.105 |

| Table 5.1 Parameters of the prototype                                          | 122      |

## **Chapter 1: Introduction**

#### 1.1 Background

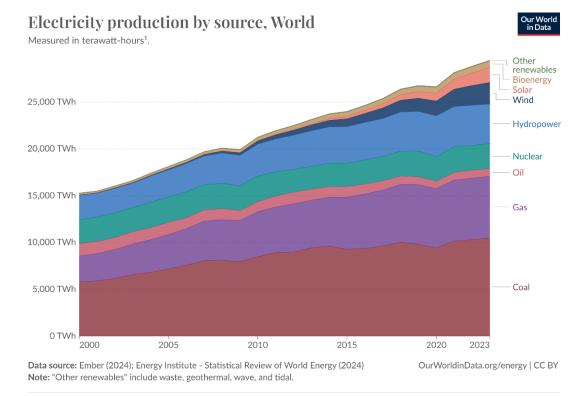

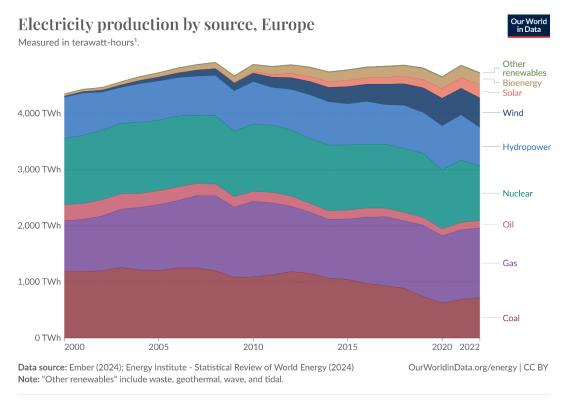

With the growth of the world's population and the improvement of the overall economic level, industry and technology are developing rapidly. Human beings are increasingly dependent on electrical energy and consume more and more electrical energy. Currently, countries around the world generally rely on traditional fossil energy power generation to meet the growing electricity demand [1]. The long-term heavy reliance on fossil energy has gradually depleted resources, and the greenhouse effect produced by carbon dioxide emissions has increased global temperatures, seriously threatening the living environment of mankind, so energy transformation is imminent [2][3]. In 2024, The United Nations pointed out the renewable energy is the cheapest option to generate electricity power. The cost of electricity generated from solar power dropped by 85% between 2010 and 2020. Affordable electricity from renewable sources could supply 65% of the world's total electricity by 2030. By 2050, it could decarbonize 90% of the power sector, significantly reducing carbon emissions and contributing to the mitigation of climate change. [4]. Figure 1.1 shows the proportion of global electricity generated by different energy sources between 2000 and 2023. It can be seen from the figure that the total global electricity generation has increased year by year from 2000 to 2023. As of 2023, renewable energy accounts for approximately 40% of the total electricity generation. However, the figure also shows that electricity generation from traditional fossil fuels is also rising year by year, indicating that the world has not yet broken its dependence on traditional fossil fuels. Figure 1.2 shows the proportion of electricity generated by different energy sources in Europe from 2000 to 2022. It can be seen that clean energy accounts for about 50% of all energy types used for power generation. However, over the past 20 years, there has been no significant change in the energy structure, and the use of traditional fossil fuels has not decreased noticeably [5]. So, the energy transition is urgent. Using wind power, solar energy and other

renewable energy to replace fossil energy is a common goal of mankind [6]. Although renewable energy generation in Europe has already surpassed that of traditional fossil fuels, it is still insufficient to eliminate reliance on them. While the development of new energy sources offers clear advantages, the initial investment in renewable power projects is often substantial. Projects like wind and solar power are highly dependent on natural conditions, making their energy output intermittent and challenging to predict. Moreover, the collection voltage of photovoltaic arrays is often lower than the grid voltage, complicating the process of integrating photovoltaic power into the grid

In the field of renewable energy power generation, compared with other power generation methods, solar energy has been vigorously developed due to its advantages such as low construction cost, simple laying, and low operating cost [7]. In the past decade, the power generation efficiency of solar power panels has been continuously improved, while the manufacturing cost has been greatly reduced. This has greatly reduced the cost of solar power generation, thus making up for the shortcomings of solar energy's greater dependence on the environment.

<sup>1.</sup> Watt-hour: A watt-hour is the energy delivered by one watt of power for one hour. Since one watt is equivalent to one joule per second, a watt-hour is equivalent to 3600 joules of energy. Metric prefixes are used for multiples of the unit, usually: - kilowatt-hours (kWh), or a thousand watt-hours. - Megawatt-hours (MWh), or a million watt-hours. - Gigawatt-hours (GWh), or a billion watt-hours. - Terawatt-hours (TWh), or a trillion watt-hours.

Fig 1.1 Distribution diagram of global power generation by different power generation methods from 2000 to 2023[8]

1. Watt-hour: A watt-hour is the energy delivered by one watt of power for one hour. Since one watt is equivalent to one joule per second, a watt-hour is equivalent to 3600 joules of energy. Metric prefixes are used for multiples of the unit, usually: - kilowatt-hours (kWh), or a thousand watt-hours. - Megawatt-hours (MWh), or a million watt-hours. - Gigawatt-hours (GWh), or a billion watt-hours. - Terawatt-hours (TWh), or a trillion watt-hours.

Fig 1.2 Distribution diagram of Europe power generation by different power generation methods from 2000 to 2022 [8]

The inverter is an important component of the photovoltaic grid-connected system, which plays the role of connecting the photovoltaic power generation array and the power grid. Usually, the transformer plays the role of current isolation between the solar power generation panel and the grid, and the DC-DC converter plays the role of balancing the voltage level between the photovoltaic panel and the grid [9][10]. However, due to the access of the transformer and DC-DC converter, the transmission efficiency of the system will be reduced [11]. The above-mentioned problems have been improved with the introduction of transformerless multilevel inverters [12][13][14][15][16].

#### 1.2 Research gap and motivation

In recent years, a large number of scholars have participated in research on multi-level inverters. Research on multi-level inverters includes optimizing topology to obtain high-level output, but more level outputs often increase the use of switching devices [17]. The disadvantages are that it increases the manufacturing cost of the inverter and complicates the control logic of the inverter. In addition, more switching devices will also increase the loss of the inverter and reduce the transmission efficiency. So how to reasonably optimize the inverter topology is a challenge [18][19][20]. Research on inverter topologies with self-boosting capabilities has also received much attention, which helps to abandon the use of DC-DC converters in photovoltaic inverter systems. In addition, the self-boosting topology makes the inverter suitable for high-power applications. But the same disadvantage is that the number of DC supply and switching devices in the inverter will increase as the voltage gain increases [21]. Therefore, how to use fewer devices to obtain higher voltage gain is one of current research challenges. In addition, blindly increasing the voltage gain while ignoring the number of output levels will increase the voltage difference between each step of the output level and increase the harmonics of the output voltage. With the development of semiconductor technology, such as silicon carbide (SiC) and gallium nitride (GaN) devices, further research is needed on how to best utilize these advanced devices in multi-level inverter applications. The control of multi-level inverters is an important part of inverter research. Designing more advanced control strategies and algorithms to improve dynamic performance, reduce harmonics and improve reliability of multi-level inverters is also the main direction of current research. For switched capacitor multilevel inverters, in addition to the above research challenges, it also includes realizing self-balancing of capacitor voltage by designing control strategies and rationalizing the capacity and layout of capacitors.

Traditional multilevel inverter structures face the challenge of a significant increase in the number of components as the number of output voltage levels increases [22]. Additionally, these inverter designs usually lack voltage self-boosting capability. As a result, a boost converter is commonly required at the input side to raise the input voltage to the desired level [23]. However, this additional boost converter introduces extra power losses, which reduces the overall system efficiency.

Designing an inverter with self-boosting capability that can achieve high voltage gain (boost) and generate a higher number of output voltage levels while using fewer switching components would greatly improve energy conversion efficiency and power quality [24]. Switched capacitor inverters meet these requirements by utilizing the charging and discharging processes of capacitors to achieve self-boosting functionality. The structure and control logic of inverters are designed specifically around these capacitor operations, effectively reducing the number of switching components required.

Since the boost converter structure that uses magnetic components (inductors) to boost voltage has been eliminated in practical applications, the overall volume and weight of capacitors are smaller than those of inductors in applications with the same power level. Therefore, SCMLIs are efficient, compact, and modular, making them suitable for microgrids and off-grid power systems, vehicle-mounted inverter systems and motor drives.

#### 1.3 Scope of the project

Based on the research challenges on multilevel inverter described above. This thesis proposed two switched capacitor multilevel inverter. The first one is 13-level switched capacitor inverter, and it has 3 times of voltage gain. The second is 17-level switched capacitor inverter and it has 4 times of voltage gain. They use fewer switching devices and are fully symmetrical structures, which helps simplify the control logic. The benefit of the optimized topology is that the voltage difference of each level in the output voltage of the two proposed topologies is 1/2 of that of others, which significantly improves the waveform quality and reduces the harmonic content. In addition, it is

worth noting that the two topologies proposed use single power supply, which fundamentally avoids the occurrence of voltage imbalance. And through the control logic, the self-balancing of the capacitor is achieved.

The control strategies for the two proposed topologies are designed in this thesis, and using MATLAB/Simulink to conduct simulation experiments, and finally produced a prototype of the 17-level switched capacitor inverter. In the hardware experiment part, FPGA (field-programmable gate array) was used to study the algorithm for controlling the designed inverter prototype. In addition, the gate driving circuit is also studied. After completing these preparatory experiments, all parts were combined into a test bench, experiments were conducted on the performance of the proposed inverter, and the experimental results were collected.

#### 1.4 Contribution

The contributions of this thesis are described following:

- (a) A novel 13-level switched capacitor inverter is proposed in this thesis.

- (b) A novel 17-level switched capacitor inverter is proposed in this thesis.

- (c) A combination idea based on switched capacitor structure and a parallel/series connected switched capacitor unit are proposed. This kind of unit can be used in different switched capacitor inverter topologies to obtain high output voltage gain.

- (d) The control strategy based on the multicarrier PWM technology is simplified through the design of topology.

#### 1.5 Thesis summary

This thesis consists of 6 chapters. Chapter 1 explains the background of the research and describes the research challenges of multi-level inverters. Chapter 2 begins with a brief description of the development of multi-level inverters, followed by an introduction to the operating principles, advantages and disadvantages of a series of

traditional multilevel inverters. Finally, a comprehensive review of the topologies proposed in previous papers from different researchers is conducted. Chapter 3 presents the modulation strategies of the multilevel inverter and describes the principle and then using MATLAB/Simulink to build the models to fully understand them. The second part of this chapter is the calculation method of the capacitance of the capacitors utilized in the switched capacitor inverter topology. Chapter 4 proposes two novel switched capacitor inverter topologies and describes the operation principle. Following that, the comparative study of simulation results is analyzed comprehensively. Chapter 5 shows the detailed prototype construction and hardware experiment of the proposed 17-level switched capacitor inverter, and the experiment results are explained at the end. Chapter 6 concludes the research of this thesis and presents the plan of future work.

## **Chapter 2: Review of Multilevel inverters**

#### 2.1 Introduction

With the current technical level, the voltage withstands capability of a single power electronic device is limited. To realize a high-power converter, it is necessary to resort to series connection of switching devices or multi-level technology. Although the inverter using the switch series technology has a simple structure, it will bring about problems such as static voltage equalization and dynamic voltage equalization of the switching device [25]. The multi-level inverter topology is widely used in medium and high-voltage high-power systems because it can output high voltage value and increase the number of the voltage level without increasing the withstand voltage rating of the semiconductor switching devices [26]. As the number of output voltage levels increases, the output voltage is closer to a sinusoidal waveform, which can significantly reduce THD to improve power quality [27]. Common multi-level topologies include NPC, FC, and CHB. The working voltage of each diode in the NPC multi-level inverter topology is half of the DC voltage source, so it can be directly applied to systems with medium and high voltage systems. However, in a three-phase NPC inverter, if the output level of any two phases is 0, the load current will flow into or out of the neutral point, which will increase or decrease the neutral point voltage, causing the voltage of the two capacitors to be different and affecting the quality of the output voltage. Therefore, it is necessary to consider the balance of capacitor voltage when designing NPC inverters [28]. Compared with NPC inverters, FC inverters have no diodes, thus overcoming the shortcomings of NPC, but as the number of output voltage levels increases, the number of flying capacitors will increase, increasing the size of the inverter and cost. In addition, too many capacitors will lead to an increase in the inverter failure rate [29][30]. The CHB inverter is cascaded by H-bridge modules to achieve multi-level output voltage. Each module in the CHB inverter is powered by an independent voltage source, and each H-bridge module can generate voltage values in three states—V, 0, and V. The sum of the output voltage of each module constitutes the multi-level voltage output by the

inverter. Compared with the other two topological structures, CHB inverters do not have the problem of balancing capacitor voltage and have fewer power electronic devices [31]. The modular structure is convenient for manufacturing and maintenance and is beneficial to improve system stability [32]. As mentioned earlier, the higher the number of voltage levels, the more the waveform is close to sinusoidal, and the higher the power quality. Thanks to the modular structure, CHB inverters can more easily obtain higher levels of voltage by stacking H-bridge modules. However, the disadvantage of this topology is that a large number of isolated DC sources are required when outputting voltage with a high number of levels.

In recent years, in order to obtain higher quality power, the number of MLI levels has also increased, which has led to an increase in the number of power switches and dc voltage sources, which has reduced the conversion efficiency of the system, increased costs, and will also affect the power output of the system quality[33]. The drawbacks of conventional MLI promote the development of hybrid multi-level inverter[34]. In this chapter, some structure of the multilevel inverters will be presented, and the advantages and disadvantages will be analyzed.

#### 2.2.1 Diode-clamped multilevel inverters

Diode-clamped MLI is one of the earlier researched multilevel topology structures. This type of MLI applies only one DC supply and using the diodes to generate voltage levels and the topology of a standard three-level DCMLI is shown in Figure 2.1. Generally, the basic topology operates three voltage levels and the modulation strategy of this structure is concise, and for the fundamental switching frequency it has relatively high efficiency. For an N-level DCMLI, there will (N-1)\*(N-2) diodes and (N-1) capacitors applied in the circuit. The balancing of the capacitor voltage is a challenging and the increased number of diodes used in the circuit make the system complicated [35][36].

Fig 2.1 Topology of a standard three-level DCMLI

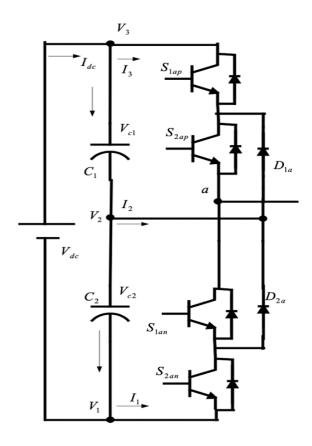

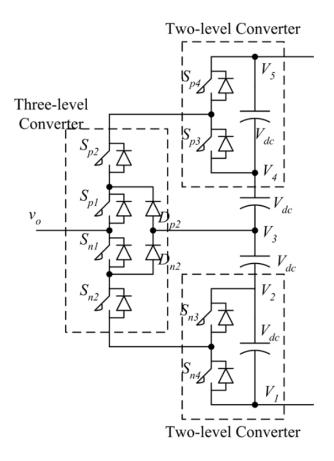

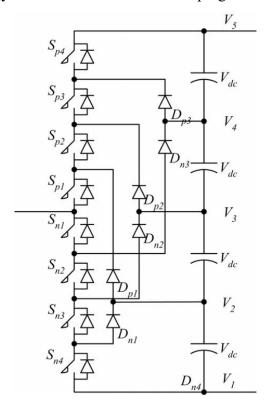

A five-level DCMLI is proposed in [37]. The topology designed in this paper is shown in Figure 2.2 and the standard five-level DCMLI is shown in Figure 2.3. Comparing these two topologies, it can be found the author replaced the three-level converter of the positive bus with the two-level converter to reduce the number of clamping diodes. But the voltage stress on the  $s_{p1}$   $s_{n1}$   $D_{p2}$   $D_{n2}$  increased from Vdc to 2Vdc. The proposed topology maintains the same number of switching devices as the traditional topology but slightly increases the total voltage rating of the switching devices. Therefore, this limits the application of this topology in high-voltage, high-power systems. Additionally, the proposed topology may require more complex control strategies to ensure voltage balancing among the levels.

Fig 2.2 Topology of a reduced number of clamping diode five-level DCMLI

Fig 2.3 Topology of standard five-level DCMLI

In [38], a new DCMLI is proposed to eliminate the imbalance of the capacitor voltage, and it is shown in Figure 2.4. The inductors are inserted between the diodes and the main switches, and the voltage balance of the DC capacitors is guaranteed by controlling the opening time of the corresponding main switches in specific modes. This eliminates the need for parallel circuits on the DC side, resulting in fewer switches, diodes, and capacitors. The proposed topology reduces costs while maintaining suitability and applicability. The document also analyzes the voltage imbalance in conventional diode-clamped multilevel inverters and presents the compensation principle of the proposed topology.

Fig 2.4 Topology of a novel DCMLI to eliminate the capacitor voltage imbalance

#### 2.2.2 Flying-capacitor multilevel inverter

The flying capacitor multilevel inverter was first proposed by Meynard and Foch in 1992 [39]. Compared with the DCMLI, the capacitors were applied to instead the diode and the basic 3-level FCMLI is shown in Figure 2.5. There are three capacitors in the circuit and each capacitor is charged to 1/2Vdc, by different switching states the circuit can generate -1/2Vdc, 0, 1/2Vdc three voltage levels as follows:

When the circuit output -1/2Vdc, the switches S3 and S4 are in the ON state.

When the circuit output 1/2Vdc, the switches S1 and S2 are in the ON state.

There are two switching states to generate 0Vdc, the first one is switches S1 and S3 in the ON state, and the other one is switches S2 and S4 in the ON state.

Table 2.1 shows the switching states of different output voltages. It can be seen from the table, the switches S1 and S4 cannot be conducted at the same time. And the switches S1 and S3, switches S2 and S4 are conducted complementary. Moreover, there are two switching states to generate 0 voltage levels, and the different switch states to generate the same voltage is termed redundant switching states. And the redundant switching states can improve the reliability of the MLI. That is because when one switching state is failure and cannot generate the desired output level redundancy can be used to maintain the output. For FCMLI, the redundant switching state can be used to balance the capacitor voltage to ensure they can operate properly.

Fig 2.5 Topology of a three-level FCMLI

| Vo      | S1 | S2 | S3 | S4 |

|---------|----|----|----|----|

| +1/2Vdc | 1  | 1  | 0  | 0  |

| 0       | 1  | 0  | 1  | 0  |

| 0       | 0  | 1  | 0  | 1  |

| -1/2Vdc | 0  | 0  | 1  | 1  |

Table 2.1 Switching states of a three-level flying capacitor inverter

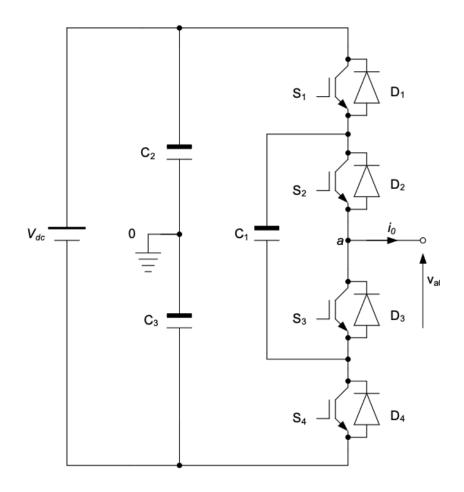

The redundant switching state will become apparent in FCMLI topologies that output more voltage levels. A standard five-level FCMLI is shown in Figure 2.6, there are 4 dc link capacitors and 6 clamping capacitors, the switching states are followed:

- (1) When output 1/4Vdc, switches S1, S2, S3 and S1' are in the ON state, or S2, S3, S4 and S4' are in the ON state, or S1, S2, S4 and S2' are in the ON state.

- (2) When output 1/2 Vdc, switches S1 S2 S3 S4 are in the ON state.

- (3) When output 0Vdc, switches S1, S2, S1'and S2' are in the ON state, or S3, S4, S3'

and S4' are in the ON state, or S1, S3, S1' and S3' are in the ON state, or S1, S4, S2', S3' are in the ON state, or S2, S4, S2' and S4' are in the ON state, or S2, S3, S1' and S4' are in the ON state.

- (4) When output -1/2Vdc, switches S1', S2', S3' and S4' are in the ON state.

- (5) When output -1/4Vdc, switches S1, S1', S2'and S3' are in the ON state, or switches S2', S3', S4' and S4 are in the ON state, or S1', S3', S4 and S3 are in the ON state, or S1', S2', S4' and S2 are in the ON state.

Table 2.2 summarises all the switching states of the 5-level FCMLI, and there are a lot of redundant states when the inverter output 1/4Vdc, 0Vdc and -1/4Vdc. The redundant states make the inverter output voltage and balancing dc link capacitor voltage more flexible. Nevertheless, there still needs a specific method to balance the clamping voltage of capacitors (flying capacitors). And for an N-level topology, the number of clamping capacitors used in the circuit is (N-1)(N-2)/2. Therefore, a large number of capacitors will be applied in high voltage level FCMLI topology. This will undoubtedly complicate the capacitor voltage balancing strategy and reduce the system reliability.

Fig 2.6 Topology of a five-level FCMLI

| Vo      | S1 | S2 | S3 | S4 | S1' | S2' | S3' | S4' |

|---------|----|----|----|----|-----|-----|-----|-----|

| +1/2Vdc | 1  | 1  | 1  | 1  | 0   | 0   | 0   | 0   |

| +1/4Vdc | 1  | 1  | 1  | 0  | 1   | 0   | 0   | 0   |

| +1/4Vdc | 0  | 1  | 1  | 1  | 0   | 0   | 0   | 1   |

| +1/4Vdc | 1  | 1  | 0  | 1  | 0   | 1   | 0   | 0   |

| 0       | 1  | 1  | 0  | 0  | 1   | 1   | 0   | 0   |

| 0       | 0  | 0  | 1  | 1  | 0   | 0   | 1   | 1   |

| 0       | 1  | 0  | 1  | 0  | 1   | 0   | 1   | 0   |

| 0       | 1  | 0  | 0  | 1  | 0   | 1   | 1   | 0   |

| 0       | 0  | 1  | 0  | 1  | 0   | 1   | 0   | 1   |

| 0       | 0  | 1  | 1  | 0  | 1   | 0   | 0   | 1   |

| -1/2Vdc | 0  | 0  | 0  | 0  | 1   | 1   | 1   | 1   |

| -1/4Vdc | 1  | 0  | 0  | 0  | 1   | 1   | 1   | 0   |

| -1/4Vdc | 0  | 0  | 0  | 1  | 0   | 1   | 1   | 1   |

| -1/4Vdc | 0  | 0  | 1  | 1  | 1   | 0   | 1   | 0   |

| -1/4Vdc | 0  | 1  | 0  | 0  | 1   | 1   | 0   | 1   |

Table 2.2 Switching states of a 5-level FCMLI

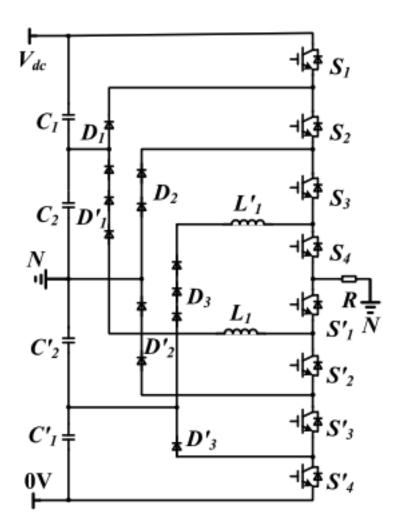

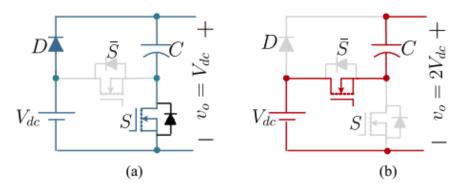

There are some new topology and balancing strategy proposed to eliminate the drawbacks referred above. In[40], a carrier-based PWM method is proposed by the author to balance the capacitor voltage. By utilizing the new carriers and the leg voltage redundancy, the average capacitor voltage change can be control to 0 during a specific period. The simulation results from this paper shows the new modulation method have a better harmonics performance than phase shifted PWM and also achieves better capacitor voltage balance. The conventional FCMLI is a kind of step-down inverter, in order to adapt to some circumstances, transformers are necessary. For example, in the grid-connection generation system using the FCMLIs, the generated voltage from the PV panels is usually smaller than the grid voltage, so there is necessary a boost module applied to the system [42][42]. In [43], a novel five-level inverter is proposed, and the topology of the single phase is shown in Figure 2.7. The topology is obtained by cascading two FC module and has an ability to boost the output to two times of the DC source. In addition, the number of capacitors utilized in this topology is fewer than the

conventional FCMLI with the same output voltage level. And the most significant feature is that the proposed topology has the capability to self-balance the capacitor voltage. In addition to the topology discussed above, a 13-level FCMLI proposed in [44] also has the capability to self-balancing and voltage boosting. And it can be seen from Figure 2.8, there are 2 DC voltage source and 4 capacitors applied in the circuit to obtain 3 times voltage boost.

Fig 2.7 Topology of a novel five-level inverter proposed

#### 2.2.3 Cascaded Multilevel inverter

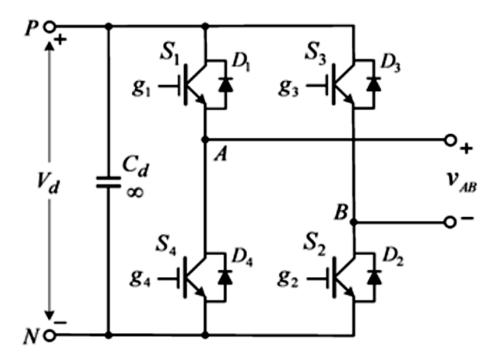

The basic structure of DCMLI and FCMLI have the same feature of utilizing one DC supply and multiple capacitors connected in series to divide the DC voltage. The advantage of that is the voltage stress between the switches are equal to one of the capacitor voltages. This allows the inverter to output a high voltage while ensuring a low voltage stress between the switches [45]. But without any control, the capacitor voltage is hard to be balanced. Cascaded multilevel inverter is formed by cascading multiple modules with independent DC supply, so there is no capacitor balancing issue. The cascaded H-bridge multilevel inverter is the simplest and widely used topology,

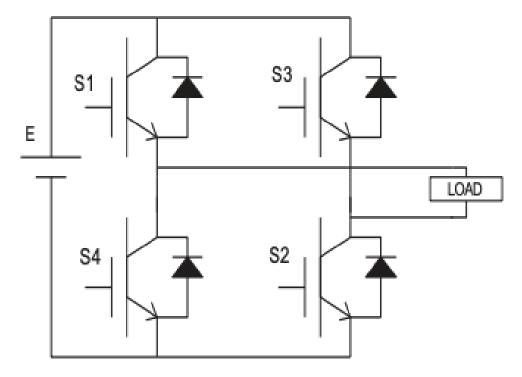

especially for high power application [46]. That is because the CHB multilevel inverter can be effectively extended to a high output voltage and a large number of voltage level by cascading a corresponding number of H-bridge [47]. The topology shown in Figure 2.8 is a three-level H-bridge inverter and it is the basic module of the cascaded H-bridge multilevel inverter. When the switches S1 and S2 are conducted the output voltage is E. When the switches S3 and S4 are conducted, the output voltage is -E, when the switches S2 and S3, or S1 and S4 are conducted, the output voltage is 0.

A 5-level CBMLI is derived by cascading two H-bridge modules and the output voltage is from -2E to 2E. The topology is shown in figure 2.9 and the switching states are shown in Table 2.3.

Fig 2.8 topology of a three-level H-bridge inverter

Fig 2.9 Topology of a cascade five-level H-bridge inverter

| Output            | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 |

|-------------------|----|----|----|----|----|----|----|----|

| Output<br>Voltage |    |    |    |    |    |    |    |    |

| +E                | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| +2E               | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  |

| 0                 | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| -2E               | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| -E                | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  |

Table 2.3 Switching state of the cascaded five-level H-bridge inverter

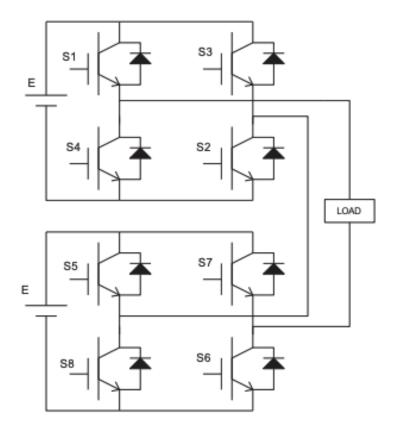

Each H-bridge module of the 5-level CHB inverter discussed above has the same value of DC supply, so this kind of topology named symmetric cascaded H-bridge inverter. But for the high-power application, it is the trend that the high voltage output of the inverter with minimum number of switches. That is because the fewer number of switches applied in the circuit, the lower switching loss generated and the higher efficiency the inverter obtained.

Therefore, using different value of DC supply is an effective way to increase the output voltage and voltage value. This kind of layout named asymmetric CHBMLI [48][49].

There are two methods to arrange the value of DC supply for different H-bridge modules. For an ACHBMLI with two H-bridge modules, the value of one DC supply is E and the value of the other module is 2E. This kind of DC supply arrangement named binary method. Similarly, if the DC supply of one module is E and the other is 3E, this arrangement names ternary method. For the extension of the ACHBMLI, the ratio of DC supply values of binary method is 1:2:4:..: $2^{N-1}$  and the ratio for the ternary method is 1:3:9:..: $3^{N-1}$ . Therefore, the maximum output voltage and the output voltage level of the binary ACHBMLIs can be expressed by  $2^N - 1 V_{dc}$  and  $2^{N+1} - 1$  respectively. In the same way, the maximum output voltage and the output level of the ternary ACHBMLIs can be obtained by  $\frac{3^{N-1}}{2} V_{dc}$  and  $3^N$  respectively [50]. Among them, N represents the number of H-bridge modules in the circuit.

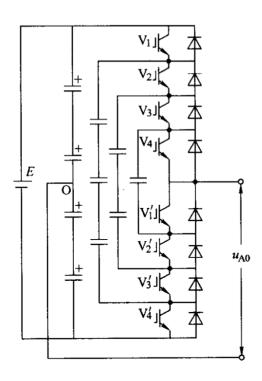

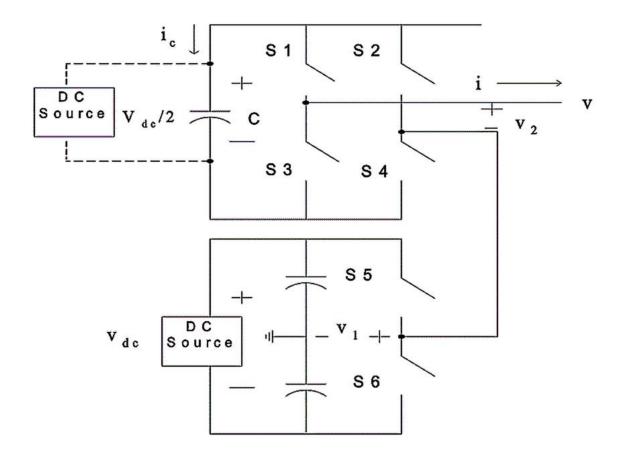

The above is a detailed analysis of the topology of the H-bridge circuit acting as a cascade module. In addition, in order to further reduce the use of switching devices, some scholars have explored the cascaded multilevel inverters applied to other modules. Figure 2.10 is a hybrid 5-level cascaded inverter designed in [51]. Knowing from figure 2.10, the topology is obtained by cascading a H-bridge inverter and one leg of a three-phase two-level inverter. A capacitor replaces the DC voltage source of the h-bridge cell to reduce the number of DC supply utilized in the circuit and operation principle of capacitor is shown in Table2.4. Although the application of the capacitor can reduce the number of DC supply, the discharge of the capacitor is an attenuation process. To maintain the stability of the electric energy, a capacitor with an enormous capacitance value is required which increases the cost. In addition, the lower safety of the capacitor reduces the reliability of the system.

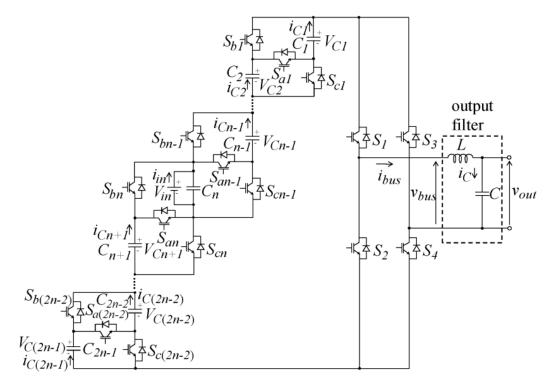

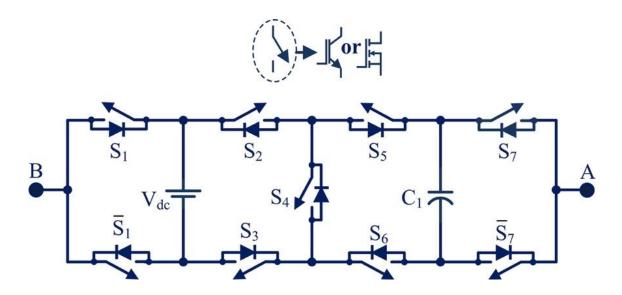

The new module shown in figure 2.11 is discussed in [52]. The module proposed by the author is also intended to use fewer switching devices to obtain higher output voltage and more output levels. And the author simplifies the drive circuit by using a large number of bidirectional MOSFETs. In addition, the author also conducted a detailed study on the DC supply arrangements of the binary method and ternary method of the

proposed module. The 49-level inverter composed of three modules in cascade is shown in figure 2.12, and comparative study with traditional cascaded inverters was conducted, and the results shows that the components utilized by the proposed inverter is the least.

Fig 2.10 Topology of a hybrid 5-level cascaded inverter

| Output voltage | V1     | V2     | С           |

|----------------|--------|--------|-------------|

| Vdc            | Vdc/2  | Vdc/2  | Discharging |

| Vdc/2          | Vdc/2  | 0      | Do not work |

| 0              | Vdc/2  | -Vdc/2 | Charging    |

| 0              | -Vdc/2 | Vdc/2  | Discharging |

| -Vdc/2         | -Vdc/2 | 0      | Do not work |

| -Vdc           | -Vdc/2 | -Vdc/2 | Charging    |

| Vdc            | Vdc/2  | Vdc/2  | Charging    |

| Vdc/2          | Vdc/2  | 0      | Do not work |

| 0              | Vdc/2  | -Vdc/2 | Discharging |

| 0              | -Vdc/2 | Vdc/2  | Charging    |

| -Vdc/2         | -Vdc/2 | 0      | Do not work |

| -Vdc           | -Vdc/2 | -Vdc/2 | Discharging |

Table 2.4 Operation principles of topology proposed in [51]

Fig2.11 Basic cascaded unit proposed in [52]

Fig 2.12 Cascaded multilevel inverter proposed in [52]

#### 2.2.4 Switched capacitor multilevel inverter

The cascaded multilevel inverter described above has the capability to output a high power when a number of modules are cascaded. However, the apparent disadvantage is several DC supplies are applied into the circuit [53][54][55]. This will limit its utilization in single power supply applications, such as PV generation, fuel cells, etc. [56][57]. Moreover, traditional multi-level inverters do not have the ability to self-boost, so in the field of power generation, especially in the field of solar power generation, a transformer is required to match the inverter output voltage with the grid-connected voltage [58].

Due to the many disadvantages of conventional multilevel inverters, new MLI topologies have been proposed in recent years. Among them, the switching capacitor MLI has great research values because the features of reduced components numbers, simplified control scheme, self-balanced capacitor voltage and step-up system [59].

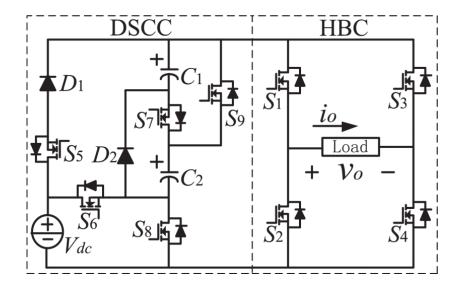

The switched capacitor inverter was originally reported by On-cheong Mak and Adrian Ioinovici in 1998 [60] and has been widely studied in the last ten years. The basic principle of the switched capacitor inverter is to use the capacitor in the circuit to reasonably arrange the charge and discharge time and the charge and discharge circuit by controlling the logical conduction of the switch to output the desired voltage value and level. The figure 2.13 below shows the basic unit circuit of a switched capacitor. The circuit highlighted by blue line is the charging circuit and the red line represents the discharging circuit. Therefore, when the isolated voltage source and the capacitor are connected in series, the capacitor is charged, and when the voltage source and the capacitor are connected in parallel, the capacitor is discharged by connecting one or more basic units and designing a polarity shift circuit, a basic switched capacitor inverter structure can be obtained. The topology derived by connecting the basic SCunit is shown in figure 2.14 [61]. It can be seen the topology can be easily extended by connecting more SC-unit and polarity shift is operated by the H-bridge. The topology proposed in [62], after substituting the DC supply with capacitors, can be seen as an optimization of the topology illustrated in figure 2.14. The updated configuration is presented in figure 2.15. By cascading the switched capacitor circuit with a full-bridge circuit, this design achieves a higher output voltage and a greater number of voltage levels, accompanied by a reduced dv/dt. This improvement theoretically results in lower electromagnetic interference (EMI) and reduced harmonic distortion.

Furthermore, the switched capacitor circuit depicted in figure 2.16 has been derived from modifications made to the topology shown in figure 2.13 [63].

The proposed switched circuit uses fewer switches to control the charging and discharging of two capacitors. And the same, the H-bridge is utilized to polarity shift. It can be found from Table 2.5, when there is one SC-unit connected in the circuit, the proposed topology has two times of voltage boost with 9-level output.

Fig 2.13 Basic unit circuit of a switched capacitor

Fig 2.14 Topology by connecting several basic units

Fig 2.15 Cascaded switched capacitor multilevel inverter with the basic unit

| Voltage      | Swi   | tches | Sv    | vitch | es in | DSC   | CC    | Diodes |       | Capacitors |       |                 |       |

|--------------|-------|-------|-------|-------|-------|-------|-------|--------|-------|------------|-------|-----------------|-------|

| levels       | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$  | $S_9$ | $D_1$      | $D_2$ | $\mathcal{C}_1$ | $C_2$ |

| $2V_{dc}$    | 1     | 0     | 0     | 1     | 1     | 1     | 1     | 0      | 0     | 0          | 0     | D               | D     |

| $3V_{dc}/2$  | 1     | 0     | 0     | 1     | 1     | 1     | 0     | 0      | 1     | 0          | 1     | D               | D     |

| $V_{dc}$     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1      | 0     | 1          | 0     | С               | С     |

| $V_{dc}/2$   | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 1      | 1     | 0          | 1     | D               | D     |

| 0            | 0     | 1     | 0     | 1     | 0     | 0     | 0     | 1      | 1     | 0          | 0     | -               | -     |

| $-V_{dc}/2$  | 0     | 1     | 1     | 0     | 0     | 0     | 0     | 1      | 1     | 0          | 1     | D               | D     |

| $-V_{dc}$    | 0     | 1     | 1     | 0     | 1     | 0     | 0     | 1      | 0     | 1          | 0     | С               | С     |

| $-3V_{dc}/2$ | 0     | 1     | 1     | 0     | 1     | 1     | 0     | 0      | 1     | 0          | 1     | D               | D     |

| $-2V_{dc}$   | 0     | 1     | 1     | 0     | 1     | 1     | 1     | 0      | 0     | 0          | 0     | D               | D     |

Table 2.5 Operation principle of the 9-level switched capacitor inverter

Fig 2.16 Nine-level switched capacitor inverter with H-bridge

However, the switched capacitor MLI mentioned above uses an H-bridge for the polarity shift of the output voltage, and the voltage stress on switches of the H-bridge is several times that of the DC voltage source. So, avoiding using H-bridge can minimize the switching loss and voltage stress across the semiconductor components.

The SCMLI without H-bridge topology proposed in [64] is shown in figure 2.17. The mentioned topology can generate bipolar output voltage without an H-bridge and the amplitude is two times to the DC source.

Fig 2.17 Switched capacitor multilevel inverter without H-bridge

#### 2.1 Chapter conclusion

In this chapter, a comprehensive review and discussion of various typical multilevel inverter types are conducted. Traditional structures include the diode-clamped multilevel inverter, flying capacitor multilevel inverter, cascaded inverter, switched capacitor inverter, and several hybrid multilevel inverters optimized for specific characteristics. The diode-clamped multilevel inverter achieves multilevel and sinusoidal outputs by using clamping diodes to clamp the capacitor voltage (connected in parallel with the input power source) to the output. This topology has a high voltagehandling capability since each switch only needs to withstand voltage stress of  $V_{dc}$ . However, as the number of output voltage levels increases, the number of diodes and capacitors required grows significantly, increasing the inverter's size and losses. Additionally, the capacitors at the output often face voltage imbalance issues, requiring extra voltage balancing strategies to maintain high-quality voltage outputs. The flying capacitor multilevel inverter generates multilevel outputs by controlling the charge and discharge processes of capacitors through switch combinations. The charge/discharge of flying capacitors effectively balances capacitor voltage, avoiding the imbalance issues seen in diode-clamped inverters. However, as the output voltage levels increase, the number of switches and capacitors in the circuit also rises, leading to larger system size and more complex control algorithms. The cascaded H-bridge multilevel inverter relies on the combination of four switches to achieve voltage level variation at the output. Its main advantage lies in the scalability, as higher voltage levels can be obtained by simply cascading multiple H-bridge units. The control algorithm is simple and logically robust. However, increasing the number of voltage levels also increases the number of switches required. Moreover, cascading multiple H-bridges necessitates the connection of multiple input voltage sources, and without proper balancing mechanisms, the quality of the output waveform may deteriorate significantly. The switched capacitor multilevel inverter achieves voltage boosting and multilevel output by controlling the charge and discharge of capacitors. The switches in the circuit are

designed to facilitate efficient capacitor charge/discharge, ensuring self-balancing of capacitor voltage and stable, high-quality output waveforms. This structure features high voltage levels and a reduced number of switching devices. However, due to the lack of a uniform configuration, designs by different researchers vary significantly. The primary challenges include achieving high voltage gain and a large number of voltage levels using fewer components. Additionally, the self-boosting characteristic of the switched capacitor inverter increases the voltage stress on the switches, necessitating circuit designs that minimize the number of switches operating under high voltage stress. In this chapter, it is observed that most researchers connect an H-bridge at the inverter's output to achieve polarity shifting. However, this approach subjects all four switches in the H-bridge to maximum voltage stress, which increases switching losses and reduces switch reliability. The primary research directions for switched capacitor multilevel inverters are summarized as follows: reducing the number of switching devices, minimizing the voltage stress on switches, increasing the number of output voltage levels, enhancing the voltage gain at the output, and achieving self-balancing of capacitor voltage.

# **Chapter 3: Methodology**

#### 3.1 Chapter introduction

This chapter presents the modulation strategies for multilevel inverters, including conventional sinusoidal pulse width modulation (SPWM) and multicarrier pulse width modulation (PWM). Since multicarrier PWM is a widely used technique for controlling switched capacitor multilevel inverters, the chapter focuses on its principles. MATLAB/Simulink is used to build multicarrier PWM models, demonstrating how to generate switching signals for the inverter by combining sine and triangular wave comparison signals. Additionally, the method of calculating capacitance values in switched capacitor multilevel inverters is also discussed in this chapter

#### 3.2 Pulse-width modulation strategy (PWM)

PWM is a commonly used strategy to control the inverter to output voltages and currents especially the sinusoidal [65][66][67]. In PWM, the desired output waveform of system is the reference signal, and the wave that is modulated is the carrier wave. The reference signal of the SPWM is the sinusoidal wave and the triangle carrier wave is commonly utilized to compare with the reference wave to generate the modulating wave [68]. Furthermore, the SPWM can be classified as unipolar SPWM method and bipolar SPWM method due to the polarity of the output control signal [69]. Figure 3.1 shows a standard h-bridge inverter and the four IGBTs are controlled by the signal generated by SPWM strategy. Both the unipolar and bipolar method can be used to generate the control signal of the H-bridge inverter, and the detailed introduction will be illustrated as follows.

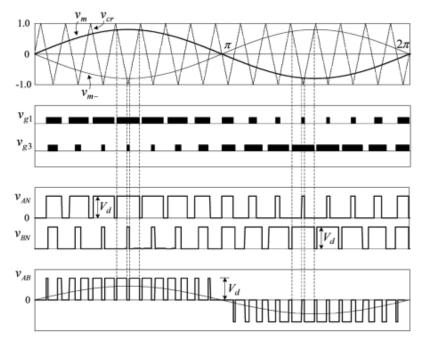

The switches in the same leg of the H-bridge inverter are conducted complementary. The state of Switches S1 and S2 can be controlled with the same gate signal. And similarly, the control signal of S3 and S4 is the same. Therefore, there are only two signals that will be considered when using the SPWM strategy [70]. It can be found in figure 3.2 there are two sinewaves used to be the reference signal and phase difference

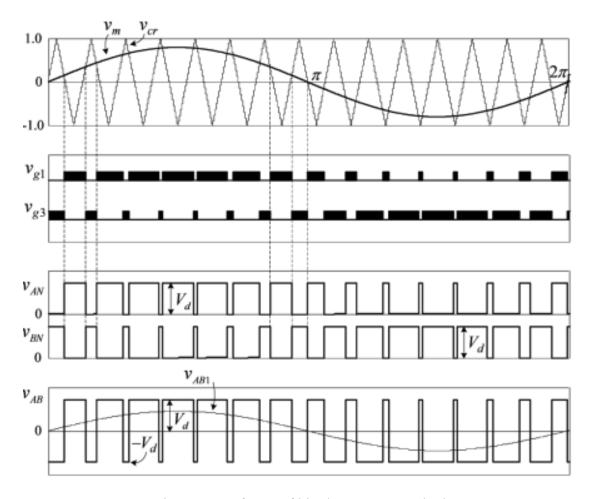

of the two sinewaves is 180 degrees. when output the signal  $V_{g1}$  (gate signal of S1 and S2), the sinewave  $V_m$  will be compared with the carrier wave  $V_{cr}$ , and when the  $V_m > V_{cr}$ , the output signal controls the switches S1 and S2 operating at ON state, and other switches are OFF state. When output the signal  $V_{g3}$  (gate signal of S3 and S4), the sinewave  $V_{m-}$  will be compared with the carrier wave  $V_{cr}$ , and when the  $V_{m-} > V_{cr}$ , the output signal controls the switches S3 and S4 operating at ON state, and other switches are OFF state. When the Switches S1 and S2 are ON state, the output voltage of the H-bridge inverter is  $V_{AN}$ . And when the switches S3 and S4 are ON state, the output voltage of the H-bridge inverter is  $V_{BN}$ . The actual output voltage ( $V_{AB}$ ) of the inverter is the vector superposition of the output voltages of the above two states, so the actual output voltage ( $V_{AB}$ ) of the inverter is shown in figure 3.2. It can be seen from the output voltage, in the half cycle of the output voltage, there is only one jump from 0 to positive voltage or from 0 to negative voltage. That is to say, the voltage can only jump to one polarity in half a cycle, so this modulation method is called unipolar SPWM [71][72].

Different from the unipolar SPWM, the bipolar SPWM applies only one sinewave compared with carrier wave to generate the control signal of the switches and the waveforms are shown in figure 3.2. And it can be observed from this figure, the output voltage of the inverter has the positive and negative two polarities within the half cycle of the output voltage, so the modulation strategy is called bipolar SPWM [73][74].

Fig 3.1 Standard H-bridge inverter

Fig 3.2 Waveforms of unipolar SPWM method

Fig 3.3 Waveforms of bipolar SPWM method

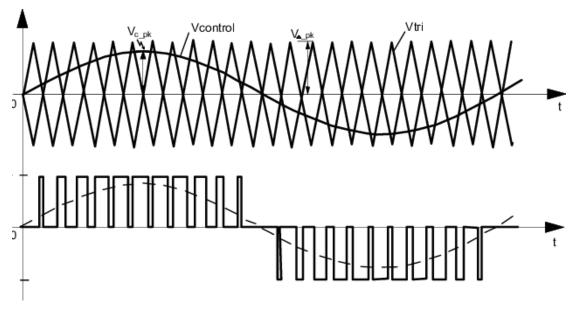

Another way to obtain the control signals using the unipolar SPWM strategy is apply only one sine wave to compare with two triangle carrier waves and the phase difference of the two carrier waves is  $180^{\circ}$ , the arrangement of waveforms is shown in figure 3.4.

Fig 3.4 Waveforms of unipolar SPWM method

Comparing with the two SPWM modulating methods, the unipolar SPWM using two triangle carrier waves to generate the signal to control the H-bridge inverter output 3-level voltage, while the signal modulated by the bipolar SPWM can only control the inverter output 2-level voltage [75][76]. That is to say, the more carrier wave applied in the PWM the more output voltage levels can be controlled by the PWM modulation signals. So, this idea can be extended to the PWM control of multilevel inverters.

#### 3.3 Multicarrier PWM

The multicarrier PWM strategy is mostly used to control the multilevel inverter. The principle is to use one reference wave to compare with multiple carrier waves to generate the control signal. Usually, the sine wave is used to be the reference wave and the triangle wave used to be a carrier wave. Depending on the different layout of the multiple carrier waves, the multicarrier PWM strategy is divided into phase shifted carrier PWM strategy (PSPWM) and level shifted PWM strategy (LSPWM). And then, the LSPWM can be classified into phase disposition PWM (PDPWM), phase opposition disposition PWM (PODPWM) and alternative phase opposition disposition PWM(APODPWM) [77][78][79][80].

#### 3.3.1 Phase shifted carrier PWM (PSPWM)

The PSPSWM is especially suitable for the cascaded multilevel inverter [81] and the arrangement of the waveforms is shown in figure 3.5. In order to control a 5-level inverter, four triangle carrier waves are applied to compared with the sine wave to generate the control signals. All the triangle waves have the same frequency and amplitude [82][83]. However, each triangle wave is  $90^{\circ}$  out of phase between the two adjacent triangle waves. And for a N-level inverter, there will be N-1 triangle waves applied in this modulation strategy and the phase angle between each triangle wave is  $\frac{360^{\circ}}{N-1}$ .

Fig 3.5 Waveform arrangements of the PSPWM

#### 3.3.2 Level shifted PWM (LSPWM)

In the LSPWM strategy, the carrier waves should be arranged by level and all the carrier waves have the same frequency and amplitude. For the LSPWM used to control an N-level inverter, the number of carrier wave is N-1. The amplitude of the reference wave is equal to the sum of the amplitude of all the carrier waves. The signals are generated by comparing the reference wave to the carrier wave separately and when the amplitude

of reference signal is higher than the carrier wave, the output signal pulse is at high level. Otherwise, the signal pulse is at low level [84][85][86].

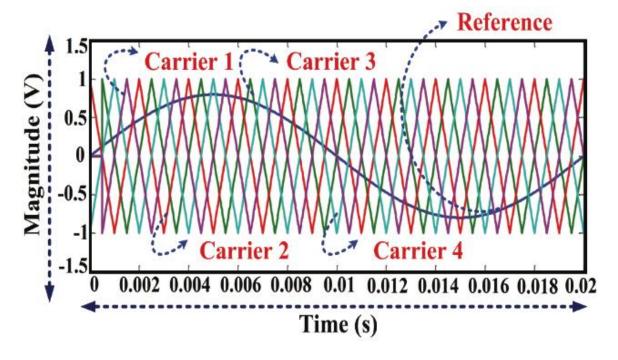

#### A. Phase disposition pulse width modulation (PDPWM)

Figure 3.6 shows the waveforms arrangement of the PDPWM strategy used to control a 7-level cascaded H-bridge inverter. It can be seen there are six triangle carrier waves, and they have the same frequency, amplitude range and the same phase. Each carrier wave is compared with the reference sine wave which is during the corresponding amplitude range. The three triangle waves above the x-axis are used to generate the pulse signal to control the inverter to output the positive three voltage levels. And the three triangle waves below the x-axis is used to generate the pulse signal to control the inverter to output the negative three voltage levels.

#### B. Phase opposition disposition pulse width modulation (PODPWM)

In this strategy, the six triangle waves have the same amplitude and frequency. The three triangle waves above the x-axis are in phase, and the three triangle waves below the x-axis are in phase but they are 180° out of phase with the triangle wave above the x-axis. The three triangle waves above the x-axis are used to generate the pulse signal to control the inverter to output the positive three voltage levels. And the three triangle waves below the x-axis are used to generate the pulse signal to control the inverter to output the negative three voltage levels. The arrangement of the waves is shown in figure 3.7.

#### C. Alternative phase opposition disposition pulse width modulation (APODWM)

In this strategy, the six triangle waves have the same amplitude and frequency. Each triangle wave is 180° out of phase with the two adjacent triangle waves. The three

triangle waves above the x-axis are used to generate the pulse signal to control the inverter to output the positive three voltage levels. And the three triangle waves below the x-axis are used to generate the pulse signal to control the inverter to output the negative three voltage levels.

The arrangement of the waves is shown in figure 3.8.

Fig 3.6 Waveform arrangements of the PDPWM

Fig 3.7 Waveform arrangements of the PODPWM

Fig 3.8 Waveform arrangements of the APODPWM

# 3.4 MATLAB/Simulink model implement

In this section, a 5-level cascaded H-bridge inverter is built in MATLAB/Simulink and different modulation strategies will be built to control the inverter.

The Simulink model of the 5-level cascaded inverter is shown in figure 3.9 and the logic schematic diagrams for the PSPWM, PDPWM, PODPWM and APODPWM are shown in figure 3.10-figure 3.13.

Fig 3.9 Simulink model of 5-level cascaded H-bridge inverter

Fig 3.10 Logic schematic of PSPWM

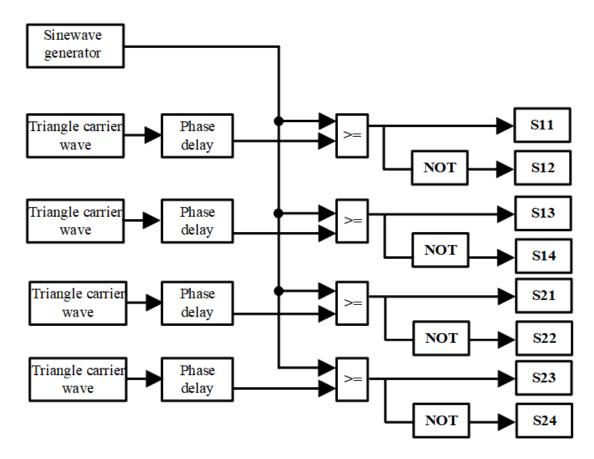

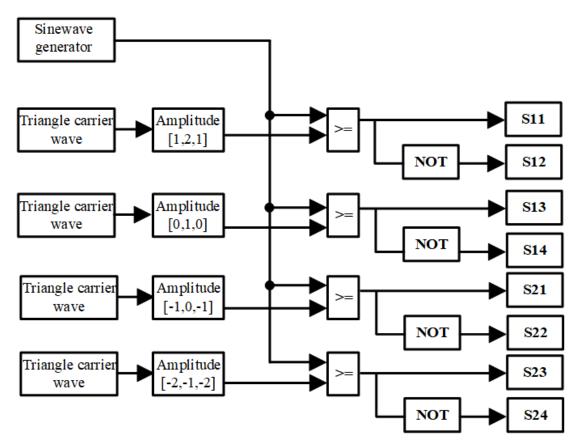

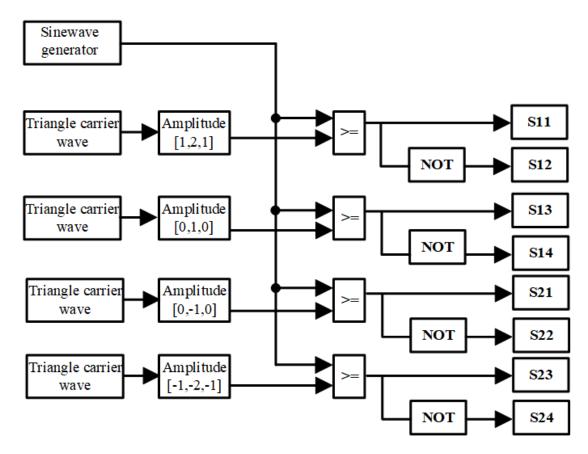

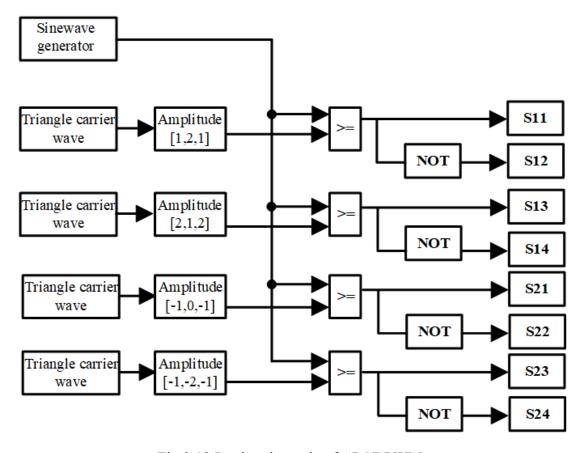

Fig 3.11 Logic schematic of PDPWM

Fig 3.12 Logic schematic of PODPWM

Fig 3.13 Logic schematic of APODPWM

#### 3.5 Capacitance calculation for switched capacitor multilevel inverter

The capacitance of the capacitors applied in the switched capacitor circuit is crucial. In switched capacitor inverters, capacitors are used to generate different voltage levels through charging and discharging processes. These voltage levels are achieved by connecting capacitors in various series and parallel configurations to form the desired output voltage [87][88]. And the capacitors need to maintain stable voltages across different switching states. Incorrect capacitance values can prevent capacitors from reaching or maintaining the required voltage levels during charging and discharging cycles, leading to inaccurate or unstable output voltage levels.

#### 3.5.1 Capacitor voltage ripple

The voltage ripple refers to the variation of fluctuation of voltage across a capacitor over time. It is typically measured as peak-to-peak voltage variation during the charge and discharge cycles of a capacitor. For the switched capacitor multilevel inverters, the capacitor voltage ripple is a critical performance metric. When the inverter operating, the capacitors will undergo several charges and discharges, when the charge and discharge time do not match, or when the switching sequence is unreasonable, can precipitate unbalance charging and discharging of the capacitor. Such unbalancing or over-discharging will increase the capacitor voltage ripple. So the capacitance value directly affects the size of the voltage ripple on the output. A capacitance value that is too small may result in a larger voltage ripple, affecting the accuracy and stability of the voltage levels. A capacitance value that is too big can significantly reduce the voltage ripple. However, the corresponding charging time will be extended, which will be detrimental to the transient response of the inverter. Appropriate capacitance values help reduce voltage ripple and improve the stability of the output voltage [89][90].

#### 3.5.2 Capacitance calculation

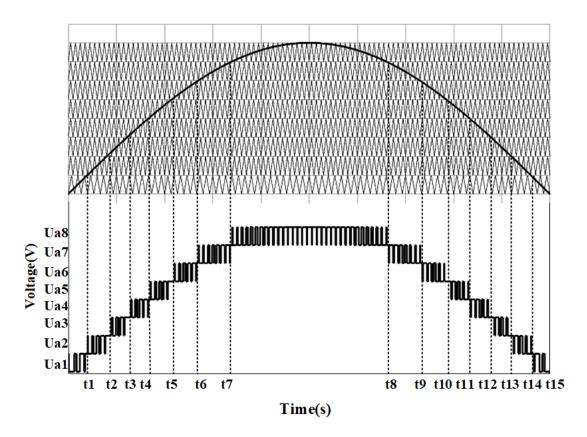

In the context of PWPWM, the intersection area between the sine wave and each triangle wave indicates each period of inverter output voltage level. This relationship is exemplified in figure 3.14, where the intersection points of these waveforms are denoted as  $t_1$  to  $t_{15}$ . These points are indicative of transitional moments where the output voltage shifts from one level to the next.

Due to different switched capacitor topologies and switching logic, the charging and discharging periods of the capacitor are also different, but the charging and discharging must be within a time range corresponding to one or more levels. However, according to the design, the level corresponding to the charging and discharging of the capacitor is known, so if the above-mentioned  $t_1$  to  $t_{10}$  can be calculated, then the charging and discharging time of the capacitor can be known. To this end, equation 3.1 and 3.2 is employed for calculating the specific time instances of  $t_1$  to  $t_{15}$ .

$$t_i = \frac{\arcsin(i/8)}{2\pi f_{ref}}$$

$i = 1, 2, ..., 7$  (3.1)

$$t_j = \pi - \frac{\arcsin[(15-j)/8]}{2\pi f_{ref}}$$

$j = 8, 9, ..., 15$  (3.2),

Where  $f_{ref}$  represents the reference signal frequency.

Fig 3.14 The waveforms of the PDPWM

The capacitance is depending on the voltage ripple  $V_r$ , and the voltage ripple is determined by the maximum discharging amount  $Q_c$ , so the capacitance can be calculated by the equation 3.3 and 3.4.

$$Q_c = \int_{t_b}^{t_a} Isin(2\pi f_{ref} t) dt$$

(3.3),

$$C = \frac{Q_c}{V_r} \tag{3.4},$$

Where  $t_a$  represents the capacitor discharge start moment and  $t_b$  represents the capacitor discharging finish moment. I represent the peak value of the output current.

#### 3.5.3 Chapter conclusion

This chapter introduces the modulation strategies used for multilevel inverters. The basic modulation strategy is sinewave pulse width modulation (SPWM). The principle of SPWM involves comparing a sinusoidal modulation wave with a triangular carrier